Предлагаемое изобретение относится к области радиотехники и может использоваться в качестве базового функционального узла многих устройств автоматики, вычислительной техники, систем связи и приборостроения, в т.ч. работающих при высоких температурах.

В современной микроэлектронике получили широкое распространение операционные усилители (ОУ) [1-11] с входными полевыми транзисторами, которые при реализации на JFet полупроводниковых приборах отличаются крайне низким уровнем шумов. Предлагаемое изобретение относится к данному классу ОУ. В практических схемах ОУ [1-11] выходной и промежуточный каскады реализуются как на n-p-n, так и на p-n-p биполярных транзисторах, что определяется используемыми технологическими процессами. Однако, перспективный арсенид-галлиевый техпроцесс [12], осваиваемый Минским НИИ радиоматериалов (https://mniirm.by/) в интересах предприятий Союзного государства, обеспечивает создание только p-n-p и nJFet транзисторов. Отсутствие n-p-n транзисторов создает схемотехнические проблемы построения GaAs ОУ с выходным каскадом класса АВ. Это не позволяет создать высокотемпературные GaAs ОУ, востребованные в ряде важных отраслей науки и техники - космическом приборостроении, нефтегазовой, автомобильной и авиационной промышленности.

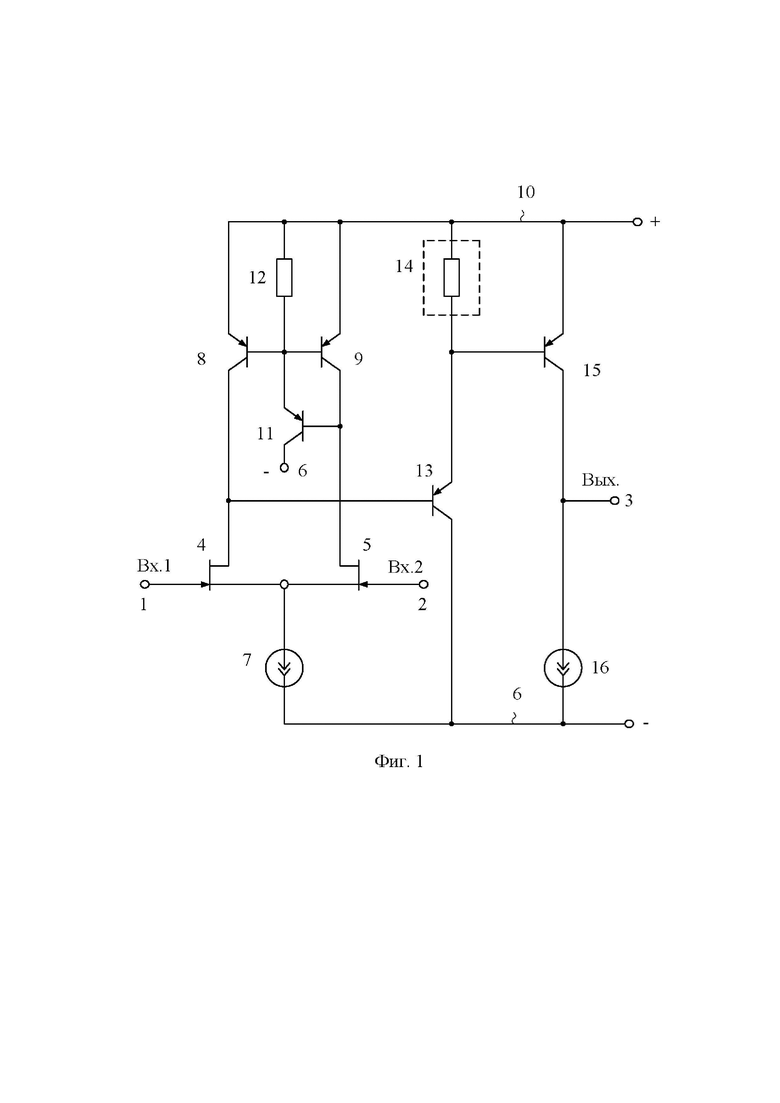

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в публикации «Bob Cordell. LSK489 Application Note. Low Noise Dual Monolithic JFET. URL: https://www.cordellaudio.com/JFETs/LSK489appnote.pdf. 16 p., fig. 11». ОУ-прототип содержит первый 1 и второй 2 входы, а также выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, объединенные истоки которых связаны с первой 6 шиной источника питания через первый 7 источник опорного тока, первый 8 и второй 9 биполярные транзисторы токового зеркала, эмиттеры которых подключены ко второй 10 шине источника питания, а базы объединены, коллектор первого 8 биполярного транзистора токового зеркала соединен со стоком первого 4 входного полевого транзистора, коллектор второго 9 биполярного транзистора токового зеркала связан со стоком второго 5 входного полевого транзистора и подключен к базе первого 11 согласующего биполярного транзистора, эмиттер первого 11 согласующего биполярного транзистора связан со второй 10 шиной источника питания через согласующий двухполюсник 12, второй 13 согласующий биполярный транзистор, коллектор которого соединен с первой 6 шиной источника питания, а эмиттер соединен со второй 10 шиной источника питания через первый 14 токостабилизирующий двухполюсник и подключен к базе первого 15 выходного биполярного транзистора, коллектор которого соединен с выходом устройства 3, а эмиттер подключен ко второй 10 шине источника питания, второй 16 токостабилизирующий двухполюсник.

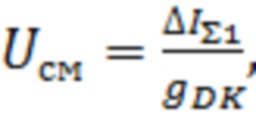

Существенный недостаток ОУ – прототипа состоит в том, что он не реализуется в рамках перспективного арсенид-галлиевого технологического процесса, осваиваемого Минским НИИ радиоматериалов, из-за отсутствия n-p-n арсенид-галлиевых транзисторов [12]. Кроме этого, известный ОУ характеризуется повышенным уровнем систематической составляющей напряжения смещения нуля (десятки милливольт), что обусловлено наличием токовой ошибки ΔIΣ1 в его высокоимпедансном узле Σ1:

(1)

(1)

где gDK – крутизна усиления входного каскада ОУ со входов 1, 2 в высокоимпедансный узел Σ1.

Основная задача предлагаемого изобретения состоит в создании схемы ОУ, которая реализуется в рамках совмещенного GaAs технологического процесса, позволяющего создавать только p-n-p биполярные и nJFet полевые транзисторы. Дополнительная задача – создание схемы ОУ с малым уровнем систематической составляющей напряжения смещения нуля (Uсм), что не реализуется в схеме ОУ-прототипа.

Поставленные задачи достигаются тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы, а также выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, объединенные истоки которых связаны с первой 6 шиной источника питания через первый 7 источник опорного тока, первый 8 и второй 9 биполярные транзисторы токового зеркала, эмиттеры которых подключены ко второй 10 шине источника питания, а базы объединены, коллектор первого 8 биполярного транзистора токового зеркала соединен со стоком первого 4 входного полевого транзистора, коллектор второго 9 биполярного транзистора токового зеркала связан со стоком второго 5 входного полевого транзистора и подключен к базе первого 11 согласующего биполярного транзистора, эмиттер первого 11 согласующего биполярного транзистора связан со второй 10 шиной источника питания через согласующий двухполюсник 12, второй 13 согласующий биполярный транзистор, коллектор которого соединен с первой 6 шиной источника питания, а эмиттер соединен со второй 10 шиной источника питания через первый 14 токостабилизирующий двухполюсник и подключен к базе первого 15 выходного биполярного транзистора, коллектор которого соединен с выходом устройства 3, а эмиттер подключен ко второй 10 шине источника питания, второй 16 токостабилизирующий двухполюсник, предусмотрены новые элементы и связи – объединенные базы первого 8 и второго 9 биполярных транзисторов токового зеркала соединены со стоком первого 4 входного полевого транзистора, коллектор второго 9 биполярного транзистора токового зеркала подключен к базе второго 13 согласующего биполярного транзистора, согласующий двухполюсник 12 выполнен в виде эмиттерного p-n перехода на основе биполярного транзистора, коллектор первого 11 согласующего биполярного транзистора связан с первой 6 шиной источника питания через второй 16 токостабилизирующий двухполюсник, а коллектор второго 13 согласующего биполярного транзистора соединен с первой 6 шиной источника питания, первый 7 источник опорного тока выполнен в виде двух параллельно включенных и идентичных второго 17 и третьего 18 источников опорного тока, каждый из которых реализован на основе выходного полевого транзистора 19, затвор которого связан с истоком этого 19 выходного полевого транзистора через согласующий резистор 20, второй 17 и третий 18 источники опорного тока, а также второй 16 токостабилизирующий двухполюсник выполнены по идентичным схемам на основе выходных полевых транзисторов 19, затворы которых соединены с истоками этих выходных транзисторов через согласующие резисторы 20, причем коллектор первого 11 согласующего биполярного транзистора связан с базой второго 21 выходного биполярного транзистора, эмиттер которого соединен с выходом устройства 3, а коллектор согласован с первой 6 шиной источника питания. Двухполюсник 22 моделирует свойства нагрузки.

На чертеже фиг. 1 показана схема операционного усилителя – прототипа.

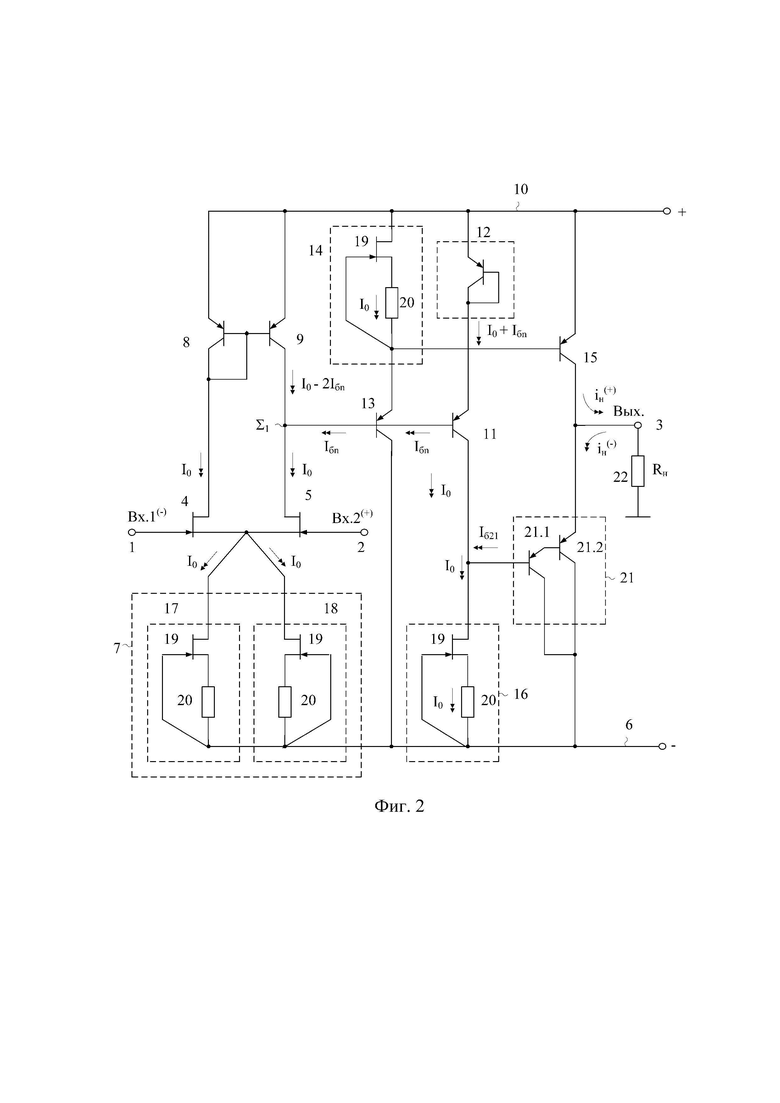

На чертеже фиг. 2 представлена схема заявляемого операционного усилителя в соответствии с формулой изобретения.

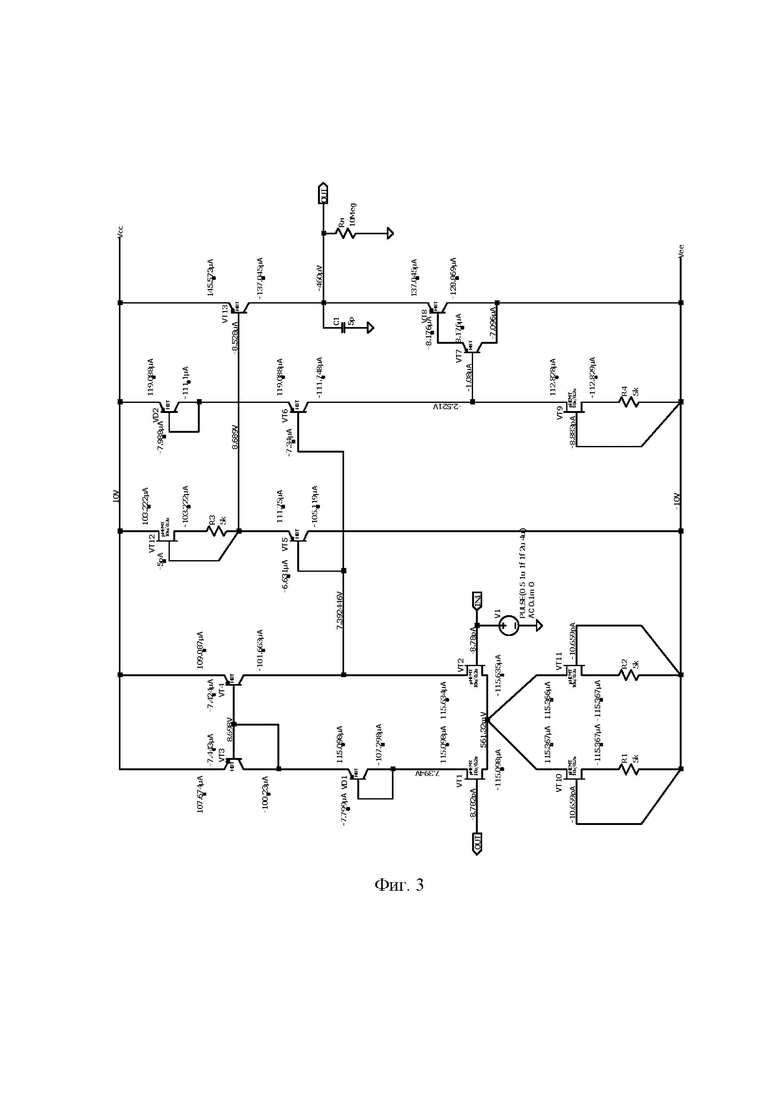

На чертеже фиг. 3 приведен статический режим ОУ фиг. 2 в среде LTspice при t=27 °C, Vcc=10 В, Vee=-10 В, R1÷R4=5 кОм, Cк=5 пФ и высокоомной нагрузке Rн=10 МОм.

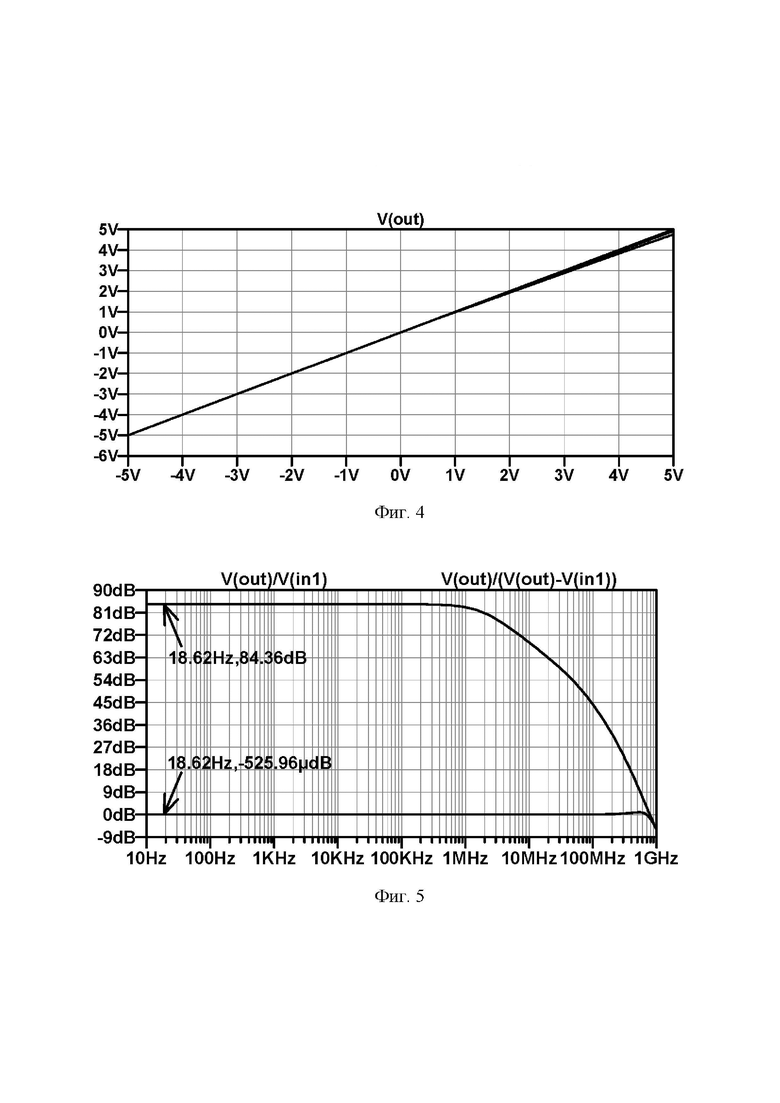

На чертеже фиг. 4 представлена зависимость выходного напряжения ОУ от входного напряжения ОУ фиг. 3 и изменении сопротивления нагрузки в диапазоне Rн=4 кОм/ 10кОм/ 10 МОм.

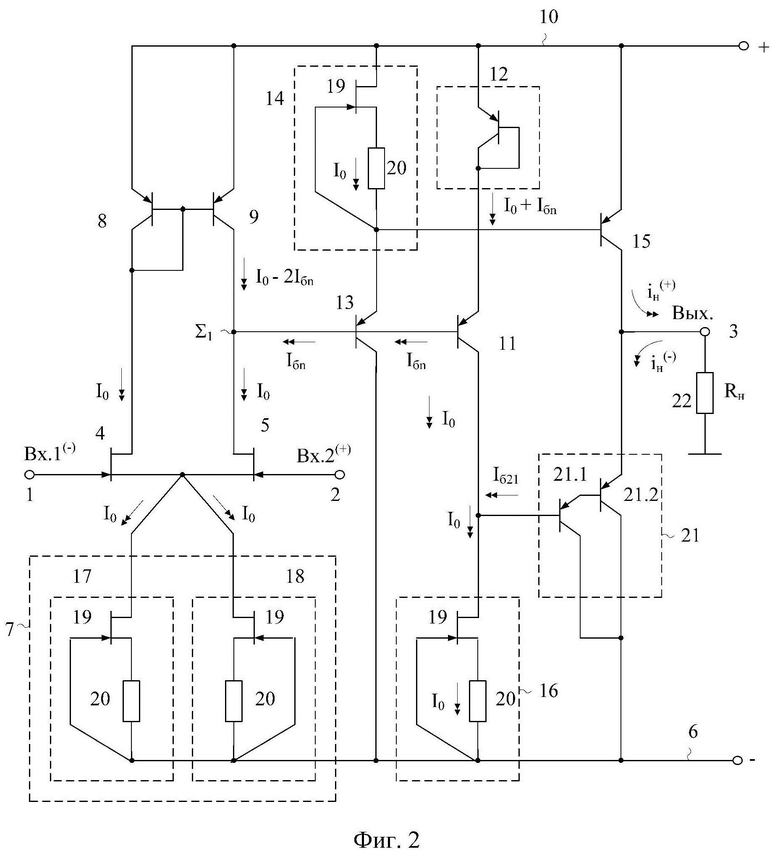

На чертеже фиг. 5 показана логарифмическая амплитудно-частотная характеристика ОУ фиг. 3.

Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 входы, а также выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, объединенные истоки которых связаны с первой 6 шиной источника питания через первый 7 источник опорного тока, первый 8 и второй 9 биполярные транзисторы токового зеркала, эмиттеры которых подключены ко второй 10 шине источника питания, а базы объединены, коллектор первого 8 биполярного транзистора токового зеркала соединен со стоком первого 4 входного полевого транзистора, коллектор второго 9 биполярного транзистора токового зеркала связан со стоком второго 5 входного полевого транзистора и подключен к базе первого 11 согласующего биполярного транзистора, эмиттер первого 11 согласующего биполярного транзистора связан со второй 10 шиной источника питания через согласующий двухполюсник 12, второй 13 согласующий биполярный транзистор, коллектор которого соединен с первой 6 шиной источника питания, а эмиттер соединен со второй 10 шиной источника питания через первый 14 токостабилизирующий двухполюсник и подключен к базе первого 15 выходного биполярного транзистора, коллектор которого соединен с выходом устройства 3, а эмиттер подключен ко второй 10 шине источника питания, второй 16 токостабилизирующий двухполюсник. Объединенные базы первого 8 и второго 9 биполярных транзисторов токового зеркала соединены со стоком первого 4 входного полевого транзистора, коллектор второго 9 биполярного транзистора токового зеркала подключен к базе второго 13 согласующего биполярного транзистора, согласующий двухполюсник 12 выполнен в виде эмиттерного p-n перехода на основе биполярного транзистора, коллектор первого 11 согласующего биполярного транзистора связан с первой 6 шиной источника питания через второй 16 токостабилизирующий двухполюсник, а коллектор второго 13 согласующего биполярного транзистора соединен с первой 6 шиной источника питания, первый 7 источник опорного тока выполнен в виде двух параллельно включенных и идентичных второго 17 и третьего 18 источников опорного тока, каждый из которых реализован на основе выходного полевого транзистора 19, затвор которого связан с истоком этого 19 выходного полевого транзистора через согласующий резистор 20, второй 17 и третий 18 источники опорного тока, а также второй 16 токостабилизирующий двухполюсник выполнены по идентичным схемам на основе выходных полевых транзисторов 19, затворы которых соединены с истоками этих выходных транзисторов через согласующие резисторы 20, причем коллектор первого 11 согласующего биполярного транзистора связан с базой второго 21 выходного биполярного транзистора, эмиттер которого соединен с выходом устройства 3, а коллектор согласован с первой 6 шиной источника питания.

Рассмотрим работу заявляемого ОУ фиг. 2.

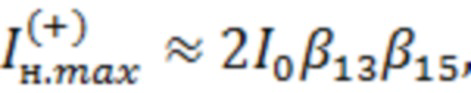

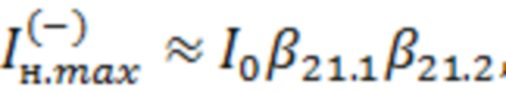

Статический режим транзисторов ОУ по току устанавливается вторым 17, третьим 18 источниками опорного тока, а также вторым 16 и первым 14 токостабилизирующими двухполюсниками. Первая существенная особенность ОУ фиг. 2 состоит в том, что его выходной каскад работает в режиме класса АВ и может обеспечить работу с относительно низкоомной нагрузкой. При этом максимальные выходные токи в нагрузке определяются формулами:

(2)

(2)

(3)

(3)

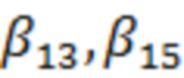

где  – коэффициенты усиления по току базы второго 13 согласующего биполярного транзистора и первого 15 выходного биполярного транзистора;

– коэффициенты усиления по току базы второго 13 согласующего биполярного транзистора и первого 15 выходного биполярного транзистора;

- коэффициенты усиления по току базы первого 21.1 и второго 21.2 транзисторов, образующих составной транзистор Дарлингтона в структуре второго 21 выходного биполярного транзистора.

- коэффициенты усиления по току базы первого 21.1 и второго 21.2 транзисторов, образующих составной транзистор Дарлингтона в структуре второго 21 выходного биполярного транзистора.

Вторая существенная особенность ОУ фиг. 2 – наличие эффекта собственной компенсации статических токов в высокоимпедансном узле Σ1:

. (4)

. (4)

Как следствие, токовая ошибка ΔIΣ1 в высокоимпедансном узле Σ1 близка к нулю

(5)

(5)

Поэтому систематическая составляющая напряжения смещения нуля в предлагаемой схеме (см. формулу (1)) имеет небольшие значения (порядка 460 мкВ), что недостижимо в ОУ-прототипе.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

ОУ с входным каскадом на JFET и перегнутым каскодом на p-n-p биполярных транзисторах

1. Патент US 6144234, fig. 9, 2000 г.

2. Патент US 4406990, fig.4, 1983 г.

3. Bob Cordell. LSK489 Application Note. Low Noise Dual Monolithic JFET. URL: https://www.cordellaudio.com/JFETs/LSK489appnote.pdf. 16 p., fig. 11

ОУ с входным каскадом на JFET и перегнутым каскодом на n-p-n биполярных транзисторах

4. Патент RU 2615070, fig. 1,

ОУ с входными каскадами на КМОП и перегнутым каскодом на p-n-p биполярных транзисторах

5. Патент US 4390850, 1983 г.

6. Патент US 5963085, fig. 3, 1999 г.

7. Патент US 5734296, fig. 3, fig. 4, 1998 г.

ОУ с входными каскадами на КМОП и перегнутым каскодом на n-p-n биполярных транзисторах

8. Патент US 7411451, fig. 5, 2008 г.

9. Патент US 7215200, fig. 6, 2007 г.

10. Патент US 5952882, 1999 г.

Серийные ОУ с входными JFET и перегнутым каскодом на n-p-n биполярных транзисторах

11. OPA42, 140УД30

12. Унифицированные схемотехнические решения аналоговых арсенид-галлиевых микросхем / Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. // Известия вузов. Электроника. 2022. Т. 27. № 4. С. 475–488. DOI: https://doi.org/10.24151/1561-5405-2022-27-4-475-488.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2616573C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2624585C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2595926C1 |

Изобретение относится к области радиотехники. Технический результат: создание операционного усилителя, который реализуется в рамках совмещенного GaAs технологического процесса, позволяющего создавать только p-n-p биполярные и nJFet полевые транзисторы, а также обеспечение малого уровня смещения нуля. Для этого предложен операционный усилитель, в котором объединенные базы первого (8) и второго (9) биполярных транзисторов токового зеркала соединены со стоком первого (4) входного полевого транзистора, коллектор второго (9) биполярного транзистора токового зеркала подключен к базе второго (13) согласующего биполярного транзистора, согласующий двухполюсник (12) выполнен в виде эмиттерного p-n перехода на основе биполярного транзистора, коллектор первого (11) согласующего биполярного транзистора связан с первой (6) шиной источника питания через второй (16) токостабилизирующий двухполюсник, а коллектор второго (13) согласующего биполярного транзистора соединен с первой (6) шиной источника питания, первый (7) источник опорного тока выполнен в виде двух параллельно включенных и идентичных второго (17) и третьего (18) источников опорного тока. 5 ил.

Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом, содержащий первый (1) и второй (2) входы, а также выход (3) устройства, первый (4) и второй (5) входные полевые транзисторы, объединенные истоки которых связаны с первой (6) шиной источника питания через первый (7) источник опорного тока, первый (8) и второй (9) биполярные транзисторы токового зеркала, эмиттеры которых подключены ко второй (10) шине источника питания, а базы объединены, коллектор первого (8) биполярного транзистора токового зеркала соединен со стоком первого (4) входного полевого транзистора, коллектор второго (9) биполярного транзистора токового зеркала связан со стоком второго (5) входного полевого транзистора и подключен к базе первого (11) согласующего биполярного транзистора, эмиттер первого (11) согласующего биполярного транзистора связан со второй (10) шиной источника питания через согласующий двухполюсник (12), второй (13) согласующий биполярный транзистор, коллектор которого соединен с первой (6) шиной источника питания, а эмиттер соединен со второй (10) шиной источника питания через первый (14) токостабилизирующий двухполюсник и подключен к базе первого (15) выходного биполярного транзистора, коллектор которого соединен с выходом устройства (3), а эмиттер подключен ко второй (10) шине источника питания, второй (16) токостабилизирующий двухполюсник, отличающийся тем, что объединенные базы первого (8) и второго (9) биполярных транзисторов токового зеркала соединены со стоком первого (4) входного полевого транзистора, коллектор второго (9) биполярного транзистора токового зеркала подключен к базе второго (13) согласующего биполярного транзистора, согласующий двухполюсник (12) выполнен в виде эмиттерного p-n перехода на основе биполярного транзистора, коллектор первого (11) согласующего биполярного транзистора связан с первой (6) шиной источника питания через второй (16) токостабилизирующий двухполюсник, а коллектор второго (13) согласующего биполярного транзистора соединен с первой (6) шиной источника питания, первый (7) источник опорного тока выполнен в виде двух параллельно включенных и идентичных второго (17) и третьего (18) источников опорного тока, каждый из которых реализован на основе выходного полевого транзистора (19), затвор которого связан с истоком этого (19) выходного полевого транзистора через согласующий резистор (20), второй (17) и третий (18) источники опорного тока, а также второй (16) токостабилизирующий двухполюсник выполнены по идентичным схемам на основе выходных полевых транзисторов (19), затворы которых соединены с истоками этих выходных транзисторов через согласующие резисторы (20), причем коллектор первого (11) согласующего биполярного транзистора связан с базой второго (21) выходного биполярного транзистора, эмиттер которого соединен с выходом устройства (3), а коллектор согласован с первой (6) шиной источника питания.

| BOB CORDELL, "LSK489 Application Note | |||

| Low Noise Dual Monolithic JFET", https://web.archive.org/web/20180127174550/https://www.cordellaudio.com/JFETs/LSK489appnote.pdf, опубл | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Операционный усилитель | 1974 |

|

SU500574A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| US 6501333 B1, 31.12.2002. | |||

Авторы

Даты

2024-02-09—Публикация

2023-11-02—Подача