Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве арсенид-галлиевого выходного каскада различных GaAs аналоговых устройств, в том числе быстродействующих операционных усилителей (ОУ), допускающих работу в условиях воздействия проникающей радиации, низких или высоких температур.

Известно значительное количество схем выходных каскадов (ВК) и буферных усилителей (БУ) аналоговых микроэлектронных изделий, которые реализуются на биполярных (BJT) и полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-26]. Сегодня популярны схемы ВК с составными BJT и CMOS (JFET) выходными транзисторами с разными типами каналов [31-33], однотактные ВК с входным CMOS и выходными n-p-n транзисторами [34], двухтактные ВК с выходными однотипными JFET транзисторами и входными биполярными BJT p-n-p (n-p-n) [35], двухтактные ВК на комплементарных JFET транзисторах [36-39], однотактные ВК только на JFET [40]. Известны также нетрадиционные ВК, у которых нагрузка подключается к истоковой [41] или эмиттерной [42, 43] цепям входного дифференциального каскада.

Во многих применениях схема ВК адаптируется под конкретные технологические процессы и внешние воздействующие факторы, например, влияние низких температур и радиации, т.к. только в этом случае обеспечивается реализация предельных параметров выходного каскада.

В настоящее время в российской и зарубежной микроэлектронике уделяется повышенное внимание арсенид-галлиевым микросхемам [44]. Данное направление создания электронной компонентной базы относится к числу наиболее перспективных в задачах космического приборостроения. Однако, особенности арсенид-галлиевых технологических процессов накладывают существенные ограничения на типы реализуемых транзисторов и их характеристики. Так, например, арсенид-галлиевый технологический процесс, освоенный Минским научно-исследовательским институтом радиоматериалов (https://mniirm.by/), ориентирован на изготовление аналоговых схем, содержащих только полевые GaAs транзисторы с управляющим p-n переходом (n- или p-канал) и биполярные GaAs p-n-p транзисторы. Применение других полупроводниковых приборов не допускается. Это накладывает существенные ограничения на схемотехнику аналоговых устройств, ориентированных на данный технологический процесс.

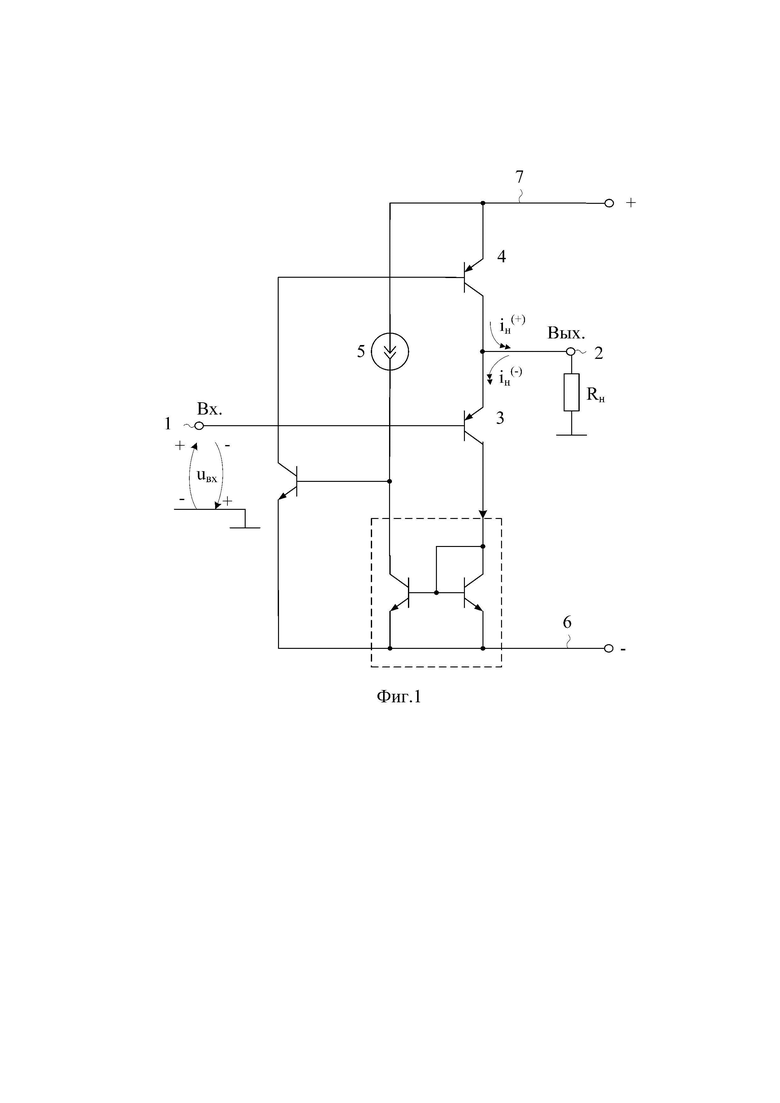

Ближайшим прототипом (фиг. 1) заявляемого устройства является выходной каскад, представленный в А.св. СССР 1092701, 1984 г. Он содержит (фиг. 1) вход 1 и выход 2 устройства, входной 3 и выходной 4 p-n-p транзисторы, токостабилизирующий двухполюсник 5, первую 6 и вторую 7 шины источников питания, причем вход 1 устройства соединен с базой входного p-n-p транзистора 3, выход устройства 2 связан с эмиттером входного p-n-p транзистора 3 и коллектором выходного p-n-p транзистора 4, а эмиттер выходного p-n-p транзистора 4 согласован со второй 7 шиной источника питания.

Существенный недостаток выходного каскада – прототипа (фиг. 1) состоит в том, что при его реализации на JFET GaAs полевых транзисторах с управляющим p-n переходом и p-n-p GaAs биполярных транзисторов, он не может обеспечить двуполярные напряжения в нагрузке Rн.

Основная задача предполагаемого изобретения состоит в создании выходного каскада операционного усилителя, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим p-n переходом и биполярных GaAs p-n-p транзисторах, который обеспечивает в нагрузке Rн (фиг. 1) выходные токи положительного iн(+) и отрицательного iн(-) направлений, а также ускоряет процесс перезарядки емкости нагрузки Cн, что важно для быстродействующих ОУ.

Поставленная задача достигается тем, что в выходном каскаде фиг. 1, содержащем вход 1 и выход 2 устройства, входной 3 и выходной 4 p-n-p транзисторы, токостабилизирующий двухполюсник 5, первую 6 и вторую 7 шины источников питания, причем вход 1 устройства соединен с базой входного p-n-p транзистора 3, выход устройства 2 связан с эмиттером входного p-n-p транзистора 3 и коллектором выходного p-n-p транзистора 4, а эмиттер выходного p-n-p транзистора 4 согласован со второй 7 шиной источника питания, предусмотрены новые элементы и связи – в схему введены дополнительный p-n-p транзистор 8, первый 9 и второй 10 дополнительные полевые транзисторы с управляющим p-n переходом, а также первый 11 и второй 12 дополнительные токостабилизирующие двухполюсники, причем коллектор входного p-n-p транзистора 3 соединен с базой дополнительного p-n-p транзистора 8 и через токостабилизирующий двухполюсник 5 связан с первой 6 шиной источника питания, эмиттер дополнительного p-n-p транзистора 8 соединен с истоком первого 9 дополнительного полевого транзистора с управляющим p-n переходом, а коллектор дополнительного p-n-p транзистора 8 согласован с первой 6 шиной источника питания, сток первого 9 дополнительного полевого транзистора с управляющим p-n переходом связан со второй 7 шиной источника питания через первый 11 дополнительный токостабилизирующий двухполюсник, затвор первого 9 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком второго 10 дополнительного полевого транзистора с управляющим p-n переходом и через второй 12 дополнительный токостабилизирующий двухполюсник связан с первой 6 шиной источника питания, сток второго 10 дополнительного полевого транзистора с управляющим p-n переходом согласован со второй 7 шиной источника питания, а затвор второго 10 дополнительного полевого транзистора с управляющим p-n переходом подключен к первой 6 шине источника питания.

На чертеже фиг. 1 показана схема выходного каскада-прототипа по А.св. СССР 1092701.

На чертеже фиг. 2 представлена схема арсенид-галиевого выходного каскада в соответствии с п.1, п.2 формулы изобретения.

На чертеже фиг. 3 приведена модификация арсенид-галиевого выходного каскада в соответствии с п.3 формулы изобретения.

На чертеже фиг. 4 показана схема для моделирования GaAs выходного каскада фиг.2 в среде LTspice при комнатной температуре (t=27 oC), +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=100 мкА, R1=10 кОм, R2=1 Гом, V1=4 В.

На чертеже фиг.5 представлена амплитудная характеристика GaAs выходного каскада фиг.4 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload= 2 кОм/10 кОм/1 МОм, I1= I2=100 мкА, R1=10 кОм, R2=1 ГОм, V1=4 В.

На чертеже фиг.6 приведена АЧХ GaAs выходного каскада фиг.4 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload= 5 кОм/1 МОм, I1= I2=100 мкА, R1=10 кОм, R2=1 ГОм, V1=4 В.

На чертеже фиг. 7 показана схема для моделирования GaAs выходного каскада фиг.3 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload= 1 МОм, I1= 100 мкА, R1=14 кОм, R2= 10 кОм.

На чертеже фиг.8 представлена амплитудная характеристика (АЧХ) GaAs выходного каскада фиг.6 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload= 2 кОм/10 кОм/1 МОм, I1= 100 мкА, R1=14 кОм, R2= 10 мкОм.

На чертеже фиг.9 приведена АЧХ GaAs выходного каскада фиг.7 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload= 5 кОм/1 МОм, I1= 100 мкА, R1=14 кОм, R2= 10 кОм.

Арсенид-галлиевый выходной каскад быстродействующего операционного усилителя фиг. 2 содержит вход 1 и выход 2 устройства, входной 3 и выходной 4 p-n-p транзисторы, токостабилизирующий двухполюсник 5, первую 6 и вторую 7 шины источников питания, причем вход 1 устройства соединен с базой входного p-n-p транзистора 3, выход устройства 2 связан с эмиттером входного p-n-p транзистора 3 и коллектором выходного p-n-p транзистора 4, а эмиттер выходного p-n-p транзистора 4 согласован со второй 7 шиной источника питания. В схему введены дополнительный p-n-p транзистор 8, первый 9 и второй 10 дополнительные полевые транзисторы с управляющим p-n переходом, а также первый 11 и второй 12 дополнительные токостабилизирующие двухполюсники, причем коллектор входного p-n-p транзистора 3 соединен с базой дополнительного p-n-p транзистора 8 и через токостабилизирующий двухполюсник 5 связан с первой 6 шиной источника питания, эмиттер дополнительного p-n-p транзистора 8 соединен с истоком первого 9 дополнительного полевого транзистора с управляющим p-n переходом, а коллектор дополнительного p-n-p транзистора 8 согласован с первой 6 шиной источника питания, сток первого 9 дополнительного полевого транзистора с управляющим p-n переходом связан со второй 7 шиной источника питания через первый 11 дополнительный токостабилизирующий двухполюсник, затвор первого 9 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком второго 10 дополнительного полевого транзистора с управляющим p-n переходом и через второй 12 дополнительный токостабилизирующий двухполюсник связан с первой 6 шиной источника питания, сток второго 10 дополнительного полевого транзистора с управляющим p-n переходом согласован со второй 7 шиной источника питания, а затвор второго 10 дополнительного полевого транзистора с управляющим p-n переходом подключен к первой 6 шине источника питания. Двухполюсник Rн, который, как правило, зашунтирован емкостью Cн, моделирует свойство нагрузки.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, база дополнительного p-n-p транзистора 8 связана с дополнительным источником напряжения 13 через дополнительный p-n переход 14.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, база дополнительного p-n-p транзистора 8 соединена с эмиттером второго 15 дополнительного p-n-p транзистора, база которого подключена к истоку второго 10 дополнительного полевого транзистора с управляющим p-n переходом, а коллектор согласован с первой 6 шиной источника питания. В частном случае входной 3 и выходной 4 p-n-p транзисторы могут выполнятся как составные транзисторы по схеме Дарлингтона и содержать исходные транзисторы 3.1 и 3.2, а также 4.1, 4.2. Это способствует улучшению работы ВК при низкоомных нагрузках. Конденсатор Cн моделирует свойства емкостной нагрузки ОУ.

Рассмотрим работу предлагаемого выходного каскада фиг. 2 при большом сопротивлении нагрузки.

За счет отрицательной обратной связи через дополнительный p-n-p транзистор 8, первый 9 дополнительный полевой транзистор и выходной p-n-p транзистор 4 cтатический ток эмиттера входного p-n-p транзистора 3 определяется током токостабилизирующего двухполюсника 5 и устанавливается на уровне I0=I5.

Если на вход 1 подается положительное напряжение относительно общей шины, то это вызывает увеличение тока эмиттера выходного p-n-p транзистора 4 и формирование положительного тока iн(+) в нагрузке Rн. Максимальное значение тока Iн.max(+) зависит от параметров выходного p-n-p транзистора 4, который может выполнятся как составной транзистор Дарлингтона (фиг.3).

Когда на вход 1 подается отрицательное напряжение uвх(-), то это напряжение передается на базу входного p-n-p транзистора 3, который по цепи эмиттера формирует отрицательное приращение iн(-) в нагрузке Rн. В этом режиме выходной p-n-p транзистор 4 запирается и не влияет на работу схемы. Увеличение тока коллектора входного p-n-p транзистора 3 на величину iн(-) приводит к отпиранию дополнительного p-n прехода 14 и, как следствие, большие значения тока iн(-)≥I0=I5 будут «закорачиваться» на дополнительный источник напряжения 13. Это предотвращает насыщение входного p-n-p транзистора 3.

Для получения повышенных значений Iн.max(-) в качестве входного p-n-p транзистора 3 может применяться составной транзистор по так называемой схеме Дарлингтона (фиг.3).

Амплитудная характеристика предлагаемого ВК фиг. 7, представленная на графиках фиг. 8, показывает, что рассматриваемая схема при двуполярном питании ±10 В и разных Rн обеспечивает выходные напряжения с максимальной амплитудой от -8,69 В до +9,66 В.

Компьютерное моделирование (фиг. 8) показывает, что предлагаемый выходной каскад, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [26], имеет существенные достоинства в сравнении с известным вариантом построения ВК при его реализации в рамках рассматриваемого арсенид-галлиевого технологического процесса, обеспечивающего создание только полевых транзисторов с управляющим p-n переходом и биполярных p-n-p транзисторов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU № 2523947 fig. 4, 2014 г.

2. Патент WO 2007135139, 2007 г.

3. Патент US 4743862, 1988 г.

4. Патент US 6433638, fig. 1a-2, 2002 г.

5. Патентная заявка US 20050253653, 2005 г.

6. Патент US 4825174, fig. 3, fig. 6, 1989 г.

7. Патент RU 2099856, fig. 3, 1997 г.

8. Патент US 4904953, fig. 2, 1990 г.

9. Патент US 7896339, fig. 4, 2011 г.

10. Патент US 6342814, 2002 г.

11. Патентная заявка US 2010/0182086, 2010 г.

12. Патент US 5387880, fig. 1, 1995 г.

13. Патент US 4598253, 1986 г.

14. Патент US 4667165, fig. 2, 1987 г.

15. Патент US 4596958, 1986 г.

16. Патент US 7116172, fig. 4, fig. 5, 2006 г.

17. Патент US 5648743, 1997 г.

18. Патент US 5367271, fig. 2, 1994 г.

19. Патентная заявка US 2000/0112075, fig. 3, 2000 г.

20. Патент US 5065043, fig. 1f, 1991 г.

21. Патентная заявка US 2007/0115056, fig. 2, 2007 г.

22. Патент US 7548117, fig. 5, 2009 г.

23. Патент EP 0 293486 B1, fig. 5, 1991 г.

24. Патент US 4420726, fig. 1 – fig. 3, 1983 г.

25. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ.— Изд. 2-е. — М.: Издательство БИНОМ. 2014. - 704 с. Рис. 3.26, рис. 3.28, рис. 3.29.

26. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. – М.: СОЛОН-Пресс, 2021. – 200 с.

27. M. Fresina, "Trends in GaAs HBTs for wireless and RF," 2011 IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Atlanta, GA, USA, 2011, pp. 150-153. doi: 10.1109/BCTM.2011.6082769.

28. P. J. Zampardi, M. Sun, C. Cismaru and J. Li, "Prospects for a BiCFET III-V HBT Process," 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 2012, pp. 1-3. doi: 10.1109/CSICS.2012.6340116.

29. W. Liu, D. Hill, D. Costa and J. S. Harris, "High-performance microwave AlGaAs-InGaAs Pnp HBT with high-DC current gain," in IEEE Microwave and Guided Wave Letters, vol. 2, no. 8, pp. 331-333, Aug. 1992. doi: 10.1109/75.153604.

30. Peatman W. et al. InGaP-Plus™: advanced GaAs BiFET technology and applications // CS MANTECH Conference, May 14-17, 2007, Austin, Texas, USA. pp. 243-246.

31. Патентная заявка US 2007/0115056, fig.2, 2007 г.

32. Патент DE 2548906, fig. 1, 1975 г.

33. Патент WO 2014/168518 (PCT RU 2014/000255), fig. 8, 2014 г.

34. Патент US 4.420.726, fig. 1, fig. 3, 1983 г.

35. Патент DE 2354552, fig. 2, 1973 г.

36. Патент RU 2723673, 2020 г.

37. Патент RU 2721940, 2020 г.

38. D. Danyuk. Linear Integrated Systems Headphone Amplifier Evaluation Board. URL: https://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluation_Board.pdf

39. Патент US 5.083.046, fig. 3, 1992 г.

40. Патент US 5.367.271, fig. 2, 1994 г.

41. Патент RU 2732583, fig. 1, 2020 г.

42. Патент RU 2676014, fig. 1, fig. 2, 2018 г.

43. Патент RU 2669075, fig.2, fig. 3, 2018 г.

44. Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. Арсенид-галлиевый аналоговый базовый кристалл // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2021. Выпуск 2. С. 47-54. doi:10.31114/2078-7707-2021-2-47-54.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ | 2021 |

|

RU2767976C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| НЕИНВЕРТИРУЮЩИЙ ВЫХОДНОЙ КАСКАД АРСЕНИД-ГАЛЛИЕВОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2784049C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве арсенид-галлиевого выходного каскада различных GaAs аналоговых устройств, в том числе быстродействующих операционных усилителей (ОУ), допускающих работу в условиях воздействия проникающей радиации, низких или высоких температур. Технический результат: создание выходного каскада операционного усилителя, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим p-n-переходом и биполярных GaAs p-n-p-транзисторах, который обеспечивает в нагрузке Rн (фиг. 1) выходные токи положительного iн(+) и отрицательного iн(-) направлений, а также ускоряет процесс перезарядки емкости нагрузки Cн, что важно для быстродействующих ОУ. Арсенид-галлиевый выходной каскад быстродействующего операционного усилителя содержит вход (1) и выход (2) устройства, входной (3) и выходной (4) p-n-p-транзисторы, токостабилизирующий двухполюсник (5), первую (6) и вторую (7) шины источников питания. В схему введены дополнительный p-n-p-транзистор (8), первый (9) и второй (10) дополнительные полевые транзисторы с управляющим p-n-переходом, а также первый (11) и второй (12) дополнительные токостабилизирующие двухполюсники. 2 з.п. ф-лы, 9 ил.

1. Арсенид-галлиевый выходной каскад быстродействующего операционного усилителя, содержащий вход (1) и выход (2) устройства, входной (3) и выходной (4) p-n-p-транзисторы, токостабилизирующий двухполюсник (5), первую (6) и вторую (7) шины источников питания, причем вход (1) устройства соединен с базой входного p-n-p-транзистора (3), выход устройства (2) связан с эмиттером входного p-n-p-транзистора (3) и коллектором выходного p-n-p-транзистора (4), а эмиттер выходного p-n-p-транзистора (4) согласован со второй (7) шиной источника питания, отличающийся тем, что в схему введены дополнительный p-n-p-транзистор (8), первый (9) и второй (10) дополнительные полевые транзисторы с управляющим p-n-переходом, а также первый (11) и второй (12) дополнительные токостабилизирующие двухполюсники, причем коллектор входного p-n-p-транзистора (3) соединен с базой дополнительного p-n-p-транзистора (8) и через токостабилизирующий двухполюсник (5) связан с первой (6) шиной источника питания, эмиттер дополнительного p-n-p-транзистора (8) соединен с истоком первого (9) дополнительного полевого транзистора с управляющим p-n-переходом, а коллектор дополнительного p-n-p-транзистора (8) согласован с первой (6) шиной источника питания, сток первого (9) дополнительного полевого транзистора с управляющим p-n-переходом связан со второй (7) шиной источника питания через первый (11) дополнительный токостабилизирующий двухполюсник, затвор первого (9) дополнительного полевого транзистора с управляющим p-n-переходом соединен с истоком второго (10) дополнительного полевого транзистора с управляющим p-n-переходом и через второй (12) дополнительный токостабилизирующий двухполюсник связан с первой (6) шиной источника питания, сток второго (10) дополнительного полевого транзистора с управляющим p-n-переходом согласован со второй (7) шиной источника питания, а затвор второго (10) дополнительного полевого транзистора с управляющим p-n-переходом подключен к первой (6) шине источника питания.

2. Арсенид-галлиевый выходной каскад быстродействующего операционного усилителя по п.1, отличающийся тем, что база дополнительного p-n-p-транзистора (8) связана с дополнительным источником напряжения (13) через дополнительный p-n-переход (14).

3. Арсенид-галлиевый выходной каскад быстродействующего операционного усилителя по п.1, отличающийся тем, что база дополнительного p-n-p-транзистора (8) соединена с эмиттером второго (15) дополнительного p-n-p-транзистора, база которого подключена к истоку второго (10) дополнительного полевого транзистора с управляющим p-n-переходом, а коллектор согласован с первой (6) шиной источника питания.

| Двухтактный усилитель | 1983 |

|

SU1092701A1 |

| ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ТРАНЗИСТОРОВ | 2013 |

|

RU2523947C1 |

| УСИЛИТЕЛЬНЫЙ КАСКАД | 1994 |

|

RU2099856C1 |

| US 4743862 A1, 10.05.1988 | |||

| US 6433638 B1, 13.08.2002 | |||

| US 7896339 B2, 01.03.2011. | |||

Авторы

Даты

2022-06-14—Публикация

2022-02-07—Подача