Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, в операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих в широком диапазоне температур и воздействия радиации.

Известны схемы классических дифференциальных каскадов (ДК) на полевых транзисторах с управляющим p-n переходом (JFet) [1-15], которые стали основой многих малошумящих аналоговых микросхем.

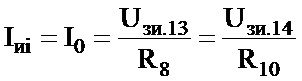

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад, представленный в патенте RU 2679970, фиг. 2, 2019 г., который содержит первый 1 и второй 2 входы, первый 3 и второй 4 токовые выходы, согласованные с первой 5 шиной источника питания, первый 6 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток согласован со второй 7 шиной источника питания, исток связан с первым выводом первого 8 вспомогательного резистора, второй 9 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, сток согласован со второй 7 шиной источника питания, исток связан с первым выводом второго 10 вспомогательного резистора, первый 11 выходной полевой транзистор, сток которого подключен к первому 3 токовому выходу устройства, второй 12 выходной полевой транзистор, сток которого подключен ко второму 4 токовому выходу устройства.

Существенный недостаток известного ДК фиг. 1 состоит в том, что при работе полевых транзисторов в микрорежиме его крутизна усиления (SДК) получается небольшой. Это отрицательно сказывается на работе микромощных устройств, например, операционных усилителей, компараторов, в которых ДК фиг.1 применяется во входных или промежуточных каскадах.

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ДК фиг. 2 повышается крутизна преобразования входного дифференциального напряжения в выходные дифференциальные токи устройства (SДК), что важно при работе ДК с малыми статическими токами транзисторов, в т.ч. арсенид-галлиевых полевых транзисторов [16]. В конечном итоге, это повышает коэффициент усиления по напряжению практических схем включения ДК, например, в операционных усилителях или компараторах напряжения.

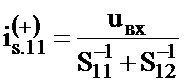

Поставленная задача решается тем, что в дифференциальном каскаде фиг. 1, содержащем первый 1 и второй 2 входы, первый 3 и второй 4 токовые выходы, согласованные с первой 5 шиной источника питания, первый 6 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток согласован со второй 7 шиной источника питания, исток связан с первым выводом первого 8 вспомогательного резистора, второй 9 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, сток согласован со второй 7 шиной источника питания, исток связан с первым выводом второго 10 вспомогательного резистора, первый 11 выходной полевой транзистор, сток которого подключен к первому 3 токовому выходу устройства, второй 12 выходной полевой транзистор, сток которого подключен ко второму 4 токовому выходу устройства, предусмотрены новые элементы и связи – исток первого 6 входного полевого транзистора соединен с затвором первого 13 дополнительного полевого транзистора, исток которого соединен с истоком первого 6 входного полевого транзистора через первый 8 вспомогательный резистор и подключен к затвору первого 11 выходного полевого транзистора, сток первого 13 дополнительного полевого транзистора соединен с истоком первого 11 выходного полевого транзистора, исток второго 9 входного полевого транзистора соединен с затвором второго 14 дополнительного полевого транзистора, исток которого соединен с истоком второго 9 входного полевого транзистора через второй 10 вспомогательный резистор и подключен к затвору второго 12 выходного полевого транзистора, сток второго 14 дополнительного полевого транзистора соединен с истоком второго 12 выходного полевого транзистора и связан со стоком первого 13 дополнительного полевого транзистора.

На чертеже фиг. 1 представлена схема ДК-прототипа по патенту RU 2679970, фиг. 2, 2019 г.

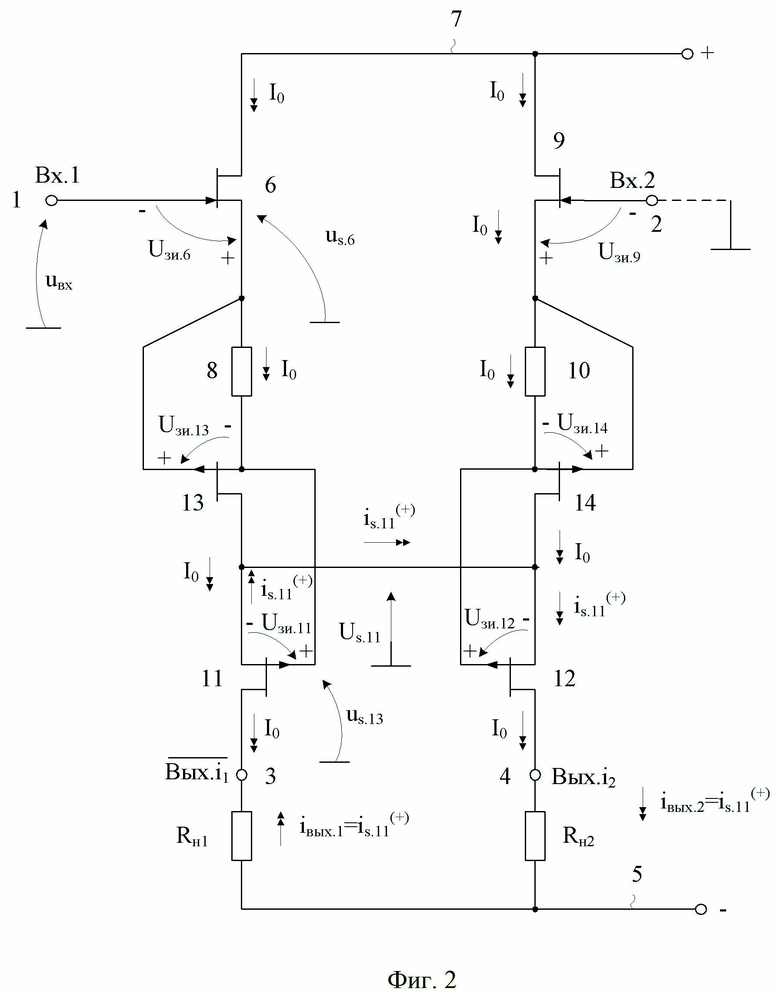

На чертеже фиг. 2 приведена схема заявляемого дифференциального каскада в соответствии с п.1 и п. 2 формулы изобретения для случая, когда в качестве полевых транзисторов используются комплементарные полевые транзисторы с управляющим p-n переходом.

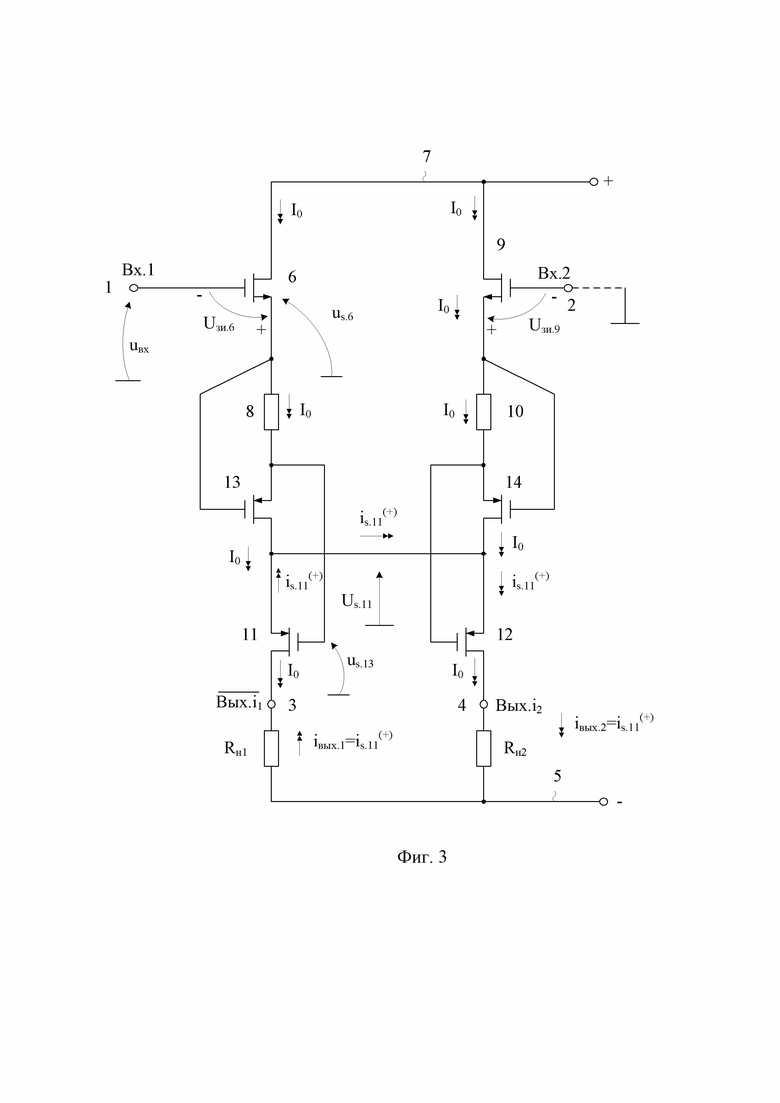

На чертеже фиг. 3 показана схема заявляемого дифференциального каскада в соответствии с п.3 формулы изобретения для случая, когда в качестве полевых транзисторов используются комплементарные КМОП транзисторы со встроенными p и n каналами.

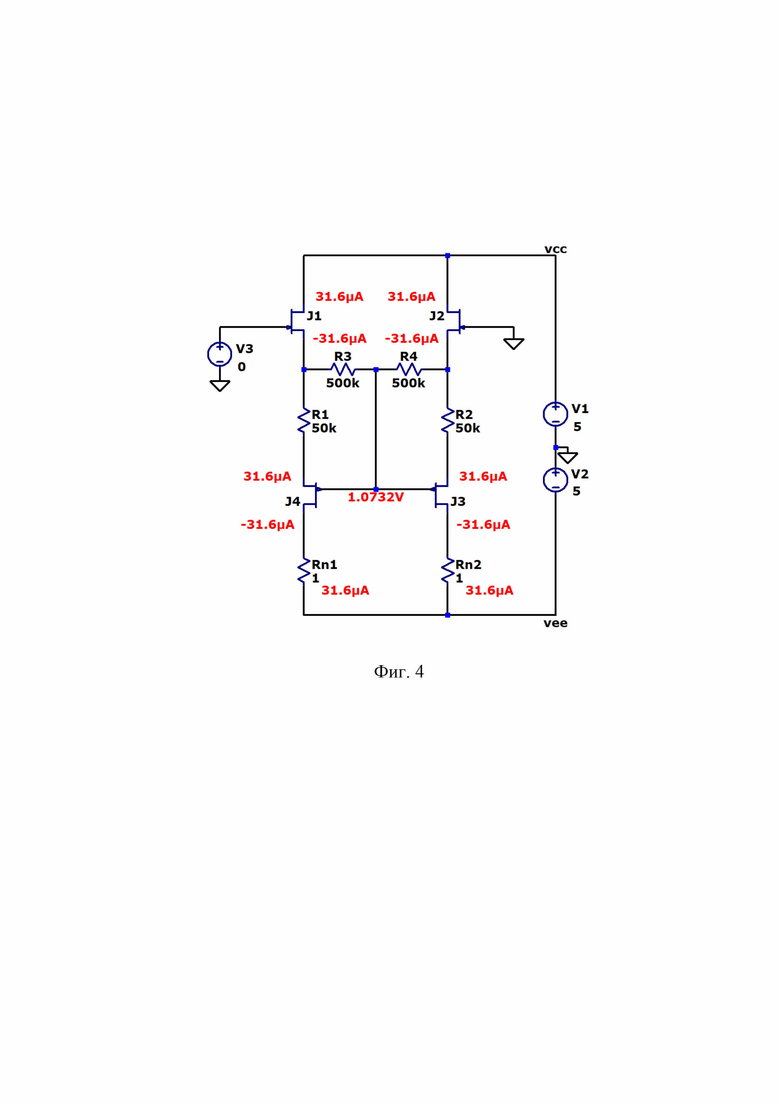

На чертеже фиг. 4 приведен статический режим в среде LTSpice дифференциального каскада-прототипа фиг. 1 при 27°С, резисторах R1=R2=50кОм, R4=R5=500кОм. Выбор численного значения сопротивлений R4=R5=500кОм сделан для исключения их влияния на крутизну ДК.

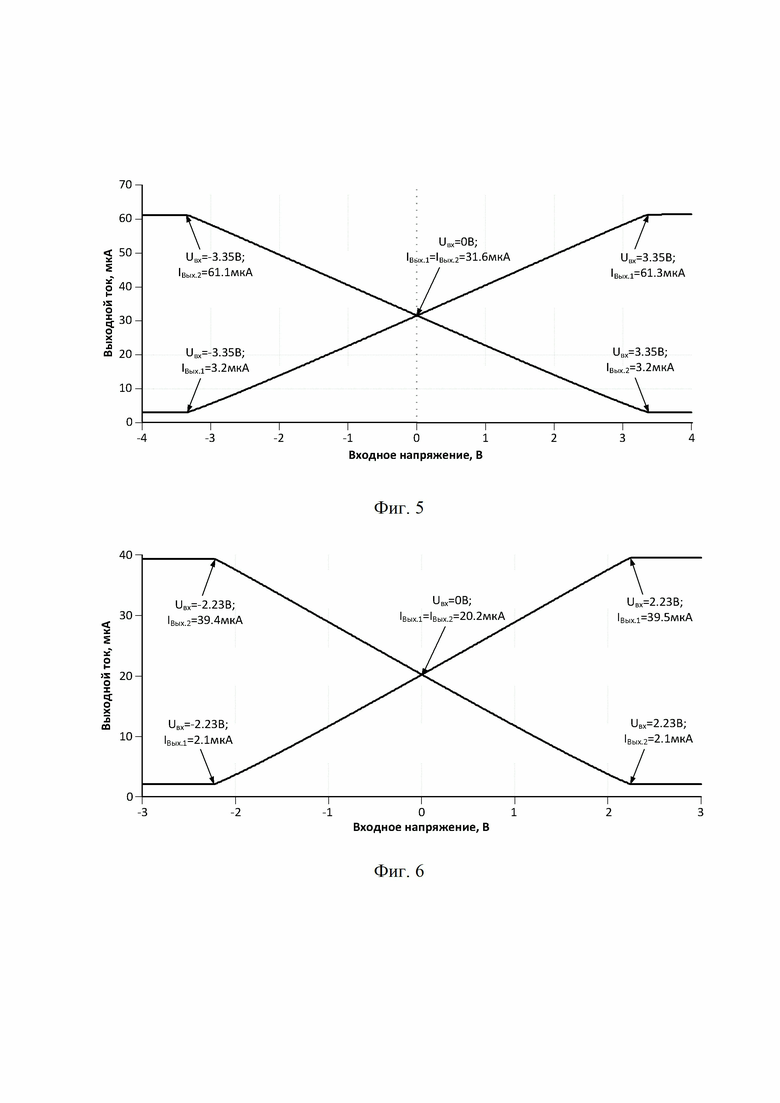

На чертеже фиг. 5 представлена зависимость выходных токов ДК-прототипа фиг. 4 от входного напряжения при температуре 27°С и резисторах R1=R2=50кОм, из которой следует что ДК – прототип при выбранных сопротивлениях резисторов имеет крутизну усиления

Sдк ≈ 8,8 мкА/В.

На чертеже фиг. 6 показана зависимость выходных токов ДК-прототипа фиг. 4 от входного напряжения при отрицательных температурах (-197°С) и резисторах R1=R2=50кОм. Здесь Sдк ≈ 8,52 мкА/В, т.е. рассматриваемая схема характеризуется слабой зависимостью Sдк от температуры.

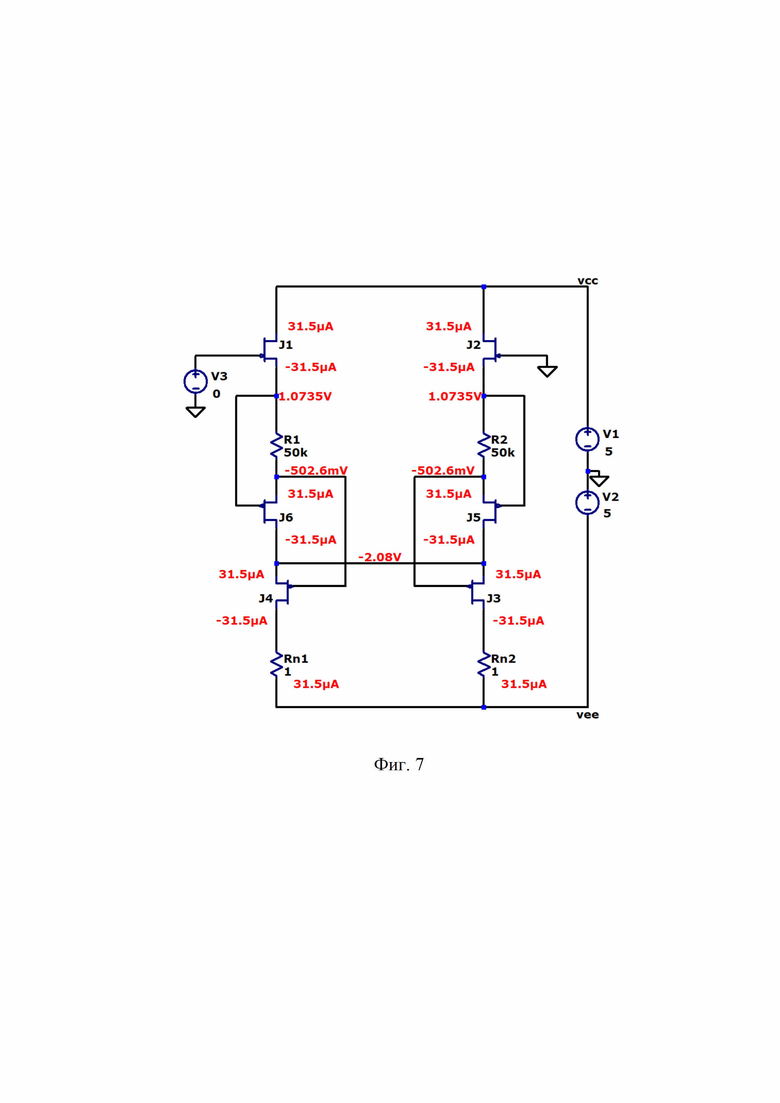

На чертеже фиг. 7 показан статический режим в среде LTSpice заявляемого дифференциального каскада фиг. 2 при 27°С, резисторах R1=R2=50кОм.

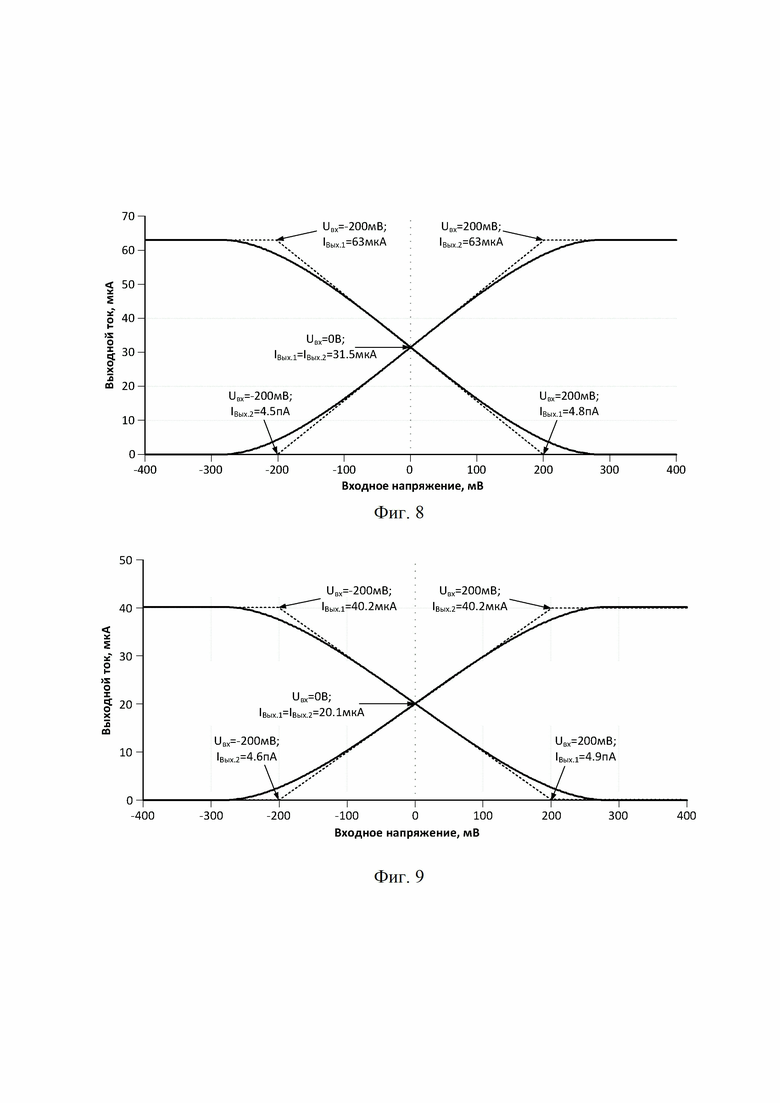

На чертеже фиг. 8 приведена зависимость выходных токов заявляемого ДК фиг. 7 от входного напряжения при температуре 27°С и резисторах R1=R2=50кОм, из которой следует что крутизна усиления ДК Sдк ≈ 150 мкА/В.

На чертеже фиг. 9 приведена зависимость выходных токов заявляемого ДК фиг. 7 от входного напряжения при отрицательных температура (-197°С) и резисторах R1=R2=50кОм. В данном режиме Sдк ≈ 100 мкА/В.

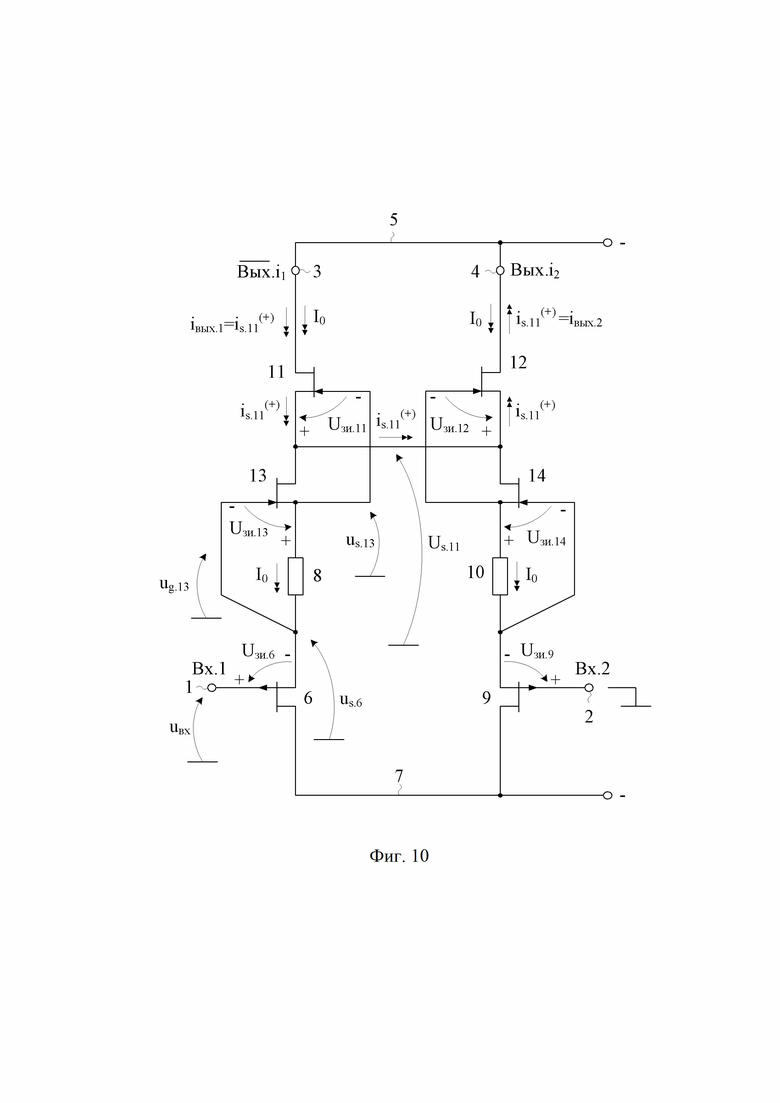

На чертеже фиг. 10 показана схема входного дифференциального каскада с умножителем крутизны усиления (фиг. 2) для случая, когда в качестве первого 6 и второго 9 входных полевых транзисторов используются JFET c p-каналом.

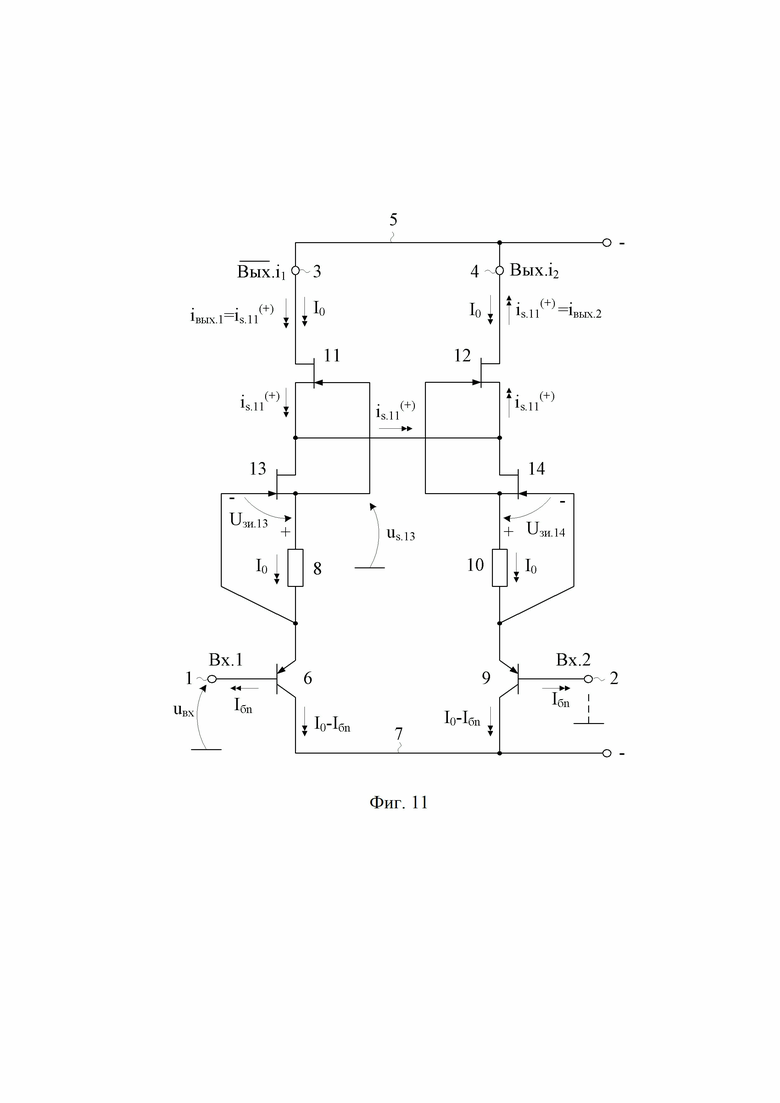

На чертеже фиг. 11 представлен пример применения входного дифференциального каскада фиг. 10 для случая, когда в качестве первого 6 и второго 9 входных транзисторов используются GaAs p-n-p биполярные транзисторы.

Дифференциальный каскад на комплементарных полевых транзисторах фиг. 2 содержит первый 1 и второй 2 входы, первый 3 и второй 4 токовые выходы, согласованные с первой 5 шиной источника питания, первый 6 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток согласован со второй 7 шиной источника питания, исток связан с первым выводом первого 8 вспомогательного резистора, второй 9 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, сток согласован со второй 7 шиной источника питания, исток связан с первым выводом второго 10 вспомогательного резистора, первый 11 выходной полевой транзистор, сток которого подключен к первому 3 токовому выходу устройства, второй 12 выходной полевой транзистор, сток которого подключен ко второму 4 токовому выходу устройства. Исток первого 6 входного полевого транзистора соединен с затвором первого 13 дополнительного полевого транзистора, исток которого соединен с истоком первого 6 входного полевого транзистора через первый 8 вспомогательный резистор и подключен к затвору первого 11 выходного полевого транзистора, сток первого 13 дополнительного полевого транзистора соединен с истоком первого 11 выходного полевого транзистора, исток второго 9 входного полевого транзистора соединен с затвором второго 14 дополнительного полевого транзистора, исток которого соединен с истоком второго 9 входного полевого транзистора через второй 10 вспомогательный резистор и подключен к затвору второго 12 выходного полевого транзистора, сток второго 14 дополнительного полевого транзистора соединен с истоком второго 12 выходного полевого транзистора и связан со стоком первого 13 дополнительного полевого транзистора. В схеме фиг. 2 двухполюсники Rн1 и Rн2 моделируют свойства нагрузки.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, в качестве комплементарных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, в качестве комплементарных полевых транзисторов используются КМОП транзисторы со встроенными p и n каналами [17].

Рассмотрим работу ДК фиг. 2.

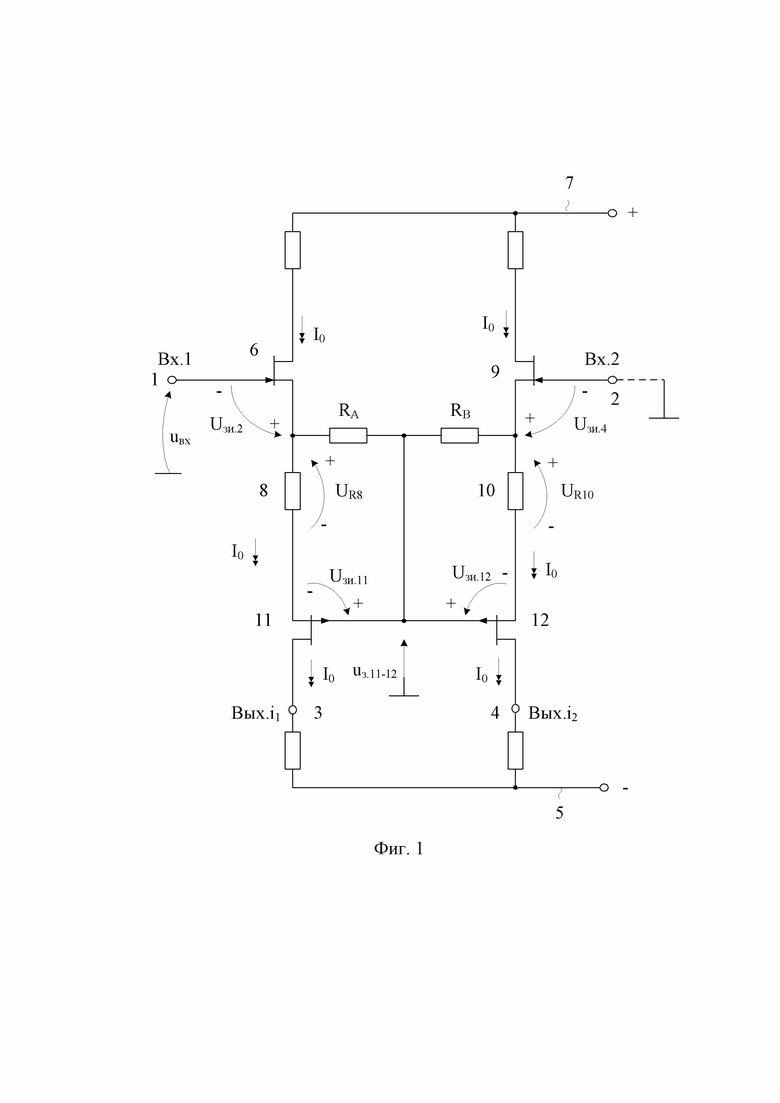

В статическом режиме, например, при подключении первого 1 и второго 2 входов ДК фиг. 2 к общей шине источников питания, статические токи истоков первого 6 и второго 9 входных полевых транзисторов, первого 11 и второго 12 выходных полевых транзисторов, первого 13 и второго 14 дополнительных полевых транзисторов определяются численными значениями идентичных сопротивлений первого 8 и второго 10 вспомогательных резисторов:

, (1)

, (1)

где Iиi – ток истока i-го полевого транзистора (6, 9, 11, 12, 13, 14);

Uзи.i – напряжение затвор-исток первого 13 и второго 14 дополнительных полевых транзисторов в рабочей точке при токе истока, равном заданному значению I0, например 200 мкА;

Ri – сопротивления первого 8 и второго 10 вспомогательных резисторов.

Таким образом, в схеме фиг. 2 за счет выбора идентичными сопротивлений первого 8 и второго 10 вспомогательных резисторов при известных стоко-затворных характеристиках идентичных JFET обеспечивается заданный статический режим по току, в т.ч. заданное постоянное напряжение на истоках первого 11 и второго 12 выходных полевых транзисторов: Us.11=Us.12=Uзи.6-Uзи.13-Uзи.11.

Если на вход 1 подается положительное приращение входного напряжения uвх относительно входа 2, то это вызывает увеличение напряжения на истоке первого 6 входного полевого транзистора (us.6), затворе первого 13 дополнительного полевого транзистора, истоке первого 13 дополнительного полевого транзистора (us.13) и затворе первого 11 выходного полевого транзистора us.13, причем:

us.6 =us.13 ≈ us.11 ≈uвх. (2)

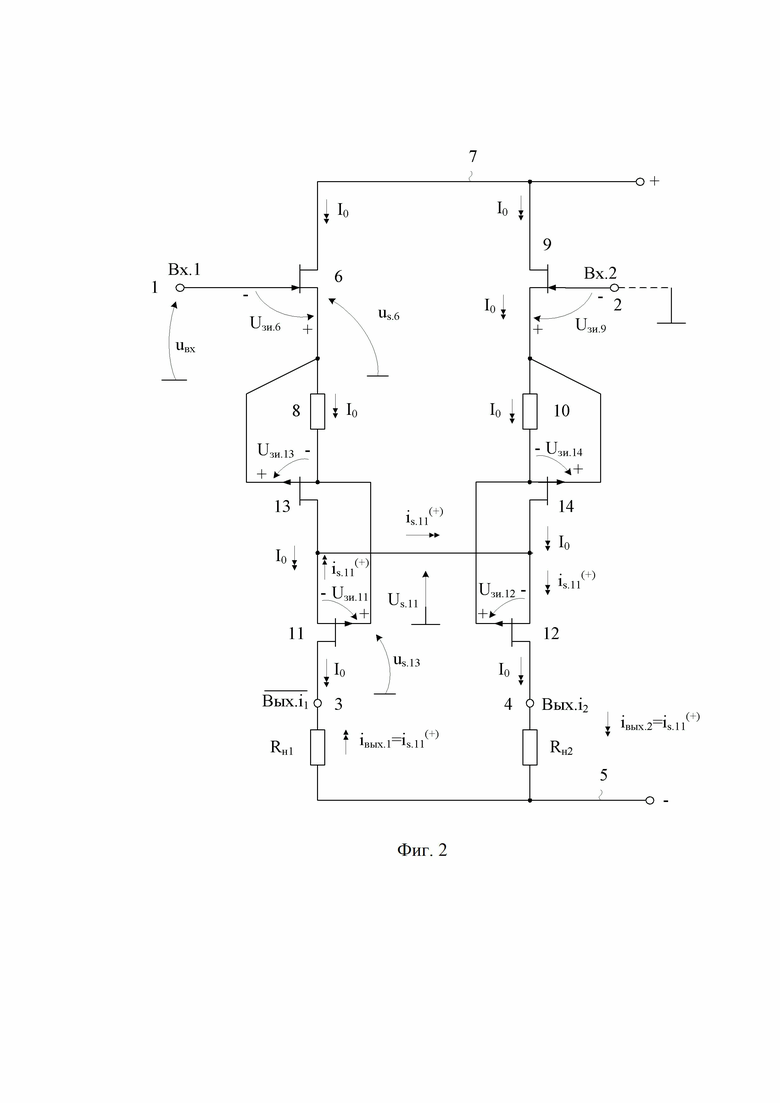

Приращение напряжения на затворе первого 11 выходного полевого транзистора ug.11=us.13 вызывает уменьшение тока стока этого полевого транзистора:

, (3)

, (3)

где S11= S12 – крутизна стоко-затворных характеристик первого 11 и второго 12 полевых выходных транзисторов.

Поэтому сигнал на выходе Вых.i1 (3) инвертируется относительно сигнала uвх на входе 1 устройства. При этом приращение тока is.11(+) передается в цепь истока второго 12 выходного полевого транзистора. Поэтому напряжение на втором 4 токовом выходе устройства совпадает по фазе с напряжением uвх на входе 1 дифференциального каскада.

В частных случаях в качестве полевых транзисторов могут использоваться КМОП транзисторы со встроенным каналом (фиг. 3). При этом КМОП ДК фиг. 3, также как и JFet ДК фиг.2, имеет повышенную крутизну усиления дифференциального сигнала. Данное схемотехническое решение перспективно для построения операционных усилителей, реализуемых с применением КМОП транзисторов со встроенным каналом [17].

В схеме ДК на чертеже фиг. 10, соответствующей п.1 формулы изобретения, в качестве первого 6 и второго 9 входных полевых транзисторов используются JFET с p-каналом.

Следует отметить, что при использовании совмещенных GaAs технологических процессов первый 6 и второй 9 входные транзисторы могут быть выполнены как GaAs p-n-p биполярные транзисторы (см. фиг. 11).

Таким образом, заявляемый ДК имеет существенные преимущества по крутизне усиления в сравнении с ДК-прототипом, что позволяет рекомендовать его для практического использования в аналоговых схемах, содержащих, например, полевые транзисторы, в т.ч. КМОП транзисторы со встроенным каналом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2710296, 2019 г.

2. Авт.св. СССР 537435, 1976 г.

3. Патентная заявка RU 2020134402, 2020 г.

4. Патент US 5.291.149, fig. 3, 1994 г.

5. Патент RU 2679970, fig. 2, 2019 г.

6. Патент RU 2624565, fig. 1, 2016 г.

7. Патент RU 2571399, fig. 2, 2014 г.

8. Авт.св. СССР 437193, 1972 г.

9. Патентная заявка US 2006/01255222, 2006 г.

10. Патент US 4.121.169, fig. 5, fig. 6, 1978 г.

11. Патент US 9.668.045, 2017 г.

12. Патент US 9.888.315, 2018 г.

13. Патент US 9.167.327, 2015 г.

14. Патент EP 0293488, fig. 1, 1988 г.

15. Патент US 5.166.553, fig. 14, 1992 г.

16. Shur, Michael S., “GaAs Devices and Circuits”, Springer Science+Business Media, New York, 1987, 677 p. DOI 10.1007/978-1-4899-1989-2

17. Санчес-Синенсио Эдгар, Аллен Филлип «Электронные схемы с переключаемыми конденсаторами», Издательство «Радио и связь», 1989, с. 548, рис. 8.7.9.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| Дифференциальный каскад на комплементарных полевых транзисторах | 2018 |

|

RU2684473C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННОЙ ТЕМПЕРАТУРНОЙ СТАБИЛЬНОСТЬЮ СТАТИЧЕСКОГО РЕЖИМА | 2020 |

|

RU2746888C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2712416C1 |

| Арсенид-галлиевый дифференциальный каскад с умножителем крутизны усиления | 2022 |

|

RU2789756C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ВХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2721943C1 |

Изобретение относится к области радиотехники. Технический результат: повышение крутизны преобразования входного дифференциального напряжения в выходные дифференциальные токи устройства, повышение коэффициента усиления по напряжению. Для этого предложен дифференциальный каскад на комплементарных полевых транзисторах, который содержит первый (1) и второй (2) входы, первый (3) и второй (4) токовые выходы, согласованные с первой (5) шиной источника питания, первый (6) входной полевой транзистор, вторую (7) шину источника питания, первый (8) вспомогательный резистор, второй (9) входной полевой транзистор, второй (10) вспомогательный резистор, первый (11) выходной полевой транзистор, второй (12) выходной полевой транзистор, первый (13) дополнительный полевой транзистор, второй (14) дополнительный полевой транзистор. 2 з.п. ф-лы, 11 ил.

1. Дифференциальный каскад на комплементарных полевых транзисторах, содержащий первый (1) и второй (2) входы, первый (3) и второй (4) токовые выходы, согласованные с первой (5) шиной источника питания, первый (6) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, сток согласован со второй (7) шиной источника питания, исток связан с первым выводом первого (8) вспомогательного резистора, второй (9) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, сток согласован со второй (7) шиной источника питания, исток связан с первым выводом второго (10) вспомогательного резистора, первый (11) выходной полевой транзистор, сток которого подключен к первому (3) токовому выходу устройства, второй (12) выходной полевой транзистор, сток которого подключен ко второму (4) токовому выходу устройства, отличающийся тем, что исток первого (6) входного полевого транзистора соединен с затвором первого (13) дополнительного полевого транзистора, исток которого соединен с истоком первого (6) входного полевого транзистора через первый (8) вспомогательный резистор и подключен к затвору первого (11) выходного полевого транзистора, сток первого (13) дополнительного полевого транзистора соединен с истоком первого (11) выходного полевого транзистора, исток второго (9) входного полевого транзистора соединен с затвором второго (14) дополнительного полевого транзистора, исток которого соединен с истоком второго (9) входного полевого транзистора через второй (10) вспомогательный резистор и подключен к затвору второго (12) выходного полевого транзистора, сток второго (14) дополнительного полевого транзистора соединен с истоком второго (12) выходного полевого транзистора и связан со стоком первого (13) дополнительного полевого транзистора.

2. Дифференциальный каскад на комплементарных полевых транзисторах по п. 1, отличающийся тем, что в качестве комплементарных полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом.

3. Дифференциальный каскад на комплементарных полевых транзисторах по п. 1, отличающийся тем, что в качестве комплементарных полевых транзисторов используются КМОП-транзисторы со встроенными p и n каналами.

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляемым напряжением ограничения проходной характеристики | 2018 |

|

RU2679970C1 |

| US 5291149 A1, 01.03.1994 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2421892C1 |

Авторы

Даты

2022-12-26—Публикация

2022-09-01—Подача