Изобретение относится к области радиоэлектроники и может быть использовано в схемах различных интегральных операционных усилителей (ОУ) и компараторов аналоговых сигналов с малым статическим токопотреблением, обеспечивающим минимальный саморазогрев кристалла, в т.ч. на SiC, GaN, GaAs широкозонных полупроводниках, работающих при повышенных температурах.

В современной микроэлектронной аппаратуре находят широкое применение дифференциальные каскады (ДК) подкласса dual-input-stage [1-22], которые содержат два параллельно включенных по входам классических ДК на комплементарных полевых [1-2] или биполярных [3-22] транзисторах с соответствующими источниками опорного тока (I1, I2), устанавливающих заданный статический режим входных транзисторов ДК. Такая структура дифференциальных каскадов при их использовании в схемах операционных усилителей не позволяет получить повышенные значения максимальной скорости нарастания выходного напряжения (SR). Это связано с ограничением выходных токов микромощных ДК при сравнительно небольших изменениях входного дифференциального напряжения [23]. Таким образом, значительное количество запатентованных в разных странах мира схемотехнических решений ДК рассматриваемого класса при малом токопотреблении не работают в режиме класса АВ, что отрицательно сказывается на численных значениях SR операционных усилителей. Кроме этого, известные ДК при их практической реализации должны иметь два идентичных источника опорного тока (I1, I2) в общих истоковых цепях каждого из параллельно включенных каскадов, отрицательно влияющих на напряжение смещения нуля ОУ, а также частотные характеристики ОУ, коэффициенты ослабления входного синфазного сигнала и подавления помех по шинам питания из-за наличия паразитных емкостей Ср1, Ср2 (фиг. 1), на которых они построены.

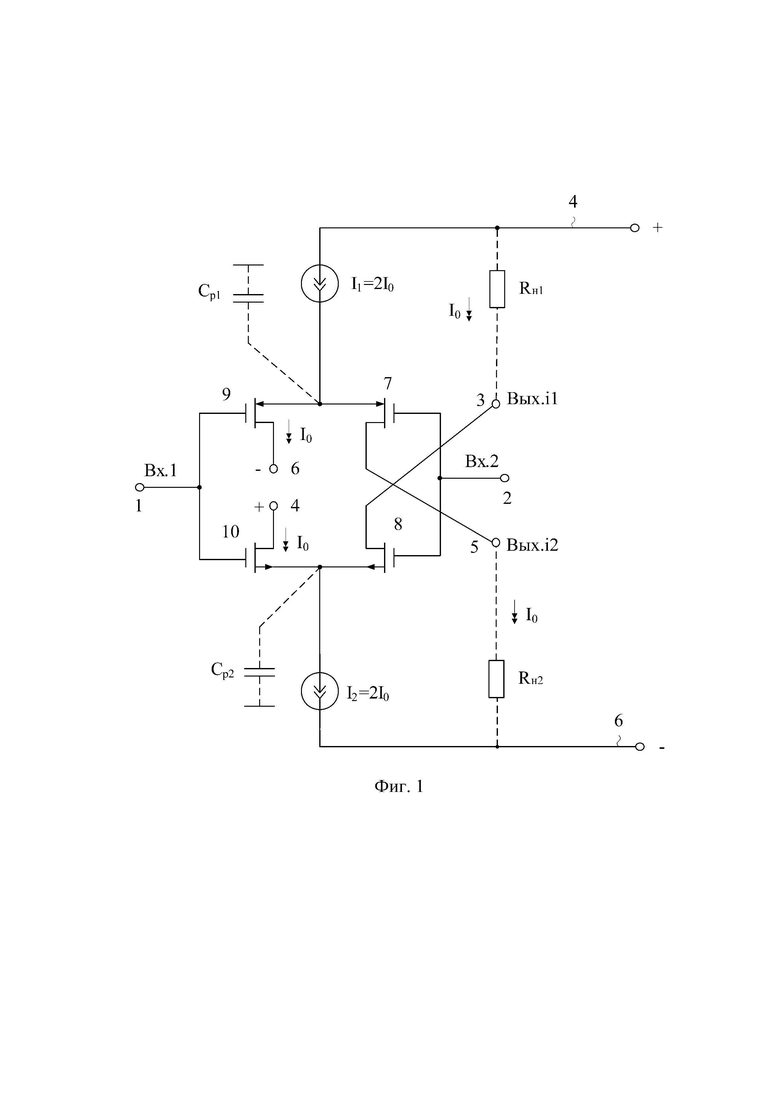

Ближайшим прототипом (фиг. 1) заявляемого устройства является КМОП дифференциальный каскад по патенту US 2006/0125523. Данное схемотехническое решение рассмотрено также в статье [2]. Дифференциальный каскад-прототип содержит (фиг. 1) первый 1 и второй 2 входы устройства, первый 3 токовый выход, согласованный с первой 4 шиной источника питания, второй 5 токовый выход, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен ко второму 5 токовому выходу, второй 8 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен к первому 3 токовому выходу, третий 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток связан со второй 6 шиной источника питания, четвертый 10 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток связан с первой 4 шиной источника питания.

Существенный недостаток известного дифференциального каскада фиг. 1 (при его включении в типовую структуру микромощного операционного усилителя) состоит в том, что в этом случае максимальная скорость нарастания выходного напряжения (SR) имеет небольшие значения (50-80 В/мкс), что обусловлено нелинейным режимом работы входного ДК [23-28]:

SR=2πUгрf1,

где Uгр – напряжение ограничения проходной характеристики входного ДК [25,26,27,23],

f1 – частота единичного усиления скорректированного операционного усилителя (ОУ).

При этом статический ток, потребляемый ДК от источников питания, равен Iq1=4I0, где I0 – заданное разработчиком значение тока истока полевых транзисторов ДК.

Основная задача предполагаемого изобретения состоит в создании более простого дифференциального каскада, который обеспечивает (при уменьшенном в два раза до уровня Iq2=2I0 статическом токопотреблении) более высокие значения выходных токов (работает в режиме класса АВ), что форсирует переходные процессы в его различных схемах включения. В предлагаемой схеме ДК исключаются два источника опорного тока I1=I2 (фиг. 1), отрицательно влияющие на многие статические и динамические параметры классических ДК. Следует отметить, что для минимизации влияния нестабильности напряжений питания и подавления помех по шинам источников питания схемотехнические решения таких двухполюсников могут содержать значительное количество транзисторов [29], что усложняет общую схему ДК. Кроме этого, паразитные емкости Ср1 и Ср2 в общих истоковых цепях ДК на чертеже фиг. 1 существенно ухудшают частотные и динамические параметры известных ДК рассматриваемого класса. Исключение из схемы источников опорного тока снимет проблему влияния паразитных емкостей Ср1, Ср2 этих источников тока на свойства ДК.

Поставленная задача достигается тем, что в дифференциальном каскаде на чертеже фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 токовый выход, согласованный с первой 4 шиной источника питания, второй 5 токовый выход, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен ко второму 5 токовому выходу, второй 8 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен к первому 3 токовому выходу, третий 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток связан со второй 6 шиной источника питания, четвертый 10 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток связан с первой 4 шиной источника питания, предусмотрены новые связи – исток первого 7 входного полевого транзистора соединен с истоком четвертого 10 входного полевого транзистора, а исток второго 8 входного полевого транзистора соединен с истоком третьего 9 входного полевого транзистора.

На фиг. 1 приведена схема КМОП дифференциального каскада – прототипа по патентной заявке US 2006/0125523.

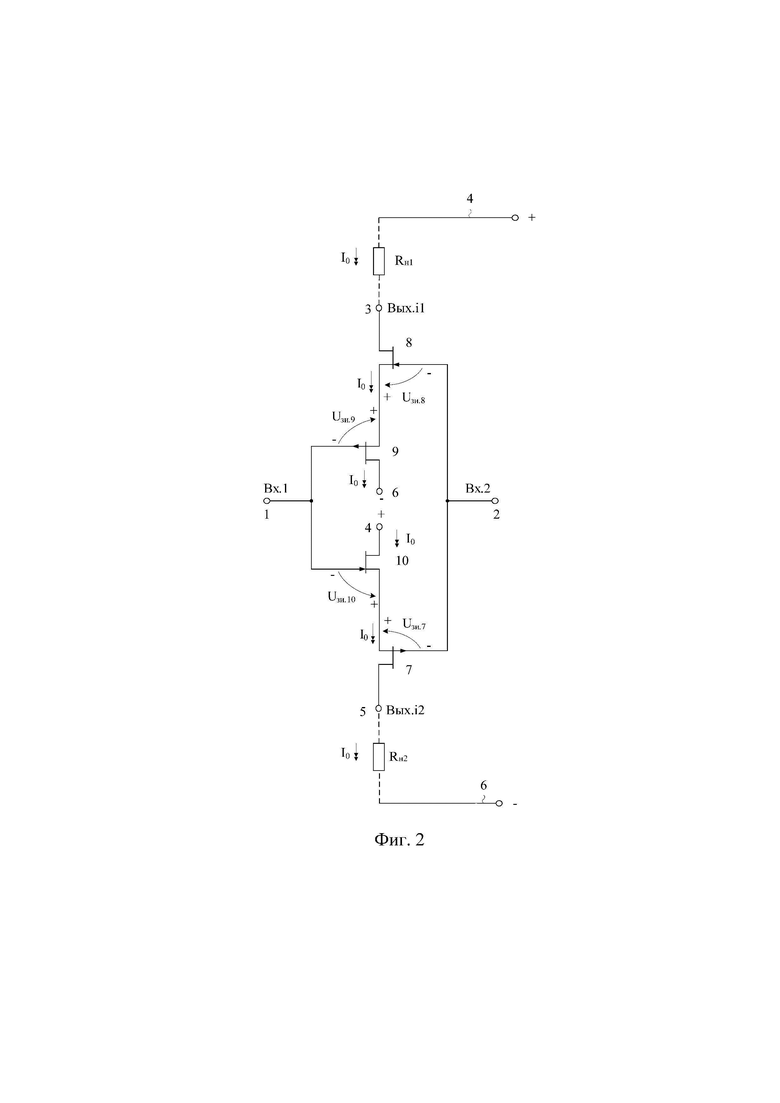

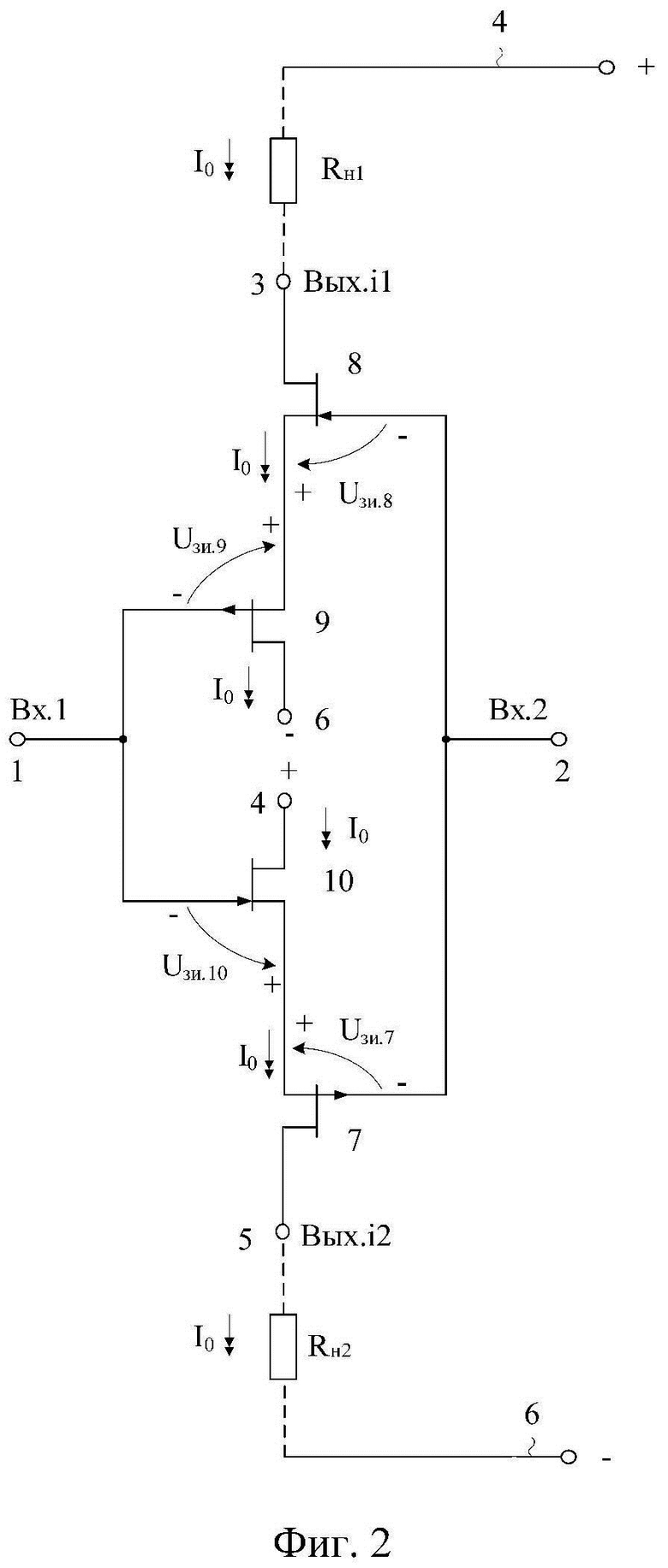

На фиг. 2 показана схема заявляемого дифференциального каскада класса АВ по п. 1 и п. 2 формулы изобретения.

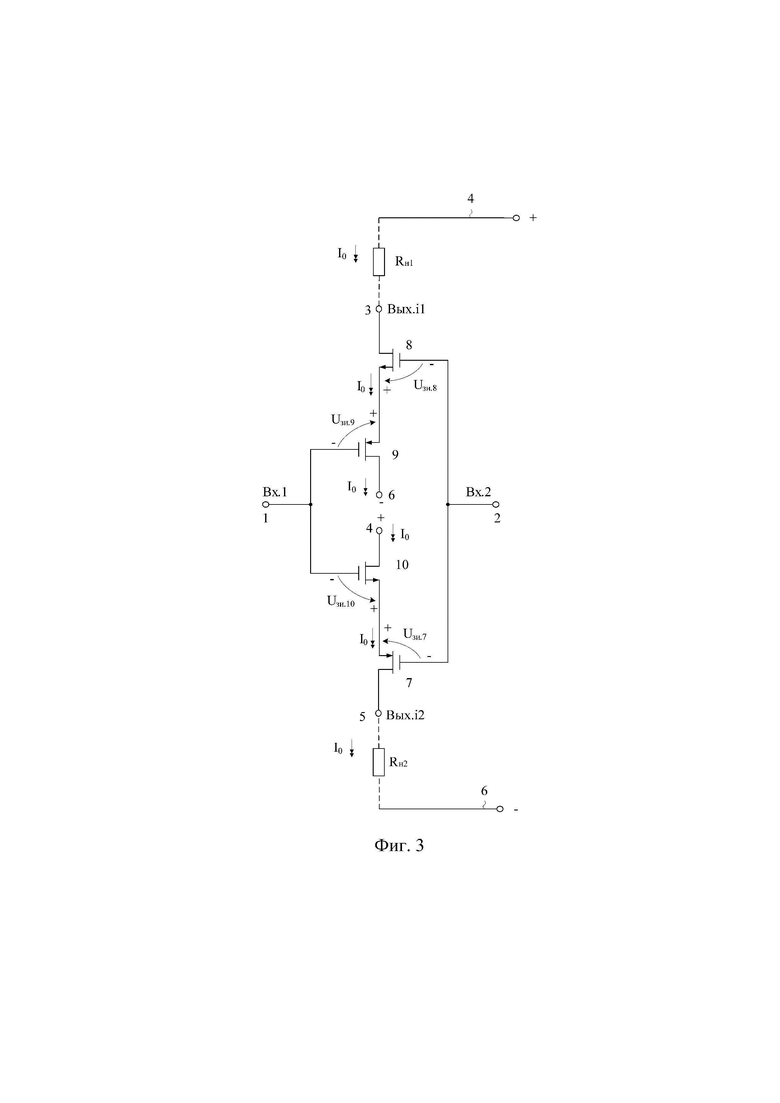

На фиг. 3 приведена схема заявляемого дифференциального каскада класса АВ по п. 3 формулы изобретения.

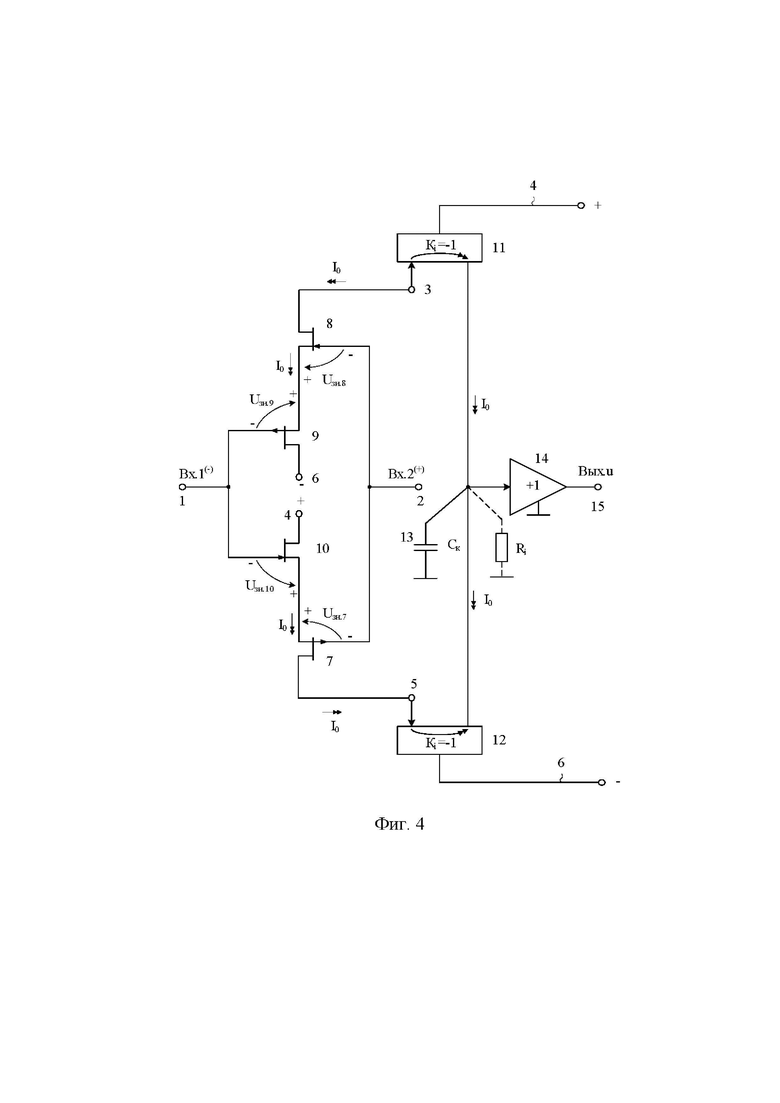

На фиг. 4 представлена схема заявляемого дифференциального каскада класса АВ по п. 4 формулы изобретения.

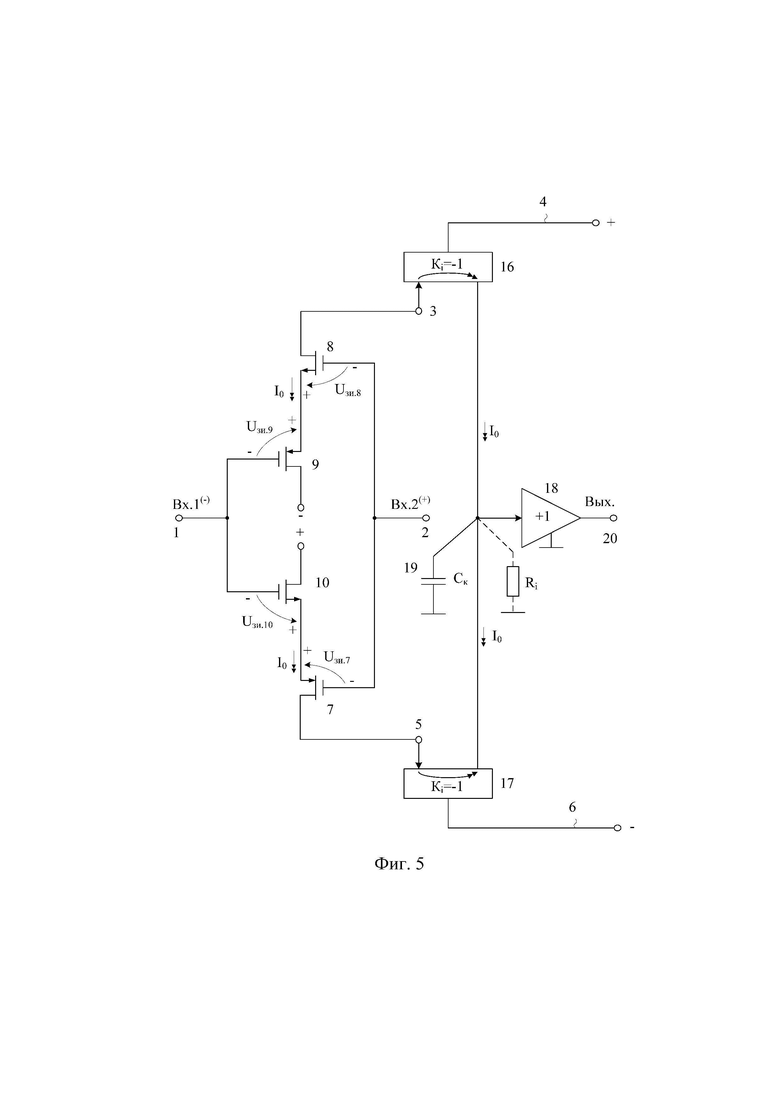

На фиг. 5 приведена схема заявляемого дифференциального каскада класса АВ по п. 5 формулы изобретения.

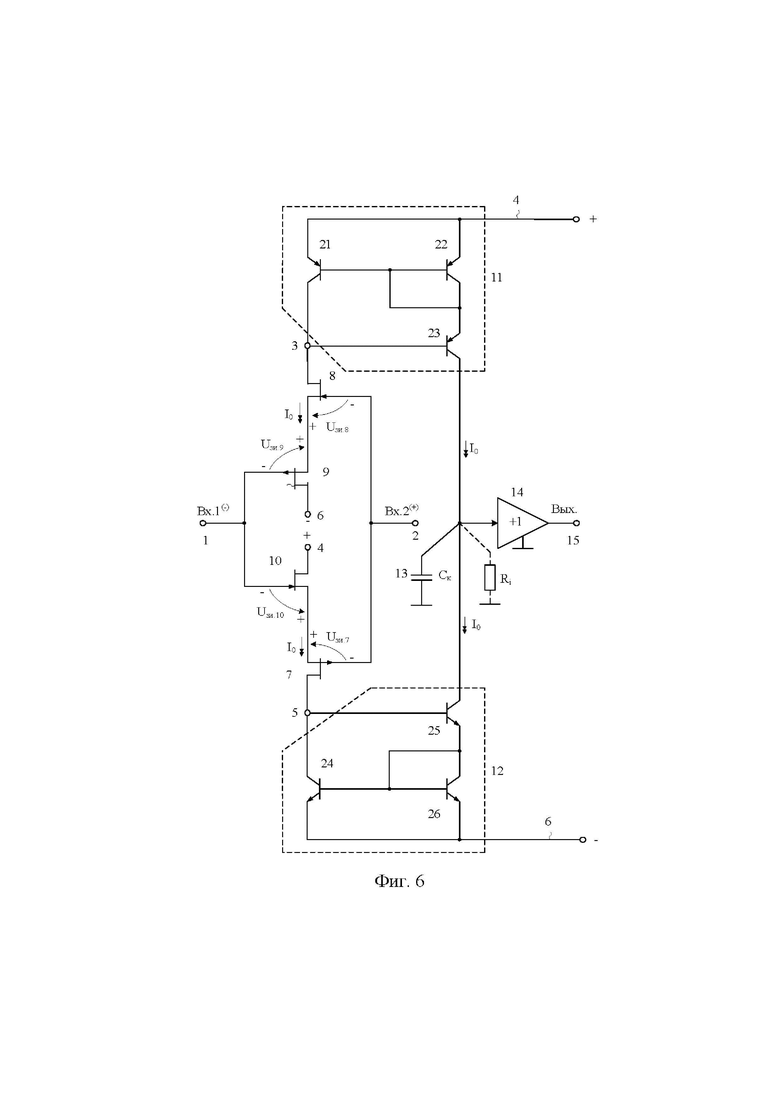

На фиг. 6 показан дифференциальный каскад класса АВ по п. 4 формулы изобретения для случая, когда первое 11 токовое зеркало выполнено на p-n-p биполярных транзисторах 21, 22 и 23, а второе 12 токовое зеркало реализовано на n-p-n биполярных транзисторах 24, 25 и 26. Такое сочетание транзисторов разрешено к применению, например, в рамках технологического процесса PR40 фирмы Intersil Corporation.

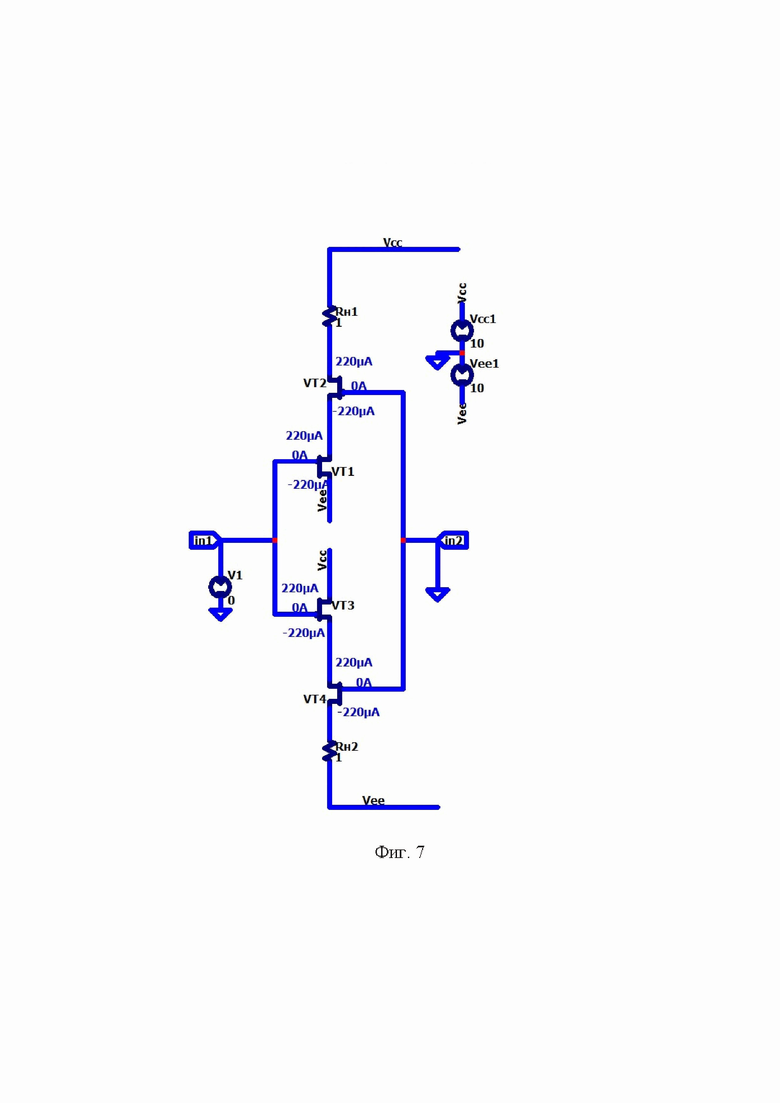

На фиг. 7 представлена схема дифференциального каскада класса АВ (фиг. 2) по п. 2 формулы изобретения в среде LTspice при t= 27°C, ширине канала полевых транзисторов W=25 нм на моделях CJFET_15.04.20 Минского АО «Интеграл».

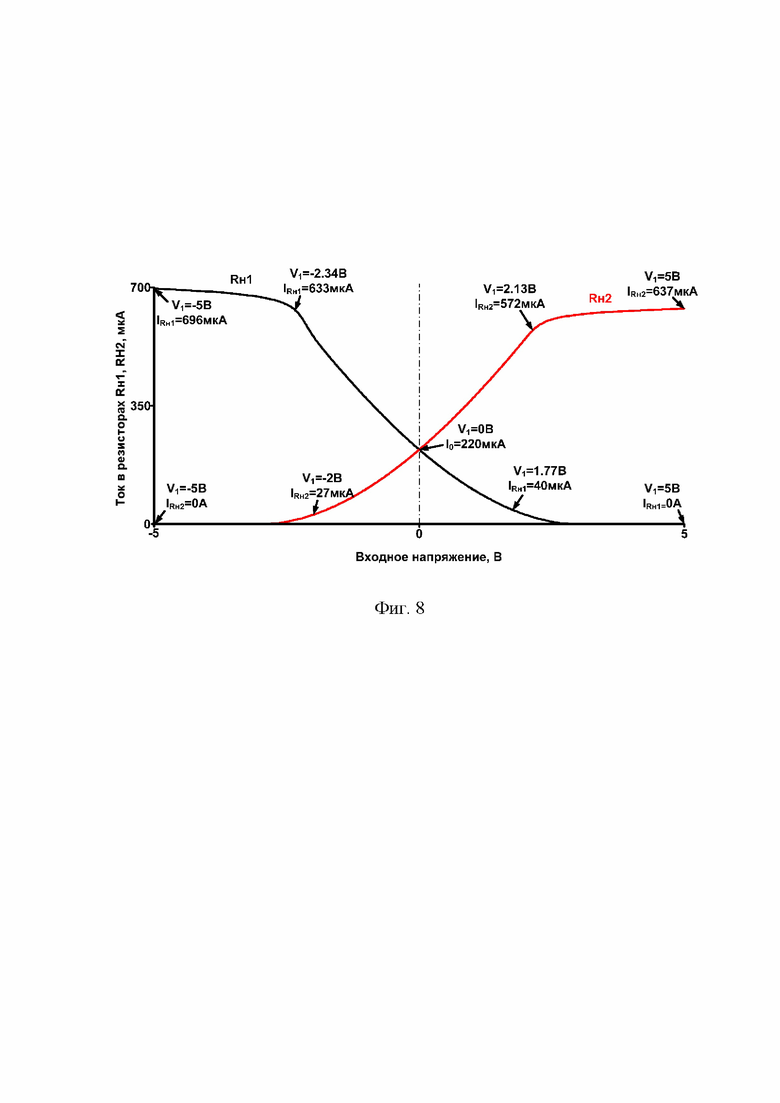

На фиг. 8 приведены проходные характеристики дифференциального каскада класса АВ фиг. 7 по п. 2 формулы изобретения при ширине канала полевых транзисторов W=25 нм. Из этих графиков следует, что при выбранных геометрических размерах JFet (W, L) максимальный выходной ток ДК в 2,9 раз превышает статическое значение тока при Uвх=0, т.е. ДК работает в режиме класса АВ.

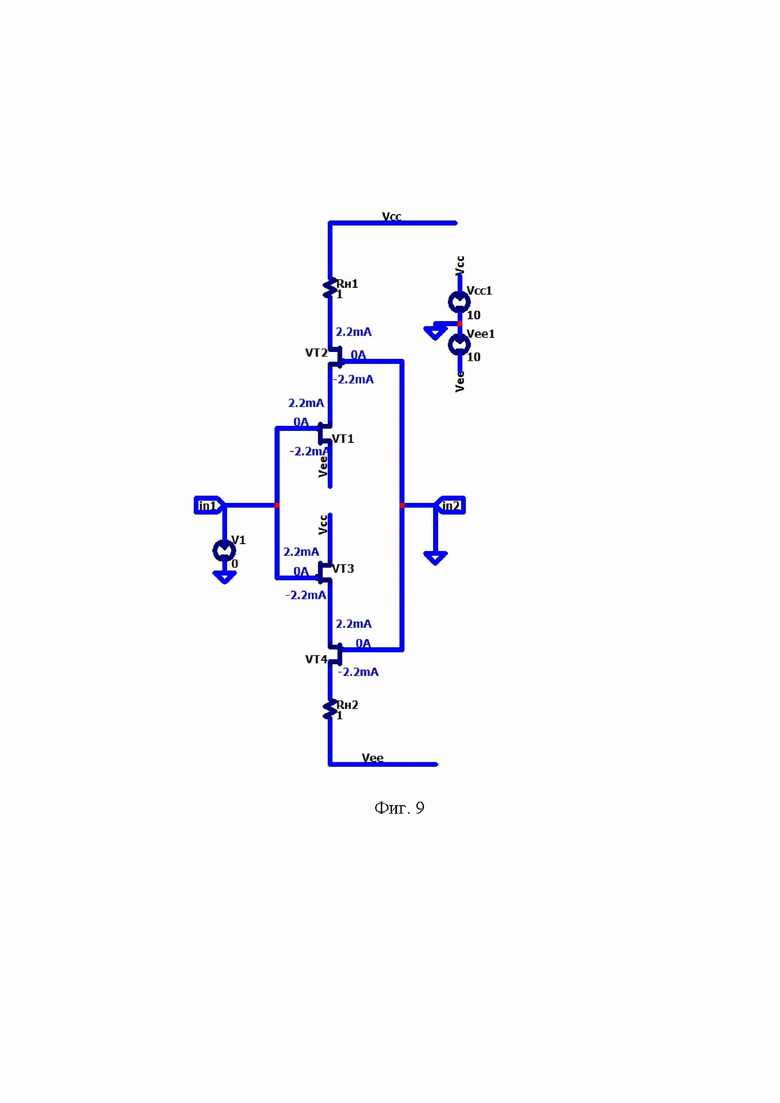

На фиг. 9 показана схема дифференциального каскада класса АВ (фиг. 2) в среде LTspice при t= 27°C, ширине канала полевых транзисторов W=250 нм на моделях CJFET_15.04.20 Минского АО «Интеграл».

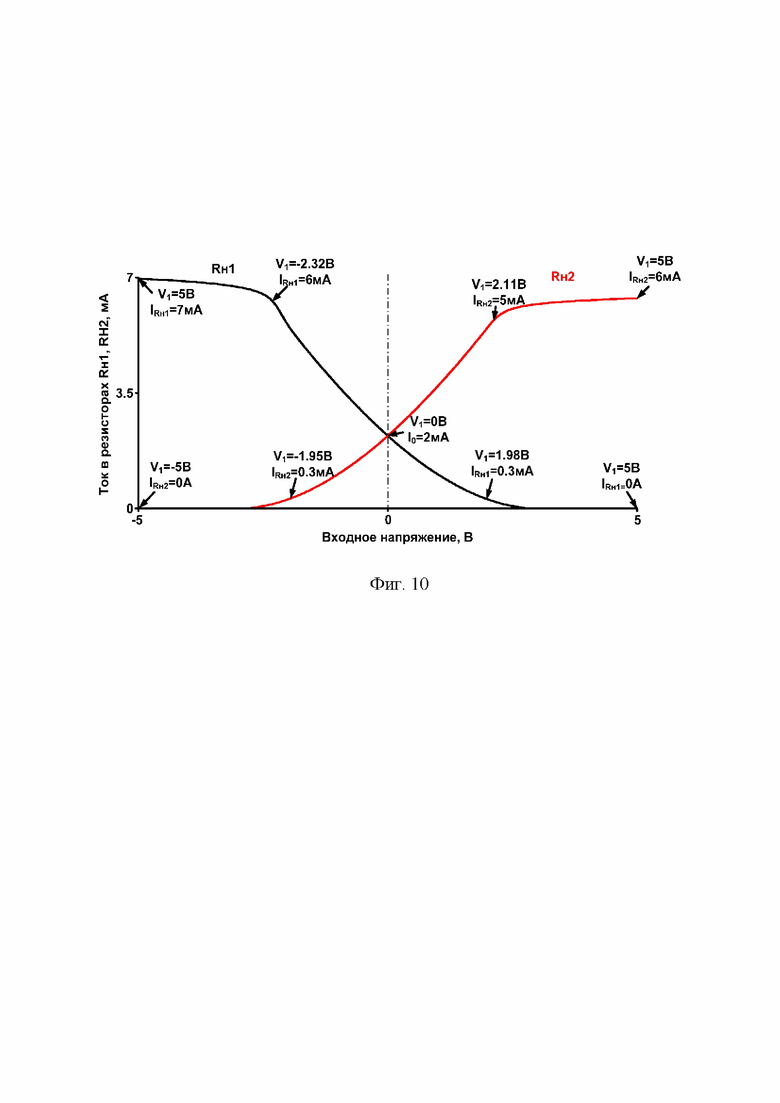

На фиг. 10 представлены проходные характеристики дифференциального каскада класса АВ фиг. 9 при ширине канала W=250 нм. Здесь максимальный выходной ток ДК превышает его статическое значение в 3 раза.

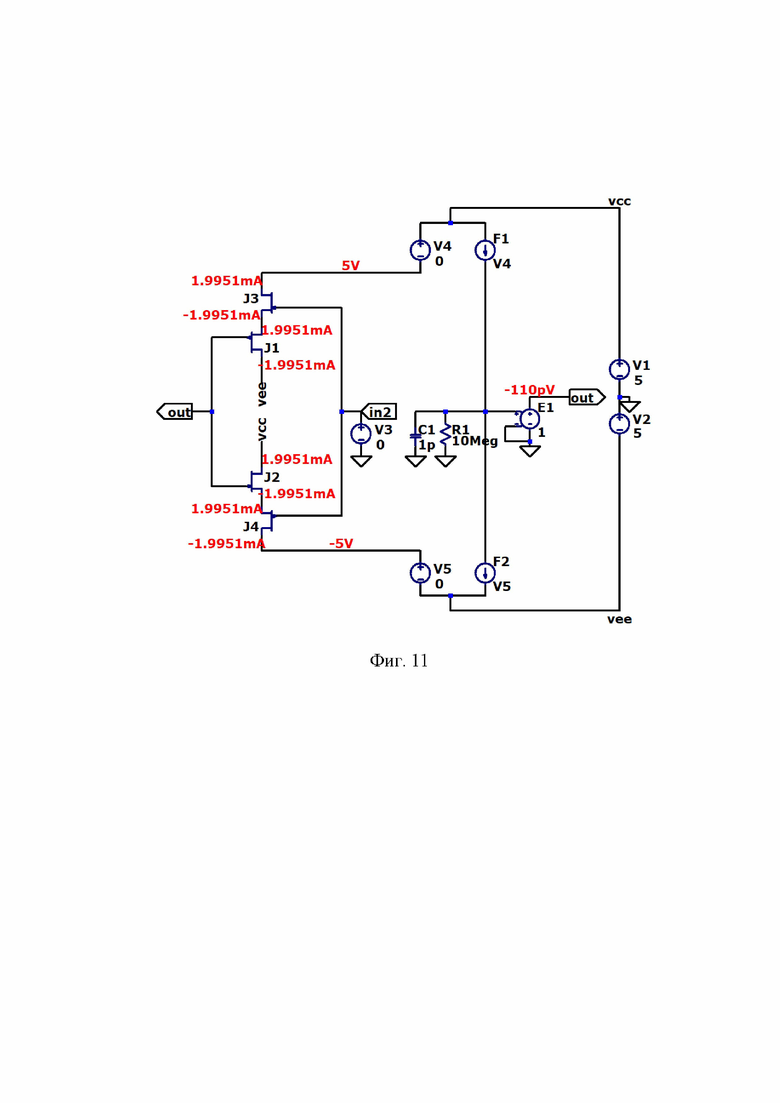

На фиг. 11 приведен статический режим в среде LTSpice дифференциального каскада класса АВ фиг. 4 на моделях CJFET_15.04.20 Минского АО «Интеграл» для ширины канала JFet W=250 нм.

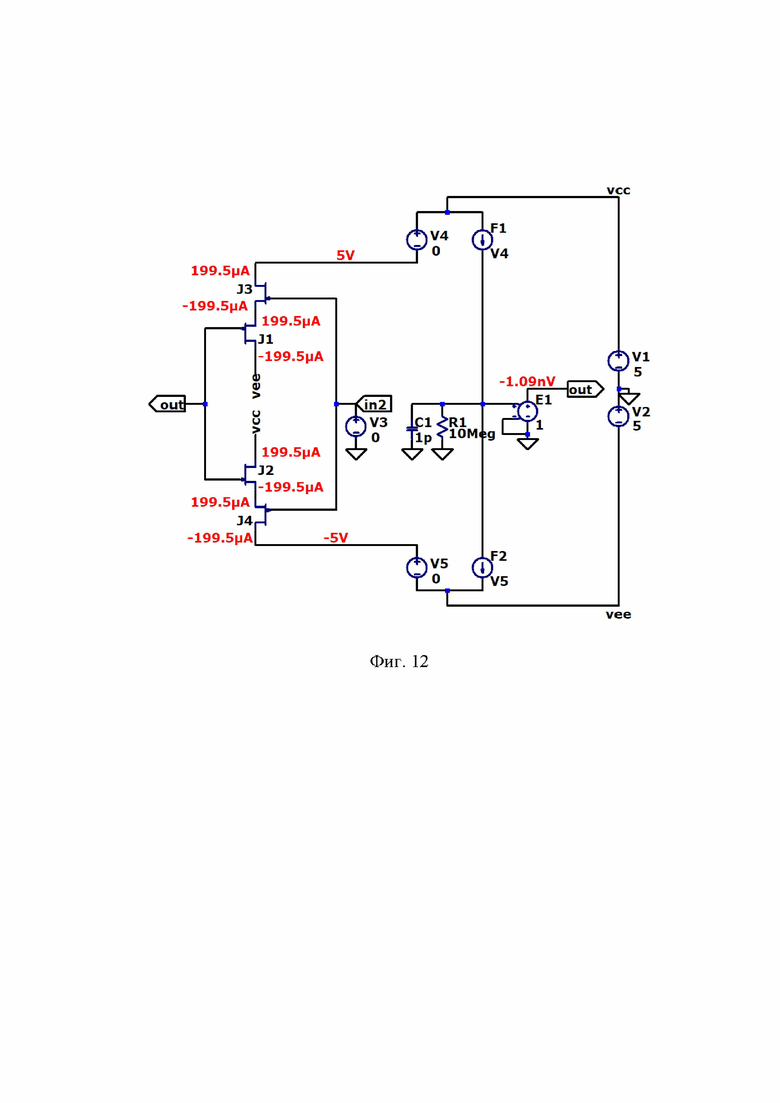

На фиг. 12 показан статический режим в среде LTSpice дифференциального каскада класса АВ фиг. 4 на моделях CJFET_15.04.20 Минского АО «Интеграл» при 27°Си ширине канала JFetW=25 нм.

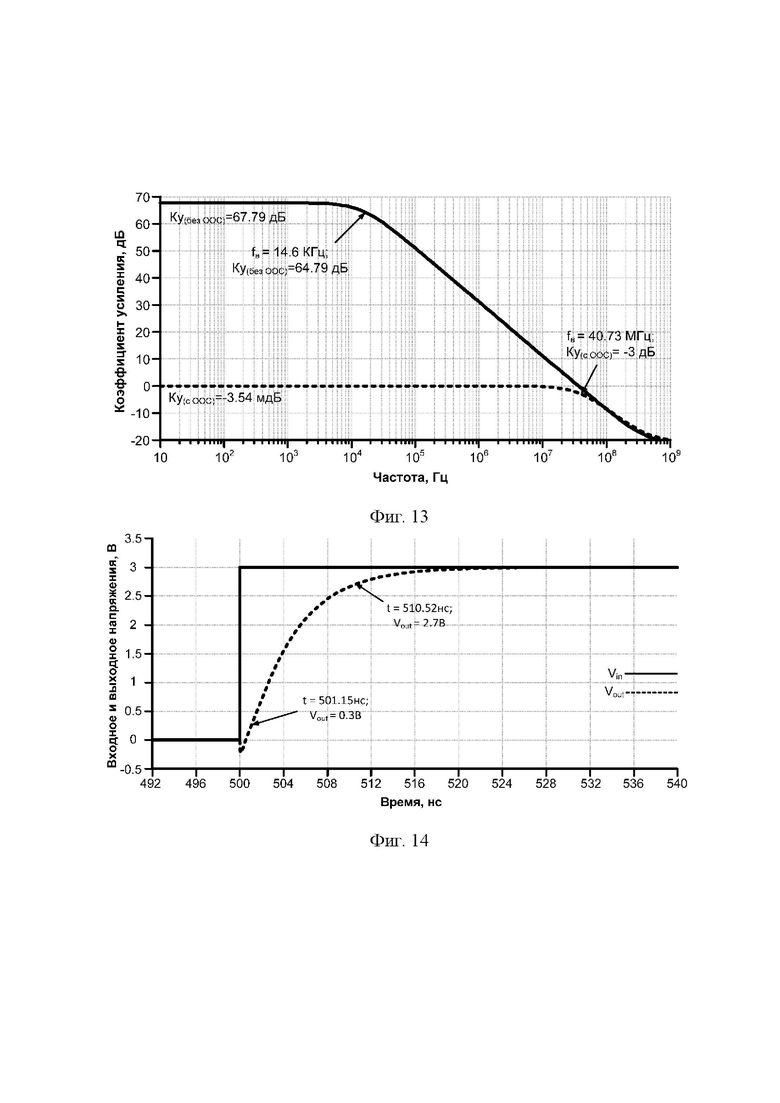

На фиг. 13 представлена логарифмическая амплитудно-частотная характеристика коэффициента усиления по напряжению предлагаемого дифференциального каскада фиг. 12 при корректирующей емкости С1=1пФ и ширине канала JFet W=25 нм.

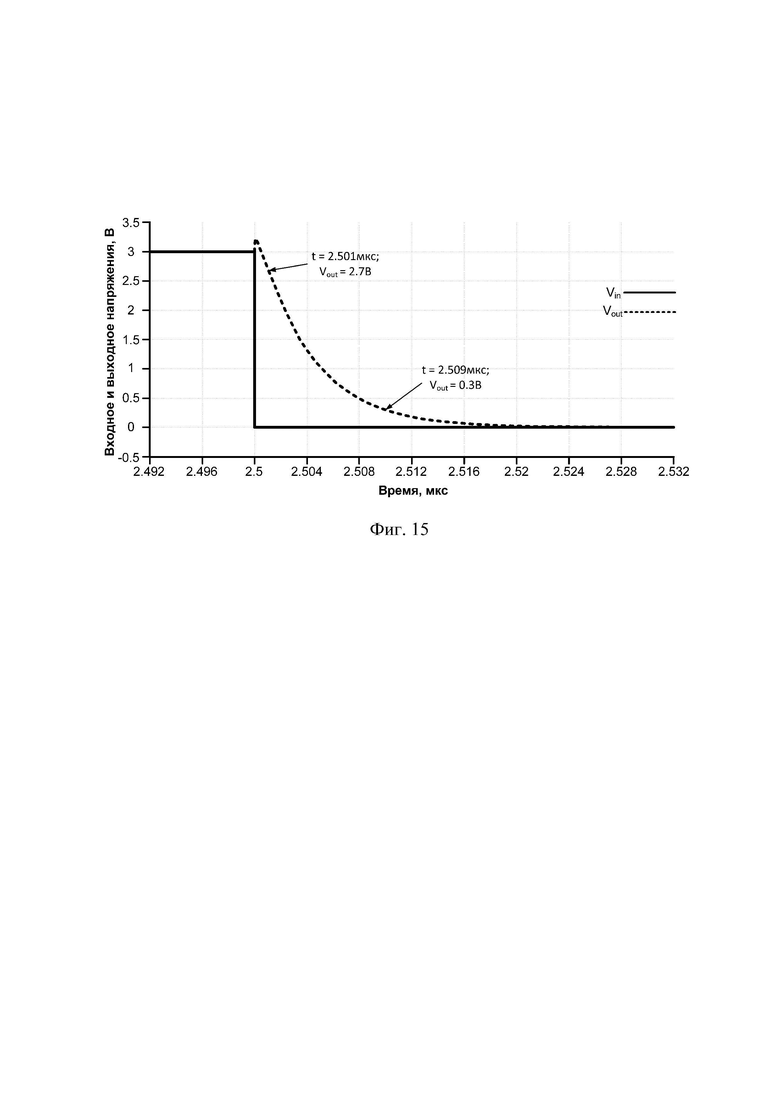

На фиг. 14 показан передний фронт переходного процесса в операционном усилителе фиг. 12 с предлагаемым дифференциальным каскадом класса АВ для ширины канала JFet W=25 нм.

На фиг. 15 приведен задний фронт переходного процесса в операционном усилителе фиг. 12 с предлагаемым дифференциальным каскадом для ширины канала JFet W=25 нм.

Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 токовый выход, согласованный с первой 4 шиной источника питания, второй 5 токовый выход, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен ко второму 5 токовому выходу, второй 8 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен к первому 3 токовому выходу, третий 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток связан со второй 6 шиной источника питания, четвертый 10 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток связан с первой 4 шиной источника питания. Исток первого 7 входного полевого транзистора соединен с истоком четвертого 10 входного полевого транзистора, а исток второго 8 входного полевого транзистора соединен с истоком третьего 9 входного полевого транзистора.

На фиг. 2, в соответствии с п. 2 формулы изобретения, в качестве первого 7 и третьего 9 входных полевых транзисторов, а также в качестве второго 8 и четвертого 10 входных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом (JFet).

На фиг. 3, в соответствии с п. 3 формулы изобретения, в качестве первого 7 и третьего 9 входных полевых транзисторов, а также в качестве второго 8 и четвертого 10 входных полевых транзисторов используются КМОП-транзисторы со встроенными каналами.

На чертеже фиг. 4, в соответствии с п. 4 формулы изобретения, токовый выход 3 дифференциального каскада по п. 2 формулы изобретения связан со входом первого 11 токового зеркала, согласованного с первой 4 шиной источника питания, а второй 5 токовый выход ДК соединен со входом второго 12 токового зеркала, согласованного со второй 6 шиной источника питания, причем выходы первого 11 и второго 12 токовых зеркал объединены и подключены к первому 13 интегрирующему корректирующему конденсатору и входу первого 14 буферного усилителя, выход которого является потенциальным выходом устройства 15.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, токовый выход 3 дифференциального каскада класса АВ по п. 2 формулы изобретения связан со входом третьего 16 токового зеркала, согласованного с первой 4 шиной источника питания, а второй 5 токовый выход ДК соединен со входом четвертого 17 токового зеркала, согласованного со второй 6 шиной источника питания, причем выходы третьего 16 и четвертого 17 токовых зеркал объединены и подключены ко второму 19 интегрирующему корректирующему конденсатору и входу второго 18 буферного усилителя, выход которого является потенциальным выходом устройства 20.

Рассмотрим работу входного ДК на чертеже фиг. 2.

Статические токи стоков всех полевых транзисторов 7, 8, 9, 10 ДК одинаковы и определяются шириной W и длиной L канала этих транзисторов, которые могут изменяться (в допустимых для конкретного технологического процесса пределах). В тех случаях, когда в схеме используются nJFet и pJFEt со строго фиксированными значениями W и L (например, Wn=260 нм, Ln=2,4,6 нм, Wp=50 нм, Lp=2,4,6 нм), то управление численными значениями статических токов ДК можно обеспечить путем параллельного включения нескольких pJFet.

Компьютерное моделирование, результаты которого показаны на чертежах фиг. 8 и фиг. 10 показывает, что при ширине канала JFet 250 нм токи стока JFet идентичны и близки к 2 мА, а при ширине канала JFet в 25 нм статические токи близки к 200 мкА. Таким образом, изменяя геометрические размеры JFet (W, L) или применяя параллельное включение нескольких элементарных JFet с фиксированной шириной и длиной канала, можно изменять статический режим транзисторов ДК фиг. 2 в широких пределах без применения источников опорного тока (как это требуется в ДК-прототипе).Данное свойство предлагаемого дифференциального каскада при его включении в структуру ОУ (фиг. 4) обеспечивает (при идентичных токовых зеркалах 11 и 12) экстремально малые значения систематической составляющей напряжения смещения нуля (менее 1 нВ). При этом общее токопотребление предлагаемого ДК фиг. 2 при одинаковых токах истока полевых транзисторов (Iq2=2I0) в два раза меньше, чем у ДК-прототипа фиг. 1 (Iq1=4I0). Это уменьшает саморазогрев кристалла ОУ на основе ДК фиг. 2, что важно для проектирования высокотемпературных микросхем.

Логарифмическая амплитудно-частотная характеристика с предлагаемым каскадом показана на чертеже фиг. 13. Численные значения разомкнутого коэффициента усиления ОУ зависят от выходных сопротивлений токовых зеркал 11 и 12. В практических схемах (фиг. 4) в качестве токовых зеркал рекомендуется использовать схемы Вильсона [29].

Компьютерное моделирование переходных процессов в ОУ на чертеже фиг. 2 с предлагаемым дифференциальным каскадом по схеме неинвертирующего включения ОУ фиг. 12 представлены на чертежах фиг. 14, фиг. 15. Из данных графиков следует, что максимальная скорость нарастания выходного напряжения для микронных технологических процессов JFet АО «Интеграл» лежит в диапазоне 300-400 В/мкс и зависит от выбранных статических режимов JFet, т.е. от ширины W и длины L канала.

Следует заметить, что существенная особенность предлагаемого входного ДК и рекомендуемой схемы его включения в ОУ состоит в том, что он обеспечивает высокие входные сопротивления как по инвертирующему, так и по неинвертирующему входам ОУ.

Применение в качестве входных полевых транзисторов КМОП-транзисторов со встроенным каналом (фиг. 3, фиг. 5) позволяет выпускать быстродействующие ОУ в рамках ряда популярных КМОП технологических процессов.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ДК-прототипом и рекомендуется для практического использования в схемах высокотемпературных операционных усилителей с малым собственным токопотреблением, что уменьшает саморазогрев кристалла микросхем.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

Схемы дифференциальных каскадов подкласса dual-input-stage на комплементарных КМОП-транзисторах

1. Патентная заявка US 2006/0125523, 2006 г.

2. Minsheng Wang, Terry L. Mayhugh, Jr., Sherif H. K. Embabi, Member, IEEE, and Edgar Sanchez-Sinencio, “ Constant-gm Rail-to-Rail CMOS Op-Amp Input Stage with Overlapped Transition Regions”, IEEE Journal Of Solid-State Circuits, vol. 34, no. 2, February 1999, pp. 148-156.

Схемы дифференциальных каскадов подкласса dual-input-stage на комплементарных биполярных транзисторах

3. Патент US 3.974.455, fig. 7, 1976 г.

4. Патент US 5.374.897, fig. 3, 1994 г.

5. Патент US 5.225.791, fig. 2, 1993 г.

6. Патент US 5.291.149, fig. 3, fig. 8, 1996 г.

7. Патент US6.268.769, fig. 3, 2001 г.

8. Патентная заявка US 2006/0125522, fig. 1, 2006 г.

9. Патент US 4.783.637, fig. 1, 1988 г.

10. Патент US 3.968.451, 1976г.

11. Патент US 4.837.523, 1989г.

12. Патент US 5.515.005, fig. 1, 1996г.

13. Патент US 6.268.769, fig. 3, 2001 г.

14. Патент US 4.636.743, fig. 1, 1987 г.

15. Патент US 5.512.859, fig. 1, 1996г.

16. Патентная заявка JP 2008/235963, 2008 г.

17. Патент JP 7050528, 2022г.

18. Патент US 5.374.897, fig. 3, 1994г.

19. Патент US № 3.968.471, 1976 г.

20. Патент РФ № 611288, 1978 г.

21. Патент US 6.504.419, fig. 2, 2003г.

22. Патент US 5.714.906, fig. 15, 1998г.

Статьи и монографии по теории ОУ

23. N. N. Prokopenko, N. V. Butyrlagin and A. V. Bugakova, "The Comparative Analysis of the Maximum Slew Rate of the Output Voltage BJT and CMOS (SiGe TSMC 0.35µ) Operational Amplifiers," 2018 19th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, Russia, 2018, pp. 1-6, doi: 10.1109/EDM.2018.8435058.

24. Матавкин В. Быстродействующие операционные усилители. – М: Радио и связь, 1989. – С. 100, рис. 6.9, ОУ154УД4.

25. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

26. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография / Н.Н. Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. – 222 с.

27. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. – Шахты: Изд-во ЮРГУЭС, 2006. – 231 с.

28. Операционные усилители для всех / Брюс Картер и Рон Манчини; пер. с англ. А.Н. Рабодзея. – М.: Додэка-XXI, 2011. – 544 с.: ил. – (Серия «Схемотехника). – Доп. тит. л. англ. – ISBN 978-5-94120-242-3, рис. 6.15-рис. 6.17.

29. I.M. Filanovsky, V.V. Ivanov, “Operational Amplifier Speed and Accuracy Improvement: Analog Circuit Design with Structural Methodology,” Kluwer Academic Publishers, New York, Boston, Dordrecht, London, 2004, 194 p.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| Дифференциальный каскад на комплементарных полевых транзисторах | 2018 |

|

RU2684473C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786941C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2712416C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

Изобретение относится к области радиоэлектроники. Технический результат: обеспечение более высоких значений выходных токов. Для этого предложен дифференциальный каскад, который содержит первый (1) и второй (2) входы, первый (3) токовый выход, согласованный с первой (4) шиной источника питания, второй (5) токовый выход, согласованный со второй (6) шиной источника питания, первый (7) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, а сток подключен ко второму (5) токовому выходу, второй (8) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, а сток подключен к первому (3) токовому выходу, третий (9) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток связан со второй (6) шиной источника питания, четвертый (10) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток связан с первой (4) шиной источника питания. Исток первого (7) входного полевого транзистора соединен с истоком четвертого (10) входного полевого транзистора, а исток второго (8) входного полевого транзистора соединен с истоком третьего (9) входного полевого транзистора. 4 з.п. ф-лы, 15 ил.

1. Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания, содержащий первый (1) и второй (2) входы устройства, первый (3) токовый выход, согласованный с первой (4) шиной источника питания, второй (5) токовый выход, согласованный со второй (6) шиной источника питания, первый (7) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, а сток подключен ко второму (5) токовому выходу, второй (8) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, а сток подключен к первому (3) токовому выходу, третий (9) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток связан со второй (6) шиной источника питания, четвертый (10) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток связан с первой (4) шиной источника питания, отличающийся тем, что исток первого (7) входного полевого транзистора соединен с истоком четвертого (10) входного полевого транзистора, а исток второго (8) входного полевого транзистора соединен с истоком третьего (9) входного полевого транзистора.

2. Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания по п.1, отличающийся тем, что в качестве первого (7) и третьего (9) входных полевых транзисторов, а также второго (8) и четвертого (10) входных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

3. Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания по п.1, отличающийся тем, что в качестве первого (7) и третьего (9) входных полевых транзисторов, а также второго (8) и четвертого (10) входных полевых транзисторов используются КМОП-транзисторы со встроенными каналами.

4. Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания по п.2, отличающийся тем, что токовый выход (3) связан со входом первого (11) токового зеркала, согласованного с первой (4) шиной источника питания, второй (5) токовый выход соединен со входом второго (12) токового зеркала, согласованного со второй (6) шиной источника питания, причем выходы первого (11) и второго (12) токовых зеркал объединены и подключены к первому (13) интегрирующему корректирующему конденсатору и входу первого (14) буферного усилителя, выход которого является потенциальным выходом устройства (15).

5. Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания по п.3, отличающийся тем, что токовый выход (3) связан со входом третьего (16) токового зеркала, согласованного с первой (4) шиной источника питания, второй (5) токовый выход соединен со входом четвертого (17) токового зеркала, согласованного со второй (6) шиной источника питания, причем выходы третьего (16) и четвертого (17) токовых зеркал объединены и подключены ко второму (19) интегрирующему корректирующему конденсатору и входу второго (18) буферного усилителя, выход которого является потенциальным выходом устройства (20).

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

Авторы

Даты

2024-07-16—Публикация

2024-02-28—Подача