Изобретение относится к цифровой технике в области обработки информации и может быть использовано в космической отрасли для разрешения конфликтов между отдельными устройствами при обращении к общей памяти в режиме прямого доступа.

Известно устройство разрешения конфликтов, описанное в авторском свидетельстве №1325479 от 24.03.1986 г. «Устройство приоритетного доступа к общей памяти», содержащее два канала для организации обмена двух вычислительных машин с общей памятью (ОП), и содержащее два триггера (1 и 2), запоминающие запросы от двух вычислительных машин, блок очередности выполнения поступающих запросов (3) и логические схемы (4-11) формирования набора сигналов для каждого канала. В указанном устройстве очередность обработки запросов не установлена и определяется очередностью их прихода. Обработка следующего запроса выполняется только после окончания обработки первого. Устройство при запросе по одному из каналов блокирует доступ по другому каналу.

Известно устройство разрешения конфликтов, описанное в патенте на изобретение №2152072 от 02.03.1999 г. - «Устройство переменного приоритета», содержащее n - разрядный регистр запросов (1) для фиксации поступающих запросов, n 1 - разрядных регистров приоритета (20), входы которых являются входами задания кодов приоритета для источников запросов, блок приоритета (3) и набор логических элементов «И» и «ИЛИ» для формирования сигналов, поступающих на информационные входы блока приоритета. Сигналы задания режима 41, 42 и управляющие сигналы 51 … 5n совместно с кодами приоритета на входах 1 - разрядных регистров приоритета предназначены для задания последовательности обработки запросов. Приоритет можно менять в процессе работы. После определения приоритетности устройств заявки также обрабатываются последовательно, т.е. следующая заявка обрабатывается после окончания обработки предыдущей.

Известно устройство разрешения конфликтов, описанное в патенте на изобретение №2320001 от 23.06.2006 г. «Устройство приоритетного обслуживания запросов», содержащее регистр запросов (1), за каждым разрядом которого жестко закреплен приоритет, счетчик тактовых импульсов (10), код которого после дешифрации (11) разрешает прохождение запросов в порядке убывания их приоритетов через ключи (12) на выход устройства. В этом устройстве приоритет задается жестко, и обработка менее приоритетной заявки выполняется после обработки более приоритетной заявки.

Недостатком указанных выше устройств может являться значительная задержка в обработке заявок отдельных устройств, при одновременном обращении к ОП нескольких устройств.

Задача изобретения - разработать устройство, обеспечивающее гарантированный доступ любого из четырех устройств (каналов ввода вывода) к ОП с определенной периодичностью для оперативного приема и выдачи информации абонентам ЦВМ.

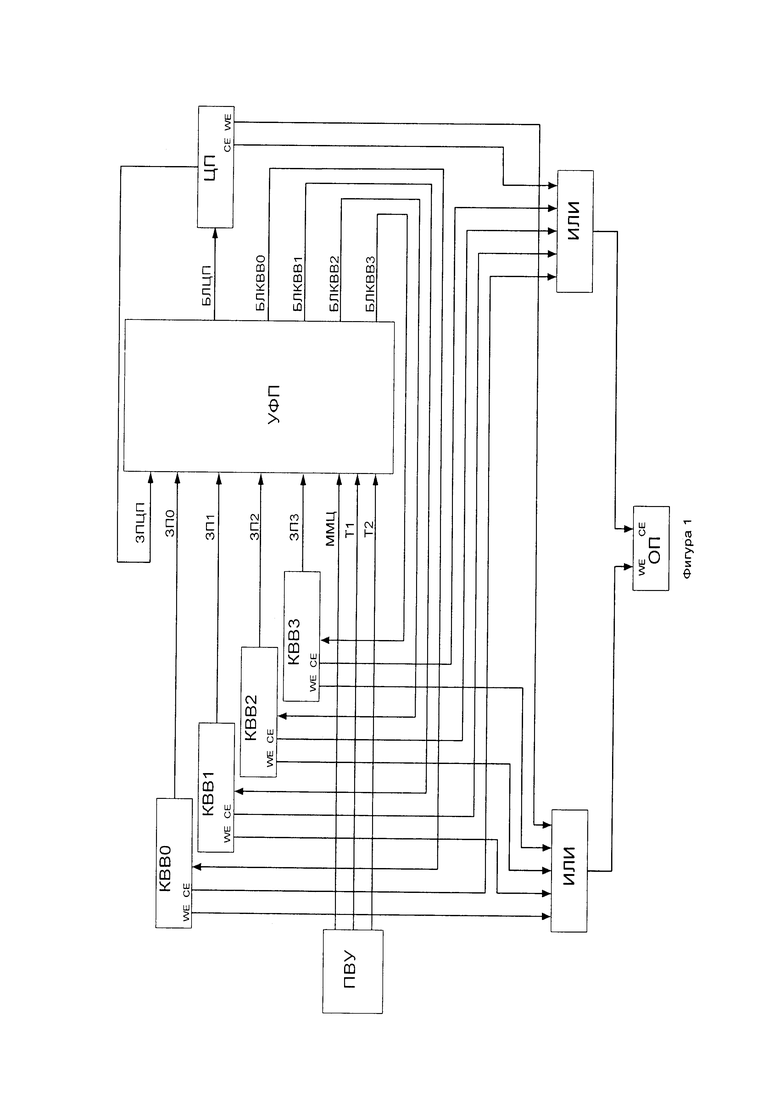

На фигуре 1 показана схема включения УФП в ЭВМ.

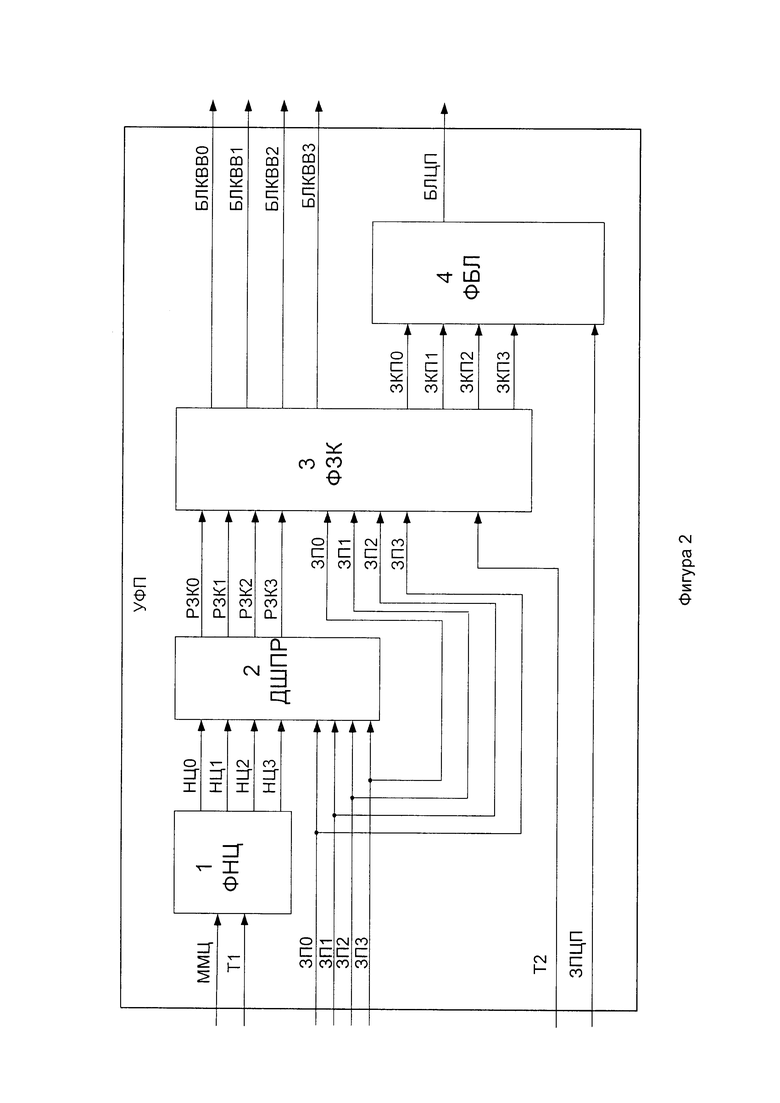

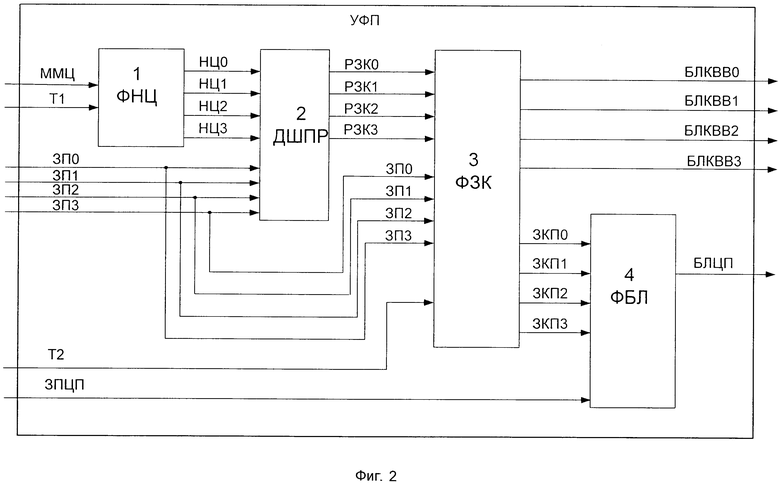

На фигуре 2 представлена структурная схема УФП, включающая в себя следующие элементы:

1 формирователь номеров циклов (ФНЦ);

2 дешифратор приоритетов (ДШПР);

3 формирователь заявок каналов (ФЗК);

4 формирователь блокировок (ФБЛ).

Сигналы согласно фигуре 2:

ММЦ - входная метка машинного цикла;

Т1 - первый тактовый сигнал;

Т2 - второй тактовый сигнал;

ЗП0 - первый входной сигнал;

ЗП1 - второй входной сигнал;

ЗП2 - третий входной сигнал;

ЗП3 - четвертый входной сигнал;

ЗППРО - запрос процессора;

НЦ0 - номер цикла «1»;

НЦ1 - номер цикла «2»

НЦ2 - номер цикла «3»;

НЦ3 - номер цикла «4»;

РЗК0 - первый сигнал разрешения;

РЗК1 - второй сигнал разрешения;

РЗК2 - третий сигнал разрешения;

РЗК3 - четвертый сигнал разрешения;

ЗКП0 - первый сигнал заявки;

ЗКП1 - второй сигнал заявки;

ЗКП2 - третий сигнал заявки;

ЗКП3 - четвертый сигнал заявки;

БЛКВВ0 - первая блокировка сигналов;

БЛКВВ1 - вторая блокировка сигналов;

БЛКВВ2 - третья блокировка сигналов;

БЛКВВ3 - четвертая блокировка сигналов;

БЛПР0 - блокировка запроса процессора.

Сформированные в программном временном устройстве (ПВУ) сигналы ММЦ, Т1 и Т2 поступают на вход УФП. От УФП сигналы ММЦ и Т1 поступают в ФНЦ (1). Сигналы НЦ0-НЦ3 поступают от ФНЦ (1) на ДШПР (2). Сигналы ЗП0-ЗП3, сформированные соответствующими КВВ0-КВВ3, поступают на вход УФП, а от входа УФП поступают на ДШПР (2) и ФЗК (3), причем на ФЗК (3) поступают сигналы РЗК0-РЗК3 от ДШПР (2). Кроме того, на ФЗК (3) поступает сигнал Т2. ФЗК (3) вырабатывает сигналы БЛКВВ0-БЛКВВ3 поступающие на выход УФП. От УФП сигналы БЛКВВ0-БЛКВВ3 поступают на соответствующие им КВВ0-КВВ3. Кроме того ФЗК (3) формирует сигналы ЗКП0-ЗКП3 поступающие на ФБЛ (4) Кроме того от входа УФП на ФБЛ (4) поступает сигнал ЗППРО. От ФБЛ (4) на выход УФП поступает сигнал БЛПРО. От выхода УФП сигнал БЛПРО поступает на процессор. Кроме того, на вход УФП от процессора поступает сигнал ЗППРО. От входа УФП данный сигнал поступает на ФБЛ (4).

Принципы работы устройства.

В состав управляющей электронно-вычислительной машины (ЭВМ) входит несколько устройств: процессор, четыре канала ввода-вывода (КВВ), имеющие прямой доступ к (ОП) и программное - временное устройство (ПВУ), которое обеспечивает синхронизацию процессора и КВВ. При необходимости одновременного обращения к ОП между устройствами возникают конфликтные ситуации.

Формирование ММЦ и тактовых сигналов T1, Т2 в ПВУ не зависит от необходимости обращения процессора или КВВ к ОП.

Сигналы ММЦ определяют длительность машинного цикла ЭВМ.

Сигналы Т1 и Т2 формируются со сдвигом 0,25 мкс.

Устройство формирования приоритетов (УФП) предназначено для разрешения конфликтных ситуаций при обращении к ОП в реальном масштабе времени в составе управляющих ЭВМ.

УФП устанавливает последовательность обращения к ОП от процессора и КВВ при одновременном запросе.

КВВ имеют одинаковый приоритет по отношению друг к другу и более высокий приоритет по отношению к процессору.

Процессор в этой схеме имеет наименьший приоритет, поскольку выполняет обработку информации, полученной КВВ от внешних датчиков, и формирует информацию для выдачи с помощью КВВ в управляющие органы системы.

Взаимодействие с внешними абонентами выполняется в строго определенное время вычислительного процесса. Обмен с внешними абонентами выполняют каналы ввода-вывода, причем каждый из четырех КВВ имеет свой набор абонентов. В этой связи трудно определить приоритетность КВВ между собой при необходимости доступа к ОП.

УФП обеспечивает формирование сигналов WE и СЕ, необходимых для обращения к ОП только от одного из устройств.

Процессор, при выполнении операции связанной с обращением в ОП, формирует сигнал ЗППРО - входной сигнал запроса на разрешение работы с ОП от процессора.

Если при наличии сигнала ЗППРО нет сигналов ЗКП0-ЗКП3 - входных сигналов запроса на разрешение работы с ОП от КВВ0-КВВ3, то процессор с помощью внутренних тактовых сигналов СП1-СП4 - формирует сигналы обращения к ОП (WE и СЕ).

Если одновременно с сигналом ЗППРО присутствует сигнал заявки на ОП хотя бы одного КВВ (ЗКП0-ЗКП3), то в блоке ФБЛ (4) формируется сигнал БЛПРО, который приводит к блокировке внутренних тактовых сигналов процессора (СП1-СП4) в части обращения к ОП и он переходит в режим СТОП - приостанавливает выполнение операций, связанных с обращением в ОП. Сигналы WE и СЕ не формируются.

Если процессор выполняет операции не связанные с обращением в ОП, то независимо от наличия, либо отсутствия сигналов ЗКП0-ЗКП3 выполнение программы продолжается.

При разрешении конфликтов между КВВ в УФП предусмотрен следующий принцип: каждый КВВ может гарантированно обратиться к ОП в «своем» цикле в зависимости от номера КВВ.

Для реализации этого время между метками машинного цикла делится на циклы работы КВВ, длительностью 0,5 мкс, последовательно следующие друг за другом.

Каждый цикл от 0 до 3 принадлежит КВВ с соответствующим номером. В этом цикле разрешается обращение к ОП данного КВВ, если это необходимо.

В блоке ФНЦ (1) формируются сигналы НЦ0-НЦ3 и поступают на блок ДШПР (2).

При необходимости обращения в ОП каждый КВВ формирует сигналы ЗП0-ЗП3, которые также поступают на блок ДШПР (2).

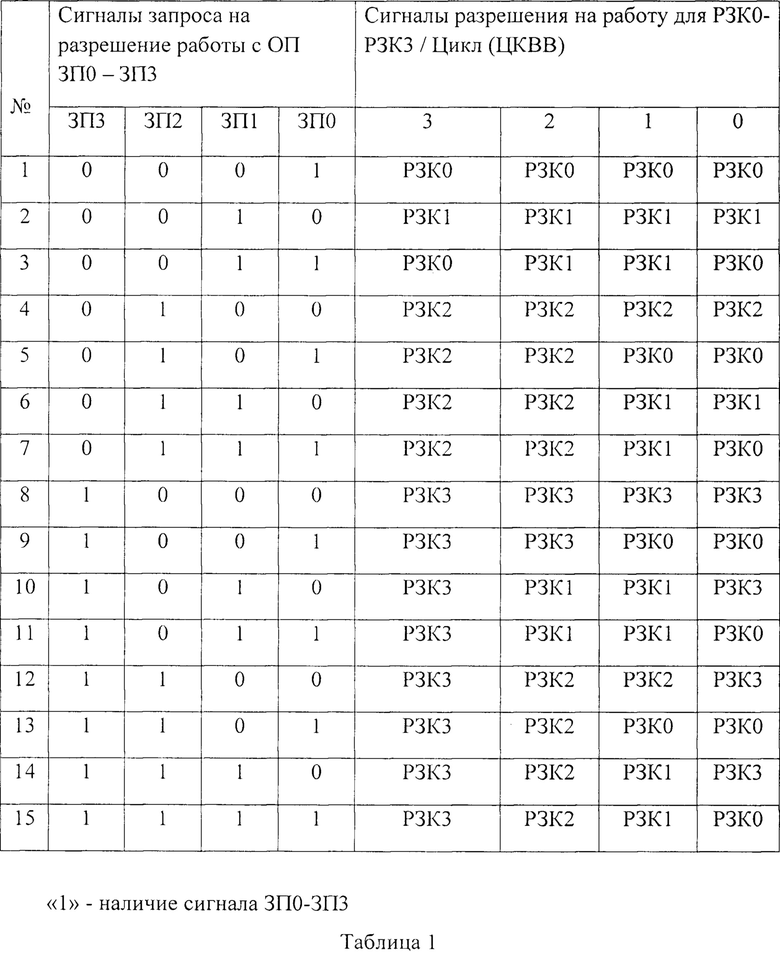

В блоке ДШПР (2) формируются сигналы РЗК0, РЗК1, РЗК2 и РЗК3 - сигналы разрешения на работу с ОП для КВВ0-КВВ3 в зависимости от НЦ0-НЦ3 - номер цикла «0-3» обращения к ОП и от наличия или отсутствия сигналов ЗП0-ЗП3 - входной сигнал запроса на разрешение работы с ОП от КВВ0-КВВ3. Алгоритм формирования сигналов РЗК0-РЗК3 представлен в таблице 1.

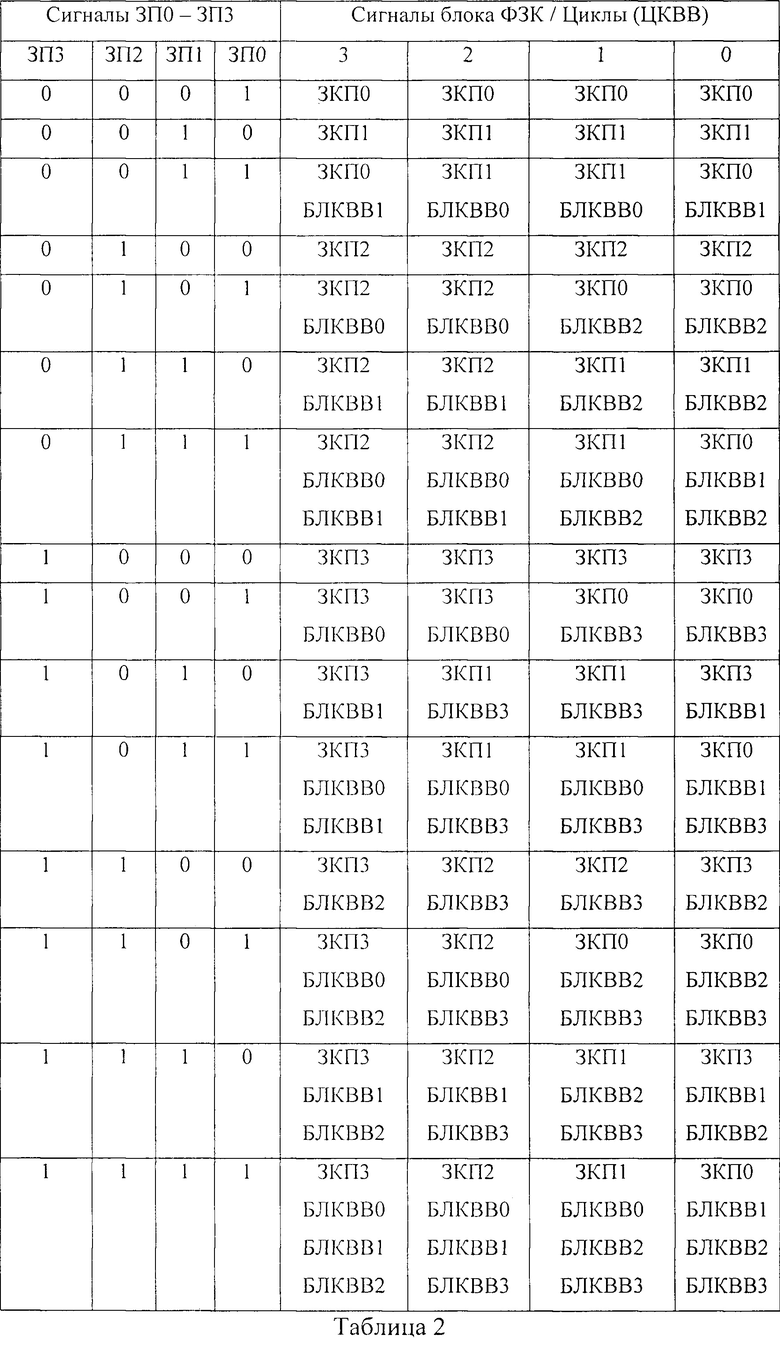

Сигналы РЗК0-РЗК3 поступают на блок ФЗК (3) и в зависимости от наличия или отсутствия сигналов ЗП0-ЗП3 в блоке ФЗК (3) формируются сигналы ЗКП0-ЗКП3 - сигнал заявки на ОП от КВВ0-КВВ3 и БЛКВВ0-БЛКВВ3 - блокировка внутренних тактовых сигналов КВВ0-КВ3 (С1-С4) в части обращения к ОП в соответствии с таблицей 2.

Сигналы БЛКВВ0-БЛКВВ3 вызывают блокировку внутренних тактовых сигналов СК1-СК4 в соответствующем КВВ, и останов КВВ на время ≤1,5 мкс в части обращения к ОП. Сигналы WE и СЕ формируются только в том КВВ, которому разрешено обращение к ОП.

Обмен с абонентами не приостанавливается, циклограмма обмена не нарушается.

При необходимости записи или чтении более одного информационного слова обращение к ОП каждого КВВ может происходить с перерывом на время обращения соседних КВВ. При этом каждый КВВ гарантированно обратится к ОП не реже, чем один раз в 2 мкс.

Максимальное количество информационных слов, которые необходимо записать или прочитать из ОП при одном сеансе обмена с ОП, равно трем. Поэтому максимальное время, за которое будет выполнен один сеанс обращения к ОП, равно 6 (0,5*3*4) мкс.

Техническим результатом является создание устройства формирования приоритетов, включение которого в управляющую машину позволит повысить скорость обработки данных при одновременном обращении к ОП нескольких устройств.

Таким образом заявлено устройство формирования приоритетов, содержащее дешифратор приоритетов (2), в который введены формирователь заявок каналов (3), формирователь блокировок (4) и формирователь номеров циклов (1), на который поступают сигналы входная метка машинного цикла и первый тактовый сигнал, при этом второй тактовый сигнал поступает на формирователь заявок каналов; сигналы номеров циклов «1», «2», «3» и «4» поступают от формирователя номеров циклов на дешифратор приоритетов, а первый, второй, третий и четвертый входные сигналы, сформированные соответствующими каналами ввода-вывода, поступают на дешифратор приоритетов и формирователь заявок каналов, причем на формирователь заявок каналов так же поступают первый, второй, третий и четвертый сигналы разрешения от дешифратора приоритетов, а формирователь заявок каналов вырабатывает сигналы первая, вторая, третья и четвертая блокировка сигналов поступающие на выход устройства, кроме того формирователь заявок каналов формирует первый, второй, третий и четвертый сигнал заявки поступающие на формирователь блокировок, который принимает сигнал запрос процессора и генерирует сигнал блокировка процессора поступающий на выход устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1989 |

|

SU1741132A1 |

| Многоканальное устройство приоритета | 1981 |

|

SU966698A1 |

| Устройство для обслуживания запросов | 1978 |

|

SU728128A1 |

| Устройство для обслуживания запросов | 1986 |

|

SU1388865A2 |

| Устройство для обмена информацией между процессором и абонентами | 1987 |

|

SU1444792A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| Устройство для обмена информацией между магистралью параллельного интерфейса и последовательным каналом | 1986 |

|

SU1444788A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

Изобретение относится к области обработки информации. Техническим результатом является создание устройства формирования приоритетов, включение которого в управляющую машину позволит повысить скорость обработки данных при одновременном обращении к общей памяти (ОП) нескольких устройств. Для этого в состав управляющей электронно-вычислительной машины (ЭВМ) входит несколько устройств: процессор, четыре канала ввода-вывода (КВВ), имеющие прямой доступ к ОП, и программно-временное устройство (ПВУ). Устройство формирования приоритетов (УФП) предназначено для разрешения конфликтных ситуаций при обращении к ОП. УФП устанавливает последовательность обращения к ОП от процессора и КВВ при одновременном запросе. КВВ имеют одинаковый приоритет по отношению друг к другу и более высокий приоритет по отношению к процессору. Процессор выполняет обработку информации, полученной КВВ от внешних датчиков, и формирует информацию для выдачи с помощью КВВ в управляющие органы системы. Обмен с внешними абонентами выполняют каналы ввода-вывода, причем каждый из четырех КВВ имеет свой набор абонентов. 2 ил., 2 табл.

Устройство формирования приоритетов, содержащее дешифратор приоритетов, отличающееся тем, что введены формирователь заявок каналов, формирователь блокировок и формирователь номеров циклов, на который поступают сигналы входная метка машинного цикла и первый тактовый сигнал, при этом второй тактовый сигнал поступает на формирователь заявок каналов; сигналы номеров циклов «1», «2», «3» и «4» поступают от формирователя номеров циклов на дешифратор приоритетов, а первый, второй, третий и четвертый входные сигналы, сформированные соответствующими каналами ввода-вывода, поступают на дешифратор приоритетов и формирователь заявок каналов, причем на формирователь заявок каналов так же поступают первый, второй, третий и четвертый сигналы разрешения от дешифратора приоритетов, а формирователь заявок каналов вырабатывает сигналы первая, вторая, третья и четвертая блокировка сигналов, поступающие на выход устройства, кроме того, формирователь заявок каналов формирует первый, второй, третий и четвертый сигналы заявки, поступающие на формирователь блокировок, который принимает сигнал запрос процессора и генерирует сигнал блокировка процессора, поступающий на выход устройства.

| УСТРОЙСТВО ПРИОРИТЕТНОГО ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2006 |

|

RU2320001C1 |

| Приоритетное устройство | 1982 |

|

SU1056194A1 |

| Способ получения цианистых соединений | 1924 |

|

SU2018A1 |

| US 8886899 B1, 11.11.2014. | |||

Авторы

Даты

2020-01-14—Публикация

2019-03-12—Подача