i 1зо6}К гсиие относится к вычислительной гсхиике, в ч;:стности к адаптивным мульти- )пес(-()рным системам, перестраивающим свою cTpvKTVjjy в зависимости от заданных способов обработки данных, и может быть нрименеио i , измерительно-вычислительных комплексах и s автоматизированных системах управления технологическими процессами, в системах автоматизации испытаний и 1чонтроля сложных обт ектов и в других подобных системах.

Целью изобретения является увеличение пропускной способности системы при обработке взаимозависимых заявок, за счет введения возможности параллельной обработки таких заявок и умеиьик пия времени простоя нроцессорон в носледовательном режиме работы системы.

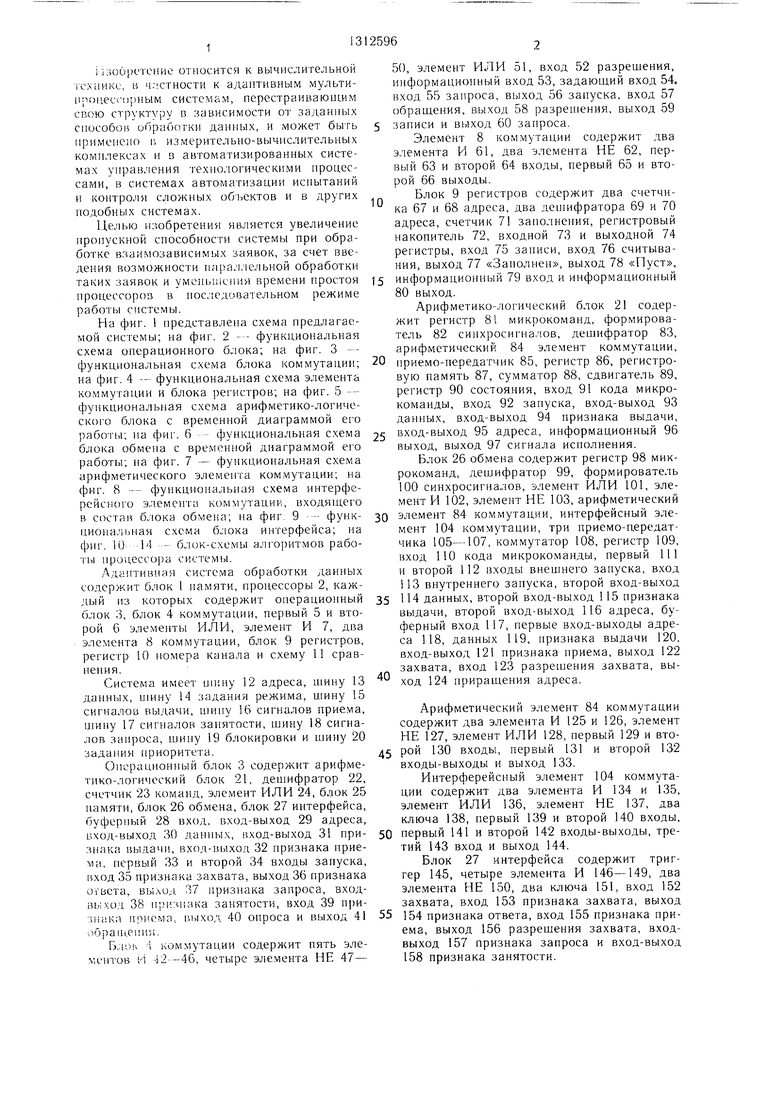

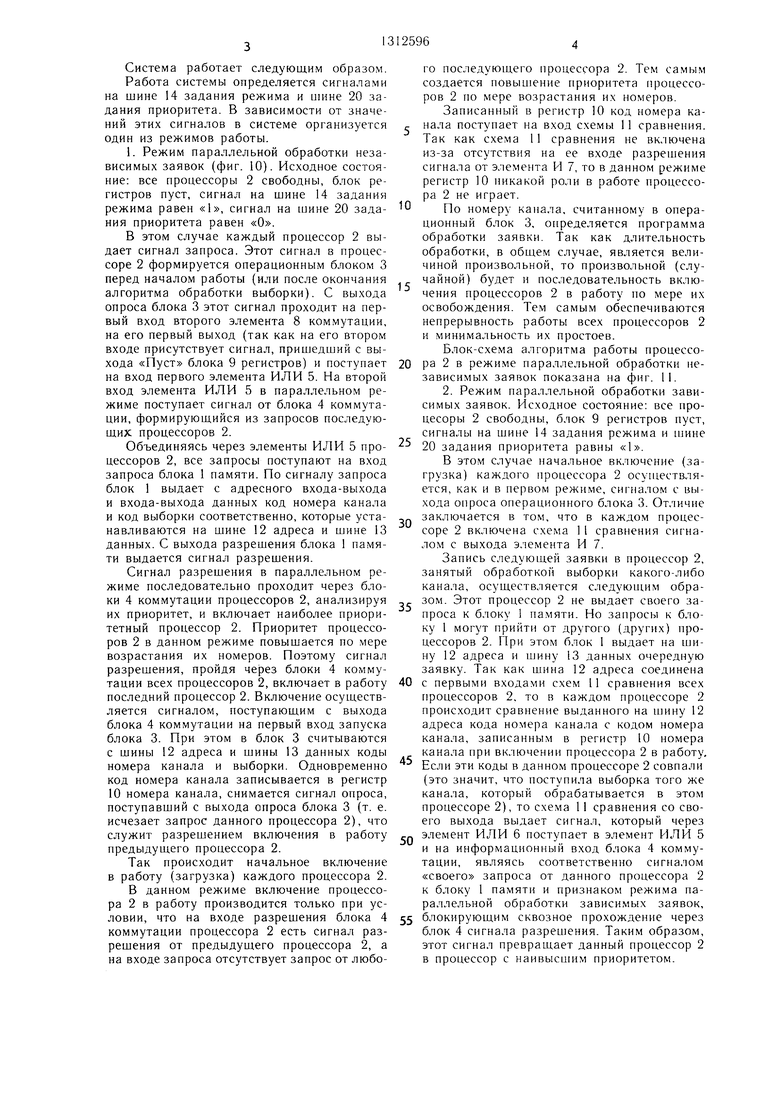

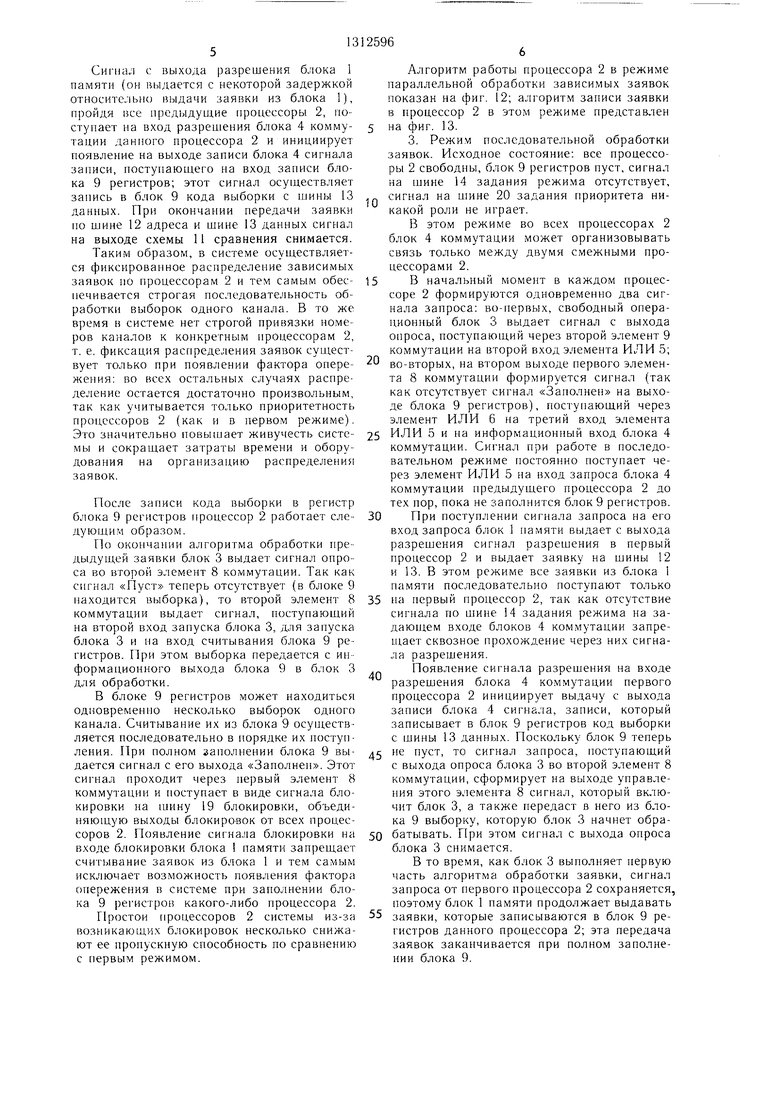

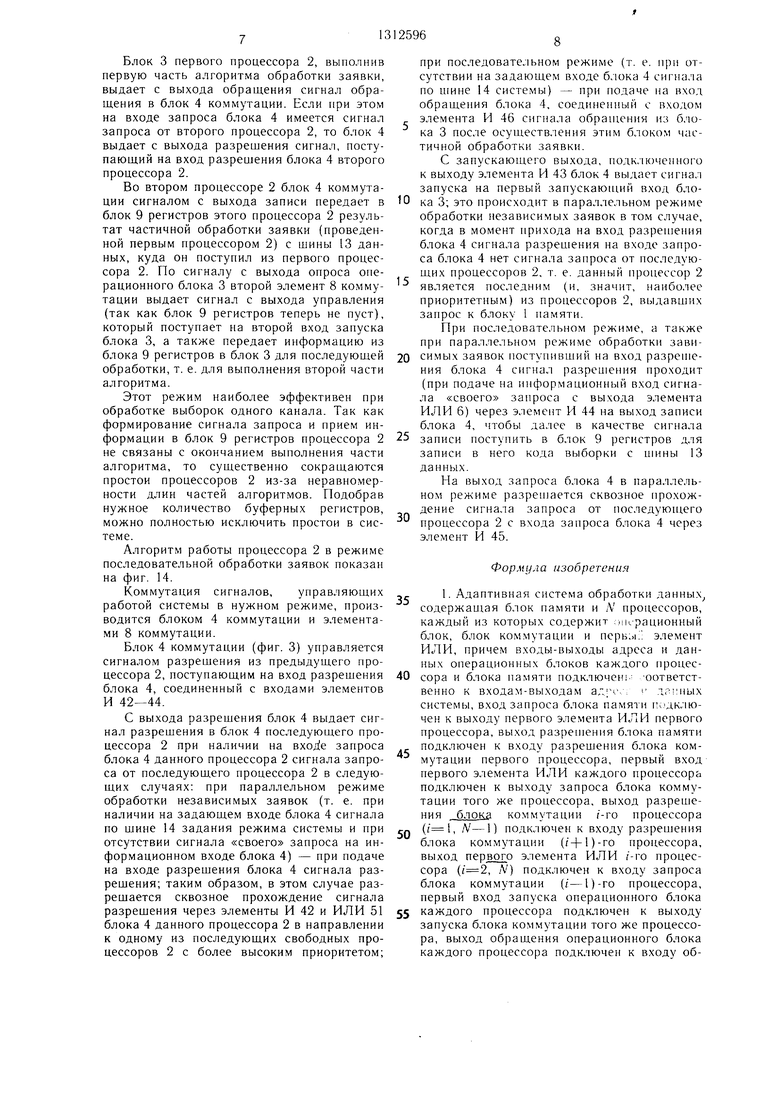

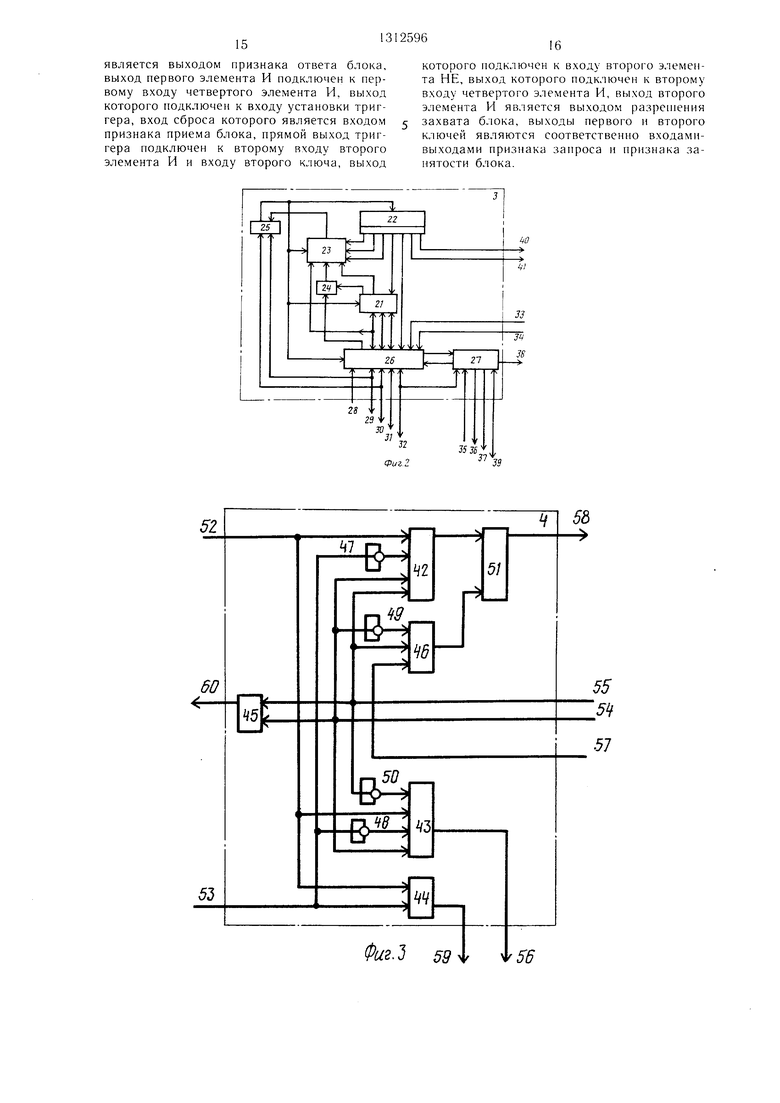

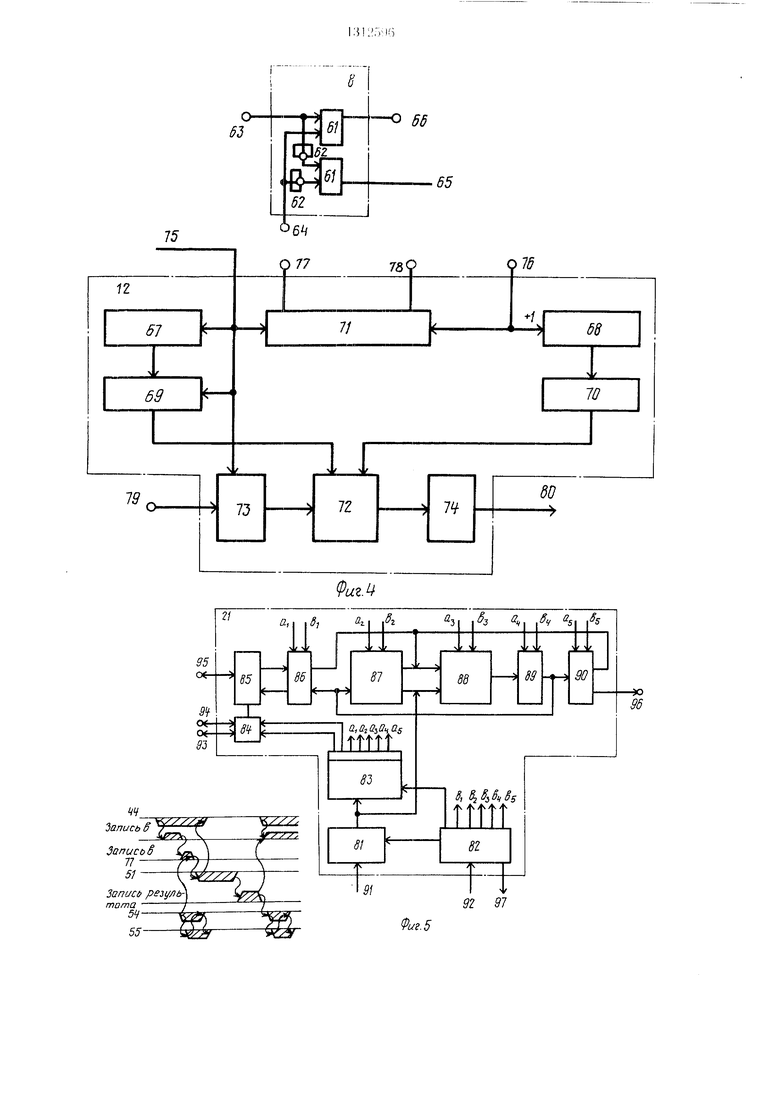

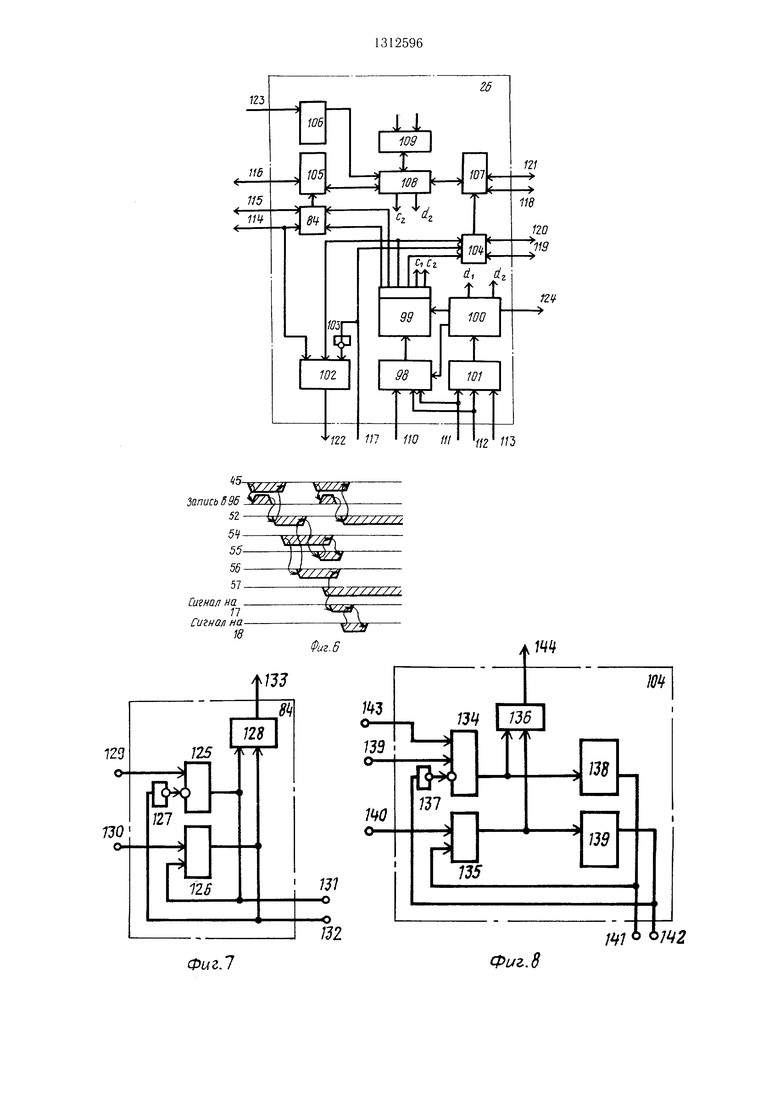

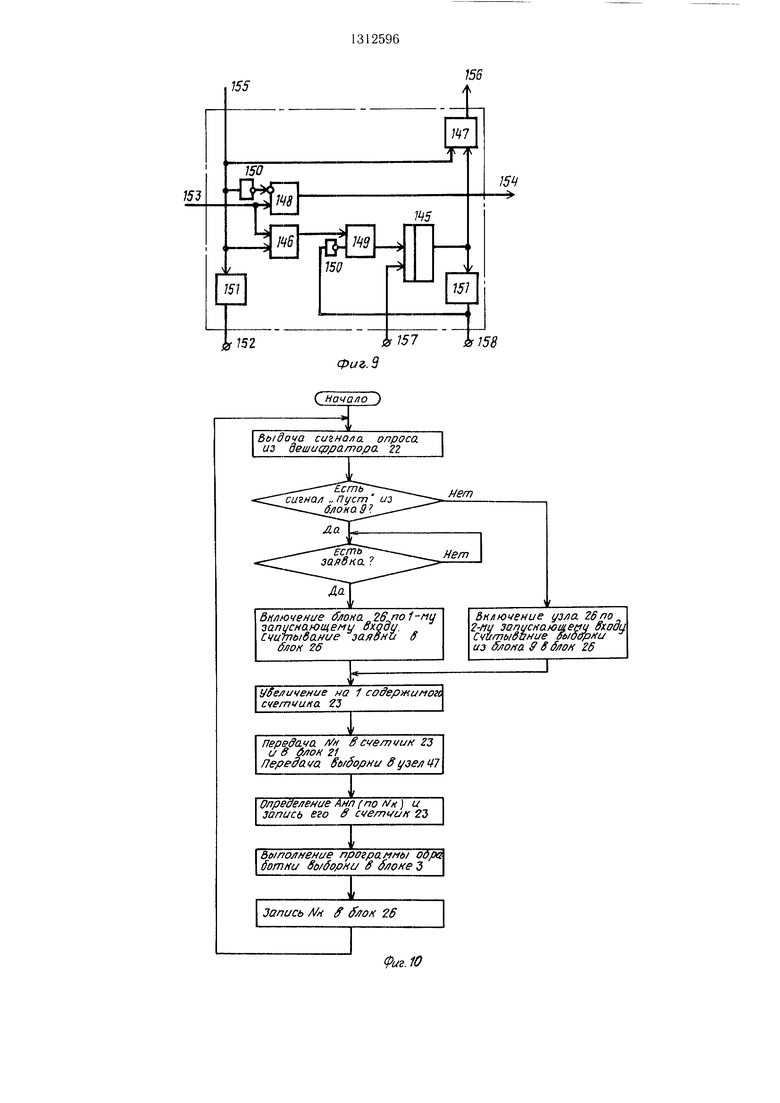

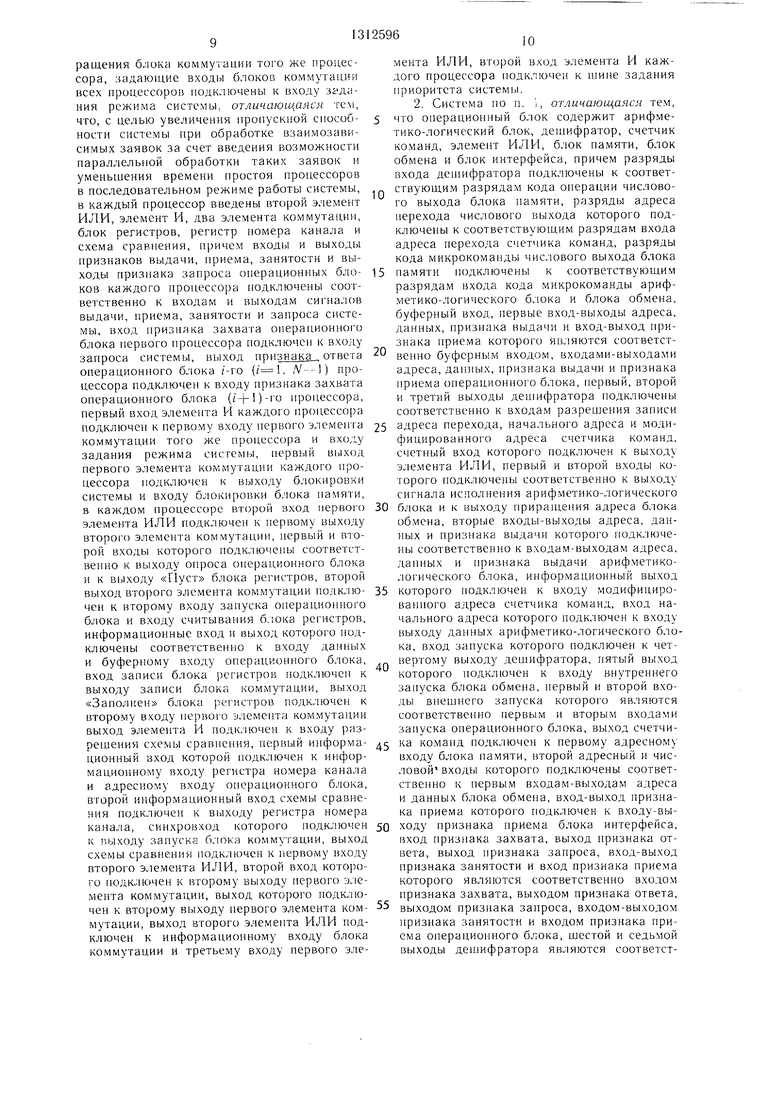

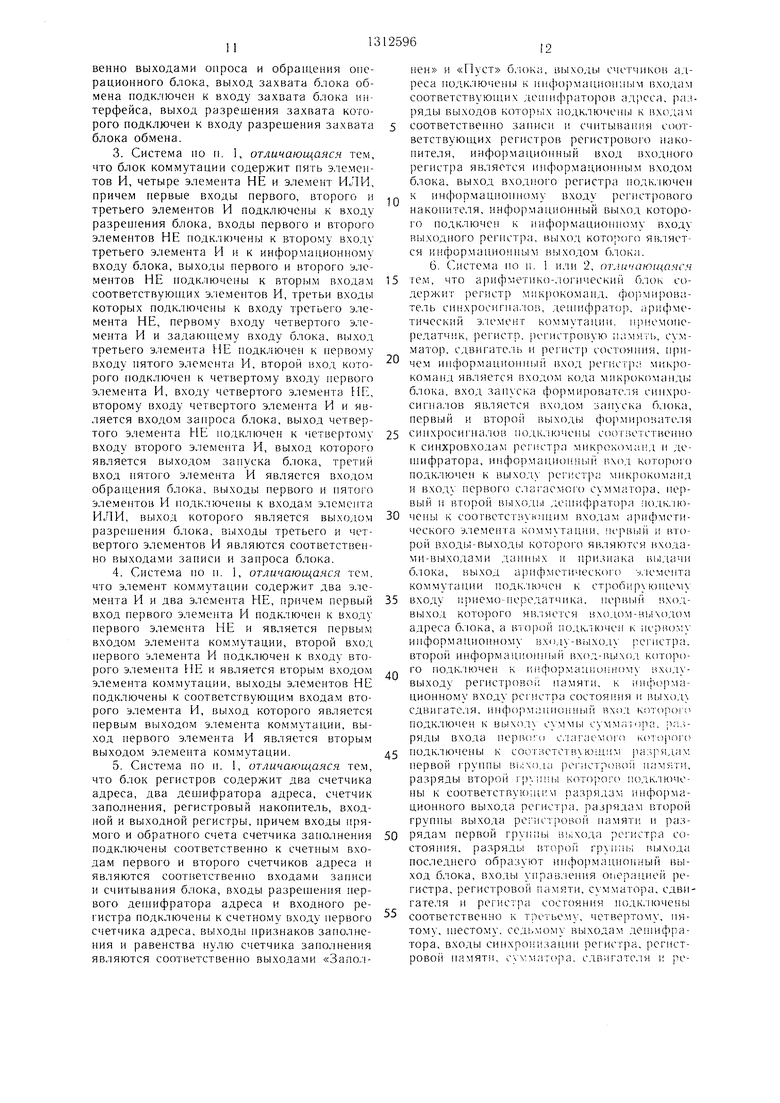

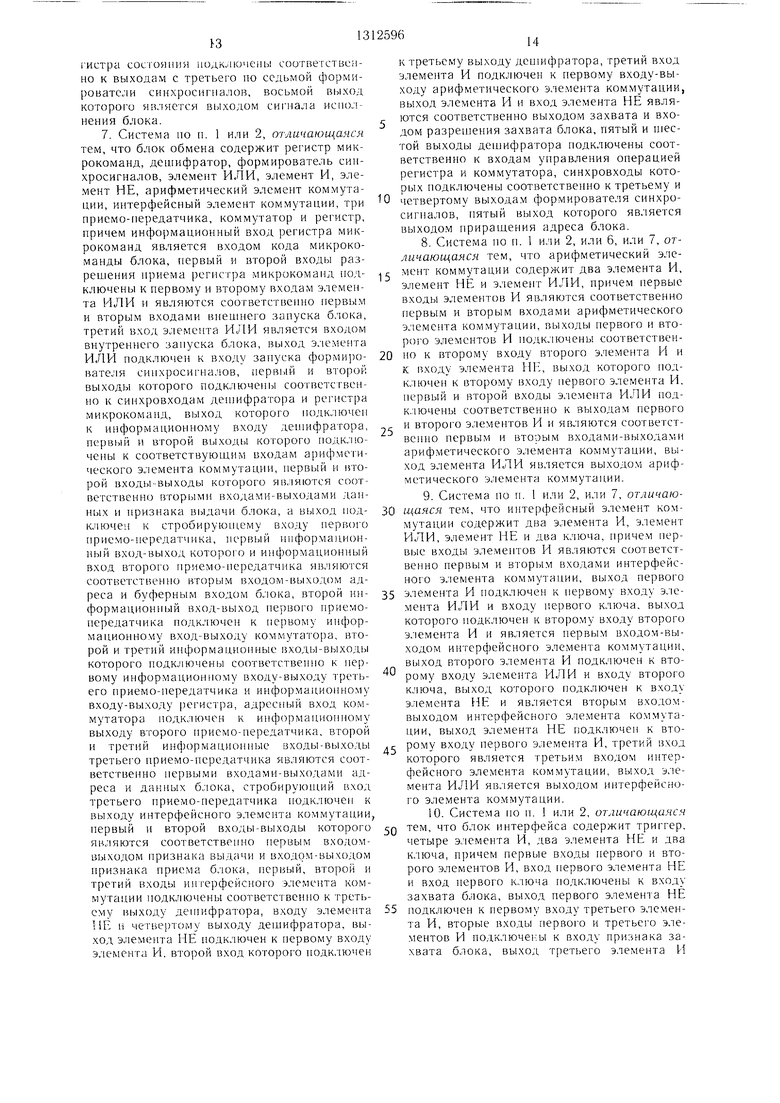

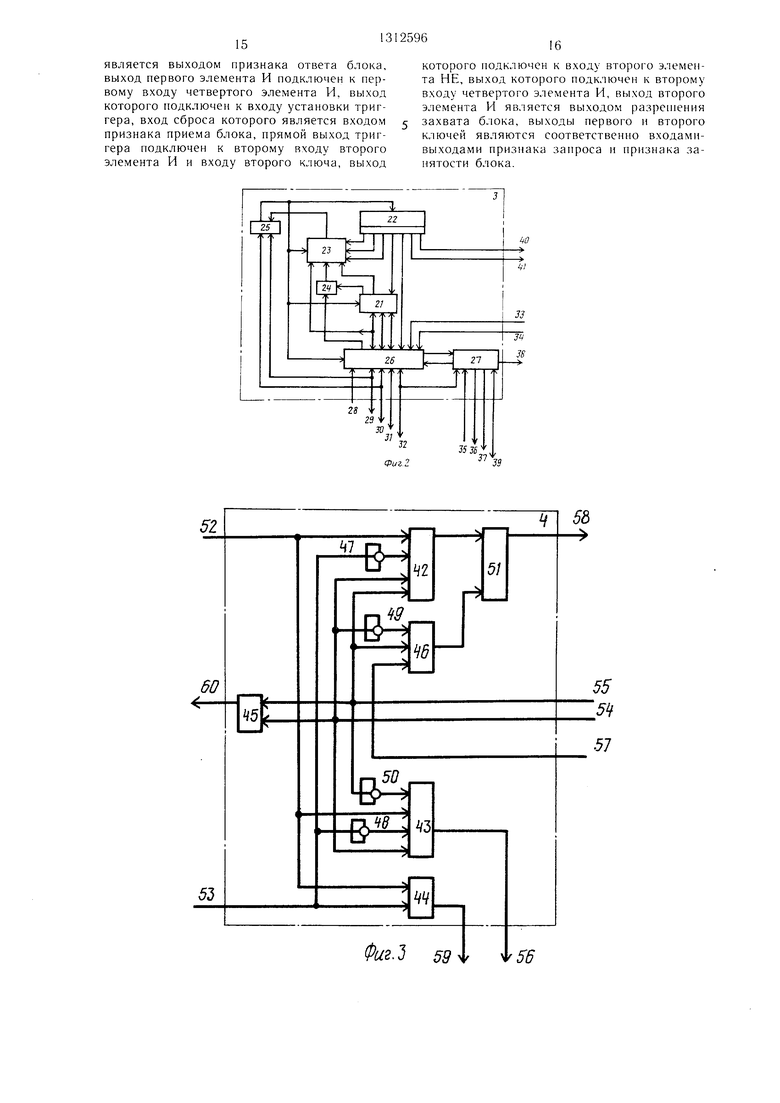

На фиг. 1 представлена схема предлагаемой системы; на фиг. 2 - - функциональная схема операционного блока; па фиг. 3 - функциональная схема блока коммутации; на фиг. 4 -- функциональная схема элемента коммута 1,ии и блока регистров; на фиг. 5 --- функциональная схема арифметико-логического блока с временной диаграммой его рабо пл; на фиг. 6 функциональная схема блока обмена с временной диаграммой его работы; на фиг. 7 - функциональная схема арифметического элемента коммутации; на фиг. 8 - функциональная схема интерфе- рейсмого элемента коммутации, входягцего в состав блока обмена; на фиг. 9 - функциональная схема блока интерфейса; на фиг. 10 14 - блок-схемы алгоритмов работы нроцессора системы.

Ада 1тивная система обработки данных содержит блок I памяти, процессоры 2, каждый из которых содержит операционный блок 3, блок 4 коммутации, первый 5 и второй б элементы ИЛИ, элемент И 7, два элемента 8 коммутации, блок 9 регистров, регистр 10 номера канала и схему 11 сравнения.

Система имеет uiiiFsy 12 адреса, тину 13 данных, тину 14 задания режима, шину 15 сигналов выдачи, тину 16 сигналов приема, типу 17 сигналов занятости, шину 18 сигналов занроса, шину 19 блокировки и шину 20 задания приоритета.

Операционный блок 3 содержит арифметико-логический блок 21, дешифратор 22, счетчик 23 команд, элемент ИЛИ 24, б.ток 25 памяти, блок 26 обмена, блок 27 интерфейса, буферный 28 вход, вход-выход 29 адреса, 15ход-выход 30 данных, р,ход-выход 31 признака выдачи, вход-выход 32 признака приема, первый 33 и второй 34 входы запуска, вход 35 признака захвата, выход 36 признака ответа, Bijixo;), 37 признака запроса, вход- вь;ход 38 н|. занятости, вход 39 нри- знакп приема, выход 40 опроса и выход 41 viopaiuenHH.

1 коммутации содержит нять эле- мептов И 42--46, четыре элемента НЕ 47-

50, элемент ИЛИ 51, вход 52 разрешения, информационный вход 53, задающий вход 54. вход 55 занроса, выход 56 запуска, вход 57 обращения, выход 58 разрен ения, выход 59

записи и выход 60 запроса.

Элемент 8 коммутации содержит два элемента И 61, два элемента НЕ 62, первый 63 и второй 64 входы, первый 65 и второй 66 выходы.

Блок 9 регистров содержит два счетчика 67 и 68 адреса, два дешифратора 69 и 70 адреса, счетчик 71 заполнеиия, регистровый накопитель 72, входной 73 и выходной 74 регистры, вход 75 записи, вход 76 считывания, выход 77 «Заполнен, выход 78 «Пуст,

информациорп1ый 79 вход и информационный 80 выход.

Арифметико-логический блок 21 содержит регистр 81 микрокоманд, формирователь 82 синхросигна.лов, дешифратор 83, арифметический 84 элемент коммутации,

0 приемо-передатчик 85, регистр 86, регистровую намять 87, сумматор 88, сдвигатель 89, регистр 90 состояния, вход 91 кода микрокоманды, вход 92 запуска, вход-выход 93 данпых, вход-выход 94 признака выдачи,

5 вход-выход 95 адреса, информационный 96 выход, выход 97 сигнала исполпения.

Блок 26 обмена содержит регистр 98 микрокоманд, дешифратор 99, формирователь 100 синхросигналов, элемент ИЛИ 101, элемент И 102, элемент НЕ 103, арифметический

0 элемент 84 коммутации, интерфейсный элемент 104 коммутации, три приемо-цередат- чика 105-107, коммутатор 108, регистр 109, вход 110 кода микрокоманды, первый 111 н второй 112 входы внешнего запуска, вход 13 внутреннего запуска, второй вход-выход

5 114 данных, второй вход-выход 115 признака выдачи, второй вход-выход 116 адреса, буферный вход 117, первые вход-выходы адреса 118, данных 119, признака выдачи 120, вход-выход 121 признака нриема, выход 122 захвата, вход 123 разрешения захвата, вы- ход 124 нриращения адреса.

Арифметический элемент 84 коммутации содержит два элемента И 125 и 126, элемент НЕ 127, элемент ИЛИ 128, первый 129 и вто5 рой 130 входы, первый 131 и второй 132 входы-выходы и выход 133.

Интерферейспый элемент 104 коммутации содержит два элемента И 134 и 135, элемент ИЛИ 136, элемент НЕ 137, два ключа 138, первый 139 и второй 140 входы,

0 первый 141 и второй 142 входы-выходы, третий 143 вход и выход 144.

Блок 27 интерфейса содержит триггер 145, четыре элемента И 146-149, два элемента НЕ 150, два ключа 151, вход 152 захвата, вход 153 признака захвата, выход

5 154 признака ответа, вход 155 признака приема, выход 156 разрешения захвата, вход- выход 157 признака запроса и вход-выход 158 признака занятости.

Система работает следующим образом.

Работа системы определяется сигналами на шине 14 задания режима и шине 20 задания приоритета. В зависимости от значений этих сигналов в системе организуется один из режимов работы.

1. Режим параллельной обработки независимых заявок (фиг. 10). Исходное состояние: все процессоры 2 свободны, блок регистров пуст, сигнал на шине 14 задания режима равен «1, сигнал на шине 20 зада- ния приоритета равен «О.

В этом случае каждый процессор 2 выдает сигнал запроса. Этот сигнал в процессоре 2 формируется операционным блоком 3 перед началом работы (или после окончания алгоритма обработки выборки). С выхода опроса блока 3 этот сигнал проходит на первый вход второго элемента 8 коммутации, на его первый выход (так как на его втором входе присутствует сигнал, пришедший с выхода «Пуст блока 9 регистров) и поступает на вход первого элемента ИЛИ 5. На второй вход элемента ИЛИ 5 в параллельном режиме поступает сигнал от блока 4 коммутации, формирующийся из запросов последующих процессоров 2.

Объединяясь через элементы ИЛИ 5 процессоров 2, все запросы поступают на вход запроса блока 1 памяти. По сигналу запроса блок 1 выдает с адресного входа-выхода и входа-выхода данных код номера канала и код выборки соответственно, которые устанавливаются на шине 12 адреса и шине 13 данных. С выхода разрешения блока 1 памяти выдается сигнал разрешения.

Сигнал разрешения в параллельном режиме последовательно проходит через блоки 4 коммутации процессоров 2, анализируя их приоритет, и включает наиболее приоритетный процессор 2. Приоритет процессоров 2 в данном режиме повышается по мере возрастания их номеров. Поэтому сигнал разрешения, пройдя через блоки 4 коммутации всех процессоров 2, включает в работу последний процессор 2. Включение осуществляется сигналом, поступающим с выхода блока 4 коммутации на первый вход запуска блока 3. При этом в блок 3 считываются с шины 12 адреса и шины 13 данных коды номера канала и выборки. Одновременно код номера канала записывается в регистр 10 номера канала, снимается сигнал опроса, поступавший с выхода опроса блока 3 (т. е. исчезает запрос данного процессора 2), что служит разрешением включения в работу предыдущего процессора 2.

Так происходит начальное включение в работу (загрузка) каждого процессора 2.

В данном режиме включение процессора 2 в работу производится только при условии, что на входе разрешения блока 4 коммутации процессора 2 есть сигнал раз- рещения от предыдущего процессора 2, а на входе запроса отсутствует запрос от любо

5

5

0

5

0

5

0

5

0

го последующего процессора 2. Тем самым создается повышение приоритета процессоров 2 по мере возрастания их номеров.

Записанный в регистр 10 код номера канала поступает на вход схемы 11 сравнения. Так как схема 11 сравнения не включена из-за отсутствия на ее входе разрешения сигнала от элемента И 7, то в данном режиме регистр 10 никакой роли в работе процессора 2 не играет.

По номеру канала, считанному в операционный блок 3, определяется программа обработки заявки. Так как длительность обработки, в общем случае, является величиной произвольной, то произвольной (случайной) будет и последовательность включения процессоров 2 в работу по мере их освобождения. Тем самым обеспечиваются непрерывность работы всех процессоров 2 и минима.тьность их простоев.

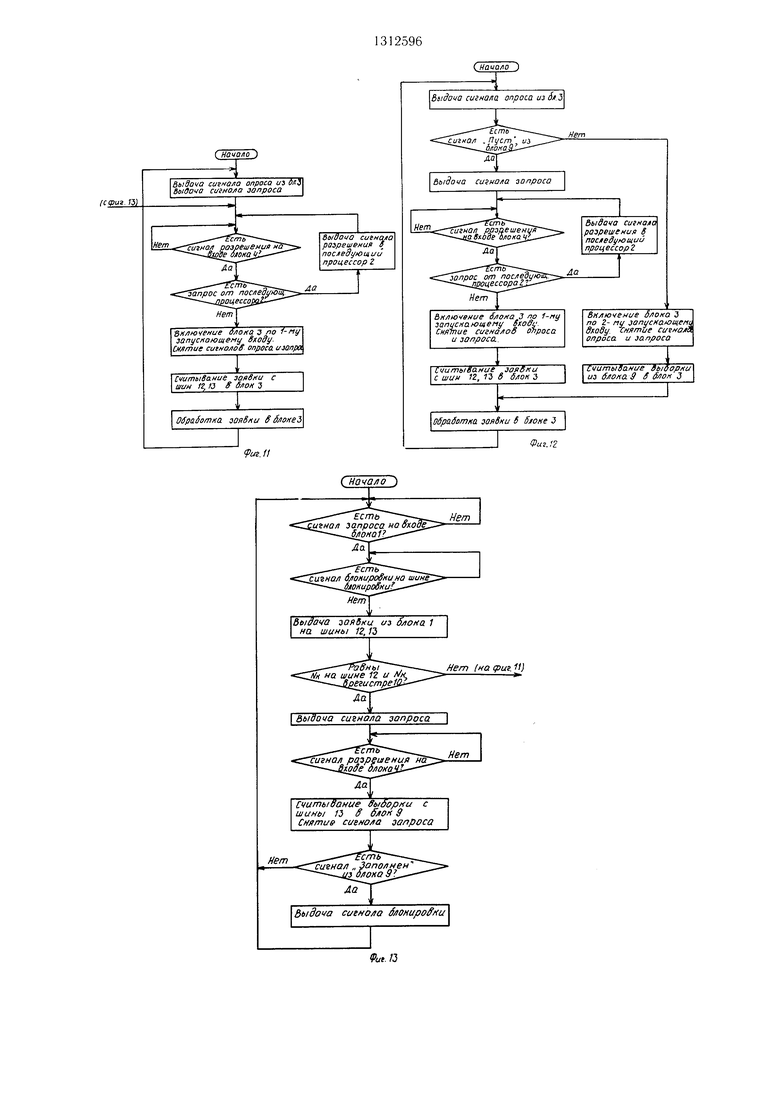

Блок-схема алгоритма работы процессора 2 в режиме параллельной обработки независимых заявок показана на фиг. 11.

2. Режим параллельной обработки зависимых заявок. Исходное состояние: все про- цесоры 2 свободны, блок 9 регистров пуст, сигналы на шине 14 задания режима и щине 20 задания приоритета равны «1.

В этом случае начальное включение (загрузка) каждого процессора 2 осуществляется, как и в первом режиме, сигналом с выхода опроса операционного блока 3. От, 1ичие заключается в том, что в каждом процессоре 2 включена схема 11 сравнения сигналом с выхода элемента И 7.

Запись следующей заявки в процессор 2, занятый обработкой выборки какого-либо канала, осуществляется следуюнщм образом. Этот процессор 2 не выдает своего запроса к блоку 1 памяти. Но запросы к блоку 1 могут прийти от другого (других) процессоров 2. При этом блок 1 выдает на шину 12 адреса и шину 13 данных очередную заявку. Так как щина 12 адреса соединена с первыми входами схем 11 сравнения всех процессоров 2, то в каждом процессоре 2 происходит сравнение выданного на шину 12 адреса кода номера канала с кодом номера канала, записанным в регистр 10 номера канала при включении процессора 2 в работу. Если эти коды в данном процессоре 2 совпали (это значит, что поступила выборка того же канала, который обрабатывается в этом процессоре 2), то схема 11 сравнения со своего выхода выдает сигнал, который через элемент ИЛИ 6 поступает в элемент ИЛИ 5 и на информационный вход блока 4 коммутации, являясь соответственно сигналом «своего запроса от данного процессора 2 к блоку 1 памяти и признаком режима параллельной обработки зависимых заявок, блокирующим сквозное прохождение через блок 4 сигнала разрешения. Таким образом, этот сигнал превращает данный процессор 2 в процессор с наивысшим приоритетом.

Сигнал с выхода разрешения блока 1 памяти (он выдается с некоторой задержкой относительно выдачи заявки из блока 1), и)ойдя все нредыдуи|ие процессоры 2, поступает па вход разрешения блока 4 коммутации данного процессора 2 и инициирует появление на выходе записи блока 4 сигнала записи, поступаюнлего на вход заниси блока 9 регистров; этот сигнал осуществляет запись в блок 9 кода выборки с шины 13 данных. При окончании передачи заявки по шине 12 адреса и шине 13 данных сигнал на выходе схемы 11 сравнения снимается.

Таким образом, в системе осуществляется фиксированное распределение зависимых заявок по процессорам 2 и тем самым обеспечивается строгая последовательность обработки выборок одного канала. В то же время в системе нет строгой привязки номеров каналов к конкретным процессорам 2, т. е. фиксация распределения заявок существует только при появлении фактора опережения: во всех остальных случаях распределение остается достаточно произвольным, так как учитывается только приоритетность процессоров 2 (как и в первом режиме). Это значительно повьииает живучесть системы и сокращает затраты времени и оборудования на организацию распределения заявок.

После записи кода выборки в регистр блока 9 регистров процессор 2 работает следующим образом.

По окончании алгоритма обработки предыдущей заявки блок 3 выдает сигнал опроса во второй элемент 8 коммутации. Так как сигнал «Пуст теперь отсутствует (в блоке 9 находится выборка), то второй элемент 8 коммутации выдает сигнал, поступающий на второй вход запуска блока 3, для запуска блока 3 и на вход считывания блока 9 регистров. При этом выборка передается с информационного выхода блока 9 в блок 3 для обработки.

В блоке 9 регистров может находиться одновременно несколько выборок одного канала. Считывание их из блока 9 осуществляется последовательно в порядке их постуг - ления. При полном заполнении блока 9 выдается сигнал с его выхода «Заполнеп. Этот сигнал проходит через первый элемент 8 коммутации и поступает в виде сигнала блокировки на щину 19 блокировки, объеди- няю1цую выходы блокировок от всех процессоров 2. Появление сигна.)1а блокировки на входе блокировки блока 1 памяти запрещает считывание заявок из блока 1 и тем самым исключает возможность появления фактора опережения в системе при заполнении блока 9 pei-истров какого-либо процессора 2.

Простои npoixeccopoB 2 системы из-за возникающих блокировок несколько снижают ее пропускную способность по сравнению с первым режимом.

0

Алгоритм работы процессора 2 в режиме параллельной обработки зависимых заявок показан на фиг. 12; алгоритм записи заявки в процессор 2 в этом режиме представлен на фиг. 13.

3. Режим последовательной обработки заявок. Исходное состояние: все процессоры 2 свободны, блок 9 регистров пуст, сигнал на щине 14 задания режима отсутствует, сигнал на шине 20 задания приоритета никакой роли не играет.

В этом режиме во всех процессорах 2 блок 4 коммутации может организовывать связь только между двумя смежными процессорами 2.

В начальный момент в каждом процессоре 2 формируются одновременно два сигнала запроса: во-первых, свободный операционный блок 3 выдает сигнал с выхода опроса, поступающий через второй элемент 9 коммутации на второй вход элемента ИЛИ 5; во-вторых, на втором выходе первого элемента 8 коммутации формируется сигнал (так как отсутствует сигнал «Заполнен на выходе блока 9 регистров), постунающий через элемент ИЛИ 6 на третий вход элемента

5 ИЛИ 5 и на информационный вход блока 4 коммутации. Сигнал при работе в последовательном режиме постоянно поступает через элемент ИЛИ 5 на вход запроса блока 4 коммутации предыдущего процессора 2 до тех пор, пока не заполнится блок 9 регистров. При поступлении сигнала запроса на его вход запроса блок 1 памяти выдает с выхода разрещения сигнал разрещения в первый процессор 2 и выдает заявку на щины 12 и 13. В этом режиме все заявки из блока 1 памяти последовательно поступают только на первый процессор 2, так как отсутствие сигнала по тине 14 задания режима на задающем входе блоков 4 коммутации запрещает сквозное прохождение через них сигнала разрешения.

Появление сигнала разрешения на входе разрещения блока 4 коммутации первого процессора 2 инициирует выдачу с выхода записи блока 4 сигнала, записи, который записывает в блок 9 регистров код выборки с шины 13 данных. Поскольку блок 9 теперь не пуст, то сигнал запроса, поступающий с выхода опроса блока 3 во второй элемент 8 коммутации, сформирует на выходе управления этого элемента 8 сигнал, который включит блок 3, а также передаст в него из блока 9 выборку, которую блок 3 начнет обра0 батывать. При этом сигнал с выхода опроса блока 3 снимается.

В то время, как блок 3 выполняет первую часть алгоритма обработки заявки, сигнал запроса от первого процессора 2 сохраняется, поэтому блок 1 памяти продолжает выдавать

5 заявки, которые записываются в блок 9 регистров данного процессора 2; эта передача заявок заканчивается при полном заполнении блока 9.

0

5

0

5

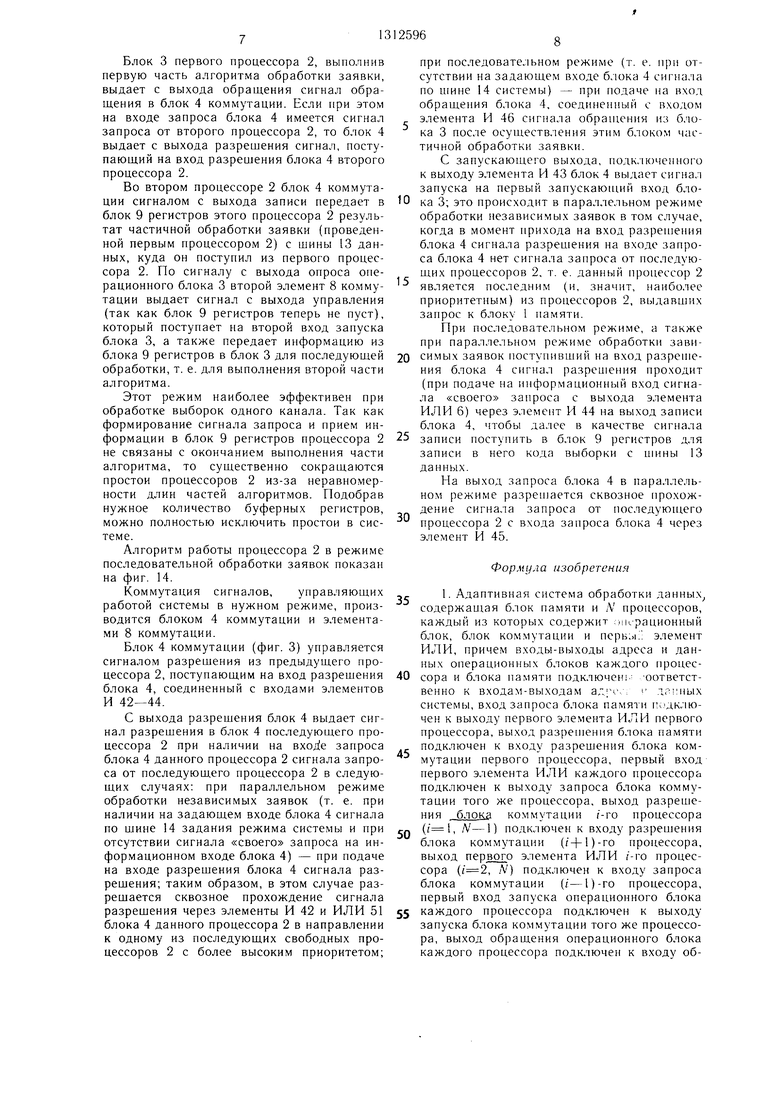

Блок 3 первого процессора 2, выполнив первую часть алгоритма обработки заявки, выдает с выхода обращения сигнал обращения в блок 4 коммутации. Если при этом на входе запроса блока 4 имеется сигнал запроса от второго процессора 2, то блок 4 выдает с выхода разрешения сигнал, поступающий на вход разрешения блока 4 второго процессора 2.

Во втором процессоре 2 блок 4 коммутации сигналом с выхода записи передает в блок 9 регистров этого процессора 2 результат частичной обработки заявки (проведенной первым процессором 2) с шины 13 данных, куда он поступил из первого процессора 2. По сигналу с выхода опроса операционного блока 3 второй элемент 8 комму- тации выдает сигнал с выхода управления (так как блок 9 регистров теперь не пуст), который поступает на второй вход запуска блока 3, а также передает информацию из блока 9 регистров в блок 3 для последующей обработки, т. е. для выполнения второй части алгоритма.

Этот режим наиболее эффективен при обработке выборок одного канала. Так как формирование сигнала запроса и прием информации в блок 9 регистров процессора 2 не связаны с окончанием выполнения части алгоритма, то существенно сокращаются простои процессоров 2 из-за неравномерности длин частей алгоритмов. Подобрав нужное количество буферных регистров, можно полностью исключить простои в системе.

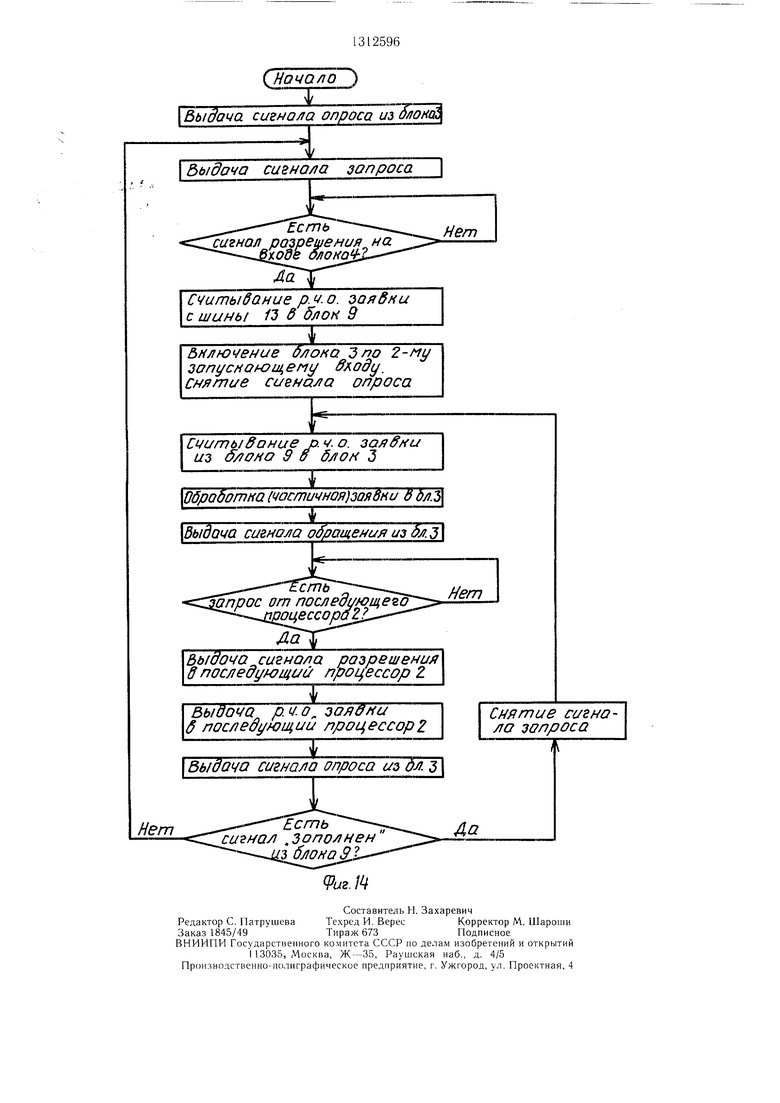

Алгоритм работы процессора 2 в режиме последовательной обработки заявок показан на фиг. 14.

Коммутация сигналов, управляющих работой системы в нужном режиме, производится блоком 4 коммутации и элементами 8 коммутации.

Блок 4 коммутации (фиг. 3) управляется сигналом разрешения из предыдущего процессора 2, поступающим на вход разрешения блока 4, соединенный с входами элементов И 42-44.

С выхода разрешения блок 4 выдает сигнал разрешения в блок 4 последующего процессора 2 при наличии на запроса блока 4 данного процессора 2 сигнала запроса от последующего процессора 2 в следующих случаях: при параллельном режиме обработки независимых заявок (т. е. при наличии на задающем входе блока 4 сигнала по щине 14 задания режима системы и при отсутствии сигнала «своего запроса на информационном входе блока 4) - при подаче на входе разрешения блока 4 сигнала разрешения; таким образом, в этом случае разрешается сквозное прохождение сигнала разрешения через элементы И 42 и ИЛИ 51 блока 4 данного процессора 2 в направлении к одному из последующих свободных процессоров 2 с более высоким приоритетом;

- 0

5

5

0

5

0

5

0

при последовательном режиме (т. е. при отсутствии на задающем входе блока 4 сигнала по шине 14 системы) - при подаче на вход обращения блока 4, соединенн1з1Й с входом элемента И 46 сигнала обращения из блока 3 после осуществления этим блоком частичной обработки заявки.

С запускающего выхода, подк. поченного к выходу элемента И 43 блок 4 выдает сигнал запуска на первый запускающий вход блока 3; это происходит в параллельном режиме обработки независимых заявок в том случае, когда в момент прихода на вход разреп ения блока 4 сигнала разрешения на входе запроса блока 4 нет сигнала запроса от последующих процессоров 2, т. е. данный процессор 2 является последним (и, значит, наиболее приоритетным) из процессоров 2, выдавших запрос к блоку 1 памяти.

При последовательном режиме, а также при параллельном режиме обработки зависимых заявок поступивший на вход разреп1е- ния блока 4 сигнал разрешения проходит (при подаче на информационный вход сигнала «своего запроса с выхода элемента ИЛИ 6) через элемент И 44 на выход записи блока 4, чтобы далее в качестве сигнала записи поступить в блок 9 регистров для записи в него кода выборки с шины 13 данных.

На выход запроса блока 4 в параллельном режиме разрешается сквозное прохождение сигнала запроса от последующего процессора 2 с входа запроса блока 4 через элемент И 45.

Формула изобретения

1. Адаптивная система обработки данных содержащая блок памяти и Л процессоров, каждый из которых содержит миграционный блок, блок коммутации и перь: к: элемент ИЛИ, причем входы-выходы адреса и данных операционных блоков каждого процессора и блока памяти подключен:- оответст- венно к входам-выходам аД Ч . данных системы, вход запроса блока памяти гк. дклю- чен к выходу первого элемента ИЛИ первого процессора, выход разрешения блока памяти подключен к входу разрешения блока коммутации первого процессора, первый вход первого элемента ИЛИ каждого процессора подключен к выходу запроса блока коммутации того же процессора, выход разрешения 6jiOji3 коммутации г -го процессора ((1, Л -1) подключен к входу разрешения блока коммутации ((+1)-го процессора, выход первого элемента ИЛИ /-го процессора ((2, ;V) подключен к входу запроса блока коммутации (/-1)-го процессора, первый вход запуска операционного блока каждого процессора подключен к выходу запуска блока коммутации того же процессора, выход обрац ения операционного блока каждого процессора подключен к входу обращения б.;1ока коммутации того же процессора, задающие входы блоков коммутации всех ироцессоров подключены к входу задания режима системы, отличаю1цаяся тем, что, с целью увеличения iipoLiycKHoft способности системы при обработке взапмозави- симых заявок за счет введения возможности параллельной обработки таких заявок и уменьщения времени простоя процессоров в последовательном режиме работы системы, в каждый процессор введены второй элемент ИЛИ, элемент И, два элемента коммутации, блок регистров, регистр номера канала и схема сравнения, причем входы и выходы признаков выдачи, приема, занятости и выходы признака запроса операционных блоков каждого процессора подключены соответственно к входам и выходам сигналс)в выдачи, приема, занятости и запроса системы, вход признака захвата операционного блока первого процессора подключеп к входу запроса системы, выход призiiajia ответа операционного блока /-го {(, .V--) процессора подключен к входу нризнака захвата операционного блока (г-|-1)-го процессора, первый вход элемента И каждого процессора подключен к первому входу первого элемента коммутации того же процессора и входу задания режима cncreMiii, первый выход первого элемента коммутации каждого процессора подключен к выходу блокировки системы и входу блокировки блока памяти, в каждом процессоре второй вход, первого элемента ИЛИ подключен к первому выходу второго элемента коммутации, первый и второй входы которого подключены соответственно к выходу опроса операционного блока и к выходу «Пуст блока регистров, второй выход второго элемента коммутации подключен к второму входу зануска онерациошюго блока и входу считываьщя б.юка регистров, информационные вход и выход которого подключены соответетвенио к входу данных и буферному входу операционного блока, вход записи блока регистров подключен к выходу записи блока коммутации, выход «Заполнен блока регистров подключен к второму входу первого элемента коммутации выход элемента И подключен к входу разрешения схемы срав1 ения, первый информационный вход которой подключен к информационному входу регистра номера канала и адресному входу операционного блока, второй информационный вход схемы сравнения подключен к выходу регистра номера канала, синхровход которого подключен к р.ыходу запуска б;юка коммутации, выход схемы сравпения подключен к первому входу второго элемента ИЛИ, второй вход KOTOJJO- го подключен к вгорому выходу первого элемента коммутации, выход которого подключен к второму выходу первого элемента коммутации, выход второго элемента ИЛИ подключен к информаи.ионному входу блока коммутации и третьему входу иервого эле5

0

5

0

5

0

5

0

5

мента ИЛИ, второй вход элемента И каждого процессора подключен к шине задания приоритета системы.

2. Система но п. ,, отличающаяся тем, что операционный блок содержит арифметико-логический блок, дешифратор, счетчик команд, элемент ИЛИ, блок памяти, блок обмена и блок интерфейса, причем разряды входа дешифратора нодключены к соответствующим разрядам кода операции числового выхода блока памяти, разряды адреса перехода числового выхода которого подключены к соответствующим разрядам входа адреса перехода счетчика команд, разряды кода микрокоманды числового выхода блока памяти подключены к соответствующим разрядам входа кода микрокоманды арифметико-логического б,:юка и блока обмена, буферный вход, первые вход-выходы адреса, данных, признака выдачи и вход-выход нризнака приема которого являются соответственно буферным входом, входами-выходами адреса, данных, нризнака выдачи и признака приема онерационного блока, первый, второй и третий выходы дешифратора подключены соответственно к входам разрешения записи адреса перехода, начального адреса и модифицированного адреса счетчика команд, счетный вход которого нодключен к выходу элемента ИЛИ, первый и второй входы которого подключены соответственно к выходу сигнала исполнения арифметико-. югического блока и к выходу приращения адреса блока обмена, вторые входы-выходы адреса, данных и призь{ака выдачи которого подключены соответственно к входам-выходам адреса, данных и признака выдачи арифметико- . югического блока, информационный выход которого подключен к входу модифицированного адреса счетчика команд, вход начального адреса которого подключен к входу выходу данных арифметико-логического блока, вход зануска которого подключен к четвертому выходу дешифратора, пятый выход которого подключен к входу внутреннего запуска блока обмена, первый и второй входы внещнего зануска которого являются соответственно первым и вторым входами запуска онерационного блока, выход счетчика комаид подключен к первому адресному входу б. юка памяти, второй адресный и числовой входы которого подключены соответственно к первым входам-выходам адреса и данных блока обмена, вход-выход признака приема KOTOpoi o подключен к входу-выходу признака приема блока интерфейса, вход признака захвата, выход признака ответа, выход признака запроса, вход-выход признака занятости и вход признака приема которого являются соответственно входом признака захвата, выходом признака ответа, выходом признака запроса, входом-выходом признака занятости и входом признака приема операционпого блока, шестой и седьмой выходы дец ифратора являются соответственно выходами опроса и обращения операционного блока, выход захвата блока обмена подключен к входу захвата блока интерфейса, выход разрешения захвата которого подключен к входу разрешения захвата блока обмена.

3.Система но п. 1, отличающаяся тем, что блок коммутации содержит пять элементов И, четыре элемента НЕ и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И подключены к входу разрен1ения блока, входы первого и второго элементов НЕ подключены к второму входу третьего элемента И и к информационному входу блока, выходы первого и второго элементов НЕ нодключены к вторым входам соответствуюп1их э. :ементов И, третьи входы которых подключены к входу третьего элемента НЕ, первому входу четвертого э.пе- мента И и задак)цему входу блока, выход третьего элемента НЕ подключен к первому входу пятого элемента И, второй вход которого подключен к четвертому входу первого элемента И, входу четвертого элемента НЕ, второму входу четвертого элемента И и является входом запроса блока, выход четвертого элемента НЕ подключен к четвертому входу второго э.лемента И, выход которого является выходом запуска блока, третий вход пятого элемента И является входом обращения блока, выходы первого и пятого элементов И нодключеш к входам элемента ИЛИ, выход которого является выходом разрец ения блока, выходы третьего и четвертого элементов И являются соответственно выходами записи и запроса блока.

4.Система но н. 1, отличающаяся тем, что элемент коммутации содержит два элемента И и два элемента НЕ, причем первый вход первого элемента И подключен к входу первого элемента НЕ и является первым входом элeмe ггa коммутации, второй вход первого элемента И подключен к входу второго элемента НЕ и является вторым входом элемента коммутации, выходы элементов НЕ подключены к соответствующим входам второго элемента И, выход которого является первым выходом элемента коммутации, выход первого элемента И является вторым выходом элемента коммутации.

5.Система но н. 1, отличающаяся тем, что блок регистров содержит два счетчика адреса, два дешифратора адреса, счетчик заполнения, регистровый накопитель, входной и выходной регистры, нричем входы мого и обратного счета счетчика заполнения подключены соответственно к счетным входам первого и второго счетчиков адреса и являются соответственно входами заниси и считывания блока, входы разрешения первого деп1ифратора адреса и входного регистра подключены к счетному входу первого счетчика адреса, выходы признаков заполнения и равенства нулю счетчика заполнения являются соответственно выходами «Sano.iнен и «Иуст б, 1ока, выходы счетчиков адреса по;1к;1Ючены к информационным входам соответствующих деншфраторов ад реса, разряды выходов которых п()дк,1ючены к входам

соответственно записи п считывания соответствующих регистров регистрового накопителя, информационный вход входного регистра является информационным входом блока, выход входного регистра подключен

„ к информацпонному входу регистрового наконителя, информационный выход которого подключен к информационному входу выходного регистра, выход которого являет ся информационным выходом блока.

6. Система по п. 1 или 2, (т,1ич1 Ю1цаяся

5 тем, что арифметико-,огимески(1 блок ct)- держит регистр )окоманд, (poininpOBa- тель си11хросигна., дешифратор, apiujiMe- тический э. 1емент ко мутацин. приемопередатчик, регистр, нм истровую .мять, сумматор, сдвигате.чь и регист}) состояния, причем ипформационН1)1;1 вход periicipa мик(1о- команд является входом кода микрокоманды блока, вход занх ска формировате,1я синхро- , 1ов яв,1яется входом запуска б.юка, первый и. BTOpOi i выходы фо|1мировате,:1я

5 синхроси1 налов нодк.иочсны соогис ственно к cииxpoвxoдa регистра микроком; . и де- ишфратора, информационный которого подключен к выход регистра микрокоманд и входу первого c. iai acMoi o сумматора, вый и BTOpoii В1 1ходы дешифратора :1одк,-1К10 чены к соогвотст П к |цим входам арифметического элемента коммутации, К рв1 П1 и второй вход1 1-выходы которого являются входами-выходами данн1 1х и признака выдачи блока, выход арифметического элемента коммутации подк. 1ючен к ст 1обг;рук)

5 входу г.риемо-передатчика, первый вход- выход которого яв, яется входом-выходом адреса б.чока, а второй подключен к пс;)0л;у информационному входу-выходу регистра. BTOpoii информационный вход-выход которо0

0

го подк 1ючен к ипфор ;ац1 о11ному входувыходу регистровои памяти, к ишрорма- ционному входу рс1 истра состояния и выхо.ч} сдвигате;1Я, информационный вход KOTCipoi o подк:1ючен к выход} , пора. ji. i.i- ряды входа перво Ч) c,iai ac K i (i KOTopoi o 5 подключены к соотзетств (тазрядам нервой группы В1) poi HCTpoiuiii памяти,

второй ГруИПЬ КОТОрОГ( и)ДК, 1ЮЧСны к соответствук) разряда ; информационного выхода регистра, разрядам второй группы выхода регистровой памяти н раз- 0 рядам нервой груп;1ы в ;хода регистра состоя , разряды второй групн -; пыхода последнего образуют информационньп 1 выход б, юка, входы унрав, 1ения 011ерацией регистра, регистровой памяти, сумматора, сдви- гателя и регистра сосгояния нодк,1ючены

5

соответственно к третьему, четвертому, пятому, ц естому, седьмому выходам дешифратора, входы синхр01 :1 зации регистра, регистровой памяти, .MHTojia. сдвигатс, 1Я i: i eгистра состояния иодк. 1юче 1ы соотЕ етствем- но к выходам с третьего по седьмой формирователи синхросигналов, восьмой выход которого является выходом си|-нала иснол- нения блока.

7. Система но п. 1 или 2, отличающаяся тем, что блок обмена содержит регистр микрокоманд, дешифратор, формирователь синхросигналов, элемент ИЛИ, элемент И, элемент НЕ, арифметический элемент коммутации, интерфейсный элемент коммутации, три нриемо-передатчика, коммутатор и регистр, причем информационный вход регистра микрокоманд является входом кода микрокоманды блока, первый и второй входы разрешения нриема регисгра микрокоманд подключены к первому и второму входам элемента ИЛИ и являются соответственно первым и вторым входами внешнего запуска блока, третий вход элемента ИЛИ является входом внутреннего запуска блока, выход э.чемента ИЛИ подключен к входу запуска форми)0- вателя cHiixpocni-najiOB, перв1 1Й и второй выходы которого подключены сооч ветсгвен- по к синхровходам дешифратора и регистра микрокоманд, выход которого подключен к информационному входу дешифратора, первый и второй выходы которого подключены к соответствующим входам арифметического элемента коммутации, первый и второй входы-вь11ходы которого яв.мяются соответственно втор1з1мп входами-выходами дап- ных и признака выдачи блока, а выход подключен к стробируюп1ему входу первого нриемо-передатчика, первый информационный вход-выход которого и информационный вход второго приемо-нередатчика являются соответственно вторым входом-выходом адреса и буферным входом б.:1ока, второй lui- формационный вход-выход нервого приемопередатчика нодключеп к первому информационному вход-выходу коммутатора, второй и третий информационные входы-выходы которого подк.лючен1з1 соответственно к первому информационному входу-выходу третьего фиемо-передатчика и информационному входу-выходу регистра, адресный вход коммутатора подключен к ипформационному выходу второго нриемо-нередатчика, второй и третий информационные входы-выходы третьего нриемо-передатчика являются соответственно нервыми входами-выходами адреса и данных б.лока, стробируюший вход третьего приемо-нередатчика иодключен к выходу интерфейсного элемента коммутации, первый н второй входы-выходы которого яв;1яются соответственно первым входом- выходом признака выдачи и входом-выходом нризнака приема блока, первый, второй и третий входы ингерфейсного элемента коммутации подключены соответственно к третьему выходу депп .фратора, входу элемента НЕ н чет15ертому выходу дешифратора, выход элемента НЕ подключен к первому входу элемента И, второй вход которого подключен

5

5

к третьему выходу деп1ифратора, третий вход элемента И подключен к первому входу-выходу арифметического элемента коммутации, выход элемента И и вход элемента НЕ являются соответственно выходом захвата и входом разрен1ения захвата блока, нятый и шестой выходы дешифратора подключены соответственно к входам унравления онерацией регистра и коммутатора, синхровходы которых подключены соответственно к третьему и четвертому выходам формирователя синхросигналов, пятый выход которого является выходом прирашения адреса блока.

8.Система по п. 1 или 2, или 6, или 7, отличающаяся тем, что арифметический элемент коммутации содержит два элемента И, элемент НЕ и элемент ИЛИ, причем первые входы элементов И являются соответственно первым и вторым входами арифметического элемента коммутации, выходы нервого и второго элементов И нодк:1ючены соответствен0 по к второму входу второго элемента И. и к входу элемента НЕ, выход которого подключен к второму входу нервого элемента И. нервый и второй входы элемента ИЛИ подключены соответственно к выходам первого и второго элементов И и являются соответственно первым и втооым входами-выходами арифметического элемента коммутации, выход элемента ИЛИ является выходом арифметического элемента коммутации.

9.Система по п. 1 или 2, или 7, огличаю- 0 щаяся тем, что интерфейсный элемент коммутации содержит два элемента И, элемент ИЛИ, элемент НЕ и два ключа, причем первые входы элемептов И являются соответственно первым и вторым входами интерфейсного элемента коммутации, выход нервого

5 элемента И подключен к нервому входу элемента ИЛИ и входу первого ключа, выход которого нодключен к второму входу второго элемента И и является первым входом-выходом интерфейсного элемента коммутации, выход второго элемента И подключен к второму входу элемента ИЛИ и входу второго ключа, выход которого подключен к входу элемента НЕ и яв.тяется вторым входом- выходом интерфейсного эле.мепта коммутации, выход элемента НЕ нодключеп к второму входу нервого элемента И, третий вход которого является третьим входом интерфейсного элемента коммутации, выход элемента ИЛИ явстяется выходом интерфейсного элемента коммутации.

10.Система но н. 1 или 2, отличающаяся Q тем, что блок интерфейса содержит триггер.

четыре элемента И, два элемента НЕ и два ключа, причем первые входы нервого и второго элементов И, вход первого элемента НЕ и вход первого ключа нодключены к входу захвата блока, выход первого элемента НЕ 5 подключен к первому входу третьего элемента И, вторые входы nepBoi o и третьего элементов И нодключег;ы к входу признака захвата блока, выход третьего элемента И

0

5

является выходом признака ответа блока, выход первого элемента И подключен к первому входу четвертого элемента И, выход которого подключен к входу установки триггера, вход сброса которого является входом признака приема блока, нрямой выход триггера подключен к второму входу второго элемента И и входу второго ключа, выход

которого подключен к входу второго элемента НЕ, выход которого подключен к второму входу четвертого элемента И, выход второго элемента И является выходом разреп1ения захвата блока, выходы первого и второго ключей являются соответственно входами- выходами признака запроса и признака занятости блока.

75

о 66

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451713A1 |

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451712A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных комплексах и автоматизированных системах управления на основе мультипроцессорных вычислительных систем. Целью изобретения является увеличение нропускной способности вычислительной системы. Данная цель достигается путем введения в процессоры 2 системы блока 9 регистров, элементов И и ИЛИ, элементов 8 коммутации, регистра 10 номера канала и схемы 11 сравнения. Пропускная способность системы при этом возрастает за счет согласования потоков заявок в блоке регистров, а также за счет обеспечения возможности параллельной работы процессоров по взаимозависимым заявкам. 9 з. i. ф-лы, 14 ил. (Л СО ГЧЭ ел со о: 15

21

г,| ,,Дм 1

1/ -Jf 1/I sir |уJ/ |/Ф Ч/

Запись 5

Запись 6 77 5/Запис резу/1 ь- тата 54

55

92 97

Фиг. 5

Фиг.7

Фиг. 8

Фиг,. 9

(нача/ о

Включение ffjiona 26 по 1 -пи

п f-i гч I If Lfn JO I/ ffVfyn/l

записнающему входу считывание эаявни блон 26

8

включение t/3/ia. 26по 2-нц эаписнаюшеми взвода Считыбаиие se toffpf u из ff S 26

I У5е/1ичемие иа 1 со&ержимок с етчина 23

Передача л/н S cvemvuH 23

и в 21

fjepedat/a воюорни 8 узел Ш

Определение Анп (по fl/к) и запись его ff 2Ъ

5о1по/ нение программы оОреА ёотни 6о/борна S Ъ

i

Запись Af /f ff ff/ioK 2S

icyui. 3)

включение о/юна у по 1-пу запускающему входу- Снятиг cutHoaoS опроса изапра

CfumtiSaHus заявки с шин К, 13 f блок 3

Внлючение б/юна J по г- пи зопискающет 8мву. Снятие сигналЬ опроса, и за просо

считывание Uti/SopHu из блока. 9 f ort 3

5Ж

Обцаботка зОйвки S S/ioxeZ

fui. //

Ctfovg/yg J

Обработки заявки S SJOHC 1

Фиг. 2

Нет (на риг. It)

I йй/доча сигнала запроса

WС итывоние выоорхи с шины 3 ff блок 9 Снятие cusHO/ia запроса

Нет

Ла

cusHQ/ia 6/iOHUpoffxu

j-lQ4a ло} Т

I Бы дач а CUSHQ/IQ опроса из блонщ

Выдача запроса |

С итывание р. v- о. ояВки с шины 1Ъ в блок 9

I

олома Зпо 2-му запусмйющепу ffj(ody. Снятие сиено/го опроса

Ci umb/ffoHueD..o. зая&ни из &/1ОНО 9 о 6/IOH J

I.

бро6отна(чостичноя)зая8н 6d/i.

.3-

Выдоуа си&иола ооращени издл.зХ

- сть

шпрос от последующего Ю14ессора2

2а

&ыаояа сигнала раэрешеиил 8 послед1/ющии процессор Z

BьlaQ a p.O золвни б послео1/ющии процессор2

Ж

5ыоачо сигнал о опроса

ет

Сняпг7ие cc/sнала wnpoca

9иг.Ш

Составитель Н. Захаревич

Редактор С. ПатрушеваТехред И. ВересКорректор М. Шароши

Заказ 1845/49Тираж 673Подписное

ВНИИПИ Государстиемного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж--35, Раушская наб., д. 4/5 Производственно-нолиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Мультипроцессорная система | 1978 |

|

SU742943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-23—Публикация

1985-12-16—Подача