(5) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для формирования и анализа семантических сетей | 1989 |

|

SU1619289A1 |

| Устройство для сопряжения управляющей и управляемых вычислительных машин | 1988 |

|

SU1517033A1 |

| Многоканальное приоритетное устройство | 1980 |

|

SU896624A1 |

| Устройство формирования приоритетов при обращении к общей памяти нескольких устройств | 2019 |

|

RU2710912C1 |

1

Изобретение относится к вычислительной технике и может быть использовано для приоритетного управления обращением к блоку оперативной памяти процессоров двухпроцессорного вычислительного комплекса (ВК).

Известно многоканальное устройство приоритета, содержащее генератор импульсов и элемент И,, в каждом канале - триггер памяти запроса, триггер запроса, триггер разрешения и два элемента И .

Однако функциональные возможности такого устройства ограничены, что обусловлено жестким назначением приоритета, сложностью исполнения, снижением надежности работы мультипроцессорной системы из-за возможного отказа одного из процессоров ВК, что может привести к нарушению доступа к оперативной памяти (ОП) процессора с более низким приоритетом.

Наиболее близким к предлагаемому является многоканальное устройство приоритета, содержащее генератор импульсов, а в каждом канале - триггер запроса, триггер разрешения,два 5 элемента И и элемента ИЛИ 2,

Однако данное устройство и устройства подобные ему, не учитывают характеристик самих процессов, происходящих в процессорах ВК, а именно частоты обращения к отдельным блокам оперативной памяти,- Назначение приоритета часто идет произвольно хотя известно, что во многих случайх

15 процессы равноприоритетны и такое произвольное назначение приоритетов ведет к увеличению конфликтных ситуаций - обращений к одному б/юку оперативной памяти одновременно двух

процессоров, что ведет к снижению надежности.

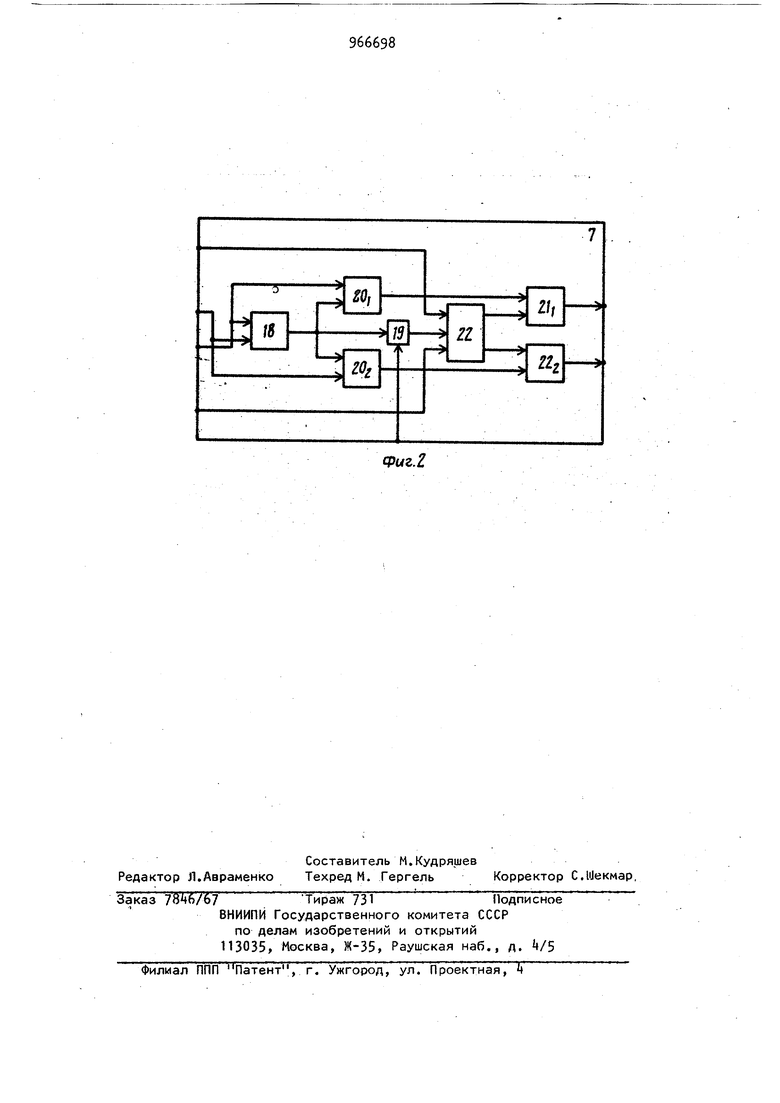

Цель изобретения - повышение надежности устройства. . Поставленная цель достигается тем, что в многоканальное устройство приоритета, содержа1чее два регистра, два дешифратора, а в каждом канале два триггера и первый элемент И, при чем информационные входы первого и второго регистров являются первым и вторым входами заявок устройства, выходы первого и второго регистров соединены с входами первого и второго дешифраторов, выходы первого дешифратора соединены с единичными входами первых триггеров соответству ющих каналов, выходы первых триггеров всех каналов соединены с первыми входами элементов И своих каналов, введены два элемента ИЛИ, два тригге ра, а в каждом канале два блока элементов И, два счетчика, второй элемент И и узел приоритета, причем единичные выходы первого и второго триггеров каналов соединены с -сметными входами первого и второго счетчиков своих каналов, информационные входы первого и второго счетчиков каналов соединены с выходами первого и второго блоков элементов И своих каналов первые входы блоков элементов И каналов соединены с выходами переполнения пер.вого и второго счетчиков своих каналов и с входами сброса первого и второго счетчиков своих каналов, информационные выходы первого и второго счетчиков каналов соединены с вторыми входами второго и первого блоков элементов И своих каналов и с первым и вторым входами узла приоритета своего канала, тактовые входы счетчиков каналов соединены с входом отсутствия обмена устройства и с третьими входами узлов приоритета каналов, первый вход второго элемента И каждого канала соединен с единичным выходом триггера своего канала, вторые входы первого и второго элементов И каналов соединены соответственно с первым и BTopbiM выходами узла приоритета своего канала, нулевые выходу первого и второго триггеров каналбв соединены соответственно с четвертым и пятым входами узла приоритета своего канала, выходы первых элементов и каналов соединены с входами первого элемента ИЛИ, выход которого соединен с единичным входом первого триггера, выход которого является первым информационным выходом устройства, выходы вторых элементов И каналов- соединены с. входами второго элемента ИЛИ, ВЫХОД которого соединен с единичным входом второго триггера, выход которого является вторым информационным выходом устройства, первый и второй входы конца обмена устройства соединены соответственно с нулевыми входами первого и второго триггеров, с нулевыми входами первого и второго триггеров каналов и с тактовыми входами первого и второго регистров, единичные входы вторых триггеров каналов соединены с соответствующими выходами второго дешифратора. Кроме того, узел приоритета содержит два элемента ИЛИ, четыре элемента И и схему сравнения, причем первый и второй входы узла соединены соответственно с первым и вторым входами схемы сравнения, первый и второй выходы которой соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с выходами третьего и четвертого элементов И, первые входы которых соединены с выходом первого элемента ИЛИ и с первым входом второго элемента ИЛИ, второй вход которого соединён с третьим входом узла, четвертый вход коTopof o соединен с вторым входом третьего элемента И и с первым входом первого элемента ИЛИ, второй вход которого соединен с пятым входом узла и с вторым входом третьего элемента И, выходы первого и второго элементов И являются соответственно первым и вторым выходами узла. На фиг, 1 йриведена структурная схема устройства; на фиг. 2 - структурная схема узла приоритета. Многоканальное устройство приоритета (фиг. 1) содержит регистры Ъ li дешифраторы 2 и 9., каналы 3x1 и 3м, триггеры /г и 2. каналов, счетЧики 5, и 5i каналов, блоки 6 и 6 элементов И каналов, узел 7 приоритета канала, элементы 8, 8 каналов-, элементы ИЛИ 9/i и 9, три|- геры 10, 10,, информационные выходы 11 и 12 устройства, входы 13 и 1 t конца обмена устройства, вход 15 отсутствия обмена устройства, запросные входы 1б и 17 устройства. Узел приоритета (фиг. 2) содержит элементы ИЛИ 18 и 19, элементы И 20, , 2(, 21 схему срав нения 22. 5 Устройство работает следующим об разом. В начальный момент регистры запросов 1 триггеры запросов Ц каналов, триггеры разрешения 10 обнулены. При поступлении запроса от одно го из процессоров (например, номер 1) на обмен с оперативной памятью (ОП) на регистр 1 заносится код, соответствующий номеру требуемого блока ОП. Сигнал высокого уровня с одного из выходов дешифратора 2 поступает на единичный вход триггера запросов Ц , перебрасывая его в единичное состояние. С единичного выхода триггера запросов 4 сигнал высокого уровня, поступает на счетный вход счетчика запросов 5 для з прашиваемого процессора, добавляя к его содержимому единицу, и на первый вход элемента И 8. Сигналы низкого уровня с нулевого выхода триггеров запросов k и (закрывают элемент И 20 блока разрешения конфликтных ситуаций и открывают элемент И 20/t. Элемент ИЛИ 19 управ ляет работой схемы сравнения 22. Сигнал высокого уровня с выхода эле мента ИЛИ 18 через элемент ИЛИ 19 з прещает работу схемы 22, и с первого и второго выходов схемы сравнения 22 снимаются сигналы низкого уровня. С открытого элемента И 20 высокий потенциал поступает на откр тый триггером запросов 4, ПО первом И -- входу элемент И . Пройдя через эл мент ИЛИ 9, сигнал высокого уровня перебрасывает в единичное состояние триггер 10 , тем самым разрешая обмен с выбранным блоком ОП запросившего процессора,. Если во время выпол нения операции обмена к данному блок ОП поступает запрос от другого процессора, в регистре 1 и в триггере запросов 2. зафиксируется обращение В момент завершения обмена ранее запросившеГо процессора с ОП на вход 13 или 1 выдается сигнал высокого уровня, который, поступив на управпящий вход регистра запросов 1-,, ну левые входы триггеров запросов Ц процессора 1, нулевой вход триггера разрешения 10 , сбрасывает их в исходное нулевое состояние, тем самым разрешая обмен с блоком ОП процессора 2, находящегося в состоянии ожида ния. Сигнал с входа 15 разрешает или запрещает работу счетчиков 5. 8 В случае одновременного обращения процессоров к одному блоку ОП сигналы низкого уровня с нулевых выходов три1- геров запросов Ц и i закрывают элементы И .П и 20 узла 7, с входа 1 ij на элемент ИЛИ 13 подается низкий потенциал, свидетельствующий об отсутствии обмена между процессорами и ОП. Низкий уровень сигнала с-выхода элемента ИЛИ 19 открывает схему Т для сравнения содержимого первого и второго счетчиков запросов 5/i и 5 /1 -2 Высокий потенциал возбуждается на том из выходов схемы сравнения, номер которого соответствует номеру счетчика запросов 5 с меньшим содержимым, а при одинаковом содержимом возбуждается выход с наименьшим номером. Сигнал высокого уровня с выхода схемы сравнения Т поступает через один из элементов И 21 и 21,,, элемент И 8, ИЛИ на триггер 10, соответствующий процессору с более высоким на момент конфликтной ситуации приоритетом (для него содержимое счетчика 5 имеет меньшее значение). При ведении обмена с ОП на входы узлов 7 подается сигнал высокого уровня с входа 15 что исключает из работы схемы сравнения соответствующего блока ОП. Для предохранения от переполнения счетчиков запросов 5 в устройстве имеются блоки 6, 2. В случае полного заполнения одного из счетчиков запросов 5 сигнал высокого уровня с единичного выхода триггера переполнения счетчика запросов поступает в соответствующий блок 6. С информационного выхода другого счетчика 5 через открытый блок 6 в код содержимого счетчика поступает информация на инверсные входы (нулевые входы триггеров счетчика) заполнившегося счетчика запросов 5, тем самым обеспечивая запись кода, дополняющего переносимый до максимального. Сигнал, открывающий блок 6, сбрасывает в нулевое состояние счетчик с переносимым кодом. Таким образом, обеспечивается сохранение динамических приоритетов процессоров,при заполнении счетчиков запросов. Применение изобретения позволяет повысить надежность устройства, так как. сокращается число конфликтных ситуаций. 7 Формула изобретения 1. Многоканальное устройство при оритет а, срдержащее два регистра, два дешифратора, а в каждом канале два триггера и первый элемент И, причем информационные входы первого и второго регистров являются первым и вторым входами заявок устройства, выходы первого и второго регист ров соединены с входами первого и второго дешифраторов, выходы первого дешифратора соединены с единичными входами первых триггеров соответствующих каналов, выходы первых триггеров всех каналов соединен с первыми входами элементов И своих каналов, отличающееся тем, что, с целью повышения надежности, устройство содержит два элемента ИЛИ, два- триггера, а в каждом канале два блока элементов И, два счетчика второй элемент И и узел приоритета, причем единичные выходы первого и второго триггеров каналов соединены с счетными входами первого и второго счетчиков своих -каналов, информационные входы первого и второго счетчиков каналов соединены с выходами первого и второго блоков элементов И своих каналов, первые входы блоков элементо И каналов соединены с выходами переполнения первого и второго счетчиков своих каналов и с входами сбр са первого и второго счетчиков своих каналов, информационные выходы первого и второго счетчиков каналов соединены с вторыми входами вто рого и первого блоков элементов И с их каналов и с первым и вторым входами узла приоритета своего канала, тактовые входы счетчиков каналов со динены с входом отсутствия обмена устройства и с третьими входами узлов приоритета каналов, первый вход второго элемента И каждого канала соединен с единичным выходом триггера своего канала, вторые входы пе вого и второго элементов И каналов соединены соответственно с первым и вторым выходами узла приоритета сво его канала, нулевые выходы первого и второго триггеров каналов соединены соответственно с четвертым и пятым входами узла приоритета своег 88 канала, выходы первых элементов И каналов соединены с входами первого элемента ИЛИ, выход которого соединен с единичным,входом первого триггера, выход которого является первым информационным выходом устройства, выходы вторых элементов И каналов соединены с входами второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера, выход которого является вторым информационным выходом устройства, первый и второй входы, конца обмена устройства соединены соответственно с нулевыми входами первого и второго триггеров, с нулевыми входами первого и второго триггеров каналов и с тактовыми входами первого и второго регистров, единичные входы вторых триггеров каналов соединены с соответствующими выходами второго дешифратора. 2. Устройство по п. 1, о т л и ч а ю 1Ц е е с я тем, что узел приоритета содержит два элемента ИЛИ, четыре элемента И и схему сравнения, причем первый и второй входы узла соединены соответственно с первым и вторым входами схемы сравнения, первый и второй выходы которой соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены соОтветственно с выходами третьего и четвертого элементов И, первые входы которых соединены с выходом первого элемента ИЛИ и с первым входом второго элемента ИЛИ, второй вход которого соединен с третьим входом узла, четвертый вход которого соединен с вторым входом третьего элемен|та И и с первым входом первого элемента ИЛИ, второй вход которого соединен с пятым входом узла и с вторым входом третьего элемента И, выходы первог о и второго элементов И являются соответственно первым и вторым выходами узла. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № Ц76566, кл. G Об F 13/00, 9Л6, 1975. . . 2,Авторское свидетельство СССР ff 656062, кло G Об F , 1979 (прототип).

(3 П

пmlМ

J/rT л. -J

Авторы

Даты

1982-10-15—Публикация

1981-01-14—Подача