Изобретение относится к радиотехнике и вычислительной технике и предназначено для использования в комплексах автоматизированных систем управления сетями многоканальной радиосвязи.

Известен автономный вероятностный автомат, содержащий генератор тактовых импульсов, два генератора случайных импульсов, два блока элементов И, три регистра, блоки задания закона распределения и памяти (см. авт. св. СССР N734701, G 06 F 15/20, 1980, бюл.18).

Однако данный вероятностный автомат моделирует однородную цепь Маркова, что сужает его функциональные возможности.

Известен вероятностный автомат, содержащий генератор тактовых импульсов, элементы И и ИЛИ, регистр сдвига, блоки памяти и задания времени (см. авт. св. СССР N1045232, G 06 F 15/36, 1983, бюл.36).

Однако данный вероятностный автомат моделирует неуправляемые полумарковские цепи без учета внешних управляющих воздействий, что не позволяет применять его для анализа реально протекающих процессов в сетях многоканальной радиосвязи, поскольку эти процессы в большинстве своем управляемы.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является вероятностный автомат (см. патент РФ N2099781, G 06 F 17/00, 1997, бюл.35), содержащий блок элементов И, блок памяти, блок задания времени, элемент ЗАПРЕТ, элемент ИЛИ, датчик случайной последовательности, блок формирования корректирующей последовательности, блок коррекции, блок формирования значений матрицы, блок формирования значений индикаторов, блок управления, дешифратор и генератор тактовых импульсов, выход которого соединен с прямым входом элемента ЗАПРЕТ и первым входом блока задания времени, выходы которого являются выходами автомата и подключены к входам элемента ИЛИ, выход которого соединен с инверсным входом элемента ЗАПРЕТ, выход которого подключен к входу блока элементов И, выходы которого соединены с входами блока памяти, выходы которого подключены к группе входов блока задания времени, выход датчика случайной последовательности подключен к первой группе входов блока коррекции, группа выходов которого соединена с первой группой входов блока формирования значений индикаторов, вторая группа входов блока коррекции подключена к группе выходов блока формирования корректирующей последовательности, группа входов которого соединена с группой выходов блока формирования значений матрицы, подключенной к третьей группе входов блока коррекции и к второй группе входов блока формирования значений индикаторов, синхронизирующий вход которого соединен с выходом элемента ЗАПРЕТ, подключенным к первому входу блока управления, второй вход которого является входом автомата, а выход соединен с входом блока формирования значений матрицы и с входом дешифратора, выход которого подключен к второму входу блока задания времени, группа входов блока элементов И соединена с группой выходов блока формирования значений индикаторов, третья группа входов которого соединена с группой выходов блока памяти.

Достоинством прототипа является его способность моделировать управляемые полумарковские цепи, формируемые с учетом шумов наблюдения и на основе гауссова представления процессов, реально протекающих в управляемой системе связи. Однако прототип имеет недостаток - невозможность динамической коррекции границ состояний моделируемого процесса. Это связано с тем, что моделирование управляемых полумарковских цепей осуществляется с заранее заданными границами состояний моделируемого случайного процесса, что исключает применение прототипа для динамического анализа реальных сетей многоканальной радиосвязи. Данный вероятностный автомат позволяет моделировать управляемые полумарковские процессы с раз и навсегда заданными пороговыми значениями (границами) состояний, в то время как большое количество процессов, реально протекающих в управляемых сетях многоканальной радиосвязи могут в динамике функционирования изменять пороговые значения своих состояний под влиянием управляющих воздействий или внешних факторов. Например, оператор управляемой многоканальной сети радиосвязи с целью предотвращения перегрузки системы множественного доступа при резком возрастании трафика может изменить требования по времени доставки сообщений, централизованно ограничить время информационного обмена каждого абонента непосредственно в ходе функционирования сети, что приводит к изменению одного их основных критериев ее эффективной работы - вероятности своевременной доставки сообщений. Динамичное изменение параметров такого класса, помимо собственно управляемых параметров, с точки зрения математической модели процесса функционирования сети и есть изменение пороговых значений состояний моделируемого случайного процесса, которое приводит к изменению всего вероятностно-временного механизма перехода случайного процесса из состояния в состояние [1, 3, 4].

Целью предлагаемого изобретения является создание управляемого вероятностного автомата, способного моделировать управляемые полумарковские цепи с динамической коррекцией пороговых значений (границ) состояний моделируемых случайных процессов.

Указанная цель достигается тем, что в известный вероятностный автомат, содержащий датчик случайной последовательности, блок коррекции, блок формирования значений матрицы, блок управления, блок формирования значений индикаторов, блок элементов И, блок памяти, блок задания времени, дешифратор, элемент ЗАПРЕТ, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с прямым входом элемента ЗАПРЕТ и тактовым входом блока задания времени, группа выходов которого является группой выходов автомата и подключена к группе входов элемента ИЛИ, выход которого соединен с инверсным входом элемента ЗАПРЕТ, выход которого подключен к тактовым входам блока элементов И, блока формирования значений индикаторов и блока управления, второй вход которого является входом автомата, а управляющий выход подключен к входам дешифратора и блока формирования значений матрицы, группа выходов блока формирования значений индикаторов соединена с группой входов блока элементов И, выходы которого подключены к входам блока памяти, группа выходов которого соединена с группой входов блока задания времени, управляющий вход которого подключен к выходу дешифратора, дополнительно введены блок формирования нецелочисленных значений индикаторов и блок пороговых устройств. Группа управляющих входов блока формирования нецелочисленных значений индикаторов соединена с выходами блока формирования значений матрицы, группа его интерполяционных входов подключена к выходам блока памяти, а группа его выходов соединена с группой вспомогательных входов блока формирования значений индикаторов и с группой информационных входов блока коррекции, стартовый вход которого подключен к выходу датчика случайной последовательности. Выход блока коррекции соединен с входом блока пороговых устройств, выходы которого подключены к информационным входам блока формирования значений индикаторов Пороговые выходы блока управления параллельно подключены к пороговым входам блока коррекции и блока пороговых устройств.

Блок формирования нецелочисленных значений индикаторов состоит из группы первичных сумматоров, группы умножителей и группы оконечных сумматоров Входы первичных сумматоров попарно соединены друг с другом, параллельно подключены к третьим входам оконечных сумматоров и являются управляющими входами блока. Выходы первичных сумматоров подключены к первым входам умножителей, вторые входы которых являются интерполяционными входами блока, а выходы умножителей попарно соединены с первыми и вторыми входами оконечных сумматоров, выходы которых являются выходами блока.

Блок коррекции состоит из группы вычислителей первичных коэффициентов, группы вычислителей вторичных коэффициентов, вычислителя отклонений математического ожидания, вычислителя отклонений дисперсии, сумматора и усилителя. Входы вычислителей первичных коэффициентов являются информационными входами блока, а их выходы соединены с входами вычислителей вторичных коэффициентов, выходы которых образуют группу информационных входов вычислителя отклонений математического ожидания, вторая группа входов которого является группой пороговых входов блока. Первый и второй выходы вычислителя отклонений математического ожидания подсоединены к первому и второму входу вычислителя отклонений дисперсии, а третий выход вычислителя отклонений математического ожидания подключен к третьему входу вычислителя отклонений дисперсии и второму входу сумматора, первый вход которого является стартовым входом блока, а выход которого соединен с первым входом усилителя. Второй вход усилителя подключен к выходу вычислителя отклонений дисперсии, а выход является выходом блока коррекции.

Блок управления состоит из управляющего постоянного запоминающего устройства (ПЗУ), порогового ПЗУ и счетчика. Выходы счетчика подключены к тактовым входам управляющего и порогового ПЗУ, первый и второй входы счетчика соединены со сбрасывающими выходами управляющего и порогового ПЗУ, третий вход счетчика является тактовым входом блока. Информационные входы управляющего и порогового постоянных запоминающих устройств соединены между собой и являются вторым входом блока, выход управляющего ПЗУ является управляющим выходом блока, группа выходов порогового ПЗУ является группой пороговых выходов блока.

Блок пороговых устройств состоит из группы схем сравнения, сумматора и ПЗУ. Параллельно подключенные первые входы схем сравнения являются информационным входом блока, вторые входы схем сравнения составляют группу пороговых входов блока. Выходы схем сравнения соединены с входами постоянного запоминающего устройства и входами сумматора, выход которого подключен к считывающему входу постоянного запоминающего устройства, выходы которого являются выходами блока.

Блок формирования значений индикаторов состоит из группы предварительных сумматоров, группы умножителей, группы компенсационных сумматоров и ПЗУ. Первые входы умножителей составляют группу информационных входов блока, вторые входы умножителей соединены с выходами предварительных сумматоров, первые входы которых являются вспомогательными входами блока и параллельно подключены ко вторым входам компенсационных сумматоров. Вторые входы предварительных сумматоров подключены к выходам ПЗУ, вход которого является тактовым входом блока Выходы умножителей соединены с первыми входами компенсационных сумматоров, выходы которых являются выходами блока формирования значений индикаторов.

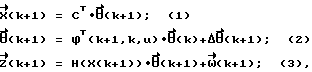

Принцип создания предлагаемого управляемого вероятностного автомата основан на известных результатах теории переменных состояния и теории марковских процессов, изложенных в работах [1 - 4]. Анализ данных работ позволяет применить для аналитического вероятностно-временного описания системы показателей качества функционирования сетей многоканальной радиосвязи аппарат управляемых цепей Маркова в форме разностных стохастических уравнений. В общем случае (для цепи Маркова) разностные стохастические уравнения имеют вид

причем выражение (1) - уравнение состояния для вектора отсчетов процесса X на каждом (k+1) шаге функционирования сети, где C - матрица-строка возможных значений процесса, a  - вектор индикаторов состояния моделируемого процесса, элементы этого вектора принимают значения

- вектор индикаторов состояния моделируемого процесса, элементы этого вектора принимают значения

Пороговые значения (границы) состояний процесса задаются в общем случае заранее, в предлагаемом вероятностном автомате - в ходе функционирования устройства. Выражение (2) - уравнение состояния для вектора индикаторов состояния на (k+1) шаге, где ϕт(k+1,k,u) - матрица вероятностей перехода процесса из одного состояния в другое, а  - вектор значений приращения индикаторов состояния, компенсирующий нецелочисленную часть уравнения (2). Выражение (3) - уравнение наблюдения за процессом, где H(X(k+1)) - матрица-строка наблюдаемых значений процесса, a

- вектор значений приращения индикаторов состояния, компенсирующий нецелочисленную часть уравнения (2). Выражение (3) - уравнение наблюдения за процессом, где H(X(k+1)) - матрица-строка наблюдаемых значений процесса, a  - вектор белых шумов наблюдения с нулевым средним и матрицей дисперсии δω(k+1).

- вектор белых шумов наблюдения с нулевым средним и матрицей дисперсии δω(k+1).

Анализ выражений позволяет сделать вывод о технической возможности реализации получения оценки состояния управляемого марковского процесса с динамически изменяемыми пороговыми значениями (границами) этих состояний.

Построение управляемого вероятностного автомата на основе предложенного принципа работы позволяет поучить преимущество перед прототипом, обеспечивая способность моделировать управляемые полумарковские цепи с динамической коррекцией пороговых значений (границ) состояний моделируемых случайных процессов. Это существенно расширяет функциональные возможности устройства, позволяя моделировать процессы, происходящие в реальных сетях многоканальной радиосвязи, с учетом наличия каналов динамического управления параметрами, а значит и границами состояний сетей такого класса.

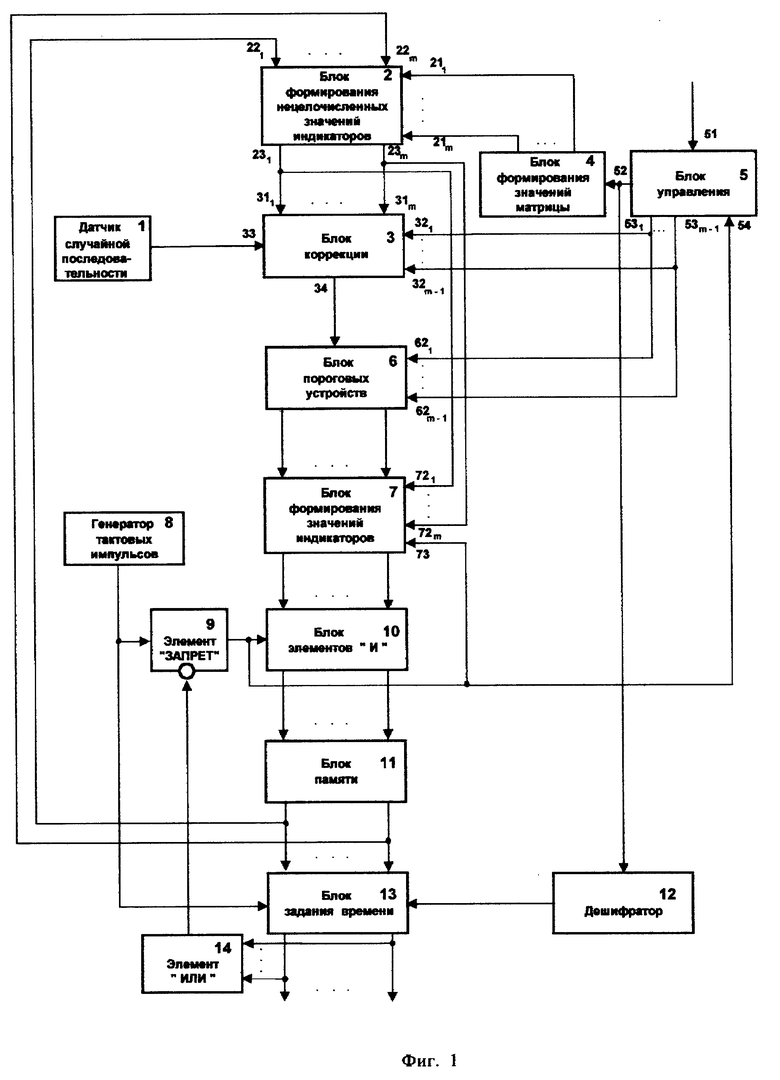

Заявленное устройство поясняется чертежами, на которых представлены:

на фиг. 1 - структурная схема управляемого вероятностного автомата;

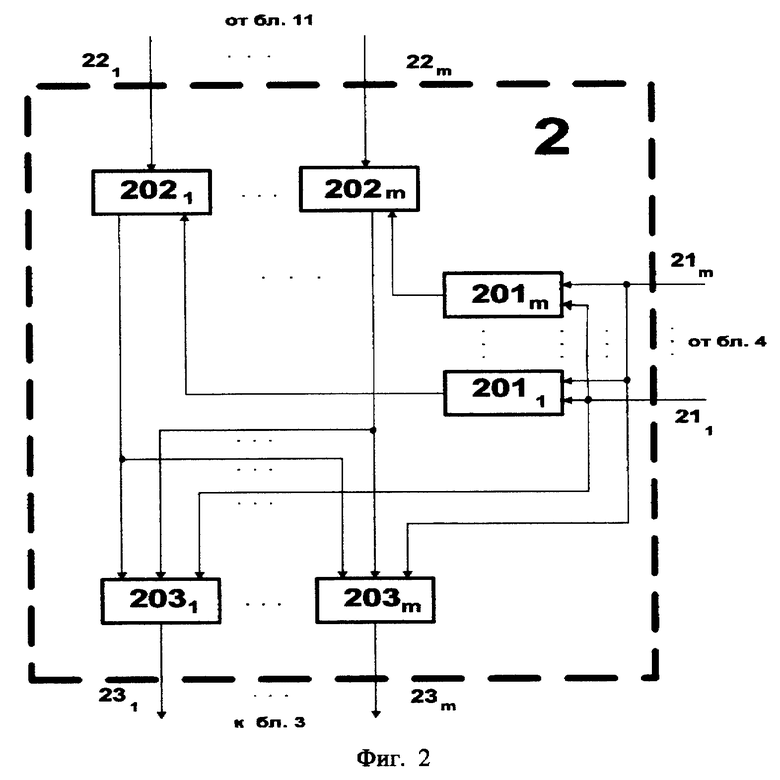

на фиг. 2 - структурная схема блока формирования нецелочисленных значений индикаторов,

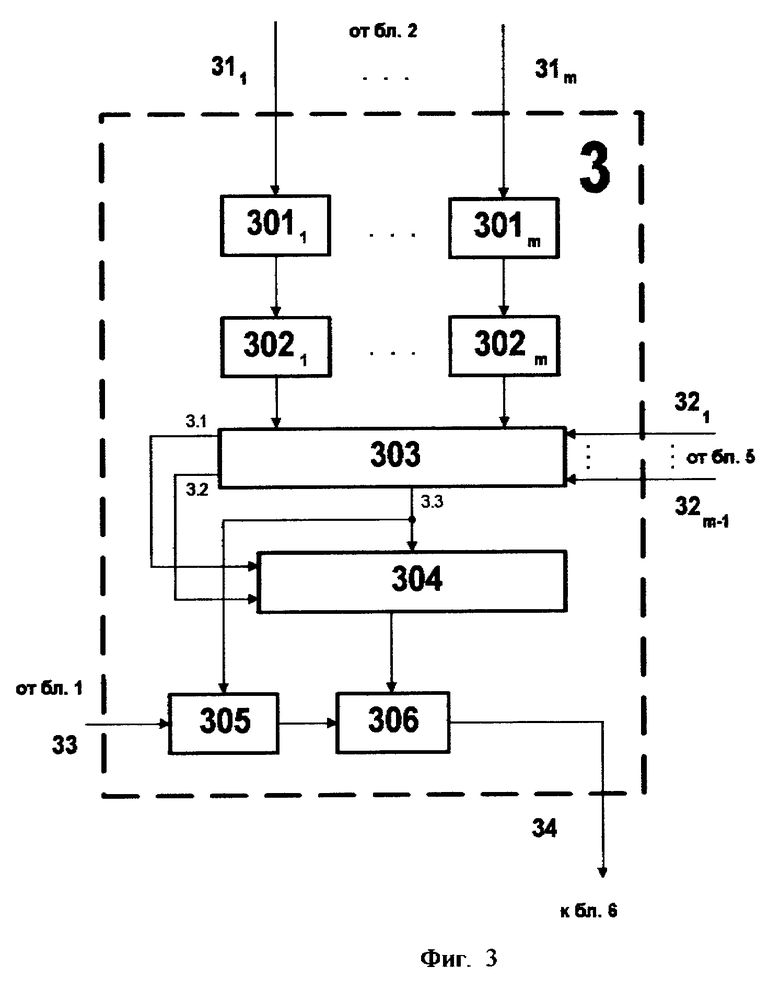

на фиг. 3 - структурная схема блока коррекции;

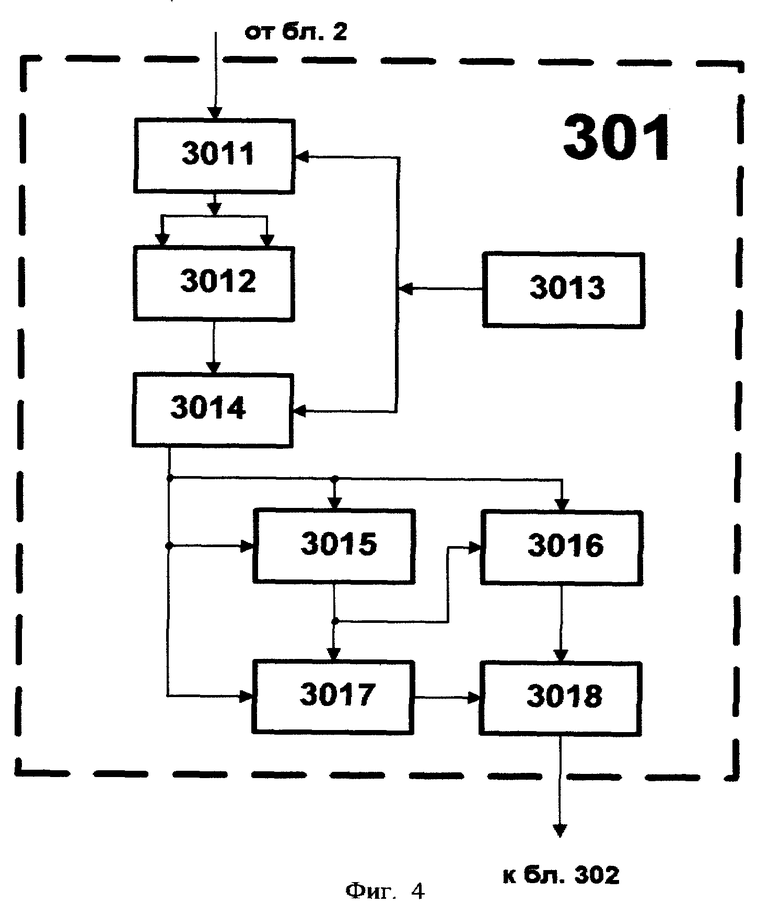

на фиг. 4 - структурная схема вычислителя первичных коэффициентов;

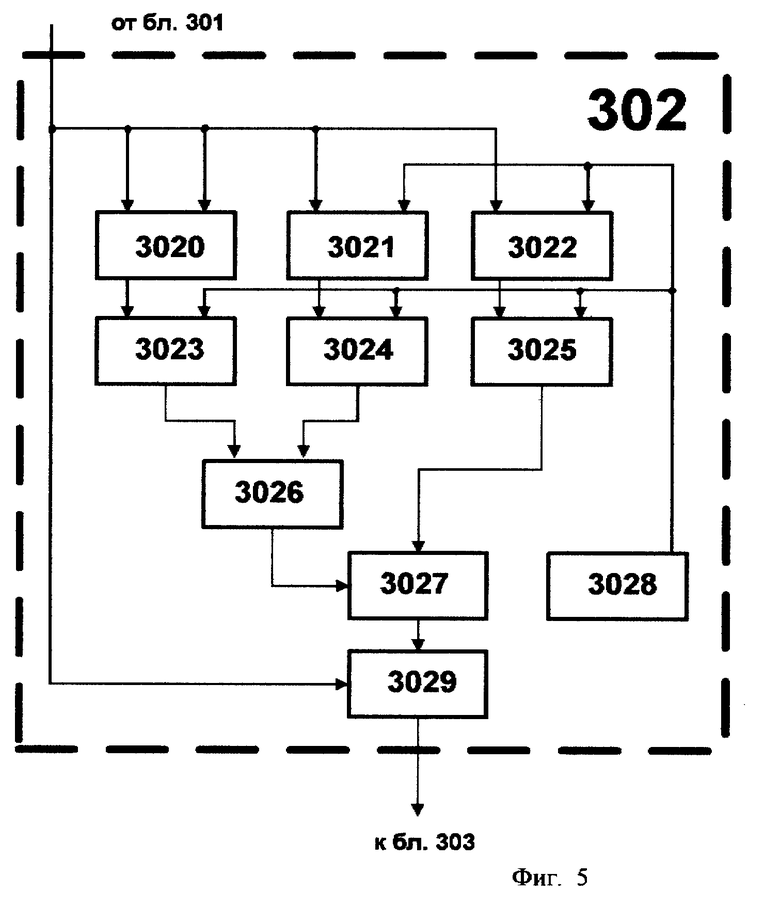

на фиг. 5 - структурная схема вычислителя вторичных коэффициентов;

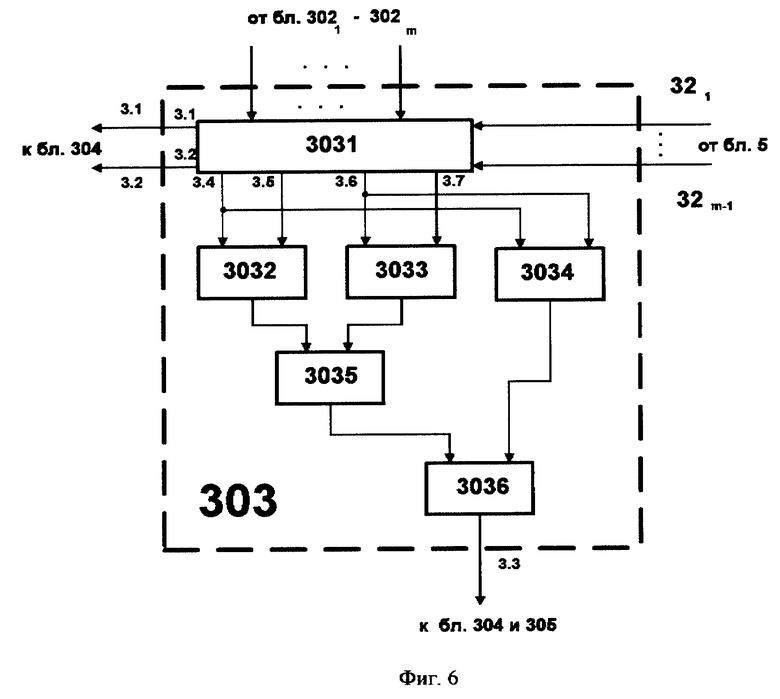

на фиг. 6 - структурная схема вычислителя отклонений математического ожидания;

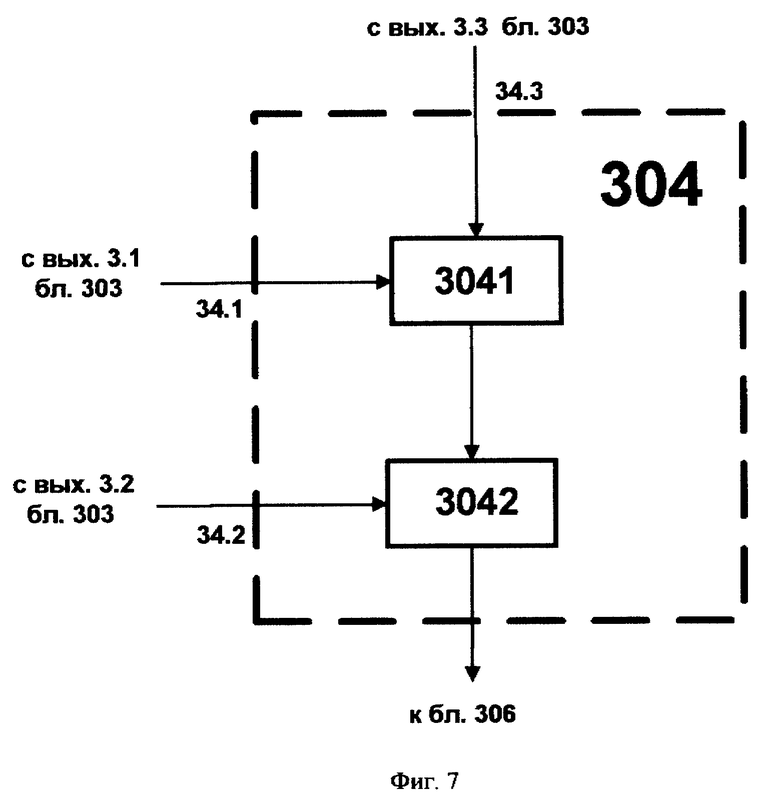

на фиг. 7 - структурная схема вычислителя отклонений дисперсии;

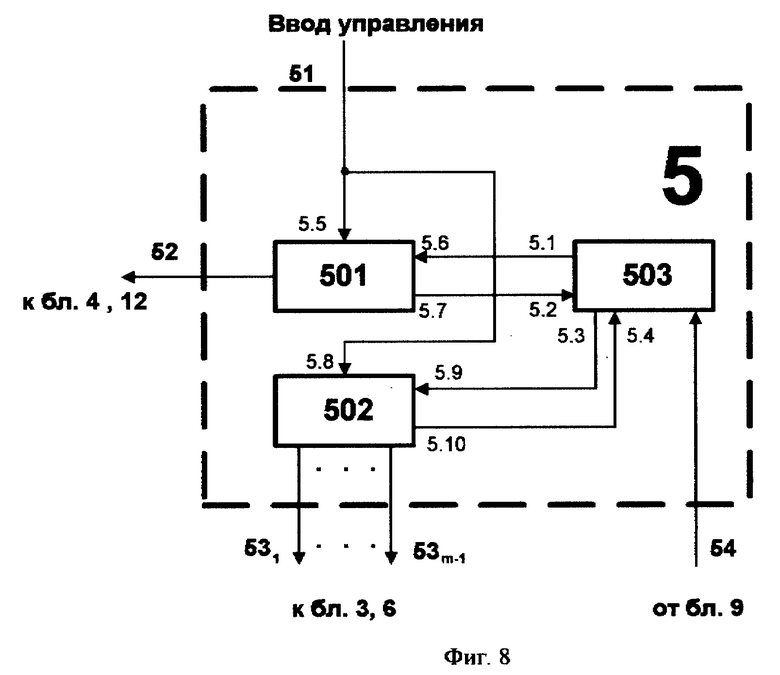

на фиг. 8 - структурная схема блока управления;

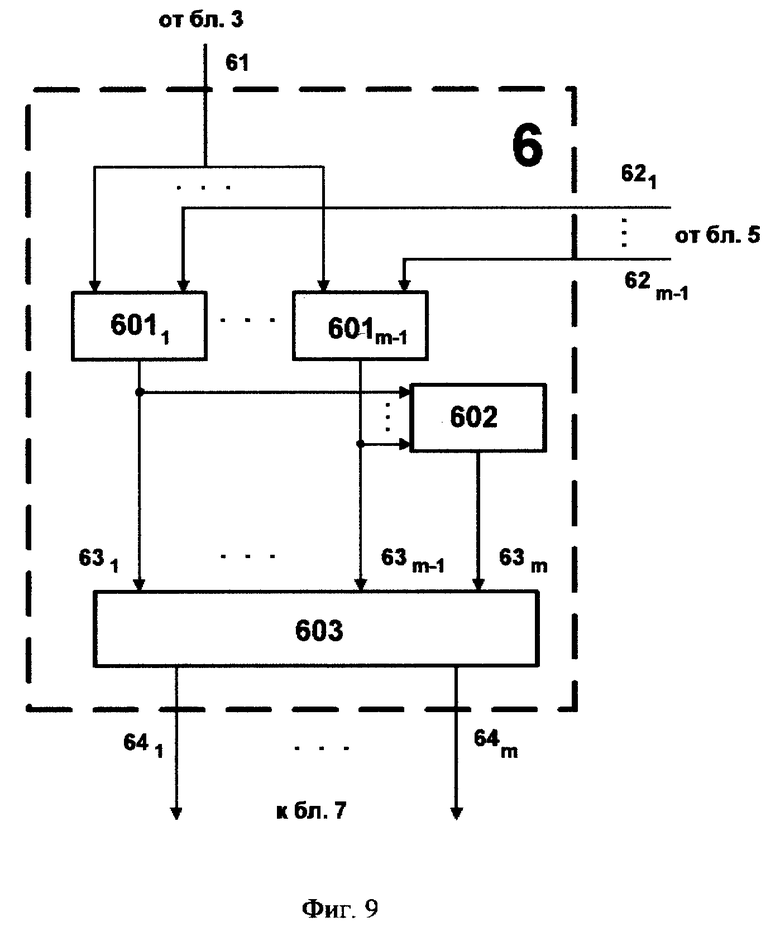

на фиг. 9 - структурная схема блока пороговых устройств;

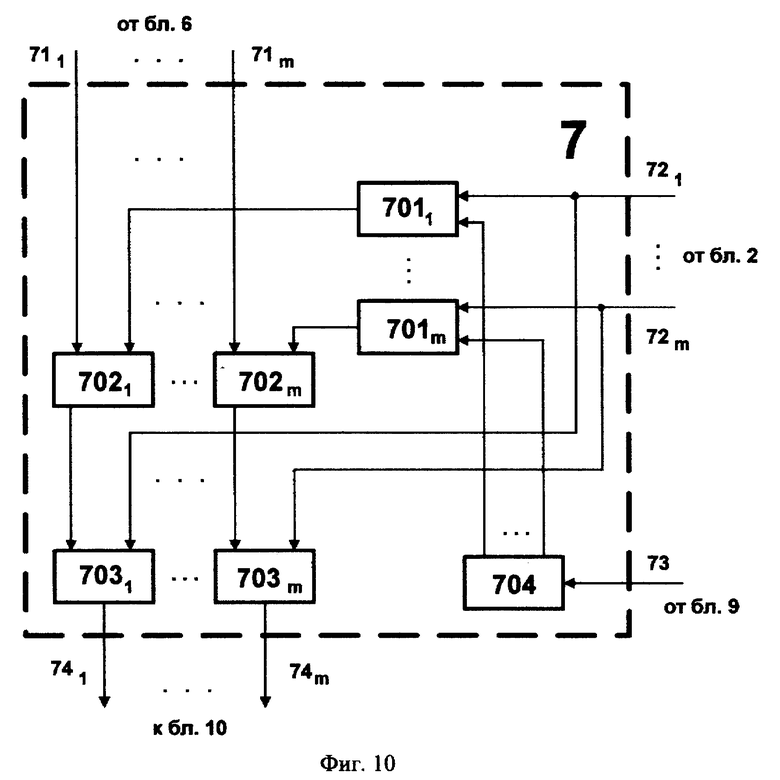

на фиг. 10 - структурная схема блока формирования значений индикаторов.

Вероятностный автомат, изображенный на фиг. 1 состоит из датчика случайной последовательности 1, блока формирования нецелочисленных значений индикаторов 2, блока коррекции 3, блока формирования значений матрицы 4, блока управления 5, блока пороговых устройств 6, блока формирования значений индикаторов 7, генератора тактовых импульсов 8, элемента ЗАПРЕТ 9, блока элементов И 10, блока памяти 11, дешифратора 12, блока задания времени 13, элемента ИЛИ 14. Выход генератора тактовых импульсов 8 соединен с прямым входом элемента ЗАПРЕТ 9 и тактовым входом блока задания времени 13, группа выходов которого является группой выходов автомата и подключена к группе входов элемента ИЛИ 14, выход которого соединен с инверсным входом элемента ЗАПРЕТ 9. Выход элемента ЗАПРЕТ 9 подключен к тактовым входам блока элементов И 10, блока формирования значений индикаторов 7 и блока управления 5. Второй вход блока управления 5 является входом автомата, а управляющий выход подключен к входам дешифратора 12 и блока формирования значений матрицы 4. Группа выходов блока формирования значений индикаторов 7 соединена с группой входов блока элементов И 10, выходы которого подключены к входам блока памяти 11, группа выходов которого соединена с группой входов блока задания времени 13 и группой интерполяционных входов блока формирования нецелочисленных значений индикаторов 2. Управляющий вход блока задания времени 13 подключен к выходу дешифратора 12. Группа управляющих входов блока формирования нецелочисленных значений индикаторов 2 соединена с выходами блока формирования значений матрицы 4, а группа его выходов соединена с группой вспомогательных входов блока формирования значений индикаторов 7 и группой информационных входов блока коррекции 3. Стартовый вход блока коррекции 3 подключен к выходу датчика случайной последовательности 1, а выход блока коррекции 3 соединен с входом блока пороговых устройств 6, выходы которого подключены к информационным входам блока формирования значений индикаторов 7. Пороговые выходы блока управления 5 параллельно подключены к пороговым входам блока коррекции 3 и блока пороговых устройств 6.

Под "группой" (входов, выходов, сумматоров, умножителей, схем сравнения и т.п.) понимается их установленное для конкретного вероятностного автомата количество - может быть от 3 (трех) до 20 (двадцати) включительно:

m = {3,4,5,6,7,8,9,10,...,18,19,20}.

Блок формирования нецелочисленных значений индикаторов 2 (фиг. 2) состоит из группы первичных сумматоров 2011 - 201m, группы умножителей 2021 - 202m и группы оконечных сумматоров 2031 - 203m. Входы первичных сумматоров 2011 - 201m попарно соединены друг с другом, параллельно подключены к третьим входам оконечных сумматоров 2031 - 203m и являются управляющими входами 211 - 21m блока. Выходы первичных сумматоров 2011 - 201m подключены к первым входам умножителей 2021 - 202m, вторые входы которых являются интерполяционными входами 221 - 22m блока, а выходы умножителей 2021 - 202m попарно соединены с первыми и вторыми входами оконечных сумматоров 2031 - 203m. Выходы оконечных сумматоров 2031 - 203m являются выходами 231 - 23m блока формирования нецелочисленных значений индикаторов 2. Блок 2 реализуется в виде арифметического устройства, элементы которого хорошо известны и построены идентично приведенным в литературе:

первичные 2011 - 201m сумматоры - [5];

умножители 2021 - 202m - [6, с. 181-184, рис. 5.27];

оконечные 2031 - 203m сумматоры - [6, с. 173-175, рис. 5.16].

Блок коррекции 3, представленный на фиг. 3, состоит из группы вычислителей первичных коэффициентов 3011 - 301m, группы вычислителей вторичных коэффициентов 3021 - 302m, вычислителя отклонений математического ожидания 303, вычислителя отклонений дисперсии 304, сумматора 305 и усилителя 306. Входы вычислителей первичных коэффициентов 3011 - 301m являются информационными входами 311-31m блока, а их выходы соединены с входами вычислителей вторичных коэффициентов 3021 - 302m, выходы которых образуют группу информационных входов вычислителя отклонений математического ожидания 303, вторая группа входов которого является группой пороговых входов 321 - 32m-1 блока. Первый 3.1 и второй 3.2 выходы вычислителя отклонений математического ожидания 303 подсоединены к первому и второму входу вычислителя отклонений дисперсии 304, а третий 3.3 выход вычислителя отклонений математического ожидания 303 подключен к третьему входу вычислителя отклонений дисперсии 304 и второму входу сумматора 305, первый вход которого является стартовым входом 33 блока. Выход сумматора 305 соединен с первым входом усилителя 306, второй вход усилителя 306 подключен к выходу вычислителя отклонений дисперсии 304, а выход усилителя 306 является выходом 34 блока коррекции 3. Сумматор 305 блока коррекции 3 может быть технически реализован, как показано в литературе [5]. Усилитель 306 блока коррекции 3 может быть реализован на базе умножителя с повышенным быстродействием, подробно описанного в литературе [6, с.185-186, рис. 5.31].

Вычислитель первичных коэффициентов 301 (фиг. 4) блока коррекции 3 состоит из сумматора 3011, умножителя 3012, ПЗУ 3013, делителя 3014, двух умножителей 3015 и 3016, двух сумматоров 3017 и 3018. Выход ПЗУ 3013 подключен ко второму входу сумматора 3011 и второму входу делителя 3014, первый вход сумматора 3011 является входом вычислителя первичных коэффициентов 301, а выход сумматора 3011 соединен с первым и вторым входами умножителя 3012, выход которого подключен к первому входу делителя 3014, выход которого соединен с первым и вторым входами умножителя 3015, первым входом умножителя 3016 и первым входом сумматора 3017, выход умножителя 3015 подключен к второму входу умножителя 3016 и второму входу сумматора 3017, выходы которых соединены с первым и вторым входами сумматора 3018, выход которого является выходом вычислителя первичных коэффициентов 301. Технически сумматоры 3011, 3017, 3018 и умножители 3012, 3015, 3016 реализуются аналогично первичным сумматорам и умножителям блока формирования нецелочисленных значений индикаторов 2. Постоянное запоминающее устройство (ПЗУ) 3013 реализуется в соответствии с описанием, представленным в работе [7, с.197-199, рис.6.10]. Делитель 3014 может быть технически реализован в виде счетчика-делителя, как описано в [7, с. 175-182, рис.5.46 (б)].

Вычислитель вторичных коэффициентов 302 блока коррекции 3, представленный на фиг. 5, состоит из умножителей 3020, 3021, 3022 и 3023, сумматоров 3024, 3025, 3026, делителя 3027, ПЗУ 3028 и сумматора 3029, причем вход вычислителя вторичных коэффициентов 302 является первым и вторым входом умножителя 3020, первым входом умножителя 3021, первым входом умножителя 3022 и первым входом сумматора 3029, второй вход которого подключен к выходу делителя 3027, а выход является выходом вычислителя вторичных коэффициентов 302. Выход ПЗУ 3028 подключен ко вторым входам умножителей 3021, 3022, 3023 и ко вторым входам сумматоров 3024 и 3025. Выход умножителя 3020 подключен к первому входу умножителя 3023, выход которого соединен с первым входом сумматора 3026. Выход умножителя 3021 подключен к первому входу сумматора 3024, выход которого подключен ко второму входу сумматора 3026, выход которого соединен с первым входом делителя 3027. Выход умножителя 3022 подключен к первому входу сумматора 3025, выход которого соединен со вторым входом делителя 3027. Сумматоры 3024-3026, 3029, умножители 3020 - 3023, делитель 3027 и ПЗУ 3028 могут быть технически реализованы аналогично сумматорам, умножителям, делителю и ПЗУ вычислителя первичных коэффициентов 301.

Вычислитель отклонений математического ожидания 303 (фиг. 6) блока коррекции 3 состоит из сдвигающего регистра 3031, двух умножителей 3032 и 3033, двух сумматоров 3034 и 3035, делителя 3036. Группа информационных входов сдвигающего регистра 3031 является группой информационных входов вычислителя отклонений математического ожидания 303, группа пороговых входов сдвигающего регистра 3031 является группой пороговых входов 321 - 32m-1 блока коррекции 3. Первый 3.1 и второй 3.2 выходы сдвигающего регистра 3031 являются первым 3.1 и вторым 3.2 выходами вычислителя отклонений математического ожидания 303, выход 3.4 сдвигающего регистра 3031 подсоединен к первому входу умножителя 3032 и первому входу сумматора 3034, выход 3.6 сдвигающего регистра 3031 подсоединен к первому входу умножителя 3033 и второму входу сумматора 3034, выход которого подключен ко второму входу делителя 3036. Выходы 3.5 и 3.7 сдвигающего регистра 3031 подключены ко вторым входам умножителей 3032 и 3033 соответственно, выходы умножителей 3032 и 3033 соединены соответственно с первым и вторым входами сумматора 3035, выход которого подключен к первому входу делителя 3036, выход которого является выходом 3.3 вычислителя отклонений математического ожидания 303. Сумматоры 3034 и 3035, умножители 3032 и 3033, делитель 3036 технически реализуются аналогично сумматорам, умножителям и делителю вычислителя первичных коэффициентов 301. Сдвигающий регистр 3031 может быть реализован на базе однотактного однофазного регистра, подробно описанного в литературе [6, с.232, рис. 7.8 (a)].

Вычислитель отклонений дисперсии 304 блока коррекции 3, представленный на фиг. 7, состоит из сумматора 3041 и делителя 3042. Первый вход сумматора 3041 является первым входом 34.1 вычислителя отклонений дисперсии 304, второй вход сумматора 3041 является третьим входом 34.3 вычислителя отклонений дисперсии 304, а выход сумматора 3041 подключен ко второму входу делителя 3042, первый вход которого является вторым входом 34.2 вычислителя отклонений дисперсии 304. Выход делителя 3042 является выходом вычислителя отклонений дисперсии 304 Сумматор 3041 и делитель 3042 реализуются аналогично сумматорам и делителю вычислителя первичных коэффициентов 301 блока коррекции 3.

Блок управления 5 (фиг. 8) состоит из управляющего ПЗУ 501, порогового ПЗУ 502 и счетчика 503. Выходы 5.1 и 5.3 счетчика 503 подключены к тактовым входам 5.6 управляющего ПЗУ 501 и 5.9 порогового ПЗУ 502 соответственно, первый вход 5.2 счетчика 503 соединен со сбрасывающим выходом 5.7 управляющего ПЗУ 501, второй вход 5.4 счетчика 503 подключен к сбрасывающему выходу 5.10 порогового ПЗУ 502. Третий вход счетчика 503 является тактовым входом 54 блока управления 5, второй вход 51 которого является информационным входом 5.5 управляющего ПЗУ 501 и информационным входом 5.8 порогового ПЗУ 502. Выход управляющего ПЗУ 501 является управляющим выходом 52 блока управления 5. Группа выходов порогового ПЗУ 502 является группой пороговых выходов 531 - 53m-1 блока управления 5. Частный случай технической реализации управляющего ПЗУ 501 и счетчика 503 представлен в работе [8, с. 96-100]. Техническая реализация порогового ПЗУ 502 возможна по аналогии с ПЗУ, описанным в [7, с. 197-199, рис. 6.10].

Блок пороговых устройств 6, представленный на фиг. 9, состоит из группы схем сравнения 6011 - 601m-1, сумматора 602 и ПЗУ 603. Информационный вход 61 блока пороговых устройств 6 подключен параллельно к первым входам схем сравнения 6011 - 601m-1, вторые входы которых составляют группу пороговых входов 621 - 62m-1 блока пороговых устройств 6. Выходы схем сравнения 6011 - 601m-1 соединены с входами 631 - 63m-1 ПЗУ 603 и входами сумматора 602. Выход сумматора 602 подключен к считывающему входу 63m ПЗУ 603, выходы 641 - 64m которого являются выходами блока пороговых устройств 6. Схемы сравнения 6011 - 601m-1 реализуются в виде цифровых узлов сравнения, описанных в [7, с. 149-152, рис. 5.19]. Сумматор 602 может быть реализован на базе одноразрядного сумматора, описанного в [6, с. 173-175, рис. 516 (а)]. Техническая реализация ПЗУ 603 может быть осуществлена на базе репрограммируемого ПЗУ, описанного в [7, с. 199-205, рис 6.12].

Блок формирования значений индикаторов 7 (фиг. 10) состоит из группы предварительных сумматоров 7011 - 701m, группы умножителей 7021 - 702m группы компенсационных сумматоров 7031 - 703m и ПЗУ 704. Первые входы умножителей 7021 - 702m составляют группу информационных входов 711-71m блока, вторые входы умножителей 7021 - 702m соединены с выходами предварительных сумматоров 7011 - 701m, первые входы которых являются вспомогательными входами 721 - 72m блока и параллельно подключены ко вторым входам компенсационных сумматоров 7031 - 703m. Вторые входы предварительных сумматоров 7011 - 701m подключены к выходам ПЗУ 704, вход которого является тактовым входом 73 блока. Выходы умножителей 7021 - 702m соединены с первыми входами компенсационных сумматоров 7031 - 703m, выходы которых являются выходами 741 - 74m блока формирования значений индикаторов 7. Предварительные 7011 - 701m, и компенсационные 7031 - 703m сумматоры могут быть реализованы на основе одноразрядного сумматора, описанного в [6, с. 173-175, рис. 5.16 (а)]. Умножители 7021 - 702m могут быть реализованы аналогично известным умножителям, описанным в [6, с. 181-184, рис. 5.27]. Техническая реализация ПЗУ 704 возможна по аналогии с ПЗУ, описанным в [7, с. 197-199, рис. 6.10].

Датчик случайной последовательности 1, входящий в общую структурную схему, может быть реализован в виде известного датчика, описанного в [9, с. 42, рис. 25].

Блок формирования значений матрицы 4, входящий в общую структурную схему, реализуется в виде запоминающего устройства, аналогично описанному в литературе [10, с. 291-292, рис. 6.7].

Генератор тактовых импульсов 8, входящий в общую структурную схему, реализуется в виде известного генератора пилообразного напряжения, описанного в работе [10, с. 149-151, рис. 3.14 (а)].

Элемент ЗАПРЕТ 9, элементы И блока элементов И 10 и элемент ИЛИ 14, входящие в общую структурную схему, могут быть построены в соответствии с описанными в [9, с. 20-24, рис. 9, 11].

Блок памяти 11, входящий в общую структурную схему, реализуется в виде регистра хранения в соответствии с описанием, представленным в работе [7, с. 156-158, рис, 5.27].

Дешифратор 12, входящий в общую структурную схему, построен в виде известного и описанного в книге [11, с. 432-436, рис. 4.46].

Блок задания времени 13, входящий в общую структурную схему, реализуется в виде цифрового таймера, аналогично описанному в работе [6, с. 264-267, рис. 7.48].

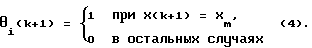

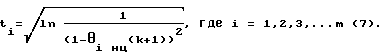

Вероятностный автомат работает следующим образом. С выхода датчика случайной последовательности 1 значения случайной вспомогательной последовательности x с нормальной плотностью распределения в двоичном коде поступают на вход 33 блока коррекции 3. В блоке 2 формируются элементы вектора нецелочисленных значений индикаторов состояния в соответствии с выражением

являющимся модификацией известного уравнения Колмогорова-Чепмена и полученным в результате преобразования выражения (2) [4, 12], где  - вектор нецелочисленных значений индикаторов состояния моделируемого процесса, имеющий математический смысл пошаговых и, в конечном итоге, финальных вероятностей нахождения случайного процесса в том или ином состоянии; ϕт(k+1,k,u) - матрица вероятностей перехода процесса из одного состояния в другое,

- вектор нецелочисленных значений индикаторов состояния моделируемого процесса, имеющий математический смысл пошаговых и, в конечном итоге, финальных вероятностей нахождения случайного процесса в том или ином состоянии; ϕт(k+1,k,u) - матрица вероятностей перехода процесса из одного состояния в другое,  - вектор целочисленных значений индикаторов состояния моделируемого процесса на предыдущем шаге. Выражение (5) для отдельного θiнц(k+1) нецелочисленного индикатора состояния в общем случае имеет вид

- вектор целочисленных значений индикаторов состояния моделируемого процесса на предыдущем шаге. Выражение (5) для отдельного θiнц(k+1) нецелочисленного индикатора состояния в общем случае имеет вид

где i = 1, 2, 3,..., m.

Блок формирования нецелочисленных значений индикаторов 2 может быть реализован по схеме, представленной на фиг. 2. Формирование нецелочисленных значений индикаторов происходит следующим образом. Группа первичных сумматоров 2011-201m и группа умножителей 2021- 202m реализуют вычисление отдельных компонент выражения (6) по значениям элементов матрицы переходных вероятностей (ПВ), поступающих в двоичном коде на входы 211-21m с выходов блока 4, и значениям индикаторов состояния на предыдущем шаге θi(k), поступающих в двоичном коде на входы 221 - 22m с выходов блока 11. Группа оконечных сумматоров 2031 - 203m осуществляет сложение полученных компонент выражения (6) и при достижении (с заданной для автомата точностью) вектором нецелочисленных значений индикаторов (вектором вероятностей состояний) своих финальных значений, подает эти нецелочисленные значения (вероятности состояний) в двоичном коде на выходы 231 - 23m блока 2. В дальнейшем, элементы вектора нецелочисленных значений индикаторов  в двоичном коде подаются на входы 311 - 31m блока коррекции 3 и на вспомогательные входы 721 - 72m блока формирования значений индикаторов 7.

в двоичном коде подаются на входы 311 - 31m блока коррекции 3 и на вспомогательные входы 721 - 72m блока формирования значений индикаторов 7.

В блоке 3 по нецелочисленным значениям индикаторов состояния (вероятностям состояний) производится коррекция математического ожидания (МО) и дисперсии случайной последовательности x' в соответствии с условиями, определяемыми принятой моделью (1-3). Алгоритм вычисления отклонений МО и дисперсии для последующей коррекции исходной случайной последовательности x' построен в соответствии с правилом рациональной аппроксимации, изложенным в работе [13, с. 729]. Блок коррекции 3 может быть реализован по схеме, представленной на фиг. 3. Коррекция МО и дисперсии последовательности x' производится следующим образом. На входы 311 - 31m блока коррекции 3 подаются нецелочисленные значения (вероятности состояний) в двоичном коде с выходов 231 - 23m блока 2 и поступают на входы вычислителей первичных коэффициентов 3011 - 301m, где реализуется выражение [13]

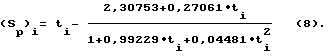

Вычислитель первичных коэффициентов 301 может быть реализован в соответствии со схемой, представленной на фиг. 4, и работает следующим образом. Из ПЗУ 3013 на второй вход сумматора 3011 и на второй вход делителя 3014 поступает в двоичном коде значение 1 (единица), позволяющее сумматору 3011, умножителю 3012 и делителю 3014, действуя последовательно, реализовать вычисление логарифмируемой переменной подкоренной части выражения (7). Умножители 3015 и 3016, сумматоры 3017 и 3018 на основе алгоритма извлечения корня квадратного из натурального логарифма, рассмотренного в работе [14, с. 30], позволяют получить окончательное решение уравнения (7) и выдать полученное значение ti в двоичном коде на выход вычислителя первичных коэффициентов 301. Полученное значение первичного коэффициента ti используется в дальнейшем для вычисления вторичного коэффициента (Sp)i в соответствии с правилом рациональной аппроксимации, изложенным в работе [13, с. 729]

Реализует выражение (8) вычислитель вторичных коэффициентов 302, структурная схема которого представлена на фиг. 5. Вычисление вторичных коэффициентов (Sp)i происходит следующим образом. Значения первичных коэффициентов ti поступают в двоичном коде на оба входа умножителя 3020 и на первые входы умножителей 3021 и 3022, на вторые входы которых из ПЗУ 3028 поступают значения постоянных коэффициентов 0,99229 и 0,27061. На второй вход умножителя 3023 подается из ПЗУ 3028 значение постоянного коэффициента 0,04481, а на вторые входы сумматоров 3024 и 3026 - значения 1 и 2,30753. Сумматор 3026 реализует сложение компонент знаменателя выражения (8), а делитель 3027 выполняет операцию деления полученных величин, осуществляя выдачу результата в двоичном коде на второй вход сумматора 3029, на первый вход которого подаются значения первичных коэффициентов ti. Полученное значение вторичного коэффициента (Sp)i используется в дальнейшем для вычисления отклонений МО, реализуемого в соответствии с выражением [13]

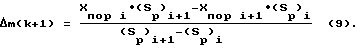

Выражение (9) реализует вычислитель отклонений математического ожидания 303, входящий в структурную схему блока коррекции 3. Вычислитель отклонений математического ожидания 303 может быть технически исполнен, как показано на фиг. 6, и функционирует следующим образом. На группу информационных входов сдвигающего регистра 3031 поступают в двоичном коде с вычислителей вторичных коэффициентов 3021 - 302m значения вторичных коэффициентов (Sp)i, на группу пороговых входов сдвигающего регистра 3031, являющихся группой пороговых входов 321 - 32m-1 блока коррекции 3, поступают в виде двоичных символов пороговые значения Xпорi состояний моделируемого процесса. Сдвигающий регистр 3031 обеспечивает хранение символов, сопоставление i-x и (i+1)-x поступающих значений (Sp) и Xпор, перезапись (сдвиг) в ячейки памяти новых значений, поступающих от блоков 5 и 3021 - 302m, а также выдачу значений Xпорi с выхода 3.1 и (Sp)i с выхода 3.2 на входы вычислителя отклонений дисперсии 304. С выходов 3.4 и 3.6 сдвигающего регистра 3031 значения (Sp)i и (Sp)i+1 поступают на входы сумматора 3034 и на первые входы умножителей 3032 и 3033, на вторые входы которых с выходов 3.5 и 3.7 сдвигающего регистра 3031 поступают пороговые значения Xпорi и Xпорi+1. Сумматор 3035 выдает значение числителя выражения (9), а делитель 3036 отвечает за окончательную реализацию выражения (9) и выдачу полученного значения отклонения МО в двоичном коде с выхода 3.3 вычислителя. Полученное значение отклонения МО используется для вычисления отклонений дисперсии в соответствии с выражением [13]

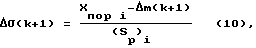

которое может быть реализовано с помощью входящего в схему блока коррекции 3 вычислителя отклонений дисперсии 304, структурная схема которого представлена на фиг 7. Вычисление отклонений дисперсии происходит следующим образом. На входы 34.1 и 34.3 вычислителя отклонений дисперсии 304 поступают значения Xпорi и Δm(k+1) соответственно, которые и вычитаются с помощью сумматора 3041. Делитель 3042 реализует деление полученного результата на значение (Sp)i, получаемое на вход 34.2 вычислителя отклонений дисперсии 304 и выдает полученное значение в двоичном коде на выход устройства 304.

На основе полученных в блоках 303 и 304 значений Δm(k+1) и Δσ(k+1), с помощью сумматора 305 и усилителя 306, входящих в структурную схему блока коррекции 3, осуществляется коррекция математического ожидания и дисперсии случайной последовательности x в соответствии с условиями, определяемыми принятой моделью (1-3) и заданными блоком управления 5 пороговыми значениями состояний процесса. В результате на выходе 34 блока коррекции 3 в двоичном коде в моменты выхода автомата из предыдущего состояния (смена такта) имеем выборочное значение случайной величины x*, полученное из модифицированной случайной последовательности x' с МО и дисперсией, соответствующими заданным условиям моделирования.

Блок управления 5 представляет собой куб постоянной памяти, в котором записана программа работы устройства и может быть реализован по схеме, представленной на фиг. 8. Формирование управляющей кодовой последовательности и последовательности пороговых значений производится следующим образом. С внешнего источника через вход 51 блока управления 5 на информационный вход 5.5 управляющего ПЗУ 501 производится запись в двоичном коде значений элементов матрицы переходных вероятностей (ПВ), соответствующих вводимому управлению, в ячейки памяти управляющего ПЗУ 501. Через этот же вход 51 блока управления 5 на информационный вход 5.8 порогового ПЗУ 502 производится запись в двоичном коде пороговых значений Xпор1 - Xпорm-1 состояний моделируемого процесса, в ячейки памяти порогового ПЗУ 502. Отсчеты моментов выхода автомата из предыдущего состояния поступают от элемента ЗАПРЕТ 9 через тактовый вход 54 блока управления 5 на третий вход счетчика 503 и определяют, поступая с выходов 5.1 и 5.3 счетчика 503 на тактовые входы 5.6 управляющего ПЗУ 501 и 5.9 порогового ПЗУ 502 соответственно, момент начала считывания значений элементов хранящейся в ПЗУ 501 новой матрицы ПВ в двоичном коде через управляющий выход 52 блока управления 5 в блок формирования значений матрицы 4 и в дешифратор 12, а также момент начала считывания в двоичном коде новых пороговых значений Xпор1 - Xпорm-1 состояний моделируемого процесса, хранящихся в ячейках памяти порогового ПЗУ 502. Считывание пороговых значений производится через пороговые выходы 531 - 53m-1 блока управления 5 в блок коррекции 3 и в блок пороговых устройств 6. Со сбрасывающих выходов 5.7 и 5.10 управляющего ПЗУ 501 и порогового ПЗУ 502 соответственно на первый 5.2 и второй 5.4 входы счетчика 503 в момент считывания матрицы ПВ или пороговых значений Xпор1 - Xпорm-1 поступает сигнал, сбрасывающий значения счетчика 503 и дающий команду счетчику 503 начать новый отсчет для вновь введенных управляющего воздействия или пороговых значений Xпор1 - Xпорm-1.

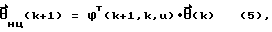

Значения элементов матрицы ПВ поддерживаются постоянными на выходах блока 4 в течение цикла управления и служат для реализации вычислений по выражениям (2), (5), (6). Пороговые значения состояний моделируемого процесса Xпор1 - Xпорm-1 в течение цикла управления поддерживаются постоянными на выходах 531 - 53m-1 блока управления 5, служат для реализации вычислений по выражениям (9) и (10), а также используются для получения элементов вектора предварительных значений индикаторов состояния процесса в соответствии с выражением [12]

Предварительные значения индикаторов состояния процесса согласно выражению (11) вычисляются в блоке пороговых устройств 6, который может быть реализован по схеме, предложенной на фиг 9. Вычисление элементов вектора предварительных значений индикаторов  происходит следующим образом. Из блока коррекции 3 на информационный вход 61 блока пороговых устройств 6, а оттуда на первые входы схем сравнения 6011 - 601m-1 в двоичном коде поступает выборочное значение случайной величины x* для данного (k+1)-го шага работы автомата. На вторые входы схем сравнения 6011 - 601m-1 из блока управления 5 через группу пороговых входов 621 - 62m-1 подаются в двоичном коде пороговые значения состояний моделируемого процесса Xпор1 - Xпорm-1. Схемы сравнения реализуют выражение (11), присваивая предварительное значение 1 тому индикатору состояния, в границы которого попадает случайная величина x*, а тем индикаторам, в границы которых x* на данном шаге не попал, присваивается предварительное значение 0. С выходов схем сравнения 6011 - 601m-1 предварительные значений, θ

происходит следующим образом. Из блока коррекции 3 на информационный вход 61 блока пороговых устройств 6, а оттуда на первые входы схем сравнения 6011 - 601m-1 в двоичном коде поступает выборочное значение случайной величины x* для данного (k+1)-го шага работы автомата. На вторые входы схем сравнения 6011 - 601m-1 из блока управления 5 через группу пороговых входов 621 - 62m-1 подаются в двоичном коде пороговые значения состояний моделируемого процесса Xпор1 - Xпорm-1. Схемы сравнения реализуют выражение (11), присваивая предварительное значение 1 тому индикатору состояния, в границы которого попадает случайная величина x*, а тем индикаторам, в границы которых x* на данном шаге не попал, присваивается предварительное значение 0. С выходов схем сравнения 6011 - 601m-1 предварительные значений, θ

θ

подавая полученное значение в двоичном коде на считывающий вход 63m ПЗУ 603. Это служит сигналом для обнуления ячеек памяти ПЗУ 603, для выдачи предварительных значений индикаторов состояний θ предварительных значений индикаторов состояний моделируемого процесса, которые используются в дальнейшем для формирования значений индикаторов в соответствии с выражениями [4, 12]

предварительных значений индикаторов состояний моделируемого процесса, которые используются в дальнейшем для формирования значений индикаторов в соответствии с выражениями [4, 12]

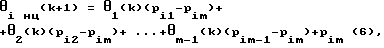

где выражение (13) описывает механизм получения элементов m-мерной матрицы компенсационных добавок  содержит элементы: A - m-мерная единичная диагональная матрица;

содержит элементы: A - m-мерная единичная диагональная матрица;  - m-мерная матрица, столбцами которой являются вектора нецелочисленных значений индикаторов

- m-мерная матрица, столбцами которой являются вектора нецелочисленных значений индикаторов  повторенные m раз. Выражение (14) описывает порядок выбора вектора компенсационных добавок

повторенные m раз. Выражение (14) описывает порядок выбора вектора компенсационных добавок  из матрицы компенсационных добавок

из матрицы компенсационных добавок  c помощью вектора

c помощью вектора  предварительных значений индикаторов состояний моделируемого процесса. Выражение (15) завершает алгоритм вычислений вектора индикаторов состояний

предварительных значений индикаторов состояний моделируемого процесса. Выражение (15) завершает алгоритм вычислений вектора индикаторов состояний  и с учетом выражения (5), является модифицированной записью уравнения состояния моделируемого процесса (2).

и с учетом выражения (5), является модифицированной записью уравнения состояния моделируемого процесса (2).

Комплекс выражений (13)-(15) реализует блок формирования значений индикаторов, структурная схема которого представлена на фиг. 10. Значения индикаторов состояния процесса формируются следующим образом. На первые входы умножителей 7021 - 702m через группу информационных входов 711-71m блока 7 из блока 6 в двоичном коде поступают значения элементов вектора  предварительных значений индикаторов состояний моделируемого процесса. На вторые входы умножителей 7021 - 702m с выходов предварительных сумматоров 7011 - 701m поступают в двоичном коде значения элементов m-мерной матрицы компенсационных добавок

предварительных значений индикаторов состояний моделируемого процесса. На вторые входы умножителей 7021 - 702m с выходов предварительных сумматоров 7011 - 701m поступают в двоичном коде значения элементов m-мерной матрицы компенсационных добавок  являющиеся результатом вычисления в соответствии с выражением (13). На вторые входы компенсационных сумматоров 7031 - 703m и на первые входы предварительных сумматоров 7011 - 701m через вспомогательные входы 721 - 72m блока 7 с выходов блока 2 в двоичном коде подаются значения элементов вектора нецелочисленных значений индикаторов

являющиеся результатом вычисления в соответствии с выражением (13). На вторые входы компенсационных сумматоров 7031 - 703m и на первые входы предварительных сумматоров 7011 - 701m через вспомогательные входы 721 - 72m блока 7 с выходов блока 2 в двоичном коде подаются значения элементов вектора нецелочисленных значений индикаторов  которые формируют матрицу нецелочисленных значений индикаторов

которые формируют матрицу нецелочисленных значений индикаторов  На вторые входы предварительных сумматоров 7011-701m с выходов ПЗУ 704 в моменты выхода автомата из предыдущего состояния, в двоичном коде подаются элементы единичной диагональной матрицы А. Моменты выхода автомата из предыдущего состояния определяются по наличию сигнала от блока 9 на входе ПЗУ 704, являющемся тактовым входом 73 блока 7. Предварительные 7011 - 701m сумматоры осуществляют вычисления в соответствии с выражением (13). Группа умножителей 7021 - 702m реализует выражение (14), причем с выходов умножителей 7021 - 702m элементы полученного вектора компенсационных добавок

На вторые входы предварительных сумматоров 7011-701m с выходов ПЗУ 704 в моменты выхода автомата из предыдущего состояния, в двоичном коде подаются элементы единичной диагональной матрицы А. Моменты выхода автомата из предыдущего состояния определяются по наличию сигнала от блока 9 на входе ПЗУ 704, являющемся тактовым входом 73 блока 7. Предварительные 7011 - 701m сумматоры осуществляют вычисления в соответствии с выражением (13). Группа умножителей 7021 - 702m реализует выражение (14), причем с выходов умножителей 7021 - 702m элементы полученного вектора компенсационных добавок  в двоичном коде поступают на первые входы компенсационных сумматоров 7031 - 703m, которые завершают вычисления, реализуя выражение (15) и подавая в двоичном коде полученные элементы вектора индикаторов состояний

в двоичном коде поступают на первые входы компенсационных сумматоров 7031 - 703m, которые завершают вычисления, реализуя выражение (15) и подавая в двоичном коде полученные элементы вектора индикаторов состояний  через выходы 741 - 74m блока формирования значений индикаторов 7 на входы блока элементов И 10.

через выходы 741 - 74m блока формирования значений индикаторов 7 на входы блока элементов И 10.

Моменты выхода автомата из предыдущего состояния определяются генератором тактовых импульсов 8, элементом ИЛИ 14, элементом ЗАПРЕТ 9 при формировании нулевой комбинации на выходе блока задания времени 13. С помощью блока элементов И 10 производится запись полученных значений элементов вектора индикаторов состояний  моделируемого процесса в блок памяти 11, где они хранятся до момента истечения периода k (периода смены состояния), определяемого блоком задания времени 13 по значениям кода, формируемого блоком управления 5. При этом значения кода с выхода 52 блока управления 5 поступают на дешифратор 12, преобразуются им в код, соответствующий временному интервалу периода смены состояний k, записываются в реверсивный счетчик блока 13 и считываются генератором тактовых импульсов 8 до момента появления нулевой комбинации на выходе блока 13, свидетельствующей об истечении времени пребывания автомата в данном состоянии. Управление вероятностно-временным механизмом смены состояний автомата и пороговыми значениями состояний осуществляется по управляющим кодовым комбинациям, поступающим с выходов 52 и 531 - 53m-1 блока управления 5 в моменты выхода автомата из предыдущего состояния.

моделируемого процесса в блок памяти 11, где они хранятся до момента истечения периода k (периода смены состояния), определяемого блоком задания времени 13 по значениям кода, формируемого блоком управления 5. При этом значения кода с выхода 52 блока управления 5 поступают на дешифратор 12, преобразуются им в код, соответствующий временному интервалу периода смены состояний k, записываются в реверсивный счетчик блока 13 и считываются генератором тактовых импульсов 8 до момента появления нулевой комбинации на выходе блока 13, свидетельствующей об истечении времени пребывания автомата в данном состоянии. Управление вероятностно-временным механизмом смены состояний автомата и пороговыми значениями состояний осуществляется по управляющим кодовым комбинациям, поступающим с выходов 52 и 531 - 53m-1 блока управления 5 в моменты выхода автомата из предыдущего состояния.

В итоге, на выходах блока 13 имеем записанные в двоичном коде значения индикаторов состояния управляемого вероятностного автомата в каждый из моментов времени (определяемых генератором тактовых импульсов 8) с учетом введенного управляющего воздействия и динамически изменяемых пороговых значений (границ) состояний моделируемых случайных процессов.

Таким образом, анализ принципа работы заявляемого вероятностного автомата показывает очевидность того факта, что наряду с сохраненными возможностями моделирования управляемых полумарковских цепей с заранее заданными границами состояний, автомат способен осуществлять моделирование управляемых полумарковских цепей с динамической коррекцией пороговых значений (границ) состояний моделируемых случайных процессов, способен моделировать случайные процессы, протекающие в реальных сетях многоканальной радиосвязи. Данный вероятностный автомат позволяет проводить на своей основе верификацию граничных условий функционирования сети и управленческих решений, принимаемых в контуре управления сетью многоканальной радиосвязи, что существенно расширяет функциональные возможности аппаратуры, где заявленный вероятностный автомат будет использован.

Источники информации

1. Сейдж Э. , Уайт Ч. Оптимальное управление системами. -М.: Радио и связь, 1982, 92 с.

2. Ненадович Д. М., Паращук И.Б., Терентьев В.М. Математическая модель процесса функционирования и оценка состояния пакетной сети спутниковой связи. // "Радиотехника", N 6, 1996, с. 9-13.

3. Сейдж Э. , Мелс Дж. Теория оценивания и ее применение в связи и управлении -М.: Связь, 1976, 496 с.

4. Терентьев В.М., Паращук И.Б. Теоретические основы управления сетями многоканальной радиосвязи. - С.-Пб.: ВАС, 1995, 196 с.

5. Пяткин О.А. Проектирование микроэлектронных цифровых устройств. -М.: Советское радио, 1977, с. 123, рис. 4.12.

6. Фролкин В.Т., Попов Л.Н. Импульсные и цифровые устройства. -М.: Радио и связь, 1992, 335 с.

7. Сидоров А.М., Гусев В.В., Лебедев О.Н. Основы импульсной и цифровой техники. - С.-Пб.: СПВВИУС, 1995, 248 с.

8. Соботка 3. , Стары Я. Микропроцессорные системы. -М.: Энергоиздат, 1981, 340 с.

9. Мальцева Л. А., Франберг Э.М., Ямпольский В.С. Основы цифровой техники. - М.: Радио и связь, 1980.

10. Быстров Ю. А., Великсон Я.М., Вогман В.Д. и др. Электроника: Справочная книга/Под ред. Быстрова Ю.А. - С.-Пб.: Энергоатомиздат, 1996, 544 с.

11. Богданович М. И, Грель И.Н., Прохоренко В.А. и др. Цифровые интегральные микросхемы: Справочник. -Минск: Беларусь, 1991, 493 с.

12. Терентьев В.М., Паращук И.Б., Белобров Е.Г. Аналитическая модель формирования цепи Маркова для анализа отклонений показателей качества от требуемых значений.// Научно-технический сборник N 59. - С.-Пб.: ВАС, 1996, с. 41-45.

13. Справочник по специальным функциям с формулами, графиками и таблицами./Под ред. Абрамовица М. и Стигана И. -М.: Наука, 1979, 832 с.

14. Корн Г., Корн Т. Справочник по математике для научных работников и инженеров. -М.: Наука, 1984, 832 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1994 |

|

RU2099781C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2001 |

|

RU2195697C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2000 |

|

RU2169944C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2005 |

|

RU2276402C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2021 |

|

RU2777531C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2018 |

|

RU2718214C1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| УСТРОЙСТВО ФАЗОВОГО ПУСКА | 1995 |

|

RU2115248C1 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 2001 |

|

RU2195698C1 |

Изобретение относится к радиотехнике и вычислительной технике и предназначено для использования в комплексах автоматизированных систем управления сетями многоканальной радиосвязи. Техническим результатом является обеспечение динамической коррекции пороговых значений состояний случайных процессов, реально протекающих в сетях многоканальной радиосвязи. Вероятностный автомат содержит датчик случайной последовательности, блок формирования нецелочисленных значений индикаторов, блок коррекции, блок формирования значений матрицы, блок управления, блок пороговых устройств, блок формирования значений индикаторов, генератор тактовых импульсов, элементы ЗАПРЕТ, ИЛИ, блок элементов И, блок памяти, дешифратор и блок задания времени. 5 з.п.ф-лы, 10 ил.

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1994 |

|

RU2099781C1 |

| Автономный вероятностный автомат | 1978 |

|

SU734701A1 |

| Вероятностный автомат | 1982 |

|

SU1045232A1 |

| НЕЧЕТКИЙ ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1995 |

|

RU2110090C1 |

| RU 94042181 A1, 27.09.96 | |||

| ВИБРОИЗОЛЯТОР РЕЗИНОВЫЙ ДЛЯ ТЕХНОЛОГИЧЕСКОГО ОБОРУДОВАНИЯ | 2006 |

|

RU2303720C1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

Авторы

Даты

1999-10-10—Публикация

1998-10-01—Подача