Изобретение относится к технике коммутации и может быть использовано для построения коммутационных полей электронных АТС.

Известна матрица точек связи [1], выполненная в технике полевых транзисторов, с парами элементов связи, предусмотренными в точках связи и соответственно образованными двумя переключательными транзисторами, соответственно нагружаемыми на управляющем электроде сигналом переключения, соответственно блокировки, переключательные транзисторы которых соответственно подключены основным электродом к одному, соответственно, к другому сигнальному проводу соответствующей матричной выходной линии, которая со своей стороны снабжена выходным дифференциальным усилителем с характеристикой опрокидывания, причем пары элементов связи соответственно имеют два входных транзистора, соответственно образующих с переключательным транзистором последовательную схему, которые соответственно подключены управляющим электродом к одному, соответственно, к другому сигнальному проводу соответствующей матричной входной линии, и соответствующий главный электрод которых, отвернутый от последовательной схемы соединен через считывающий транзистор с одним присоединительным элементом (корпус) источника рабочего напряжения, с другим присоединительным элементом которого соединен соответственно через транзистор предварительного заряда каждый сигнальный провод соответствующей матричной выходной линии, и причем транзисторы предварительного заряда и считывающий транзистор противофазно по отношению друг к другу нагружены на своем управляющем электроде тактом управления коммутационным полем, подразделяющим промежуток времени переключения бита на фазу предварительного заряда и собственную фазу переключения, так что в каждой предварительной фазе при заблокированном считывающем транзисторе оба сигнальных провода матричной выходной линии через соответствующей транзистор предварительно заряда по меньшей мере приблизительно заряжаются до потенциала, имеющегося на указанном другом присоединительном элементе источника рабочего напряжения.

Это известное устройство связи широкополосного сигнала несет с собой в дополнение к преимуществам, связанным с матрицей коммутационных точек, выполненной в технике полевых транзисторов, другое преимущество, заключающееся в том, что, с одной стороны, при заблокированной точке связи, даже без дополнительных мер по демпфированию, никакие сигналы помех не попадают через точку связи на выход матрицы и что, с другой стороны, при проводящей точке связи - при собственном переключении бита имеющие место при известных условиях перезаряды матричной выходной линии всегда происходят только в одном направлении перезаряда, исходя из рабочего потенциала, соответствующего состоянию сигнала, и таким образом уже с малым перезарядом (соответствующим превышению порога, являющего близким к этому значению рабочего потенциала и соответствующего точке опрокидывания дифференциального усилителя) и тем самым соответственно быстро связан однозначный переход переключенного цифрового сигнала, появляющегося на выходе устройства связи, из одного состояния сигнала в другое состояние сигнала.

В случае такого устройства связи широкополосного сигнала дальнейшее повышение быстродействия делается возможным за счет того, что оба транзистора предварительного заряда на своих главных электродах, повернутых к соответствующей матричной выходной линии, соединены друг с другом посредством поперечного транзистора, управляющий электрод которого соединен с управляющими электродами транзисторов предварительного заряда (выложенная заявка на европейский патент N 345623); это в сочетании с преимуществом, связанным с ускорением предварительного заряда матричных выходных линий, несет с собой другое преимущество, заключающееся в очень раннем симметривании потенциалов матричных выходных линий, так что также соответственно рано имеются начальные условия для надежного усиления с помощью послевключенного дифференциального усилителя.

Достигаемый технический результат заключается в отсутствии необходимости в считывающем транзисторе в опорной точке элементов связи, а также в отсутствии необходимости в соответствующих проводках для отделения переключающих транзисторов от соответствующего присоединения элемента (масса) источника рабочего напряжения в фазе предварительного заряда, однако эта функция отделения быть обеспечена путем соответствующего тактирования матричных входных линий посредством соответствующих логических схем, заблокированных во время такта предварительного заряда, в матричных входных линиях, тем что ко всем сигнальным проводам матричной входной линии во время такта предварительного заряда прикладывается потенциал массы с последующей блокировкой входных транзисторов, имеющихся в парах элементов связи.

В другом варианте осуществления изобретения за каждым логическим элементом может быть включена возбуждающая схема, с помощью которой может быть при известных условиях также устранено инвертирование, вызываемое логическими элементами.

Для подключения к двум, проводящим комплементарные сигналы, сигнальным проводам соответствующей матричной входной линии целесообразно, чтобы пары элементов связи в другом варианте осуществления изобретения соответственно имели два входных транзистора одинакового канального типа.

Согласно другому предпочтительному варианту осуществления изобретения пары элементов связи могут соответственно иметь два входных транзистора различного канального типа, которые подключены своим управляющим электродом к одному и тому же сигнальному проводу соответствующей матричной входной линии; тем самым на каждую матричную входную линию требуется лишь один единственный сигнальный провод, что означает дальнейшее уменьшение занимаемой площади.

Еще более отчетливое уменьшение занимаемой площади получают тогда, когда в другом варианте осуществления изобретения пары элементов связи соответственно имеют два переключательных транзистора различного канального типа, которые соответственно образуют с предвключенным транзистором того же канального типа последовательную схему.

Чтобы при этом избежать несимметричной нагрузки обоих сигнальных проводов матричных выходных линий и тем самым также несимметричной нагрузки обоих входов последующего дифференциального усилителя, устройство связи широкополосного сигнала согласно настоящему изобретению далее может быть усовершенствовано в том отношении, что только в случае одной части пар элементов связи, ведущих и той же матричной выходной линии, соответственно транзисторная последовательная схема одного канального типа соединена с одним сигнальным проводом, а транзисторная последовательная схема другого канального типа соединена с другим сигнальным проводом матричной выходной линии, в то время как в случае другой части пар элементов связи, ведущих к соответствующей матричной линии, соответственно транзисторная последовательная схема указанного другого канального типа соединена с указанным одним сигнальным проводом, а транзисторная последовательная схема указанного канального типа соединена с указанным другим сигнальным проводом матричной выходной линии; это в частности может происходить таким образом, что пары элементов связи, соединенные одним, соответственно другим способом с сигнальными проводами соответствующей матричной выходной линии, в соответствующей матричном ряду попеременно следуют друг за другом.

Другие особенности изобретения следуют из нижеследующего более подробного объяснения изобретения с помощью чертежей.

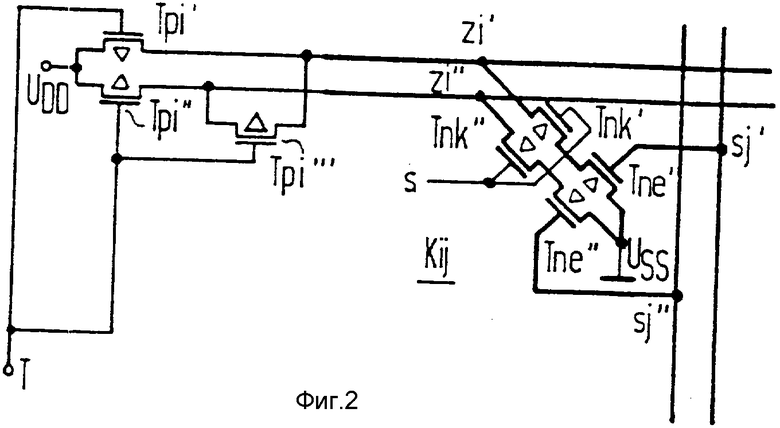

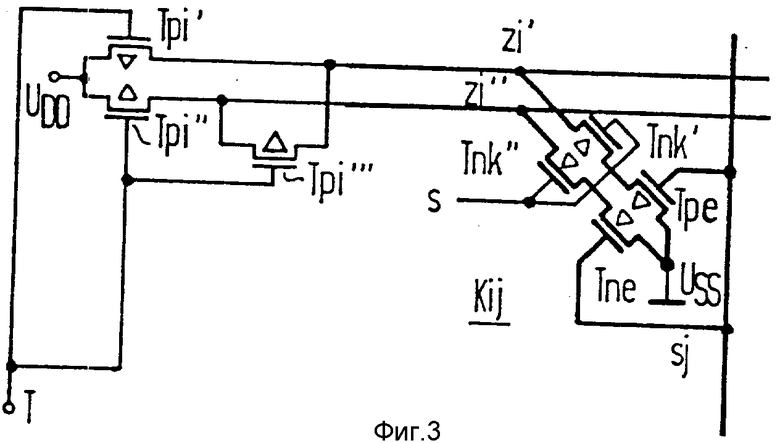

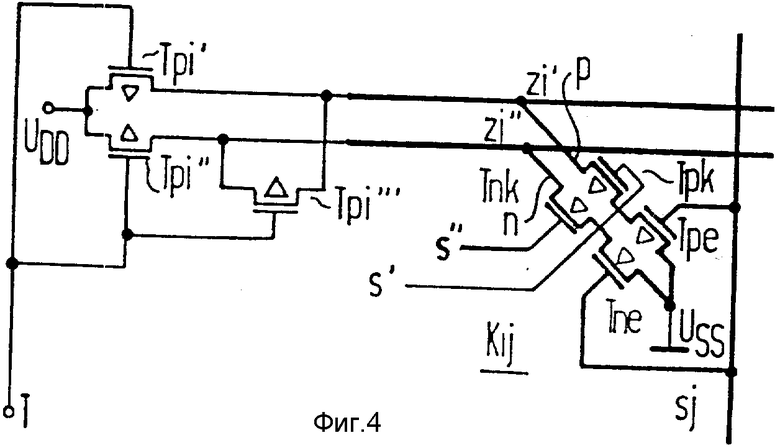

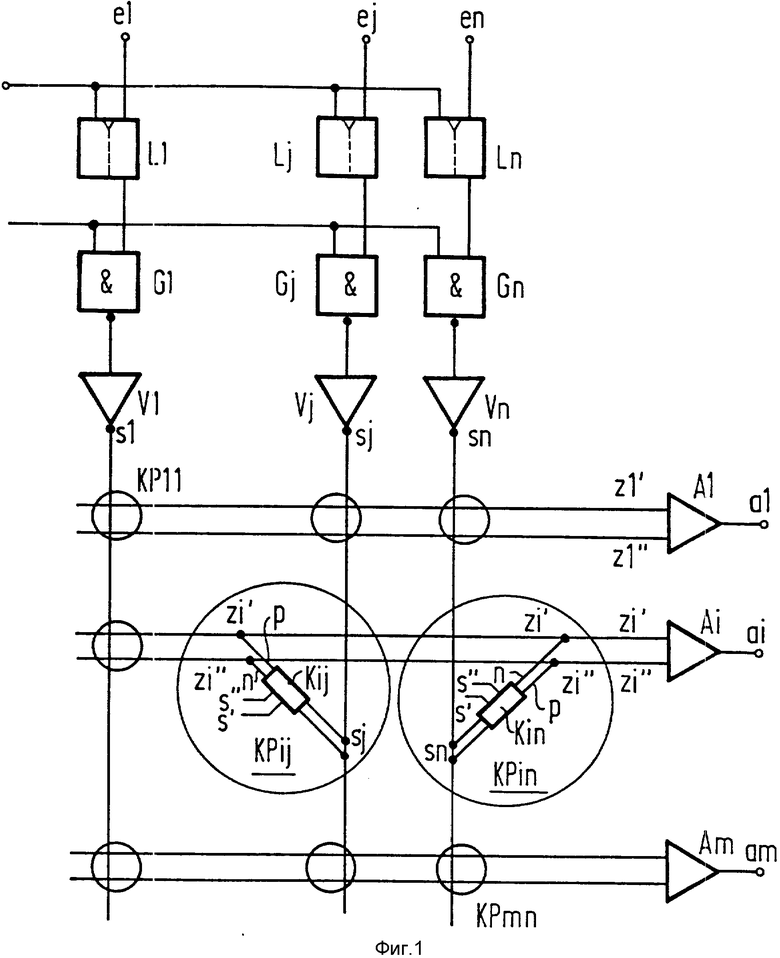

На фиг. 1 изображена схема устройства связи широкополосного сигнала соласно изобретению; на фиг. 2, 3 и 4 - примеры схемотехнической реализации ее элементов связи.

На фиг. 1 схематично изображено в объеме, необходимом для понимания изобретения, устройство связи широкополосного сигнала, на входах eI... ej... en которого, ведущих к линиям столбцов SI... Sj ... Sn матрицы точек связи, предусмотрены, ниже объясняемые более подробно, входные цифровые сигнальные схемы, а его выходы aI ... ai ... am, достижимые от линий строк ZI ... Zi .. . Zm матрицы точек связи, снабжены выходными усилительными схемами AI ... Ai ... Am, которые могут быть соответственно образованы с помощью дифференциального усилителя с характеристикой опрокидывания.

Пары ... Kij ... элементов связи могут быть схематехнически реализованы, как показано на фиг. 2, 3 и 4. Пары ... Kij ... элементов связи соответственно образованы с помощью двух переключающих транзисторов (T'nk, T"nk на фиг. 2 и 3; Tpk, Tnk на фиг. 4), соответственно нагружаемых на управляющем электроде сигналом переключения, соответственно блокировки и подключенных главным электродом к одному, соответственно другому сигнальному проводу Z'i, Z"i соответствующей матричной выходной линии, и с помощью двух входных транзисторов (T'ne, T"ne на фиг. 2; Tpe, Tne на фиг. 3 и 4), соответственно образующих с переключательным транзистором последовательную схему, которые соответственно подключены управляющим электродом к соответствующей матричной входной линии (линия столбцов) ... S'j ...

При этом, как показано на фиг. 1 и 2, матричные входные линии (линии столбцов) могут иметь соответственно два - проводящих комплементарные сигналы - сигнальных провода (S'j и S"j, причем согласно фиг. 2 в таком случае один входной транзистор T'ne своим управляющим электродом подключен к сигнальному проводу S'j, а другой входной транзистор T"ne такого же канального типа своим управляющим электродом подключен к другому сигнальному проводу S"j. Как это поясняют фиг. 3 и 4 в сочетании с фиг. 1, могут быть также предусмотрены два входных транзистора Tpe, Tne различного канального типа, которые соответственно подключены своим управляющим электродом к (в таком случае единственному) сигнальному проводу Sj соответствующей матричной входной линии (линия столбцов). При этом согласно фиг. 4 оба переключающих транзистора Tpk и Tnk также могут быть различного канального типа, так что переключательный транзистор Tpk (соответственно Tnk) и входной транзистор Tpe (соответственно Tne) того же канального типа образуют последовательную схему.

Своим отвернутым от последовательной схемы главным электродом входные транзисторы непосредственно соединены с присоединительным элементом Uss (корпус) источника рабочего напряжения. С другим присоединительным элементом UDD источника рабочего напряжения соединены оба сигнальных провода (Z'i, Z"i) соответствующей матричной выходной линии (линия строк) ... Zi ... соответственно посредством транзистора T'pi, соответственно T"pi предварительного заряда; на своих главных электродах, повернутых к соответствующей матричной выходной линии (Z'i, Z"i), оба транзистора T'pi, T"pi могут быть соединены друг с другом посредством поперечного транзистора T'''pi, управляющий электрод которого так же, как и управляющие электроды транзисторов T'pi. T"pi предварительного заряда, подключены к линии T такового сигнала предварительного заряда-перезаряда такта управления полем связи, который, как это еще будет ниже объяснено более подробно, подразделяет промежуток времени переключения бита на фазу предварительного заряда и собственную фазу перезаряда, соответственно переключения.

Теперь снова вернемся к фиг. 1. В изображенных там устройствах связи широкополосного сигнала входные цифровые сигнальные схемы, предусмотренные на их входах eI, ... , ej, ..., en, имеют прежде всего соответственно схему-защелку Li, ..., Lj, ..., Ln, управляемую синхронизирующими импульсами от линии C синхронизации; позади этой схемы - защелки L в матричную входную линию соответственно включена логическая схема GI, ..., Gj, ..., Gn (на фиг. 1), подключенная к вышеуказанной линии T тактового сигнала предварительного заряда-перезаряда, которая с помощью тактового сигнала противофазно управляется по отношению к транзисторам T'pi, T''pi (на фиг. 2 - 4) предварительного заряда. В случае матричных исходных линий, имеющих два сигнальных провода, как это также показано на фиг. 1, каждая такая логическая схема содержит два логических элемента, из которых один включен в один сигнальный провод, а другой включен в другой сигнальный провод; в случае матричных входных линий только с одним (единственным) сигнальным проводом, как это показано на фиг. 1, достаточным является один логический элемент в каждой логической схеме. Как это показано на фиг. 1, каждый логический элемент может быть, например, образован с помощью элемента НЕ-И (G'1, G''1i, ..., G'j, G''j, ..., G'n, G''n на фиг. 1; причем за каждым элементом НЕ-И может быть включена возбуждающая схема V'i...Vj..Vn (на фиг. 1), например, также инвертирующая и тем самым устраняющая инвертирование сигнала, вызванное элементом НЕ-И.

Как это также показано на фиг. 4, в матрице точек связи, выдержанной в КМОП-технике, соответственно переключающий транзистор Tnk и входной транзистор Tne одной последовательной схемы Tne - Tnk могут быть транзисторами с каналом n-типа, в то время как переключательный транзистор Tpk и входной транзистор Tpe другой последовательной схем Tpe - Tpk так же, как и транзисторы Tpi предварительного заряда, являются транзисторами с каналом p-типа.

Так как транзисторы с каналом p-типа (при одинаковом выходе по току) должны быть рассчитаны в два раза более широкими, чем транзисторы с каналом n-типа, целесообразно во избежании вытекающих из этого ассиметричных нагрузок обоих сигнальных проводов Z'i, Z''i матричной выходной линии - в случае представленного на фиг. 4 варианта выполнения пар элементов связи с соответственно двумя транзисторными последовательными схемами различного канального типа, чтобы только в случае одной части пар элементов связи, ведущих к одной и той же матричной выходной линии, транзисторная последовательная схема (Tpe, Tpk) одного канального типа была соединена с одним сигнальным проводом (Z'i), а транзисторная последовательная схема (Tne, Tnk) другого канального типа соединена с другим сигнальным проводом (Z''i) матричной выходной линии, в то время как в случае другой части пар коммутационных элементов, ведущих к соответствующей матричной выходной линии, транзисторная последовательная схема (Tne, Tnk) указанного другого канального типа была соединена с указанным одним сигнальным проводом (Z'i), а транзисторная последовательная схема (Tpe, Tpk) указанного канального типа была соединена с указанным другим сигнальным проводом (Z''i) матричной выходной линии; в частности при этом пары элементов связи, соединенные одним или другим способом с соответствующей матричной выходной линией, могут попеременно следовать друг за другом в соответствующем матричном ряду.

Такие попеременно следующие друг за другом пары элементов связи показаны на фиг. 1. В случае точки связи KPij выход транзисторной последовательной схемы с каналом p-типа (Tpe-Tpk на фиг. 4) подключен к одному сигнальному проводу Zi соответствующей матричной выходной линии, а выход транзисторной последовательной схемы с каналом n-типа (Tne - Tnk на фиг. 4) подключен к другому сигнальному проводу Z''i. Далее на фиг. 1 показано, что также и остальные точки, лежащие на матричной входной линии Sj, соответствующим образом подключены к остальным матричным выходным линиям. Одновременно на фиг. 1 показано, что в случае точек связи, лежащих на матричной входной линии Sn выходы элемента связи подключены обратным образом к обоим сигнальным проводам соответствующей матричной выходной линии. Как это более подробно показано на фиг. 1 для точки связи KPin, в этом столбце матрицы соответственно выход n (см. также фиг. 4) транзисторной последовательной схемы с каналом n-типа соответствующей пары элементов связи (например, Kin) соединен с сигнальным проводом (Z''i на фиг. 1), в то время как выход p (см. также фиг. 4) транзисторной последовательной схемы с каналом p-типа соответствующей пары элементов связи (например, Kin) соединен с другим сигнальным проводом (Z''i на фиг. 1) соответствующей матричной выходной линии. Соответствующим образом элементы связи всех точек связи, ведущих от различных матричных входных линий Si... Sn (на фиг. 1) к одной и той же матричной выходной линии (например, Z'i, Z''i), могут быть подключены своей ветвью канала n-типа попеременно от столбца матрицы к столбцу матрицы к одному сигнальному проводу (Z'i) и к другому сигнальному проводу (Z''i) соответствующей матричной выходной линии, а своей ветвью канала p-типа могут быть попеременно подключены к этому другому сигнальному проводу (Z''i) и к вышеуказанному одному сигнальному проводу (Z'i) соответствующей матричной выходной линии.

Во время фазы PV предварительного заряда соответственно оба сигнальных провода (Z'i, Z''i) матричных выходных линий (линии строк) ... Zi... заряжаются по меньшей мере приблизительно до рабочего потенциала UDD посредством соответствующего транзистора (T'pi, соответственно T''pi и на фиг. 2, фиг. 4) предварительного заряда, для чего транзисторы T'pi, T''pi предварительного заряда, образованные, например, с помощью транзисторов с каналом p-типа, делаются проводящими, например, с помощью тактового сигнала T "Low" строка T).

При этом с помощью среза тактового сигнала T одновременно также становится проводящим поперечный транзистор T'''pi, расположенный между обоими сигнальными проводами Z''i, Z''i с последующим коротким замыканием обоих сигнальных проводов Z'i, Z''i, вследствие чего к началу фазы предварительного заряда быстро прежде всего происходит выравнивание потенциалов обоих сигнальных проводов Z'i, Z''i; затем оба (теперь выравнивание по потенциалу) сигнальных провода Z'i, Z''i заряжаются посредством обоих транзисторов T'pi, T''pi предварительного заряда до рабочего потенциала UDD, причем продолжительность заряда в общем сокращается тем, что после выравнивания потенциалов, осуществленного с помощью поперечного транзистора T''pi, теперь в процессе заряда вовлечены оба транзистора T'pi, T''pi, предварительного заряда.

Одновременно с разблокировкой транзисторов T'pi, T''pi предварительного заряда и поперечного транзистора T''pi с помощью тактового сигнала T "LOW" логические элементы Gi,...Gj...Gn (на фиг. 1), включенные согласно фиг. 1 в сигнальные провода соответственно Si, ... , Sj, ... , Sn (на фиг. 1) входных линий, управляются в противоположном смысле, например, с помощью того же тактового сигнала T "LOW", так что на выходе (соответственно на выходе последующей возбуждающей схемы ... Vj ..., устраняющей инвертирование, вызываемое логическим элементом ... Gj ...) и тем самым в соответствующем сигнальном проводе ... Sj ... соответствующей матричной входной линии имеется рабочий потенциал USS (корпус). Это имеет своим следствием то, что входные транзисторы T'ne, T''ne (на фиг. 2), соответственно Tne, Tpe (на фиг. 3 и фиг. 4) всех пар ... Kji ... элементов связи становятся заблокированными, так что заряд соответственно обоих сигнальных проводов (Z'i, Z''i) матричных выходных линий (линий строк) ... Zi ... осуществляется независимо от управления соответствующими переключающими транзисторами T'nk, T''nk (на фиг. 2 и 3), соответственно Tpk, Tnk (на фиг. 4) отдельных пар ... Kij ... элементов связи. На соответствующей матричной входной линии (линии столбцов) ... Sj .. . при этом может при известных условиях уже установиться (соответственно сохраниться) потенциал, соответствующий соответственно переключенному биту, как это показывает строка Sj на фиг. 5.

При равенстве потенциалов обоих сигнальных проводов Z'i, Z''i, осуществленном с помощью поперечного транзистора T'''pi, соответственно рано имеются в распоряжении начальные условия для надежного усиления с помощью дифференциального усилителя Ai (на фиг. 1), так что уже к соответственно раннему моменту времени может начаться последующая фаза ph перезаряда, соответственно переключения. Во время этой фазы nh перезаряда, например, с помощью тактового сигнала T "High" блокируются транзисторы T'pi, T''pi предварительного заряда и поперечный транзистор T'''pi, и одновременно в известной степени снова деблокируются логические элементы, включенные в сигнальные провода матричных входных линий, так что на соответствующем сигнальном проводе S'i, S''i, ... , S'j, S''j, ... , S'n, S''n (на фиг. 1 и 2), соответственно Si, . .., Sj, ..., Sn (на фиг. 1, 3 и 4) появляется соответственно выходной сигнал соответствующей находящейся со стороны входа схемы-защелки Li, ..., Lj, Ln (на фиг. 1). Соответствующая схема-защелка ... Lj ... при этом может управляться от линии C синхронизации с помощью синхронизирующего сигнала. Если теперь в паре ... Kij ... элементов связи ее переключательные транзисторы T'nk, T''nk (на фиг. 2 и 3), соответственно Tpk, Tnk (на фиг. 4) являются проводящими вследствие переключательного сигнала (например, "High"), имеющегося на управляющем входе (на фиг. 2 и 3), соответственно вследствие переключательного сигнала (например, "LOW"), имеющегося на управляющем входе S' (на фиг. 4), и переключательного сигнала (например, "High"), имеющегося на управляющем входе (на фиг. 4), и если тем самым точка связи находится в переключающем состоянии, то теперь в зависимости от состояния сигнала, соответствующего подлежащему переключению биту, имеющемуся на соответствующей матричной входной линии (линия столбцов) ... Sj ..., сигнальные провода Z'i, Z''i матричной выходной линии (линии строк), соединенной с этой матричной входной линией (линией столбцов) ... Sj ... посредством соответствующего элемента связи ... Kij ... разряжаются, соответственно остаются на потенциале UDD, принятом во время фазы PV предварительного заряда.

Если на (единственном) сигнальном проводе соответствующей матричной входной линии (линия столбцов) Sj (на фиг. 1, 3 и 4) имеется состояние сигнала "LOW", и если в соответствии с этим входной транзистор Tne с каналом n-типа (на фиг. 3 и фиг. 4) соответствующей пары Kij коммутационных элементов является заблокированным, то соответствующий сигнальный провод Z''i матричной выходной линии (линии строк) Zi не будет разряжаться через соответствующий элемент связи этой пары Kij элементов связи, а сохранит состояние потенциала UDD, если никакая другая точка связи, ведущая к этой матричной выходной линии (линии сток) Zi, не находится в состоянии переключения. Одновременно входной транзистор Tpe (на фиг. 3 и 4) рассматриваемой пары Kij элементов связи также является проводящим как и переключающий транзистор Tpk, так что приданный сигнальный провод Z'i матричной выходной линии (линии строк) Zi будет разряжаться через этот элемент связи пары Kij элементов связи и получит потенциал USS.

Если, напротив, на сигнальном проводе только что рассмотренной матричной входной линии Sj (на фиг. 1, 3 и 4) имеется состояние сигнала "High", и если в соответствии с этим входной транзистор Tne с каналом n-типа (на фиг. 3 и 4) соответствующей пары Kij элементов связи является проводящим, то соответствующий сигнальный провод Z''i матричной выходной линии (линии строк) Zi будет разряжаться через соответствующий элемент связи этой пары Kij элемент связи и получит потенциал USS.

Одновременно в таком случае входной транзистор Tpe (на фиг. 3 и фиг. 4) рассматриваемой пары Kij элементов связи является непроводящим, так что приданный сигнальный провод Z'i матричной выходной линии (линия строк) не будет разряжаться через этот элемент связи пары Kij элементов связи, а сохранит состояние потенциала UDD, если никакая другая точка связи, ведущая к этой матричной выходной линии (линии строк) Zi, не находится в состоянии переключения.

Если на одном сигнальном проводе S'j (на фиг. 1 и фиг. 2) матричной входной линии (линия столбцов), имеющей два сигнальных провода S'j, Sj (на фиг. 1 и 2) имеется состояние сигнала "LOW", и если в соответствии с этим входной транзистор с каналом n-типа Tne' (на фиг. 2) соответствующей пары Kij элементов связи является заблокированным, то соответствующий сигнальный провод Z'i матричной выходной линии (линии строк) Zi не будет разряжаться через соответствующий элемент связи этой пары Kij элементов связи, а сохранит состояние потенциала UDD, если никакая другая точка связи, ведущая к этой матричной выходной линии (линия строк) Zi, не находится в состоянии переключения.

Одновременно на другом сигнальном проводе S''j (на фиг. 1 и 2) имеется состояние сигнала "High", так что входной транзистор T''ne (на фиг. 2) рассматриваемой пары Kij элементов связи является проводящим одновременно с переключающим транзистором T''nk, вследствие чего приданный сигнальный провод Z''i матричной выходной линии (линия строк) Zi будет разряжаться через этот элемент связи пары Kij элементов связи и получит потенциал USS.

Если, наоборот, на сигнальном проводе S'j (на фиг. 1 и 2) только что рассмотренный матричный входной линии имеется состояние сигнала "High", и если в соответствии с этим входной транзистор с каналом n-типа T'ne (на фиг. 2) соответствующей пары Kij элементов связи является проводящим одновременно с переключающим транзистором T'nk, то соответствующий сигнальный провод Z'i матричной выходной линии (линия строк) Zi будет разряжаться через соответствующий элемент связи этой пары Kij элементов связи и получит потенциал USS.

В таком случае одновременно на другом сигнальном проводе Sj (на фиг. 1 и 2) имеется состояние сигнала "LOW", так что входной транзистор T''ne (на фиг. 3) соответствующей пары Kij элементов связи является непроводящим, вследствие чего приданный сигнальный провод Z''i матричной выходной линии (линия строк) не будет разряжаться через этот элемент связи пары Kij элементов связи, а сохранит состояние потенциала UDD, если никакая другая точка связи, ведущая к этой матричной выходной линии (линии строк) Zi, не находится в состоянии переключения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2105430C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2103832C1 |

| ШИРОКОПОЛОСНОЕ УСТРОЙСТВО КОММУТАЦИИ | 1991 |

|

RU2103841C1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2106755C1 |

| УСТРОЙСТВО СВЯЗИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2013877C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2103831C1 |

| Устройство коммутации широкополосных сигналов | 1989 |

|

SU1838888A3 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1838887A3 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

Изобретение относится к технике коммутации и может быть использовано для построения коммутационных полей электронных АТС. Введение поперечного транзистора и схемы деблокировки входной линии позволяет согласовать параметры входных и выходных линий матрицы и повысить надежность коммутации сигналов длительности (широкополосных). 6 з.п. ф-лы, 4 ил.

| EP, 0264046, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-02-20—Публикация

1991-04-11—Подача