Изобретение относится к технике связи, в частности к устройствам коммутации широкополосных сигналов.

Известное, например из EP-A1-0 262 479 устройство коммутации широкополосных сигналов содержит матрицу точек коммутации на полевых транзисторах, выходы которой соответственно снабжены выходной усилительной схемой и управляемые накопительной и удерживающей ячейкой элементы коммутации которой образованы последовательной схемой нагруженного на своем управляющем электроде сигналом проключения или блокировки переключающего транзистора и подключенного своим управляющим электродом к соответствующей входной линии матрицы входного транзистора, которая обращенным от последовательной схемы главным электродом одного транзистора подключена к соответствующей выходной линии матрицы причем выходная линия матрицы через транзистор соединена с одним выводом источника рабочего напряжения.

Задача изобретения - уменьшение мощности потерь при достаточной степени помехозащищенности.

Задача решается тем что, что обращенный от последовательной схемы главный электрод другого транзистора соединен постоянно с другим выводом источника рабочего напряжения и выходы матрицы соответственно снабжены индивидуальной по выходным линиям матрицы выходной усилительной схемой, которая содержит последовательную схему подключенного своим управляющим электродом к другому выводу источника рабочего напряжения первого транзистора и нагруженного на своем управляющем электроде опорным напряжением второго транзистора, которая подключена обращенным от последовательной схемы главным электродом одного транзистора к соответствующей выходной линии матрицы и в которой обращенный от последовательной схемы, ведущий к выходу усилителя главный электрод другого транзистора соединен с названным другим выводом источника рабочего напряжения через нагрузочный транзистор, управляющий электрод которого через управляемый накопительной и удерживающей ячейкой транзистор соединен с названным другим выводом источника рабочего напряжения, и которая вместе с транзисторной последовательной схемой соответствующего элемента коммутации образует дифференциальный усилитель, который содержит таким образом индивидуальную по точкам коммутации первую ветвь и общую для точек коммутации, ведущих к одной и той же выходной линии вторую ветвь.

В случае следующей формы выполнения изобретения транзисторная последовательная схема каждого элемента коммутации соединена с названным другим выводом источника рабочего напряжения через нагрузочный транзистор, что обеспечивает симметрию обоих ветвей образованного дифференциального усилителя.

Согласно другой форме выполнения изобретения транзисторная последовательная схема каждого элемента коммутации подключена своим переключающим транзистором, а транзисторная последовательная схема соответствующего выходного усилителя подключена своим названным первым транзистором к выходной линии матрицы, что позволяет избежать емкостную нагрузку выходной линии матрицы за счет канальной емкости предвключенных транзисторов непроключенных элементов коммутации.

В другой форме выполнения изобретения транзисторная последовательная схема каждого элемента коммутации может быть подключена своим входным транзистором, а транзисторная последовательня схема соответствующего выходного усилителя своим названным вторым транзистором - к выходной линии матрицы. При этом возможно предусматривать в качестве источника опорного напряжения охваченный обратной связью КМОП-инвертор.

Согласно форме дальнейшего развития устройства коммутации в него введены входные задающие элементы, подключенные ко входам матрицы точек коммутации, причем каждый входной задающий элемент образован охваченным обратной связью КМОП-инвертором с одинаковыми размерами транзисторов, который образует со следующей, охваченной обратной связью КМОП-инвертирующей схемой кольцевую схему, причем эта следующая КМОП-инвертирующая схема содержит в своих обеих ветвях по одной последовательной схеме из двух транзисторов, внутренний транзистор которой подключен своим управляющим электродом к входу устройства коммутации широкополосного сигнала. При этом после МОП-инвертора предусмотрен включенный как повторитель напряжения дифференциальный усилитель.

На фиг. 1 приведена схема устройства коммутации широкополосных сигналов; на фиг. 2 - подробности его технической реализации согласно изобретения.

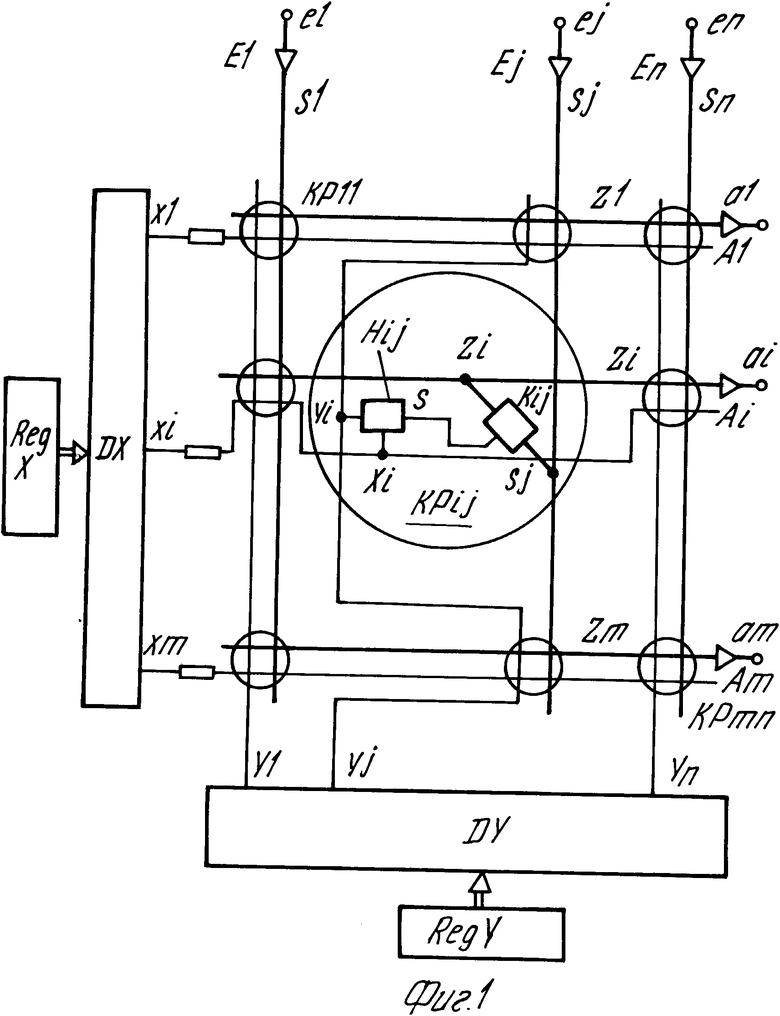

На фиг. 1 в необходимом для понимания изобретения объеме изображено устройство коммутации широкополосных сигналов (далее устройство связи), на ведущих к линиям столбцов si...sj...sn матрицы точек коммутации (названных далее также точками сопряжения или связи), входах el...ej...en которого предусмотрены входные задающие схемы El...Ej...En и проходящие от линий строк zl.. . zi. . . zm матрицы точек коммутации, выходы al...ai...am которого снабжены выходными усилительными схемами Al...Ai...Am.

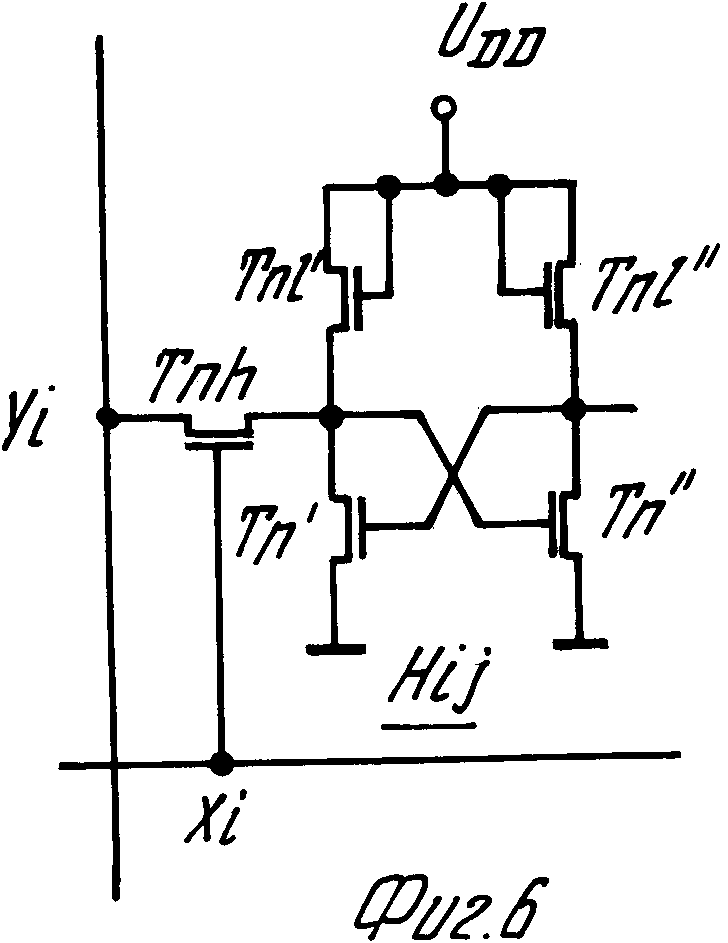

Матрицы точек коммутации содержит точки коммутации KPll...Kpij... KPmn, элементы коммутации которых (более подробно далее на примере точки коммутации Kij) могут управляться индивидуальной для точек коммутации накопительной и удерживающей ячейкой Hij (для точки коммутации Kij), выход s который ведет к управляющему входу соответствующего элемента коммутации (Kij в точке коммутации (Kij в точке коммутации KPij).

Накопительные и удерживающие ячейки ...Hij... управляются в соответствии с фиг. 1 с помощью двух управляющих декодеров, а именно декодер строк DX и декодера столбцов DY через соответствующие управляющие линии xl... xi... xm; yl...yj...en по двум координатам.

К тому же, как видно из фиг. 1, оба управляющих декодера DX, DY могут нагружаться от входных регистров Reg X, Reg Y общим для ряда матрицы (строки или столбца) точек коммутации адресом строки точек коммутации или соответственно столбца точек коммутации, на который они выдают на соответствующей адресу ряда точек коммутации управляющей линии соответственно управляющий сигнал "1". Встреча управляющего сигнала строки "1" и управляющего сигнала столбца"1" в точке пересечения соответствующей строки матрицы с соответствующим столбцом матрицы при установлении соответствующего соединения обуславливает в этом случае активацию находящейся там накопительной и удерживающей ячейки, например, накопительной ячейки Hij, в результате чего управляемый соответствующей накопительной и удерживающей ячейкой (Hij) элемент коммутации, в примере элемент коммутации Kij, становится проводящим.

Для запирания рассмотренного в примере элемента коммутации Kij при исчезновении соответствующего соединения управляющий декодер строки DX снова нагружается от входного регистра Reg X соответствующим адресом строки так, что декодер строки DX снова выдает на своей выходной линии xi управляющий сигнал строки "1" и одновременно декодер столбца DY нагружается от своего входного регистра Reg Y, например, фиктивным адресом или адресом столбца неподключенных точек коммутации так, что он выдает на своей выходной линии Yj управляющий сигнал столбца "0"; встреча управляющего сигнала строки "1" и управляющего сигнала столбца "0" обуславливает тогда обратную установку накопительной и удерживающей ячейки Hij, в результате чего управляемый ею элемент коммутации Kij запирается.

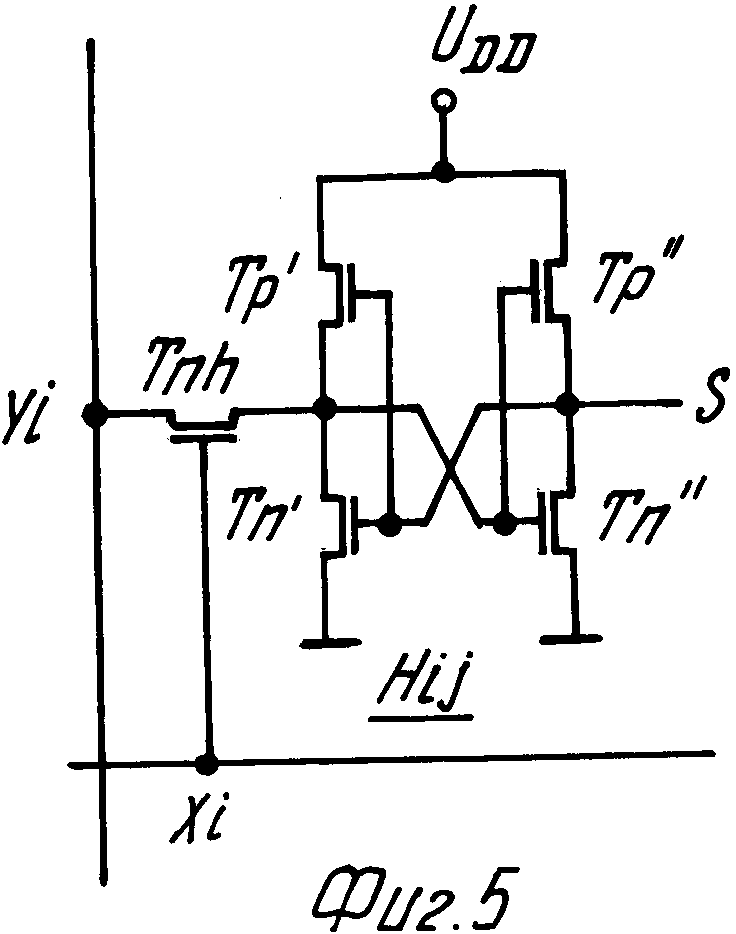

Накопительные и удерживающие ячейки ...Hij... могут быть выполнены известным по себе образом. Так, например, накопитальные и удерживающие ячейки могут быть образованы так, как это, например, известно из EP-A-0 238 834 и показано на фиг. 5 и 6 n -канальным транзистором Thn и двумя инверторными схемами с перекрестной связью (КМОП-инверторные схемы Tp', Tn'; Tp'', Tn'' на фиг. 5, n-МОП-инверторные схемы Tnl', Tn'; Tnl'', Tn'' на фиг. 5), причем инверторная схема на стороне входа соединена с соответствующим выходом yj управляющего декодера через n-канальный транзистор Thn, который со своей стороны на своем управляющем электроде нагружен выходным сигналом соответствующего выхода xi другого управляющего декодера, и причем инверторная схема на стороне выхода ведет к управляющему входу s соответствующего элемента коммутации.

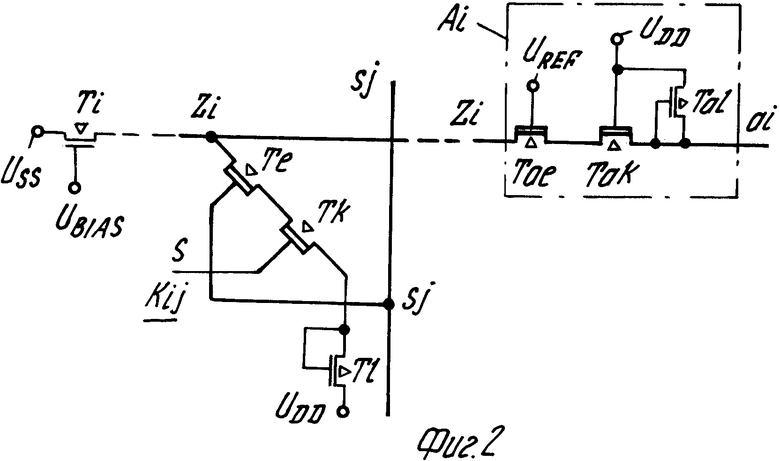

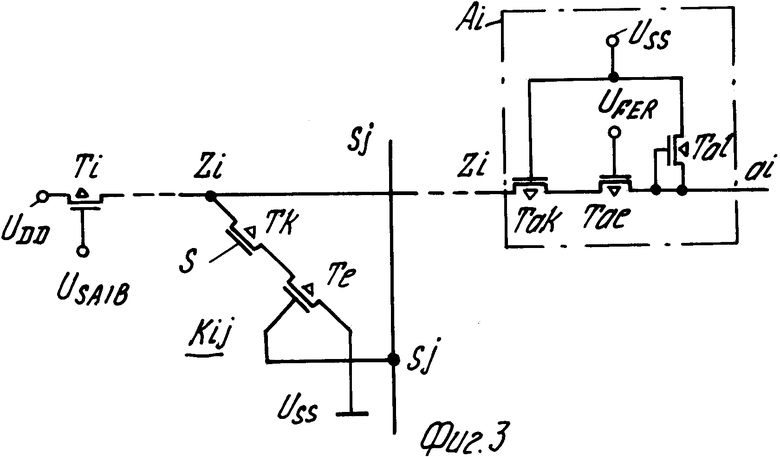

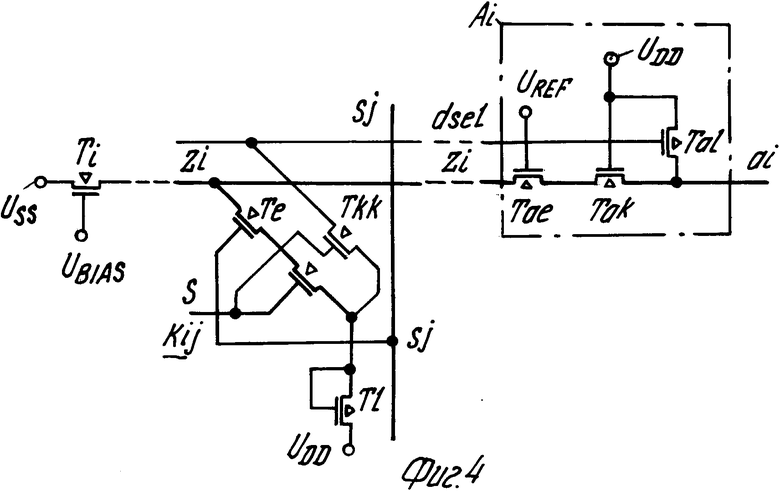

Примеры схемотехнической реализации элементов коммутации Kij показаны на фиг. 2 - 4. Элементы коммутации ...Kij... образованы последовательной схемой нагруженного на своем управляющем электроде накопительной и удерживающей ячейкой сигналом коммутации или блокировки переключающего транзистора Tk и подключенного своим управляющим электродом к соответствующей входной линии матрицы sj входного транзистора Te, которая обращенным от последовательной схемы главным электродом одного транзистора Tk (фиг. 3) или Te (фиг. 2 и 4) подключена к соответствующей выходной линии матрицы zi соединена с одним выводом (UDD на фиг. 3; USS на фиг. 2 и 4) источника рабочего напряжения UDD-USS через транзистор Ti, лежащий своим управляющим электродом на соответствующем напряжении смещения (USAIB на фиг. 3; UBIAS на фиг. 2 и 4), который образует вместе и источником рабочего напряжения источник тока. Обращенный от последовательной схемы главный электрод другого транзистора Te (фиг. 3) или соответственно Tk (фиг. 2 и 4) соединен постоянно с другим выводом USS, масса (фиг. 3) или соответственно UDD (фиг. 2 и 4) источника рабочего напряжения. При этом транзисторная последовательная схема Tk-Te каждого элемента коммутации Kij образует индивидуальную по точкам коммутации одну ветвь дифференциального усилителя, вторая ветвь которого образована индивидуальной по выходным линиям матрицы выходной усилительной схемой Ai и таким образом является общей для точек коммутации, ведущих к одной и той же выходной линии zi. Выходная усилительная схема Ai для этого содержит последовательную схему подключенного своим управляющим электродом к названному другому выводу USS (масса на фиг. 3); UDD (на фиг.2 и 4) источника рабочего напряжения первого транзистора Tak и нагруженного на своем управляющем электроде опорным напряжением (UFER на фиг. 3; UREF на фиг. 2 и 4) второго транзистора Tae, которая подключена обращенным от последовательной схемы главным электродом одного транзистора Tak (на фиг. 3) или Tae (на фиг. 2 и 4) к соответствующей выходной линии матрицы zi и в которой обращенный от последовательной схемы, ведущий к выходу усилителя ai главный электрод другого транзистора Tae (фиг. 3) или соответственно Tak (на фиг. 2 и 4) соединен с названным другим выводом (USS, масса на фиг. 3; UDD на фиг. 2 и 4) источника рабочего напряжения через включенный, при необходимости, как диод нагрузочный транзистор Tal.

При этом, как это в отличие от фиг. 3 показано на фиг. 2 и 4 транзисторная последовательная схема Tk-Te каждого элемента коммутации Kij может быть соединена с названным другим выводом (USS, масса на фиг. 3; UDD на фиг. 2 и 4) источника рабочего напряжения через включенный как диод нагрузочный транзистор Tl. Такой нагрузочный транзистор обеспечивает соответственно высокую симметрию образованного соответственно элементом коммутации Kij и выходным усилителем Ai дифференциального усилителя и нуждается в соответствующей площади. Эта потребность в площади отпадает при связанном с незначительной асимметрией дифференциального усилителя и следовательно требующем незначительного увеличения размаха сигнала отказе от использования индивидуального для точек связи нагрузочного транзистора Tl (на фиг. 2 и 4).

Как видно из фиг. 2 и 4, транзисторная последовательная схема Tk-Te каждого элемента коммутации Kij с ее входным транзистором Te может быть подключена к выходной линии матрицы, соответственно последовательная схема Tak-Tae индивидуального для выходной линии матрицы выходного усилителя Ai с названным вторым транзистором Tae подключена в этом случае к выходной линии матрицы zi. При этом входной транзистор Te при рассмотрении со стороны выходной линии матрицы zi является в известной степени "прозрачным", в результате чего изменения состояния сигнала во входной линии матрицы sj действуют через канальную емкость входного транзистора Te также при запертой точки коммутации Kij на выходную линию матрицы zi.

Этого проникновения можно избежать, если в транзисторной последовательной схеме Tk-Te каждого элемента коммутации Kij поменять последовательность выходного транзистора Te и переключающего транзистора Tk. Как это видно также из фиг. 3, тогда транзисторная последовательная схема Tk-Te каждого элемента коммутации Kij подключена своим переключающим транзистором Tk к выходной линии матрицы zi, и тогда транзисторная последовательная схема Tak-Tae соответствующего индивидуального по выходным линиям матрицы выходного усилителя Ai подключена своим названным первым транзистором Tak к выходной линии матрицы zi.

Согласно схематично показанному на фиг. 4 примеру выполнения рядом с каждой выходной линией матрицы zi предусмотрена ведущая к управляющему электроду нагрузочного транзистора Tal выходного усилителя сигнальная линия dsel, которой нагрузочный транзистора Tl каждого подключенного к соответствующей выходной линии матрицы zi элемента коммутации Kij соединен через дополнительный транзистор Tkk, который также как и переключающий транзистор Tk соответствующего элемента коммутации Kij подключен к его управляющему входу s. В результате этого с помощью зеркального отображения тока от ветви элемента коммутации на ветвь выходного усилителя дифференциального усилителя, образованного элементом коммутации Kij и индивидуальной по выходным линиям матрицы выходной усилительной схемой Ai, достигается преобразование дифференциального сигнала на один выход проключаемых через соответствующий элемент коммутации цифровых сигналов, что дает усиление сигнала 6 дБ, однако связано с соответствующей потребностью в площади и мощности.

Как показывают фиг. 2 - 4, в образованном элементом коммутации Kij и выходной усилительной схемой Ai, в известной степени "распределенном" дифференциальном усилителе транзисторы Te, Tae, Ti являются транзисторами типа, дополнительного к типу соответствующего нагрузочного транзистора Tal и при необходимости Tl.

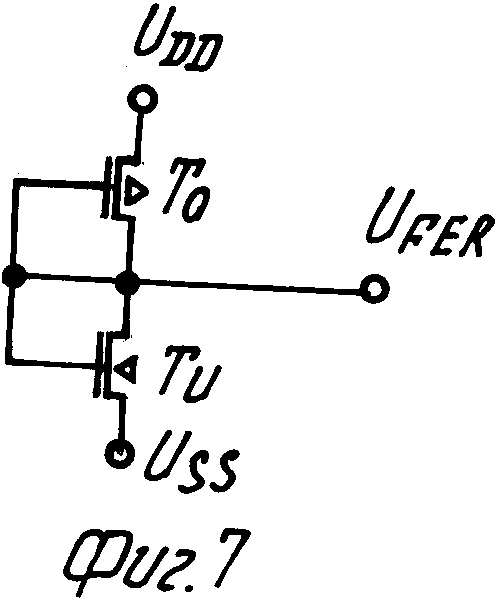

Как показывают фиг. 2 - 4, нагрузочные транзисторы Tal И Tl являются транзисторами p-типа канала, в то время как транзисторы выходного усилителя Tae и Tak, транзистор источника тока Ti и входной транзистор Te соответствующего элемента коммутации Kij и в примере выполнения также переключающий транзистор Tk являются транзисторами n-типа канала. Источник рабочего напряжения UDD-USS может при этом выдавать обычное для КМОП-схем рабочее напряжение, например 5B, из которого с помощью содержащей транзисторы Tp, Tu с соответственно выбранными параметрами схемы делителя напряжения в виде инверторной схемы с обратной связью, которая схематично показана на фиг. 7, можно отводить также опорное напряжение UREF, например 2B или соответственно превышающее пороговое значение напряжение смещения UBIAS, например, 1,5B.

Согласно фиг. 3 нагрузочный транзистор выходного усилителя Tal является транзистором n-типа канала, в то время как транзисторы выходного усилителя Tae и Tak и входной транзистор Te соответствующего элемента коммутации Kij, а в примере выполнения также соответствующий переключающий транзистор Tk являются транзисторами p-типа канала. Источник рабочего напряжения UDD-USS может при этом опять-таки выдавать обычное для КМОП-систем рабочее напряжение, например, 5 B, из которого опять-таки с помощью схемы делителя напряжения, которая схематично показана на фиг. 7, можно отводить также опорное напряжение UFER, например 3 B, или соответственно напряжение смещения транзистора источника тока USAIB, например, 3,5B.

Чтобы поддерживать отдельные элементы коммутации ...Kij... по возможности малыми, усиление "распределенного" дифференциального усилителя поддерживается относительно малым. Для возможно необходимого дальнейшего усиления выходного сигнала тогда можно к индивидуальной по выходным линиям матрицы выходной усилительной схемой Ai подключать, например, псевдо-p-МОП или соответственно -n-МОП-усилительный каскад, что не показано на чертеже, так как не является необходимым для понимания сущности изобретения.

Как уже упоминалось, источник опорного напряжения транзистора Tae выходного усилителя может быть образован в виде инвертора с обратной связью, работающего в качестве делителя напряжения, приложенного к источнику рабочего напряжение UDD-USS. Подобная реализованная p-канальным транзистором To и n-канальным транзистором Tu КМОП-инверторная схема делителя напряжения представлена на фиг. 7. При этом появляющееся на выходе этого работающего в качестве КМОП-инвертора опорное напряжение определяется размерами обоих транзисторов Tp и Tu.

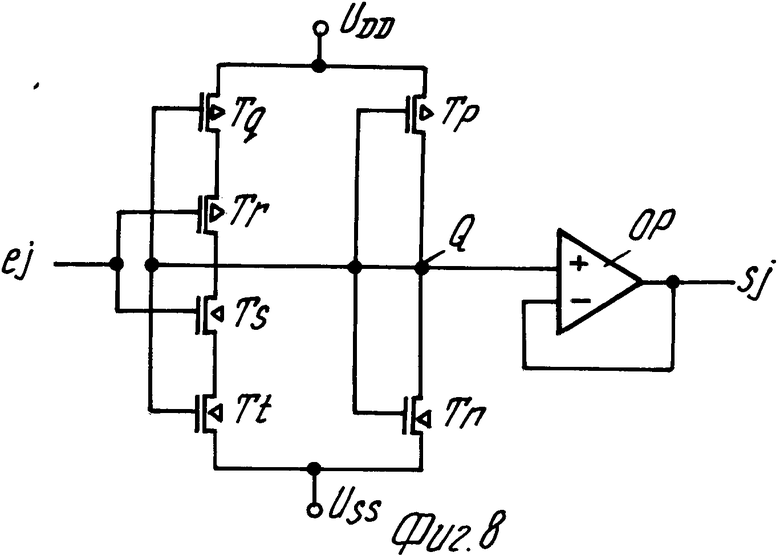

Одинаковые размеры могут также иметь транзисторы охваченных обратной связью К-МОП-инверторов Tp-Tn (фиг. 8), которые соответственно вместе с другой охваченной обратной связью схемой К-МОП-инверторной схемой Tq-Tr-Ts-Tt (на фиг. 8) образуя с ней кольцевую схему, образуют предусмотренные на выходах . ..ej... устройства коммутации широкополосных сигналов входные задающие схемы . . .Ej... . Кольцевые схемы двух охваченных по себе обратной связью К-МОП-инверторов являются сами по себе известными (из EP-A-0 250933). В схематично показанном на фиг. 8 примере выполнения названная другая охваченная обратной связью К-МОП-инверторная схема содержит при этом в своих обеих ветвях схемы соответственно последовательную схему двух транзисторов Tq-Tr или соответственно Ts-Tt, внутренний транзистор Tr или соответственно Ts которых соединен на своем управляющем электроде с входом ej устройства коммутации широкополосных сигналов.

Порог коммутации К-МОП-инверторов Tp-Tn определяется геометрическими размерами его подключенного к выводу UDD источника рабочего напряжения p-канальным транзистора Tp и его подключенного к другому выводу USS источника рабочего напряжения n-канальным транзистора Tn; при совпадении их размеров с размерами обоих соответствующих транзисторов (To и Tu) выполненного согласно фиг. 7 в виде КМОП-инверторной схемы делителя напряжения источника рабочего напряжения он лежит при выдаваемом им опорном напряжении. Это имеет следствием, что также при колебаниях рабочего напряжения UDD-USS или также при изменении технологических параметров уровень "высоко" и уровень "низко" коммутируемого от входа ej сигнала через устройство коммутации широкополосных сигналов цифрового сигнала относительно уровня действующего в выходной усилительной схеме Ai (фиг. 2 и 4) опорного напряжения UREF (фиг. 2 и 4) или соответственно UFER (фиг. 3 и 7) остаются постоянными в широких пределах.

При этом высота уровня определяется геометрическими размерами подключенного к выводу UDD источника рабочего напряжения p-канального транзистора Tq и подключенного к выводу USS источника рабочего напряжения n-канального транзистора Tt названной другой К-МОП-инверторной схемы. При появляющемся на входе ej поля коммутации сигнале низкого уровня через проводящий вследствие этого p-канальный транзистор Tr p-канальный транзистор Tq названной другой К-МОП-инверторной схемы Tq-Tr-Ts-Tt включен параллельно p-канальному транзистору Tp охваченного обратной связью К-МОП-инвертора Tp-Tn и при появляющемся на входе ej поля коммутации сигнале высокого уровня через проводящий вследствие этого n-канальный транзистор Ts n-канальный транзистор Tt названной другой К-МОП-инверторной схемы Tq-Tr-Ts-Tt включен параллельно n-канальному транзистору Tn охваченного обратной связью К-МОП-инвертора Tp-Tn. Эта параллельная схема изменяет действующий в точке Q коэффициент деления напряжения так, что при полном К-МОП-размахе сигнала в 5B появляющихся на входе ej поля коммутации (фиг. 1 и 8) цифровых сигналов цифровые сигналы, появляющиеся на выходе входной задающей схемы Ej (фиг. 1 и 8) и тем самым на соответствующей входной линии матрицы (фиг. 1 и 8), уменьшены в своем размахе сигнала до значения, например, 1 B. При этом эти цифровые сигналы могут быть буферированы (фиг. 8) с помощью включенного как повторитель напряжения дифференциального усилителя OP.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1991 |

|

RU2105431C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2105430C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2103832C1 |

| Устройство коммутации широкополосных сигналов | 1989 |

|

SU1838888A3 |

| УСТРОЙСТВО СВЯЗИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2013877C1 |

| ШИРОКОПОЛОСНОЕ УСТРОЙСТВО КОММУТАЦИИ | 1991 |

|

RU2103841C1 |

| УСТРОЙСТВО ПРОСТРАНСТВЕННОЙ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1986 |

|

RU2011304C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНТЕГРАЛЬНЫМ МОДУЛЕМ | 1987 |

|

RU2071636C1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

Изобретение относится к технике связи, в частности к устройствам коммутации широкополосных сигналов. Согласно изобретению выходы матрицы соответственно снабжены индивидуальными усилительными схемами (приводится их выполнение) и это (совместно с включением одного из электродов транзистора элемента коммутации) приводит к образованию дифференциального усилители. Устройство позволяет уменьшить мощность потерь при достаточной степени помехозащищенности. 6 з. п. ф-лы, 8 ил.

| ЕР, патент N 262479, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-03-10—Публикация

1989-07-27—Подача