Изобретение относится к технике связи, в частности к устройствам коммутации, выполненным в виде матрицы на полевых транзисторах.

Известное (например из EP-A-O 262479) устройство связи широкополосных сигналов имеет матрицу точек связи в PET-технике, чьи элементы связи образованы по мере надобности с помощью нагружаемого на своем управляющем электроде соединяющим или же замыкающим сигналом, подключенного своим главным электродом к соответствующей исходящей линии матрицы переключающего транзистора, причем элементы связи имеют по мере надобности один образующий с переключающим транзистором последовательное соединение предвключенный транзистор, который своим управляющим электродом подключен к соответствующей входной линии матрицы, а обращенный от последовательного соединения главный электрод которого через считывающий транзистор соединен с одним вводом источника рабочего напряжения, с другим вводом которого через предварительно заряжающий транзистор соединена текущая выходная линия матрицы, причем зарядный транзистор и считывающий транзистор в противоположном друг другу направлении по мере надобности на своем управляющем электроде нагружены разделяющим период переключения двоичных знаков на фазу предварительной зарядки и собственную фазу переключения тактом настройки поля связи, так что в каждой предварительной фазе при замкнутом считывающем транзисторе выходная линия матрицы через предварительно заряжающий транзистор заряжается, по крайней мере, приблизительно, на имеющийся на указанном другом вводе источника рабочего напряжения потенциал. Это известное широкополосное сигнальное устройство связи, которое может содержать индивидуальные считывающие транзисторы для элементов связи или индивидуальные считывающие транзисторы входной линии матрицы или индивидуальные считывающие транзисторы выходной линии матрицы, для настройки этих считывающих транзисторов нуждаются в собственных, проходящих через матрицу точек связи тактовых линиях, что требует соответствующую занимаемую площадь и несет с собой соответствующую емкостную нагрузку исходящей линии матрицы; тактовое распределение и связи между входной линией матрицы и выходной линией матрицы для обеспечения достаточной помехозащищенности требуют достаточно больших амплитуд сигналов на выходных линиях матрицы, что связано с относительно высокой потребляемой мощностью.

Известное (например из EP-A-O 354252) другое устройство связи широкополосных сигналов содержит матрицы точек связи в ГЕТ-технике, чьи входы могут быть снабжены по мере надобности одной схемой возбуждения на входе, чьи выходы снабжены по мере надобности одной схемой усиления на выходе и чьи управляемые по мере надобности одной фиксирующей ячейкой памяти элементы связи образованы по мере надобности одной схемой последовательного соединения одного из своем управляющем электроде нагружаемого сигналом последовательного перемыкания или же замыкания, переключающего транзистора и одного своим управляющим электродом подключаемого к соответствующей входной линии матрицы входного транзистора, которая обращенным от схемы последовательного соединения главным электродом одного транзистора подключена к соответствующей выходной линии матрицы, причем выходная линия матрицы через один транзистор соединена с одним вводом источника рабочего напряжения; причем таким образом, что обращенный от схемы последовательного включения главный электрод другого транзистора постоянно соединен с другим вводом источника рабочего напряжения и что схема последовательного включения транзистора каждого элемента связи образует одно индивидуальное для точки связи ответвление дифференциального усилителя, чье по мере надобности для ведущих к одной и той же выходной линии точек связи общее другое ответвление образовано посредством содержащей последовательное соединение расположенного своим управляющим электродом на другом вводе источника рабочего напряжения, первого транзистора и нагружаемого на своем управляющем электроде опорным напряжением, второго транзистора, индивидуальной для выходной линии матрицы схемы усиления на выходе, которая обращенным от схемы последовательного соединения главным электродом одного транзистора подключена к соответствующей линии выхода матрицы, а обращенный от схемы последовательного включения, ведущий к усиливающему выходу главный электрод другого транзистора, который через один нагрузочный транзистор соединен с указанным другим вводом источника рабочего напряжения.

Достигаемый технический результат заключается в снижении требований к генератору опорного напряжения и повышении точности согласования транзисторов.

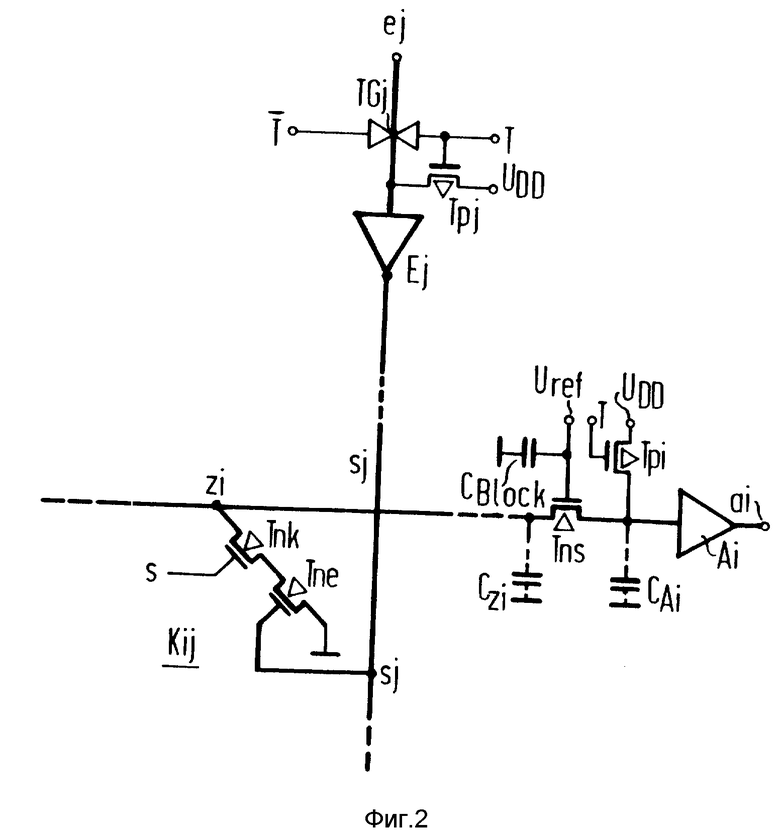

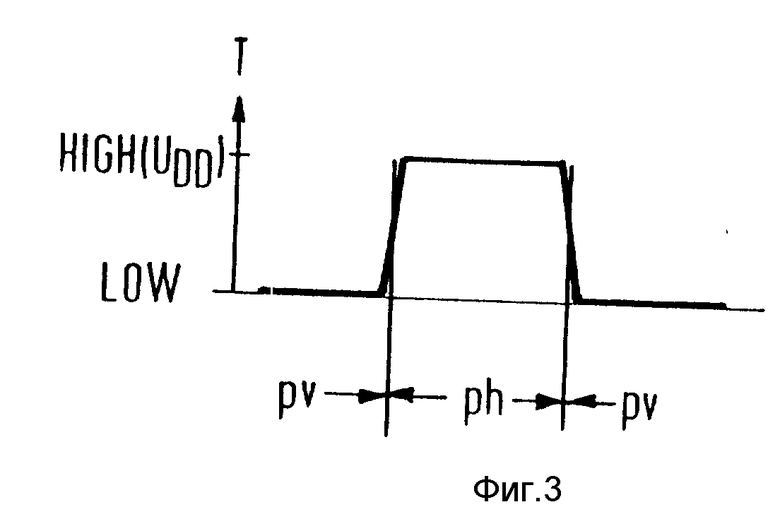

На фиг. 1 представлена структурная электрическая схема широкополосного устройства коммутации; на фиг. 2 - детали его схемной реализации согласно изобретению; на фиг.3 - такт переключения поля связи.

На чертеже фиг.1 схематично в необходимом для понимания изобретения объеме показано широкополосное сигнальное устройство связи, на ведущих к линиям столбцов S1. . . Sj...Sn матрицы точек связи входах e1...ej ....en которого предусмотрены схемы возбудителя E1...Ej ...En на входе, а достигаемые линиями строк Z1. ..Zi...Zm матрицы точек связи выхода а1...аi...am которого снабжены схемами выходных усилителей А1...Аi...Am.

Матрица точек связи содержит точки KP11...KPij...KPmn связи, элементы связи которых, как это дальше отдельно указано при точке KPij связи для ее элемента Kij связи, могут быть управляемыми (при точке KIij связи) по мере надобности одной индивидуальной для точек связи, фиксирующей ячейкой Hij памяти, выход S которой ведет к управляющему входу текущего элемента связи (Kij при точке KPij связи).

Фиксирующие ячейки ...Hij... памяти согласно фиг. 1 настраиваются двумя дешифраторами, а именно одним дешифратором строк X и одним дешифратором столбцов DY, через соответствующие линии настройки x1...xi...xm, y1...yj... yn в двух координатах.

К тому же, как это видно из фиг. 1, оба настраивающих дешифратора DX, DY от входных регистров Reg X, Reg У могут быть нагружены по мере надобности одним общим для одного матричного ряда (строки или же столбцы) точек связи адресом строк точек связи или же столбцов, на который по соответствующей текущему адресу рядов точек связи, управляющей линии они выдают по мере надобности один управляющий сигнал "1". Встреча одного сигнала "1" управления строкой и одного сигнала "1" управления столбцом в точке пересечения соответствующей строке матрицы с соответствующим столбцом матрицы при синтезе соответствующей связи осуществляет тогда активацию находящейся там фиксирующей ячейки памяти, например ячейки Hij памяти, с результатом, что управляемый соответствующей фиксирующей ячейкой (Hij) памяти элемент связи, например элемент Kij, становится проводящим.

Для того, чтобы рассматриваемый в примере элемент Kij связи при создании соответствующей связи опять закрылся, управляющий дешифратор DX от входного регистра Reg X снова нагружается соответствующим адресом строки, так что строчный дешифратор DX снова по своей выходной линии xi выдает строчный управляющий сигнал "1", и одновременно столбцовый дешифратор DY из своего входного регистра Reg Y нагружается, например, одним пустым адресом или адресом одного столбца неозвучиваемых точек связи, так что он на своей выходной линии Yj выдает столбцовый управляющий сигнал "0"; встреча строчного управляющего сигнала "1" и столбцового управляющего сигнала "0" производит тогда обратную загрузку фиксирующей ячейки Hij памяти с результатом, что запирается управляемый ею элемент Kij связи.

То, как могут быть реализованы элементы Кij связи, разъясняется на фиг. 2: элементы ...Кij...связи образованы по мере надобности одной схемой последовательного соединения одного, на своем управляющем электроде от фиксирующей ячейки памяти нагружаемого одним переключающим или запирающим сигналом, переключающего транзистора Тпк и одного своим управляющим электродом подключаемого к соответствующей входной линии Sj, матрицы входного транзистора Тпк, которая обращенным от схемы последовательного соединения главным электродом одного переключающего транзистора Тпк подключена к соответствующей выходной линии матрицы; выходная линия Zi матрицы, со своей стороны, через п-канальный последовательно включенный п-канальный транзистор Тпs соединена с входом схемы выходного усилителя Аi, причем на входе схемы выходного усилителя Аi находится, кроме того, зарядный транзистор Трs, через который (в ряде с последовательно включенным "n"-канальным транзистором Тns) соответствующая выходная линия Zi матрицы в каждой фазе рV зарядки (на фиг. 3) одного разделяемого одним тактом Т (на фиг. 3) управления полем связи на такую фазу зарядки pV (нa фиг. 3) и фазу оценки рh (на фиг. З) периода переключения двоичного разряда соединена с источником UDD потенциала заряда. Транзистор предварительного заряда Тр к тому же расположен своим управляющим входом на линии тактирующего сигнала Т (на фиг. 2) такта управления поля связи.

Введенный между выходной линией Zi матрицы и выходным усилителем Ai п-канальный последовательно включенный n - канальный транзистор Тпs своим управляющим электродом лежит на источнике Uref опорного потенциала, причем для опорного потенциала (Uref) и упомянутого ранее зарядного потенциала (UDD) действует соотношение Uref UDD. Посредством конденсатора CBlock источник опорного потенциала Uref хорошо заблокирован против массы.

Расположенный между выходной линией Zi матрицы и выходным усилителем Аi п-канальный параллельно включенный транзистор Тпs вместе с расположенным на входе выходного усилителя Аi транзистором предварительного заряда Трi образует схему переноса зарядов, к которой еще вернутся при последующем дальнейшем объяснении принципа действия показанного на фиг. 2 расположения элементов схемы; однако прежде всего следует еще рассмотреть схемное выполнение на ведущем к линии столбце Sj матрицы точек связи входа ej устройства связи широкополосных сигналов.

Согласно фиг. 2 перед входной линией Sj матрицы (линией столбца) включена схема входного возбудителя Ej, перед которой, в свою очередь, включена расположенная двумя своими управляющими входами на ведущий такт управления полем связи линии тактирующего сигнала Т или же на ведущей выполняющей логическую операцию "НЕ" такт управления поля связи линии тактирующего сигнала Т стробирующая схема ТGj переноса. На входе схемы выходного возбудителя Ej расположен другой транзистор предварительного заряда Трj, который своим управляющим электродом тоже соединен с линией тактирующего сигнала Т фазы зарядки и фазы оценки.

Представленная на фиг. 2 схема работает следующим образом:

Во время фазы зарядки (рV на фиг. 3) является проводящим расположенный со стороны входа другой транзистор предварительного заряда Трj, так что вход схемы входного возбудителя Ej принимает управляющий потенциал, на основании которого выход входного возбудителя Ej и тем самым линия Sj столбца попадает на опорный потенциал (ОV, корпус) с результатом, что входной транзистор Тпе - а тем самым и схема последовательного соединения входного транзистора Тпе и переключающего транзистора Тпк - попадает в состояние запирания.

Вход выходного усилителя Аi в фазе загрузки (pV фиг. 3) через зарядный транзистор Трi поднимается на потенциал UDD, что дает в результате то, что через п-канальный последовательно включенный транзистор Тпs выходная линия Zi матрицы (строчная линия) попадает на потенциал Uref - Utn, Utn - пороговое напряжение последовательно включенного транзистора Тпs.

С переходом тактирующего сигнала Т управления поля связи (на фиг. 3) от LOW на HICH (VDD) кончается фаза зарядки (pV на фиг. 3) и начинается следующая фаза оценки (рh на фиг. 3). Разрядный транзистор Трj на входе схемы входного возбудителя Ej запирается, а стробирующая схема ТGj передачи становится проводящей с результатом, что сообразно с как раз находящимся на входе Ej переключаемым битом входная линия матрицы (линия столбца) Sj остается на своем прежнем потенциале (ОV, масса) или заряжается.

В первом случае потенциал выходной линии матрицы (строчной линии) Zi остается неизменным, в то время как во втором случае выходная линия Zi матрицы через схему последовательного соединения входного транзистора Tпе переключающего транзистора Тпе как раз рассматриваемого, находящегося в состоянии переключения элемента Кij связи разряжается. Посредством этого изменения потенциала на выходной линии Zi матрицы п-канальный последовательно включенный транзистор Тпs, который раньше в фазе зарядки при недостижении своего порогового напряжения попал в закрытое состояние, по причине теперешнего превышения своего порогового напряжения становится опять проводящим, а электрический заряд попадает от заряженного на потенциал UDD входа выходного усилителя Аi через последовательно включенный транзистор Тпs на выходную линию Zi матрицы. При этом для соотношения размаха UAi напряжения на входе схемы выходного усилителя Аi с размахом Uzi напряжения на выходной линии Zi матрицы действительна пропорция:

где Czi - емкость выходной линии Zi матрицы, в СAi - активная на входе выходного усилителя Аi емкость схемы. Так как емкость Сzi длинной выходной линии Zi матрицы (сточной линии) намного больше емкости СAi на входе схемы выходного усилителя Аi, то это ведет на входе выходного усилителя Аi к соответствующему усилению напряжения, так что небольшой размах сигнала на выходной линии Zi матрицы уже достаточен для обеспечения надежного обозначения по мере надобности переключенного двоичного знака на выходном усилителе Аi. Этот двоичный знак может тогда в конце фазы оценки (ph на фиг. 3) тактироваться с выходного усилителя Аi.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2106755C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1991 |

|

RU2105431C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2105430C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2103832C1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

| УСТРОЙСТВО ПРОСТРАНСТВЕННОЙ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1986 |

|

RU2011304C1 |

| Устройство коммутации широкополосных сигналов | 1989 |

|

SU1838888A3 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

| УСТРОЙСТВО СВЯЗИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2013877C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНТЕГРАЛЬНЫМ МОДУЛЕМ | 1987 |

|

RU2071636C1 |

В матрицей точек связи в ГЕТ-технике, чьи управляемые по мере надобности одной фиксирующей ячейкой памяти элементы связи образованы по мере надобности одной схемой последовательного соединения одного переключающего транзистора и одного входного транзистора, по мере надобности между выходной линией матрицы и последующей схемой выходного усилителя введен расположенный своим управляющим электродом на источнике опорного потенциала п-канальный последовательно включенный транзистор, который вместе с расположенным на входе схемы выходного усилителя зарядным транзистором образует схему передачи зарядка, которая осуществляет усиление напряжения. И на входе включенной перед входной линией матрицы схемы входного возбудителя предусмотрен другой транзистор предварительного заряда, который своим управляющим электродом тоже подключен к линии тактирующего сигнала фаза зарядки - фаза оценки, от которой одновременно устраняется также включенная перед схемой входного возбудителя стробирующая схема передачи. 2 з.п. ф-лы, 3 ил.

| EP, патент, АО-354252, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-01-27—Публикация

1991-09-25—Подача