3161574

Изобретение относится к вычисли тельной технике и может быть использовано в специализированных системах многоканальной обработки сигналов и в измерительно-вычислительных системах.

Цель изобретения - расширение области применения за счет многоканальной обработки данных,.„

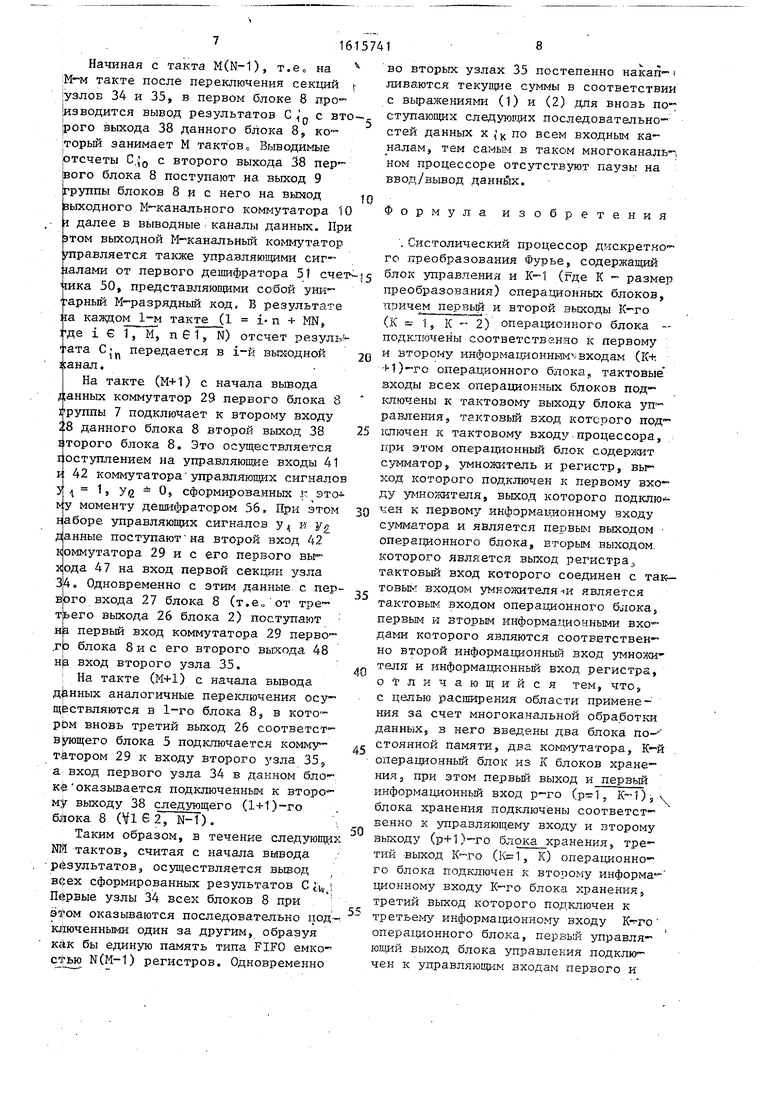

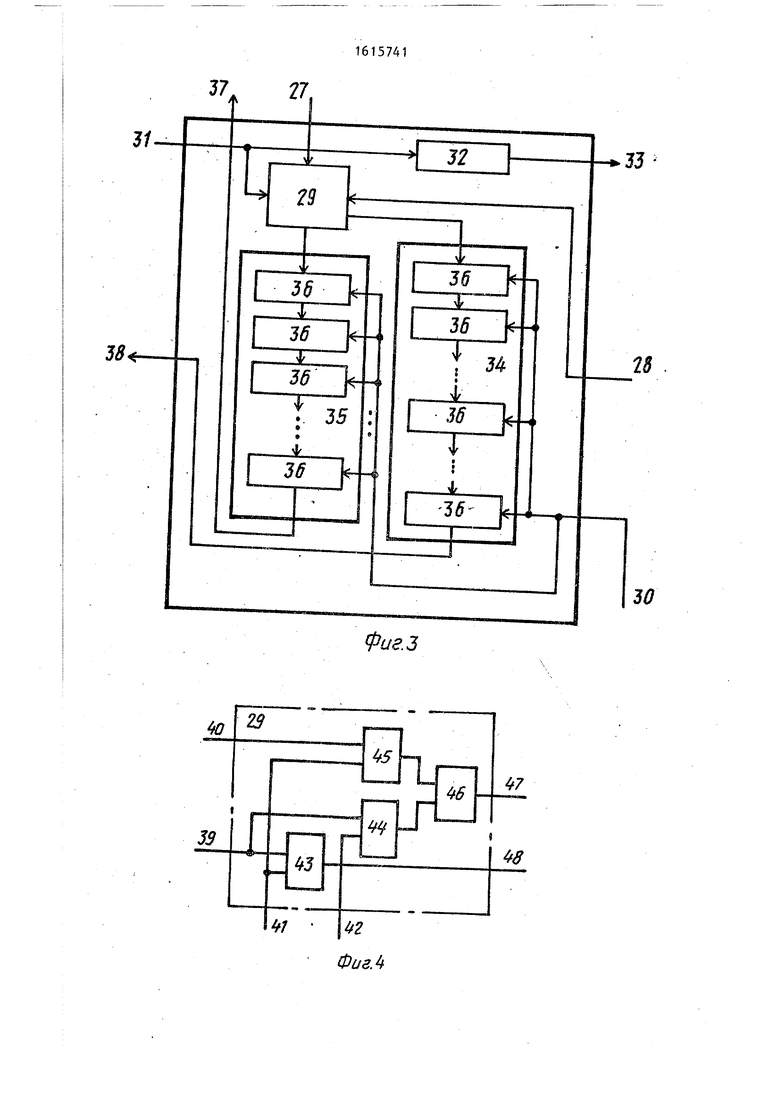

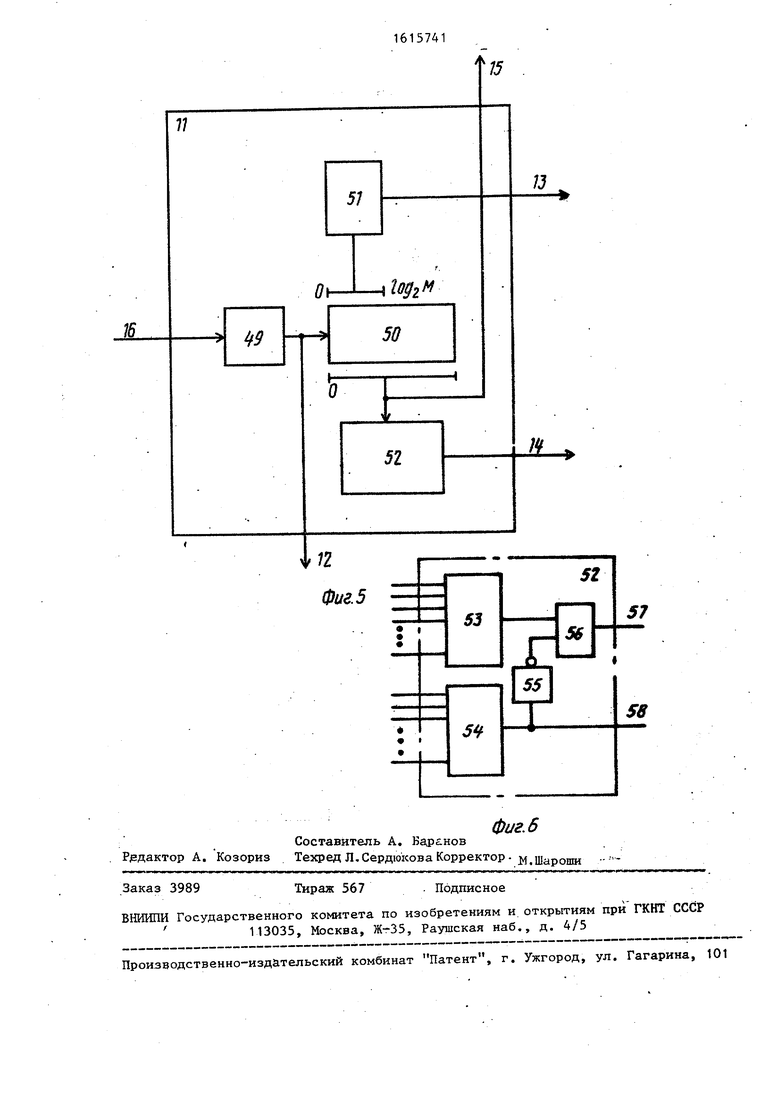

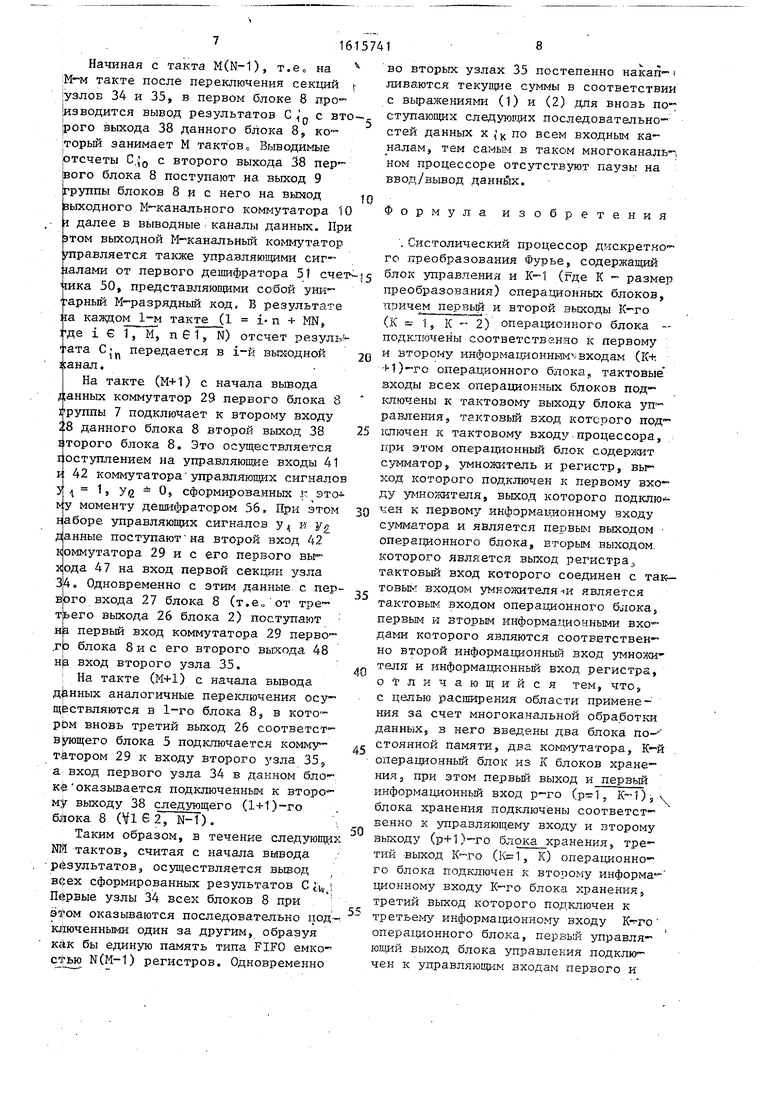

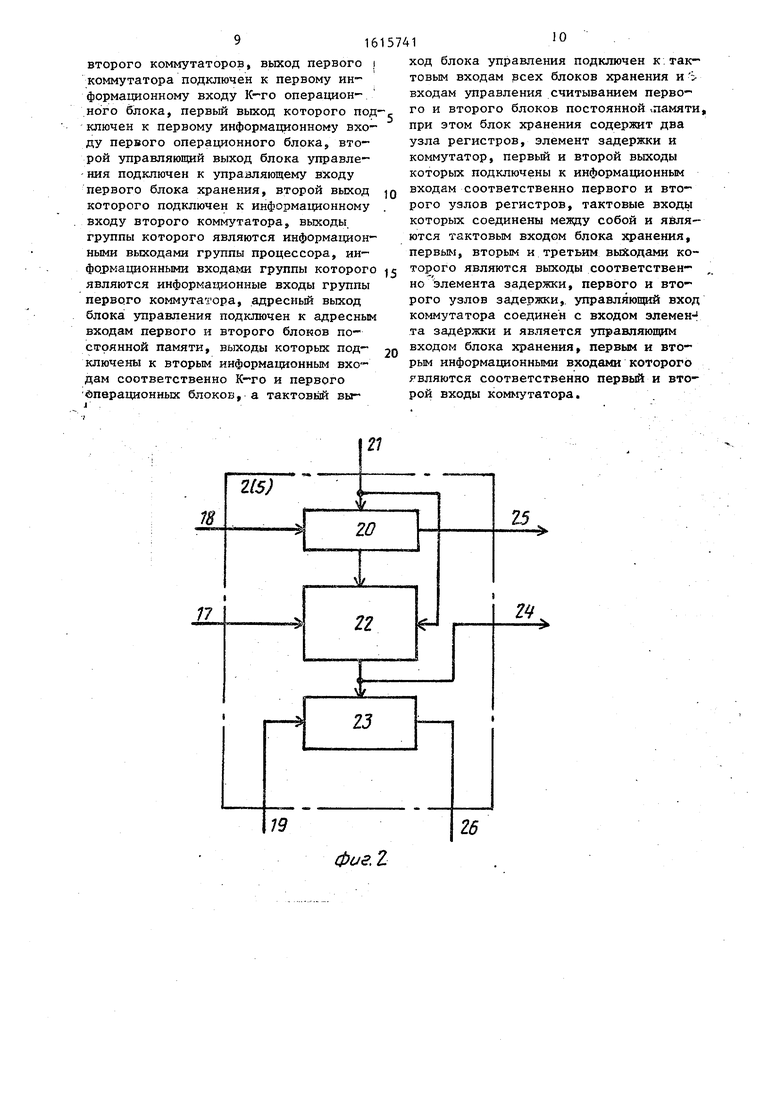

На фиг, 1 представлена функциональная схема (многоканального) систолического ДПФ-процессора; на фиг. 2 - функциональная схема опера1щонного блока; на фиг„ 3 - функциональная ,с схема блока хранения; на фиг. 4 - функциональная схема коммутатора блока хранения; на фиг, 5 - функциональная схема блока управленияj на фиг. 6- функциональная схема второго дешифра-.2п тора состояний счетчика.

Процессор (фиг, 1) содержит (входной М-канальньй) коммутатор 1, опера- ционный блок 2, блок 3 постоянной памяти взвешивающих множителей), сие- 25 толическую матрицу 4 из (N-l)-ro операционного блока 5, блок 6 постоянной памяти.(весовых множителей), грзттпу 7 из N блоков 8 хранения, выход 9 группы 7, (вькодной М-канальньй) коммутатор 10, блок 11 управления, вьй выход 12 блока управления, пер- : вый 13 и второй 14 управляющие выходы блока управления, адресный выход 15 блока управления и тактовьй вход 16.35

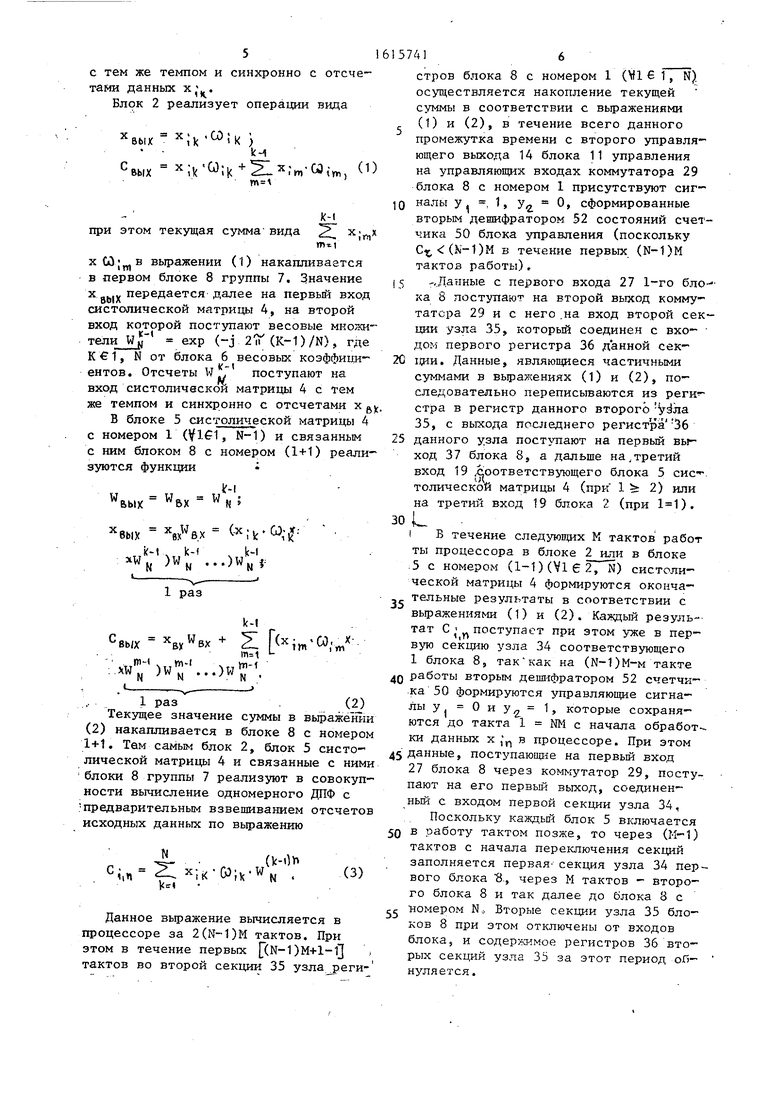

Операционньй блок процессора (фиг. 2) содержит первьй 17, второй , 18 и третий 19 входы, регистр (весовых коэффициентов) 20, тактовый вход 21, умножитель 22, сумматор 23, первьй 24, второй 25 и третий 26 выходы.

Каждьй блок 8 хранения (фиг. 3) содержит входы 27 и 28, коммутатор 29, тактовьй вход 30, вход 31, элемент 32 задержки, выход 33, узлы 34 и 35 регистров из (М-1) И|М регистров 36 соответственно и выходы 37 и 38.

Коммутатор 29 (фиг. 4) содержит первьй 39 и второй 40 вход данных, вход 41, управляющий вход 42, эле- менты И 43 - 45, элемент ИЖ 46, пер,ь- вый 47 и второй 48 выходы.

30

40

45

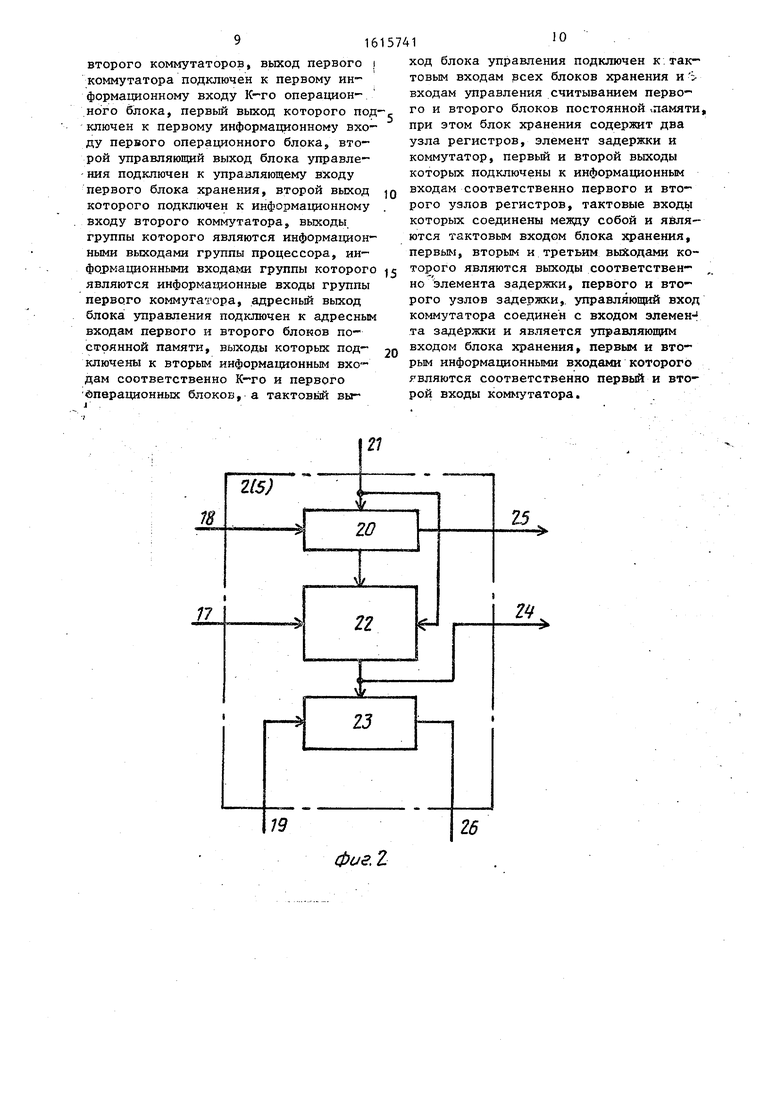

Блок 11 управления (фиг, 5) содержит генератор 49 тактовых импульс.ов lo gj, NM-разрядньй двоичньй счетчик 50, первьй дешифратор 51 состояний счетчика и второй дешифратор 52.

.„

,с п

5 5

0

0

5

14

Второй дешифратор 52 блока управления (фиг. 6) содержит 1о§2 (Н-1)М-й элемент ИЛИ 53, log N-входной элемент ИЛИ 54, элемент НЕ 55, элемент И 56, выходы 57 и 58.

Процессор работает следующим образом.

Блок 3 взвешиваю1ц:их множителей емко- стью слов имеет страничную организа- 1ЩЮ из N страниц по М слов. В каждой странице блока 3 записаны взвешивающие множители для отсчетов данных с номерами xj|, где i е 1, М, а К - порядковый номер страницы. Для обращения к блоку 3 по адресному выходу

2

5

15 блока 11 передается (log, N + 1о§2 М)-разрядньй адрес.

Блок 6 весовых множителей имеет емкость N слов, для обращения к нему требуется logg N-разрядньй адрес, что достигается подключением старших logg N разрядов адресного выхода 16 блока 12 к адресному входу данного блока.

Перед началом работы процессора счетчик 50 обнулен и тем самым на управляющих входах 41 и 42 коммутаторов 29 всех блоков 8 поступают управляющие-сигналы, обнуляющие все ре гистры 36 всех секций 34 и 35 памяти - типа FIFO.

Пусть М входных параллельных потоков данных формируются так, что в те-- чение очередньк М тактов времени на вход процессора по одному отсчету данных в кахдьй такт, при этом последовательно поступают М отсчетов данных X от каждого из М jca- налов - источников данных ( € Т, ll) , где п 50, N-1, номер отсчета данных, - N - длина входной:- последовательности (число отсчетов) . данных, а i - номер канала данных

Отсчеты данных -х; (Vi-C l, М; К€ G1, N) поступают на входы входного М-канального коммутатора 1, -управляю- шдй вход которого соединен с выходом первого дешифратора 51 состояний счетчика 50. В результате на 1-м такте ра ,боты (1 i-k, i ei,. MF К 61, N) К-Й отсчет данных от i-го канала переда - - ется с входа коммутатора 1 на его выход и далее на первый вход операци-: онного блока 2.

На второй вход блока 2 поступают с выхода блока 3 взвешивающих множи- j телей отсчеты весовой функции окна

с тем же темпом и синхронно с отсчетами данных х.

Блок 2 реализует операции вида

вых I k )

М

вых ,, (1)

гл

k-i

при этом текущая сумма вида

mil

im

хСО;,в выражении (1) накапливается в первом блоке 8 группы 7. Значение

X

вых

передается далее на первьй вход

систолической матрицы 4, на второй вход которой поступают весовые множи- тели ехр (-J 2 (К-1) /N), где К € 1, N от блока 6 весовых коэффициНентов. Отсчеты W ;, поступают на

вход систолической матрицы 4 с тем же темпом и синхронно с отсчетами х

В блоке 5 систолической матрицы 4 с номером 1 (fiei, N-1) и связанным с ним блоком 8 с номером (1+1) реализуются функции

М

N

шк WBX W

вых ( ;гЦ-к - )w J, ...)w j f

1 раз

вых +

k-l

Z

m

-I

Е: (im W;

Xm

N N

.. 1 раз. (2)

Текущее значение суммы в выражеюзи (2) накапливается в блоке 8 с номером 1+1. Там самьк. блок 2, блок 5 систолической матрицы 4 и связанные с ними

блоки 8 группы 7 реализуют в совокупности вычисление одномерного ДПФ с

предварительным взвешиванием отсчетов исходных данных по вьфажению

N

«

(k-Oh

;к-0з;к-м . (3)

Данное вьгражение вычисляется в процессоре за 2(N-1)M тактов. При этом в течение первых (N-1)M+l-l3 тактов во второй секции 35 узла реги157416

стров блока 8 с номером 1 (VI € 1, N). осуществляется накопление текущей суммы в соответствии с выражениями (1) и (2), в течение всего данного промежутка времени с второго управляющего выхода 14 блока 11 управления на управляющих входах коммутатора 29 блока 8 с номером 1 присутствуют сиг-

0 налы уJ , 1, У О, сформированные вторым дешифратором 52 состояний счетчика 50 блока управления (поскольку Ct(N-1)M в течение первых (N-1)M тактов работы),

(5 -.Данные с первого входа 27 1-го блока 8 поступают на второй выход коммутатора 29 и с него .на вход вто.рой секции узла 35, который соединен с вхо- дом первого регистра 36 данной сек20 1ЩИ. Данные, являющиеся частичными суммами в выражениях (1) и (2), последовательно переписываются из реги - стра в регистр данного второго 35, с выхода последнего регистра 36

25 данного узла поступают на первый выход, 37 блока 8, а дальше на,третий вход 19 соответствующего блока 5 сис-. толической матрицы 4 (при 1 Ь 2) или на третий вход 19 блока 2 (при ).

30 L

I в течение следующих К тактов работ ты процессора в блоке в блоке :5 с номером (1-1) (VI 62, N) систолической матрицы 4 формируются оконча35 результаты в соответствии с выражениями (1) и (2). Каждый резуль- С поступает при этом уже в первую секцию узла 34 соответствующего 1 блока 8, так как на (N-I)M-M такте

4Q работы вторым дeшiфpaтopoм 52 счетчика 50 формируются управляющие сигналы у О и у 1, которые сохраняются до такта 1 Ш с начала обработки данных к , f в процессоре. При этом

5 данные, поступающ11е на первый вход 27 блока 8 через коммутатор 29, поступают на его первьй выход, соединенный с входом первой секции узла 34, Поскольку каждый блок 5 включается

0 в работу тактом позже, то через (М-1) тактов с начала переключения секций заполняется первая- секция узла 34 первого блока tJ., через М тактов - второго блока 8 и так далее до блока 8 с 5 номером No Вторые секции узла 35 блоков 8 при этом отключены от входов блока, и содержимое регистров 36 вторых секций узла 35 за этот период обнуляется.

Начиная с такта M(N-1), т.е„ на |М-м такте после переключения секций |узлов 34 и 35, в первом блоке 8 про- зводится вывод результатов С i- с второго выхода 38 данного блока 8, ко- ;торый занимает М тактов о Выводимые (отсчеты С.;о с второго выкода 38 пер- |вого блока 8 поступают на выход 9 группы блоков 8 и с него на выход выходного М канального коммутатора 10 я далее в выводные каналы данных. При этом выходной М-канальный коммутатор )Шравляется также управляющими сиг- :шламн от первого дешифратора 51 счетС. шка 50, представляющими собой унк- арньй М-разрядный код, В результате на каждом 1-м такте (1 i- п + Ш где i € 1, М, п е1, N) отсчет резулыto

ата С|| передается в i-й выходной анал.

На такте (М+1) с начала вывода д;анных коммутатор 29 первого блока 8 группы 7 подключает к второму входу :8 данного блока 8 второй выход 38 iToporo блока 8. Это осуществляется гоступлением на управляюшде входы 41 р 42 коммутатора-управляющих сигналов У - У2 О, сформированных к это Ny моменту дешифратором 36. При этом наборе управляющих сигналов у к у данные поступают на второй вход 42 коммутатора 29 и с его первого вьр- хода 47 на вход первой секщш узла 34. Одновременно с этим данные, с пер- врго входа 27 блока 8 (т.е.. от тое- т|ьего выхода 26 блока 2) поступают нр первьй вход коммутатора 29 перво - .гр блока 8ис его второго выхода 48 н вход второго узла 35.

: На такте (М+1) с начала вывода данных аналогичные переютючения осуществляются в 1-го блока 8, в кото-- рОм вновь третий выход 26 соответст- блока 5 подключается комму- тутором 29 к входу второго з зла 35, а вход первого узла 34 в данном бло-: К( оказывается подключенным к второ- м;|г выходу 38 следующего (1ч-1)-го бйока 8 (VI 6 2, N-1),

Таким образом, в течение следующих МЙ тактов, считая с начала вывода езультатов, осуществляется вьшод (fex сформированных результатов С i. ; йрвые узлы 34 всех блоков 8 при tOM оказываются последовательно под 11 юченными один за другим, образуя бы единую память типа FIFO емко- z, N(M-1) регистров. Одновременно

20

25

30

35

40

45

50

55

во вторых узлах 35 постепенно накап- i ливаются текущие суммы в соответствии с вьгражениями (1) и (2) для вновь по-; ступающих следук11и;их последовательностей данных X , j4 по всем входным каналам, тем самым в таком многоканаль-, ном процессоре отсутствуют паузы на ввод/вывод даннйх.

Формула изобретения

.

20

25

30

35

0

5

0

5

, Систолический процессор дискретно- го преобразования Фурье, содержащий блок управления и К-1 (где К - размер преобразования) оператдионных блоков, причем первьй и второй выходы К-го (к 1j К - 2).операционного блока - подключены соответственно к первому и второму информацнонньпч входам (К+, f-D-ro операодонного блока, тактовые входы всех операционных блоков под- ютючены к тактов выходу блока управления, тактовый вход когсрого подключен к тактовому входу-процессора, при этом операционный блок содерлсит сумматор умножитель и регистр, выход которого подключен к первому входу умножителя, выход которого подклю. чен к первом / информационному входу сумматора и является первым выходом операгщонного блока, вторым выходом, которого является выход регистраэ тактовьй вход которого соединен с так- товь&я входом умножителя1И является тактовым входом операционного блока, первым и вторым информагдионными вхо-- дами которого являются соответственно второй информационный вход умнолш- теля и информационньй вход регистра, обличающийся тем, что, с целью расширения области применения за счет многоканальной обработки данны х, 3 него введены два блока по-- стоянной памяти, два коммутатора, К-й операционньй блок из К блоков хранения, при этом первьй выход и первый информационньй вход р-го (, К-i), блока хранения подключены соответст- венно к управляющему входу и второму выходу (р+1)го блока хранения, третий выход К-го (Ifc1, К) операционного блока подключен к второму информа- ционному входу блока хранения, третий выход которого подключен к третьему информагщонному входу операционного блока, первый управля- Ю1ДИЙ .выход блока управления подключен к управляющим входам первого и

второго коммутаторов, выход первого j коммутатора подключен к первому ин формационному входу К-го операционного блока, первый выход которого под ключен к первому информационному входу первого операционного блока, второй управляющий выход блока управле- -ния подключен к управляющему входу первого блока хранения, второй выход которого подключен к информационному входу второго коммутатора, выходы группы которого являются информационными выходами группы процессора, ин5741

ход блока управления подключен к.так- товым входам всех блоков хранения и i- входам управления считыванием первого и второго блоков постоянной ,памяти, при этом блок хранения содержит два узла регистров, элемент задержки и коммутатор, первый и второй выходы которых подключены к информационным входам соответственно первого и второго узлов регистров, тактовые входы которых соединены между собой и являются тактовым входом блока хранения, первым, вторым и третьим выходами ко0

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный систолический процессор для вычисления полиномиальных функций | 2020 |

|

RU2737236C1 |

| Систолический процессор для вычисления полиномиальных функций | 1988 |

|

SU1608689A1 |

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДЛЯ ВЫЧИСЛЕНИЯ ПОЛИНОМИАЛЬНЫХ ФУНКЦИЙ | 1991 |

|

RU2015549C1 |

| СИСТОЛИЧЕСКИЙ ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1992 |

|

RU2029437C1 |

| Систолический процессор для двумерного дискретного преобразования Фурье | 1988 |

|

SU1608688A1 |

| Систолический процессор цифровой обработки сигналов | 1987 |

|

SU1471200A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах многоканальной обработки сигналов и в измерительно-вычислительных системах. Цель изобретения - расширение области применения за счет многоканальной обработки данных. Поставленная цель достигается за счет того, что в состав устройства входят коммутатор 1, операционный блок 2, блок постоянной памяти 3, группа 4 из К-1 /К- размер преобразования/ операционных блоков 5, блок постоянной памяти 6, группа 7 из К блоков хранения 8, коммутатор 10 и блок управления 11. 6 ил.

формационными входами группы которого с торого являются выходы соответствен- являются информационные входы грзшпы первого коммутатора, адресиьй выход блока управления подключен к адресным входам первого и второго блоков постоянной памяти, выходы которых подключены к вторым информационньм входам соответственно К-го и первого

20

но элемента задержки, первого и второго узлов задержки,, управляющий вход коммутатора соединен с входом элемен- та задержки и является управляюи ш входом блока хранения, первым и вторым информационными входами которого являются соответственно первьй и второй входы коммутатора.

Операционных блоков, а тактовый вы

фиг, г

торого являются выходы соответствен-

но элемента задержки, первого и второго узлов задержки,, управляющий вход коммутатора соединен с входом элемен- та задержки и является управляюи ш входом блока хранения, первым и вторым информационными входами которого являются соответственно первьй и второй входы коммутатора.

J/

ФигЛ

Фиг.З

51

0

/5

9

-

72 Фиг. 5

г/г5

Составитель А. Баранов Редактор А. Козориз Техред Л,Сердюкова Корректор- jyj Ujypojjm

Заказ 3989

Тираж 567

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

, Ц-, I - - .-.-I I

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

;j

50

52

Ж

5Z

«

5J

jd

55

±П

I

54

Подписное

| Системымпараллельной обработки М.: Мир, 1985 | |||

| Rung Н | |||

| Т | |||

| Systolic algpritms | |||

| for CMD WARP Processor | |||

| II Int, Conf | |||

| jPattern) Recogn | |||

| - Montreal, July 30- iAugust/2, 1984, p.p | |||

| Секретный замок | 1923 |

|

SU570A1 |

Авторы

Даты

1990-12-23—Публикация

1989-01-27—Подача