Предлагаемое изобретение относится к электротехнике, а именно, к способам и устройствам управления шаговыми двигателями (ШД).

Наиболее часто при работе двухобмоточного ШД используется полношаговый режим, как позволяющий развивать максимальный момент. При этом регулирование тока в обмотках обеспечивается импульсным регулятором, который на интервале отключения обмотки от источника тока обеспечивает медленный спад тока (slow decay mode) для минимизации частоты переключений и уровня пульсаций.

Известны технические решения, которые применяются для стабилизации уровня тока в обмотке двухобмоточного шагового двигателя при его работе в полношаговом режиме. Наиболее широко применяются способы стабилизации тока в обмотке ШД, включающие в себя циклическую подачу напряжения питания на обмотку, сравнение тока в питающей диагонали моста с пороговым значением на интервале времени от момента подачи напряжения до достижения величиной тока порогового значения и снятие напряжения питания с обмотки на фиксированный по длительности интервал времени. Такое решение применяется в большинстве современных драйверов ШД. Например в А4989 Allegro MicroSystems [1] или ТМС262 TRJNAMIC Motion Control GmbH & Co. KG [2]. Необходимость использования фиксированного по длительности интервала времени выключенного состояния (Fixed Off-Time) вызвано отсутствием информации о величине тока при отключении обмотки ШД от источника питания. Недостаток данного способа обусловлен тем что, несмотря на непрерывность тока в обмотке ШД, при использовании в качестве чувствительного элемента датчика тока резистора включенного между нижней точкой питающей диагонали силового моста и минусом источника питания, при выключении напряжения питания обмотки ток в нем прерывается. Из-за этого независимо от величины тока на момент окончания отрезка времени «Fixed Off-Time» приходится подавать напряжение на обмотку. Это, если ток в этот момент больше порогового значения, приводит к дополнительному приросту тока вместо его снижения и повышению частоты переключения, что, в свою очередь, повышает нагрев элементов силового моста. Описание работы ключей силового моста и характер изменения токов приведены, например, в [3].

Известно также техническое решение, описанное в [4], в котором применены два измерительных резистора в нижних плечах каждого питающего полумоста, что позволяет непрерывно контролировать ток, протекающий через обмотку ШД. Такое решение позволяет повысить точность стабилизации тока в обмотке ШД и избежать подачи напряжения на обмотку, когда ток в ней превышает заданное пороговое значение. Это позволяет снизить потребление электроэнергии и повысить надежность работы ключей. Но данное решение, принятое за прототип, не обеспечивает стабилизацию тока в обмотке ШД при отключенном источнике питания, если эдс самоиндукции, возникающая при колебаниях якоря ШД, вызывает в обмотке ток, превышающий его стабилизируемое значение.

Задачей предполагаемого изобретения является расширение функциональных возможностей, позволяющее обеспечить требуемую точность стабилизации тока в обмотке на заданном стационарном уровне при любых исследованных режимах работы ШД.

Решение этой задачи достигается за счет того, что при увеличении тока в нижнем плече того силового полумоста, в котором замкнут нижний ключ, выше заданного первого верхнего порогового значения при разомкнутых верхних ключах обоих силовых полумостов сравнивают уровень тока в нижнем плече того силового полумоста, в котором замкнут нижний ключ, с заданным вторым верхним пороговым значением, при превышении которого размыкают этот нижний ключ. После чего контроль уровня тока осуществляют в нижнем плече того силового полумоста, в котором ток течет в отрицательном направлении. И, когда уровень тока достигнет заданного второго нижнего порогового значения, замыкают нижний ключ того силового полумоста, который обеспечивает протекание тока в обмотке в прежнем направлении. При этом, заданное второе верхнее пороговое значение выбирают выше заданного первого верхнего порогового значения, а заданное второе нижнее пороговое значение выбирают выше заданного первого нижнего порогового значения. Под уровнем тока будем понимать его абсолютную величину независимо от направления его протекания в обмотке.

Для реализации предлагаемого способа стабилизации уровня тока в обмотке двухобмоточного шагового двигателя, работающего в полношаговом режиме, в его драйвер введены введены два сумматора, три программно управляемых ключа, третий компаратор, второй, третий и четвертый источники опорного напряжения и логический элемент НЕ в блок формирования сигнала стабилизации тока. При этом дополнительный выход блока формирования сигнала стабилизации тока, которым является выход логического элемента 2ИЛИ, соединен с дополнительным входом блока формирования управляющих сигналов. Выход логического элемента 2ИЛИ соединен со входом логического элемента НЕ, выход которого соединен со вторым входом логического элемента 2И. Первый вход логического элемента 2ИЛИ соединен со вторым входом блока формирования сигнала стабилизации тока, а его второй вход - с третьим входом блока формирования сигнала стабилизации тока, с которым соединен выход третьего компаратора. Инвертирующий вход первого компаратора соединен с выходом первого программно управляемого ключа. Неинвертирующий вход второго компаратора соединен с выходом второго программно управляемого ключа, а его инвертирующий вход соединен с выходом второго источника опорного напряжения. Неинвертирующий вход третьего компаратора соединен с выходом третьего источника опорного напряжения, а его инвертирующий вход соединен с выходом третьего программно управляемого ключа. Первые и вторые входы программно управляемых ключей соединены соответственно с выходами первого и второго сумматоров, первые входы которых соединены с выходом четвертого источника опорного напряжения. Причем второй вход первого сумматора соединен с верхним выводом первого измерительного резистора, а второй вход второго сумматора соединен с верхним выводом второго измерительного резистора.

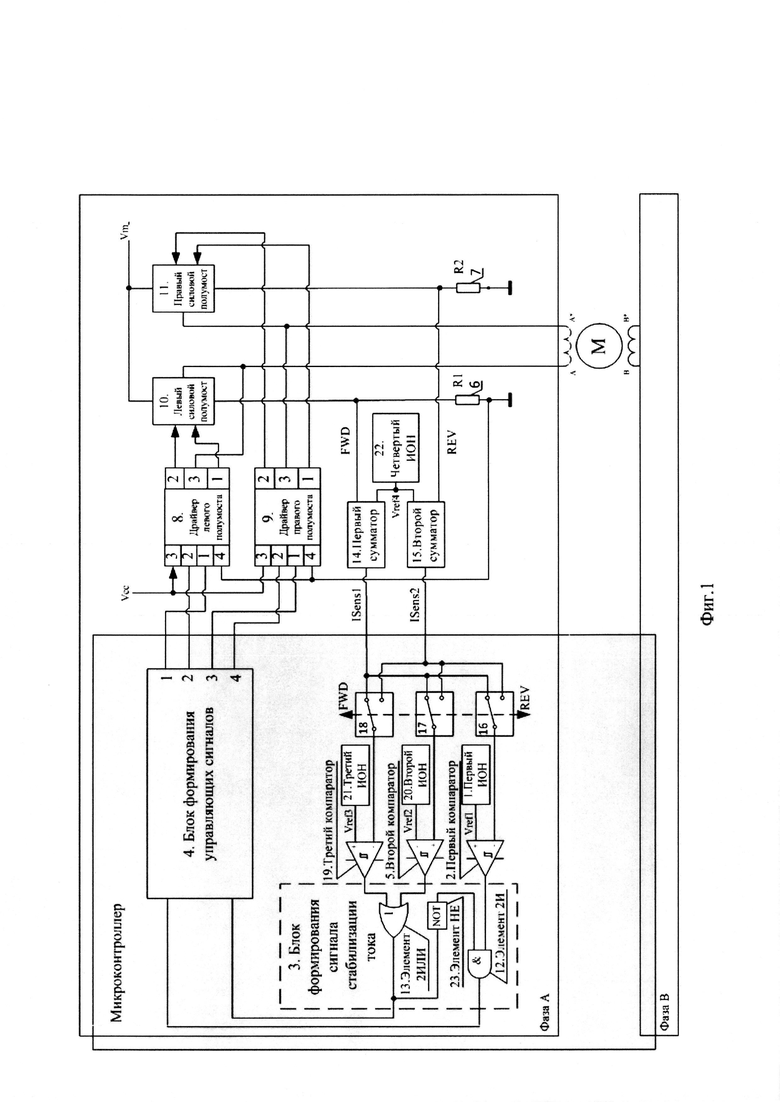

Сущность предлагаемого технического решения поясняется чертежами.

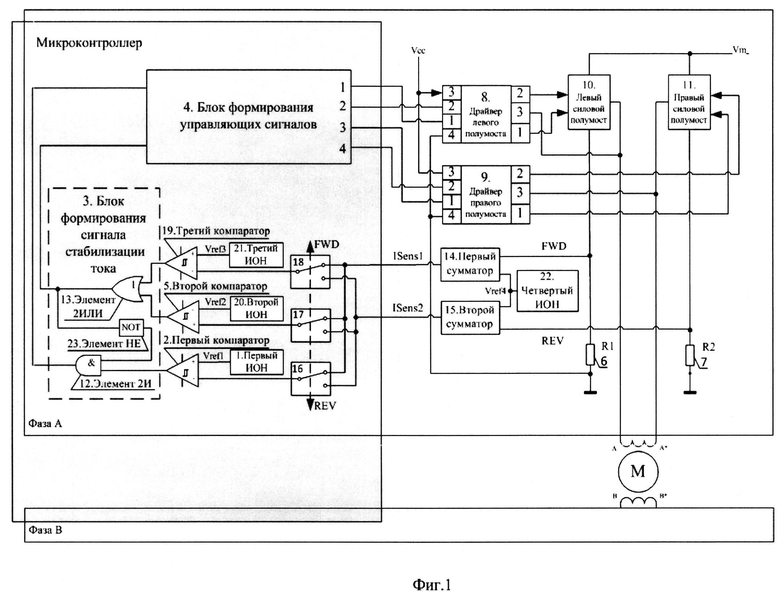

Фиг. 1. Функциональная схема драйвера двухобмоточного шагового двигателя с контуром стабилизации уровня тока в обмотке, реализующим предлагаемый способ.

Фиг. 2. Схема протекания тока в элементах силового моста и через обмотку ШД в разных режимах коммутации цепи питания.

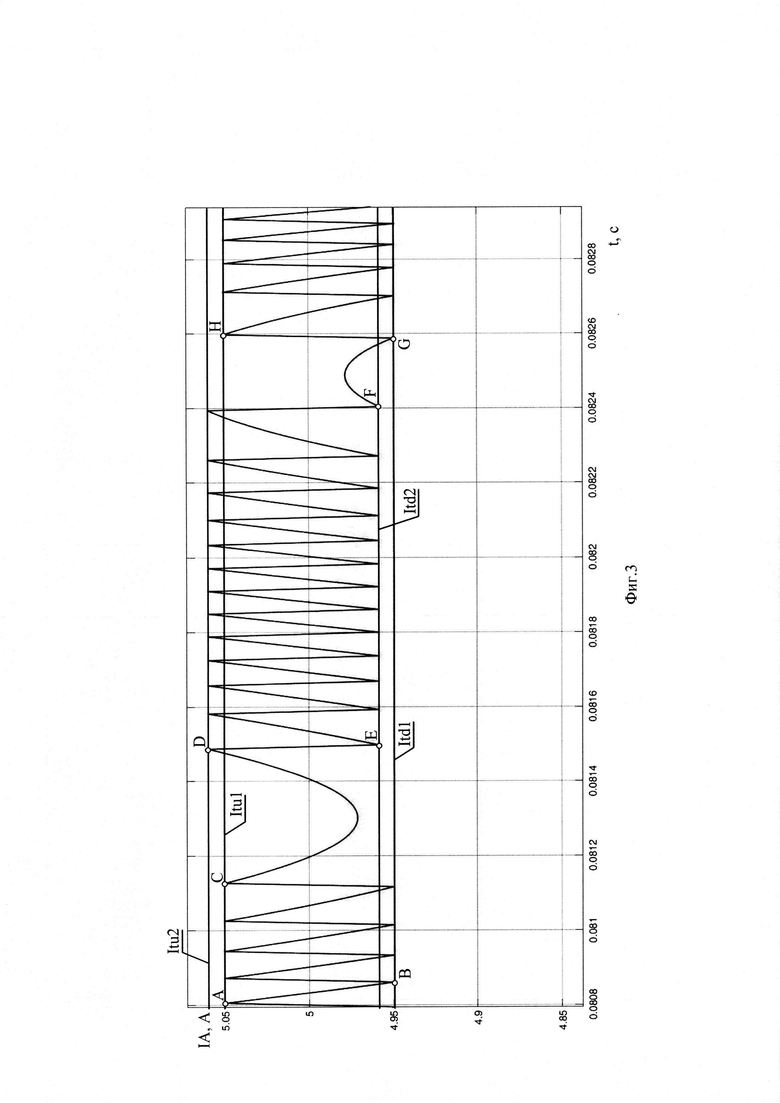

Фиг. 3. Осциллограмма процесса изменения тока в обмотке ШД при его стабилизации с использованием предлагаемого технического решения, полученная методом компьютерного моделирования.

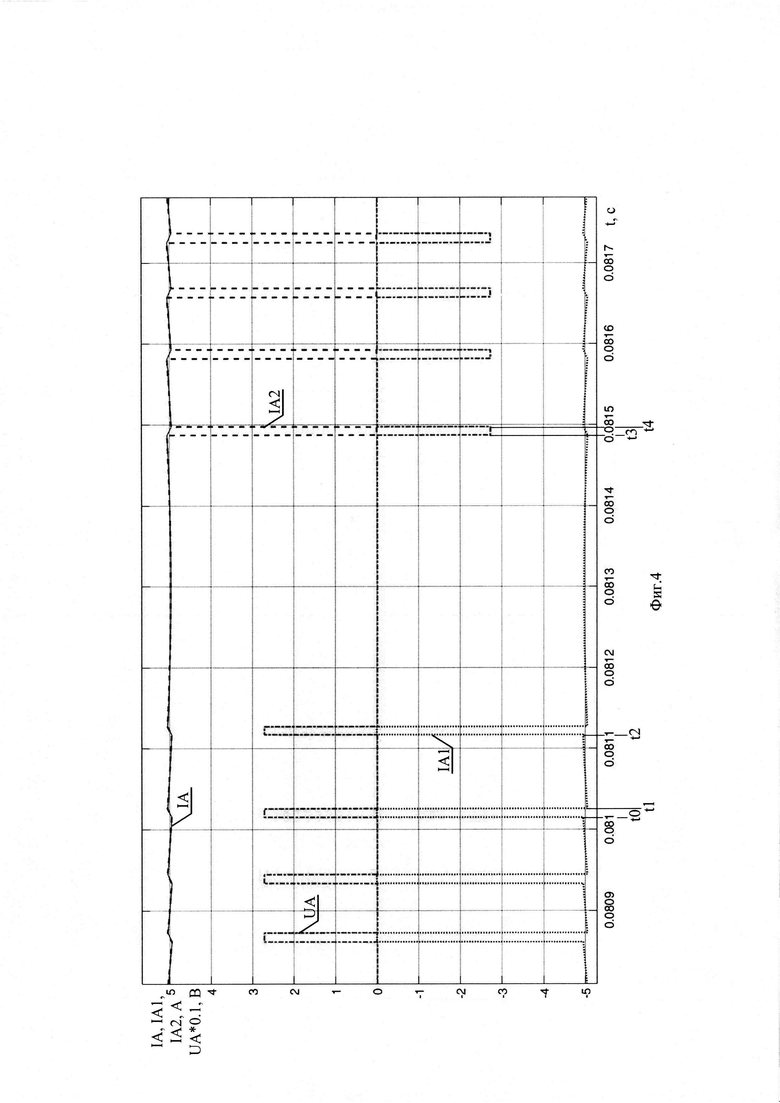

Фиг. 4. Осциллограммы полученных методом компьютерного моделирования переходных процессов изменения напряжения на обмотке и токов в обмотке ШД и нижних плечах силовых полумостов при использовании предлагаемого технического решения.

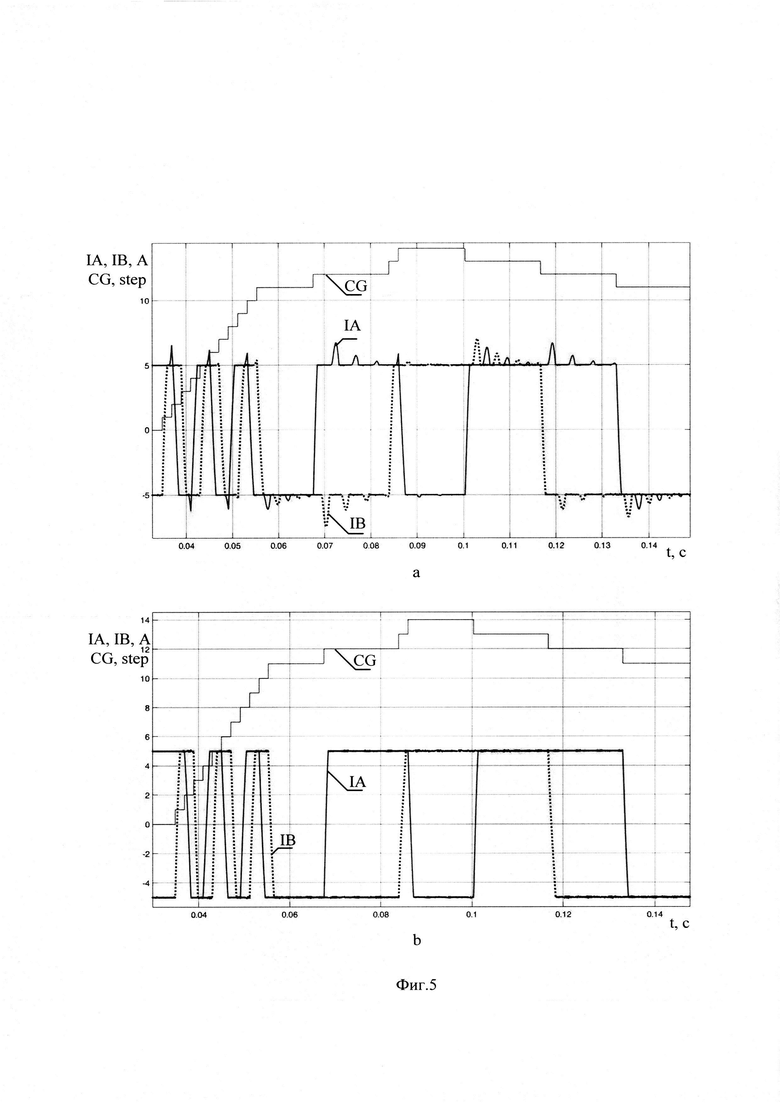

Фиг. 5. Полученные методом компьютерного моделирования осциллограммы переходных процессов изменения токов в обмотках ШД при отработке одинакового участка типовой циклограммы использовании технического решения-прототипа (фигура а) и предлагаемого технического решения (фигура b).

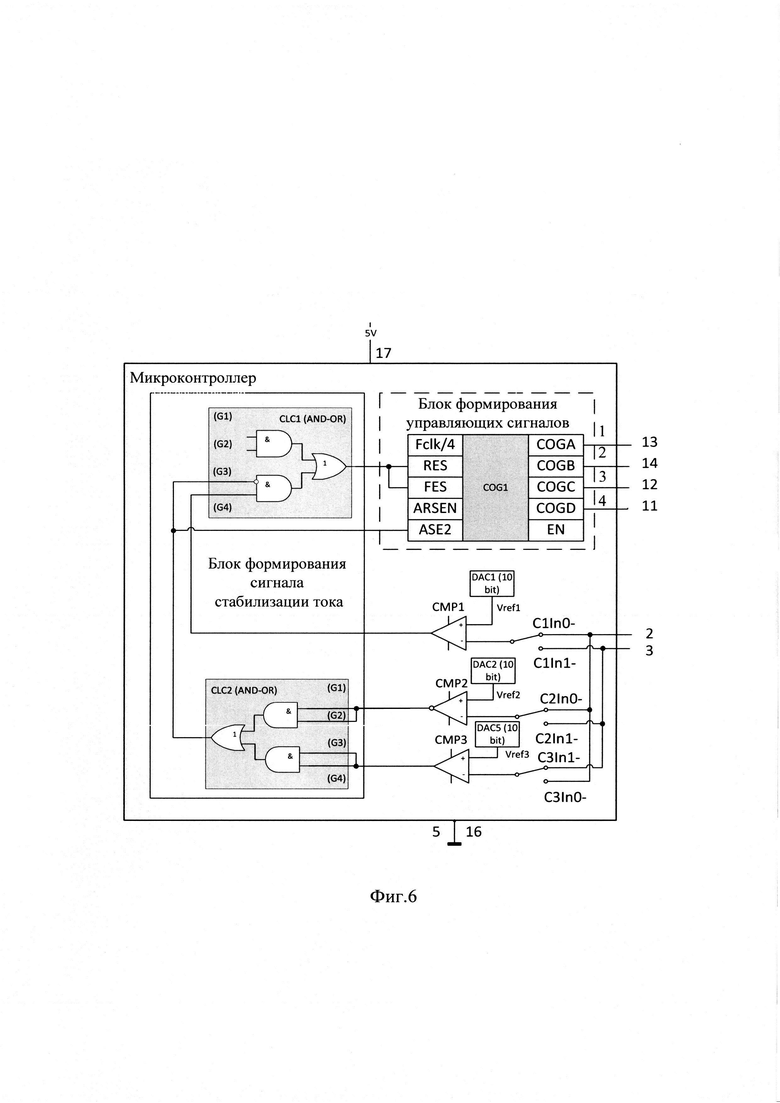

Фиг. 6. Структурная схема конфигурации внутренних модулей микроконтроллера при его использовании для реализации предлагаемого технического решения.

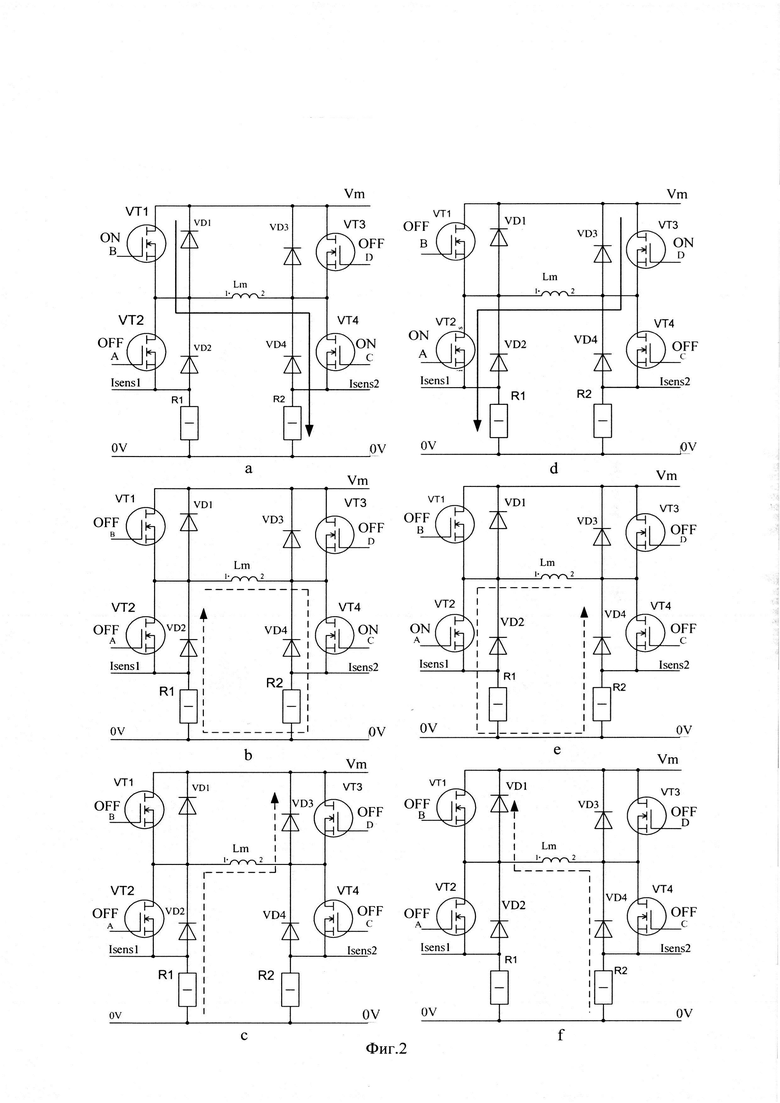

Приведенная на фиг. 2 схема позволяет пояснить, как формируется цепь протекания тока в обмотке ШД при коммутации ключей силового моста на разных участках работы контура стабилизации тока.

Примем за положительное направление тока в обмотке слева направо. Тогда при подаче напряжения питания на силовой мост и замкнутом состоянии верхнего ключа В левого силового полумоста и нижнего ключа С правого силового полумоста ток через обмотку ШД потечет в положительном направлении (см. фиг. 2, а). Путь его будет проходить от положительного вывода источника питания Vm через открытый транзистор VT1, обмотку ШД (Lm), открытый транзистор VT4 и измерительный резистор R2 к отрицательному выводу источника питания 0V.

На фиг. 3 представлена полученная методом компьютерного моделирования осциллограмма процесса изменения тока в обмотке ШД вблизи стабилизируемого уровня 5 В при его стабилизации с использованием предлагаемого технического решения. Когда ток превысит заданное первое верхнее пороговое значение Itu1 (точка А на фиг. 3), размыкают верхний ключ В левого силового полумоста, и схема протекания тока в обмотке приобретает состояние, показанное на фиг. 2, b. При этом ток в обмотке сохраняет свое направление и замыкается по цепи: обмотка ШД (Lm), открытый транзистор VT4, измерительный резистор R2, измерительный резистор R1 и диод VD2. При таком состоянии схемы и отсутствии существенных значений эдс самоиндукции, возникающей в обмотке при вращении якоря ШД, ток в обмотке начинает падать. Если его уровень, измеряемый в нижнем плече правого силового полумоста, опускается ниже заданного первого нижнего порогового значения Itd1, что соответствует точке В на осциллограмме фиг. 3, замыкают верхний ключ В левого силового полумоста, и схема протекания тока в обмотке возвращается в состояние, показанное на фиг. 2, а, и напряжение питания подается на обмотку снова.

Далее уровень тока в обмотке будет возрастать, и цикл работы алгоритма стабилизации тока будет повторяться до тех пор, пока не возникнет ситуация, показанная на участке моделирования процесса изменения тока после точки С. Здесь, после размыкания верхнего ключа В левого силового полумоста и перехода схемы питания в состояние, показанное на фиг. 2, b, уровень тока в обмотке не падает до заданного первого нижнего порогового значения Itd1, а возрастает из-за того, что при вращении якоря с достаточной скоростью возникает эдс самоиндукции существенной величины, которая вызывает в обмотке ток того же положительного направления. Тогда, при превышении уровнем тока заданного второго верхнего порогового значения Itu2 (точка D на фиг. 3), размыкают нижний ключ С правого силового полумоста, после чего схема питания переходит в состояние, показанное на фиг. 2, с. В этом случае ток в обмотке опять сохраняет свое направление и, поскольку напряжение, приложенное к обмотке ШД, оказывается больше напряжения питания, протекает по цепи: отрицательный вывод источника питания, измерительный резистор R1, диод VD2 и диод VD3 к положительному выводу источника питания. При этом часть запасенной в обмотке ШД энергии передается источнику питания, а уровень тока начинает падать. Контроль уровня тока в обмотке в этом состоянии схемы питания осуществляют в нижнем плече того силового полумоста, в котором ток течет в отрицательном направлении, т.е. в нижнем плече левого полумоста (см. фиг. 2, с).

Когда уровень тока достигнет заданного второго нижнего порогового значения Itd2 (точка Е на фиг. 3), замыкают нижний ключ того силового полумоста, который обеспечивает протекание тока в обмотке в прежнем направлении, т.е. нижний ключ С правого силового полумоста, после чего схема питания возвращается в состояние, показанное на фиг. 2, b. После этого возможны два варианта дальнейшего изменения тока. Если напряжение, приложенное к обмотке ШД, из-за действия эдс самоиндукции по-прежнему будет больше напряжения питания, то уровень тока в обмотке, измеряемый теперь снова в нижнем плече правого силового полумоста, будет возрастать. И цикл регулирования уровня тока между значениями Itd2 и Itu2 повторится снова (см. фиг. 3). Если же напряжение, приложенное к обмотке ШД, после перехода схемы питания в состояние, показанное на фиг. 2, b, станет меньше напряжения питания, то уровень тока в обмотке будет уменьшаться. Такое состояние возникло при компьютерном моделировании после достижения током значения Itd2 в точке F (см. осциллограмму изменения тока на фиг. 3). Тогда уровень тока в обмотке начинает снижаться и достигает заданного первого нижнего порогового значения Itd1 (точка G на графике фиг. 3). После этого замыкают верхний ключ В левого силового полумоста, схема питания переходит в состояние, показанное на фиг. 2, а, и процесс стабилизации уровня тока в обмотке ШД возобновляется предлагаемым способом.

Когда ток в обмотке ШД течет в противоположном направлении, процесс его стабилизации осуществляется аналогично. Как будет осуществляться коммутация в схеме питания обмотки ШД в этом случае, показано на фиг. 2 d,e,f.

Процессы изменения напряжения на обмотке ШД и токов в обмотке и нижних плечах силовых полумостов при использовании предлагаемого технического решения, полученные при компьютерном моделировании, показаны на фиг. 4 для обмотки А ШД на небольшом отрезке времени. На этих осциллограммах ток в обмотке (IA) показан тонкой сплошной линией, напряжение на обмотке (UA) показано штрихпунктирной линией, ток в нижнем плече левого силового полумоста (IA1) показан пунктирной линией, а ток в нижнем плече правого силового полумоста (IA2) - штриховой линией.

Отрезок времени, обозначенный на фиг. 4 [t0,t1], соответствует состоянию схемы питания, показанному на фиг. 2, а. На этом отрезке времени ток в обмотке IA течет в положительном направлении, напряжение UA, приложенное к обмотке, имеет положительное значение. Ток в нижнем плече левого силового полумоста IA1 равен нулю, а ток в нижнем плече правого силового полумоста IA2 положителен и равен току в обмотке IA. Отрезок времени, обозначенный на фиг. 4 [t1,t2], соответствует состоянию схемы питания, показанному на фиг. 2, b. На этом отрезке времени ток в обмотке IA течет в положительном направлении, напряжение UA, приложенное к обмотке, равно нулю. Ток в нижнем плече левого силового полумоста IA1 имеет отрицательное значение, а его уровень равен уровню тока в обмотке IA. Ток в нижнем плече правого силового полумоста IA2 положителен и равен току в обмотке IA. Отрезок времени, обозначенный на фиг. 4 [t3,t4], соответствует состоянию схемы питания, показанному на фиг. 2, с. На этом отрезке времени ток в обмотке IA, по-прежнему, течет в положительном направлении, а напряжение UA, приложенное к обмотке, имеет отрицательное значение. Ток в нижнем плече левого силового полумоста IA1 имеет отрицательное значение, а его уровень равен уровню тока в обмотке IA. Ток в нижнем плече правого силового полумоста IA2 равен нулю. Осциллограммы, приведенные на фиг. 4, позволяют понять, как операции замыкания и размыкания соответствующих ключей, выполняемые при изменении тока в обмотке ШД, позволяют обеспечить его стабилизацию при разных условиях работы ШД.

На фиг. 5 показаны полученные методом компьютерного моделирования процессы изменения тока в обмотках ШД при отработке им участка типовой циклограммы изменения положения вала ШД. На фиг. 5, а показаны процессы, полученные при использовании технического решения-прототипа, а на фиг. 5, b - предлагаемого технического решения. На этих графиках процесс изменения тока IA в обмотке А показан толстой сплошной линией, процесс изменения тока IB в обмотке В - пунктирной линией, а процесс CG изменения заданного значения положения вала ШД (циклограмма) показан тонкой сплошной линией. Сравнение графиков, приведенных на фиг. 5 а и b, позволяет сделать вывод, что предлагаемое техническое решение обеспечивает стабилизацию тока в обмотках ШД с заданной точностью во всех рассмотренных режимах работы ШД. Тогда как использование технического решения-прототипа не обеспечивает стабилизацию тока на участках работы, где действие эдс самоиндукции при отключенном напряжении питания увеличивает уровень тока в обмотке до величины, превосходящей заданное первое верхнее пороговое значение.

Заданное второе верхнее пороговое значение выбирают выше заданного первого верхнего порогового значения, и заданное второе нижнее пороговое значение выбирают выше заданного первого нижнего порогового значения, чтобы обеспечить последовательный переход при изменении схемы протекания тока из состояния, показанного на фиг. 2, а, в состояние, показанное на фиг. 2, b, и, далее, в состояние, показанное на фиг. 2, с, и обратно. Это обеспечит отсутствие противоречий при замыкании и размыкании ключей и необходимую последовательность этих операций.

Функциональная схема драйвера ШД, реализующего предлагаемый способ стабилизации уровня тока в обмотке ШД, работающего в полношаговом режиме, приведена на фиг. 1. Контур стабилизации уровня тока в обмотке ШД, реализованный в драйвере, содержит последовательно соединенные первый источник опорного напряжения (ИОН) 1, первый компаратор 2, блок формирования сигнала стабилизации тока 3 и блок формирования управляющих сигналов 4. А также второй компаратор 5 первый и второй измерительные резисторы 6 и 7, драйверы левого и правого полумостов 8 и 9 и два силовых полумоста 10 и 11. Причем первый и второй выходы блока формирования управляющих сигналов соединены с соответствующими входами драйвера левого полумоста. Третий и четвертый выходы блока формирования управляющих сигналов соединены с соответствующими входами драйвера правого полумоста. Одновременно первый и второй выходы каждого драйвера соединены с управляющими входами соответствующих силовых полумостов, верхние точки которых соединены с положительным выводом источника питания шагового двигателя, а средние точки - с обмоткой шагового двигателя. При этом нижняя точка левого силового полумоста через первый измерительный резистор и нижняя точка правого силового полумоста через второй измерительный резистор соединены с отрицательным выводом источника питания шагового двигателя. Третьи и четвертые входы обоих драйверов соединены соответственно с положительным и отрицательным выводами источника питания драйверов, а их третьи выходы - соответственно со средними точками левого и правого силовых полумостов. Блок формирования сигнала стабилизации тока содержит логический элемент 2И 12 и логический элемент 2ИЛИ 13, чей выход является выходом блока формирования сигнала стабилизации тока. Первый вход логического элемента 2И является первым входом блока формирования сигнала стабилизации тока и соединен с выходом первого компаратора. Второй вход блока формирования сигнала стабилизации тока соединен с выходом второго компаратора и отрицательные выводы всех источников питания соединены между собой. Контур стабилизации уровня тока также содержит два сумматора 14 и 15, три программно управляемых ключа 16, 17 и 18, третий компаратор 19, второй, третий и четвертый источники опорного напряжения 20, 21 и 22. В блок формирования сигнала стабилизации тока 3 введен логический элемент НЕ 23. Дополнительный выход блока формирования сигнала стабилизации тока, которым является выход логического элемента 2ИЛИ 13, соединен с дополнительным входом блока формирования управляющих сигналов 4. Выход логического элемента 2ИЛИ 13 соединен со входом логического элемента НЕ 22, выход которого соединен со вторым входом логического элемента 2И 12. Первый вход логического элемента 2ИЛИ 13 соединен со вторым входом блока формирования сигнала стабилизации тока 3, а его второй вход - с третьим входом блока формирования сигнала стабилизации тока 3, с которым соединен выход третьего компаратора 19. Инвертирующий вход первого компаратора 2 соединен с выходом первого программно управляемого ключа 16. Неинвертирующий вход второго компаратора 5 соединен с выходом второго программно управляемого ключа 17, а его инвертирующий вход соединен с выходом второго ИОН 20. Неинвертирующий вход третьего компаратора 19 соединен с выходом третьего ИОН 21, а его инвертирующий вход соединен с выходом третьего программно управляемого ключа 18. Первые и вторые входы программно управляемых ключей 16, 17 и 18 соединены соответственно с выходами первого и второго сумматоров 14 и 15, первые входы которых соединены с выходом четвертого ИОН 22. Причем второй вход первого сумматора 14 соединен с верхним выводом первого измерительного резистора 6, а второй вход второго сумматора 15 соединен с верхним выводом второго измерительного резистора 7.

Так как драйвер двухобмоточного ШД содержит два идентичных контура стабилизации уровня тока в обмотках фаз А и В ШД, то его работа будет рассмотрена на примере одной фазы А.

Управление направлением тока в обмотке, как уже отмечалось, осуществляется выбором одной из двух пар диагонально расположенных ключей VT1, VT4 или VT2, VT3 (см. фиг. 2, а и d). Причем для обеспечения непрерывности тока в измерительных резисторах R1 и R2 стабилизация тока осуществляется модуляцией открытого состояния одного из верхних ключей VT1 или VT3. Путь протекания тока в схеме в этом случае показан на фиг. 2, а и b или на фиг. 2, d и е.

Для исключения роста тока в обмотке ШД при замкнутом только одном нижнем ключе используется переход к возврату энергии в источник питания, что достигается размыканием всех ключей. При этом контроль уровня тока необходимо выполнять не в измерительном резисторе R2 (см. фиг. 2, с), в котором при замкнутом нижнем ключе ток течет в положительном направлении, а в резисторе R1, в котором ток течет в отрицательном направлении. Для решения этой задачи сигналы с измерительных резисторов R1 и R2 складываются с постоянным опорным напряжением Vref4 в сумматорах 14 и 15 (см. функциональную схему на фиг. 5). В качестве источника опорного напряжения может быть использован резистивный делитель напряжения. Параметры сумматоров и делителя напряжения выбираются так, чтобы обеспечить выходное напряжение равное половине напряжения питания схемы при нулевом токе в контролируемом измерительном резисторе и необходимый для работы регулятора размах напряжения при максимальном токе через него.

Возможная схема сумматора (14 или 15) и расчет его параметров описаны в книге [5] на с. 77 и в статье [6]. Подобный сумматор можно построить с использованием операционного усилителя MCP6V02-E/SN/ [7]. Остальные функциональные узлы регулятора, показанные в левой части фиг. 6, могут быть выполнены на модулях периферии независимой от ядра (Core Independent Peripheral, CIP) микроконтроллера PIC16F1778-I/SO [8]. Функционирование такой периферии почти не зависит от тактовой частоты микроконтроллера и его состояния (RUN, IDLE, SLEEP), и конфигурируется программой микроконтроллера, после чего функционирует независимо.

Драйверы левого и правого полумостов и сами силовые полумосты могут быть выполнены, например, в соответствии с их схемами и описанием, приведенным в описании патента [4].

С выходов сумматоров 14 и 15 сигналы поступают на блок программно управляемых ключей 16, 17 и 18 (см. фиг. 5), которые переключаются одновременно при изменении направления тока в контролируемой обмотке ШД. На функциональной схеме они показаны в положении FWD, соответствующем протеканию тока в прямом направлении через R1 (первый измерительный резистор 6). Ключи могут быть выполнены на мультиплексорах, входящих в состав компараторов СМР1-СМР3 (см. фиг. 6), и управляются установкой соответствующих значений в их управляющие регистры. Кроме того, посредством этих регистров в компараторах включается гистерезис, обеспечивающий наличие зоны нечувствительности между верхним и нижним пороговыми значениями каждого компаратора. Таким образом, значение верхнего порогового значения компаратора составит Vref+Vhys, а нижнего - Vref -Vhys, где Vref -значение опорного напряжения, a Vhys - размер зоны нечувствительности данного компаратора. Так на компараторе СМР1 формируются первое верхнее и первое нижнее пороговые значения. На компараторах СМР2 и СМР3 таким же образом формируются второе верхнее и второе нижнее пороговые значения, но только на одном (СМР2) - для стабилизации уровня тока, имеющего отрицательное направление, а на другом (СМР3) -для стабилизации уровня тока, имеющего положительное направление.

Контур, реализующий стабилизацию уровня тока за счет модуляции открытого состояния верхнего ключа при замкнутом нижнем ключе и описанный в прототипе [4], реализован с использованием первого компаратора 2 (см. фиг. 1). В зависимости от направления тока в обмотке инвертирующий вход указанного компаратора будет подключен к выходу соответствующего сумматора первого 14 или второго 15. Пороговое напряжение Vref1 формируется первым ИОН 1. Выходной сигнал второго компаратора 5, через логический элемент 2И 12 блока формирования сигнала стабилизации тока 3, управляет работой блока формирования управляющих сигналов 4. Указанный выше логический элемент 2И 12 блокирует прохождение сигнала первого компаратора 2 при срабатывании любого из компараторов - второго компаратора 5 или третьего компаратора 19, контролирующих превышение током обмотки ШД заданного второго верхнего порогового значения Itu2. Сигналы с выходов этих компараторов (5 и 19) объединяются логическим элементом 2ИЛИ 13, в результате чего формируется выходной сигнал блока формирования сигнала стабилизации тока 3, с дополнительного выхода которого он поступает на дополнительный вход блока формирования управляющих сигналов 4. В результате по этому сигналу обеспечивается отключение всех ключей силовых полумостов, управляющих данной обмоткой ШД.

Пример реализации описанных выше функций с использованием ресурсов микроконтроллера PIC16F1778 [8] приведен на фиг. 6. Номера выводов микроконтроллера, показанные на фиг. 6, соответствуют корпусу SOIC 28 [8]. Соответственно, выводы 13, 14, 12 и 11 являются первым, вторым, третьим и четвертым выходами блока формирования управляющих сигналов (см. фиг. 6). Выводы 2 и 3 соединены соответственно с первым и вторым входами каждого из программно управляемых ключей 16, 17 и 18. Вывод 17 соединен с положительным выводом 5-вольтового источника питания. И, наконец, выводы 5 и 16 соединены с отрицательным выводом 5-вольтового источника питания.

Сигналы с выходов первого и второго сумматоров 14 и 15 (см. фиг. 1) поступают на выводы 2 и 3 микроконтроллера (см. фиг. 6), к которым подключены входы компараторов СМР1-СМР3. Состояние ключей мультиплексоров указанных компараторов, изображенное на схеме фиг. 6, соответствует протеканию тока через измерительный резистор R1 при замкнутом состоянии нижнего ключа в левом силовом полумосте и верхнего - в правом. Сигнал с выхода компаратора СМР1 (см. фиг. 6) поступает на вход логического элемента 2И, выполненного на конфигурируемой логической ячейке CLC1 (CONFIGURABLE LOGIC CELL) микроконтроллера, настроенной на выполнение функции AND-OR. Сигнал с выхода CLC1 подается на соответствующие входы блока формирования управляющих сигналов только при отсутствии сигнала высокого логического уровня с выхода логического элемента 2ИЛИ, выполненного на ячейке CLC2, настроенной на выполнение функции AND-OR.

Блок формирования управляющих сигналов может быть построен в микропроцессоре (см. фиг. 6) на модуле генератора комплиментарного выхода COG1 (COMPLEMENTARY OUTPUT GENERATOR MODULES). Выходные сигналы блока формирования управляющих сигналов, имеющие логические уровни 5 вольт преобразуются драйверами левого и правого полумостов в сигналы, имеющие уровни, необходимые для работы полевых транзисторов соответствующего силового полумоста. Модуль COG1 настроен на работу в режимах Forward and Reverse FULL-BRIDGE MODES, в которых всегда два выхода из четырех активны, а два других пассивны. При этом один из активных выходов, управляющий верхним ключом соответствующего силового полумоста, модулируется импульсным сигналом по сигналу с выхода компаратора СМР1, поступающим на входы, являющиеся источниками нарастающего и падающего фронтов - Rising event source (RES) и Falling event sources (FES) соответственно. Для отключения всех ключей используется вход ASE2 (Auto-Shutdown Even), соединенный с выходом логической ячейки CLC2.

Особо отметим, что выбор числовых параметров верхних и нижних пороговых значений тока при осуществлении его стабилизации, во-первых, определяется требуемой точностью стабилизации тока, а, во-вторых, достигаемая точность стабилизации ограничивается допустимым быстродействием ключей и других используемых при реализации устройства элементов электронных схем. На приведенных на фиг. 3-5 результатах компьютерного моделирования предлагаемого технического решения обеспечена точность стабилизации тока в пределах 1,5%, частота коммутации ключей при этом не превышает 25 кГц, что вполне допустимо для используемых при реализации предлагаемого драйвера элементов электронных схем.

Представленные результаты компьютерного моделирования подтверждают работоспособность и эффективность предлагаемого технического решения, а также доказывают, что поставленная задача изобретения решена.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. A4989-Datasheet.pdf, Inc. www.allegromicro.com.

2. ТМС262 DATASHEET (Rev. 2.14 / 2016-JUL-14). www.trinamic.com.

3. Борисевич А.В., Глебко Д.В. Подход к оптимальной стратегии переключений для регулятора тока в обмотках шагового двигателя // Современная техника и технологии. 2015. №3 [Электронный ресурс]. URL: http://technology.snauka.ru/2015/03/5935.

4. Патент RU 2708073, 04.12.2019, бюл. №34. Способ стабилизации уровня тока в обмотке двухфазного биполярного шагового двигателя в полношаговом режиме и драйвер для его осуществления.

5. Алексенко А.Г., Коломбет Е.А., Стародуб Г.И. Применение прецизионных аналоговых ИС. - М.: Радио и связь, 1981. - 224 с.

6. Averager and summer circuits, http://www.allaboutcircuits.com/vol_3/chpt_8/8.html.

7. 22058c.pdf www.microchip.com/product/en/MCP6V02.

8. DS40001819B.pdf www.microchip.com/product/en/PIC16F1778.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СТАБИЛИЗАЦИИ УРОВНЯ ТОКА В ОБМОТКЕ ДВУХФАЗНОГО БИПОЛЯРНОГО ШАГОВОГО ДВИГАТЕЛЯ В ПОЛНОШАГОВОМ РЕЖИМЕ И ДРАЙВЕР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2019 |

|

RU2708073C1 |

| СПОСОБ КОНТРОЛЯ РАБОТЫ ЭЛЕКТРОПРИВОДА НА ОСНОВЕ ДВУХОБМОТОЧНОГО ШАГОВОГО ДВИГАТЕЛЯ, РАБОТАЮЩЕГО В ПОЛНОШАГОВОМ РЕЖИМЕ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2020 |

|

RU2738348C1 |

| СПОСОБ КОНТРОЛЯ РАБОТЫ ЭЛЕКТРОПРИВОДА НА ОСНОВЕ ДВУХОБМОТОЧНОГО ШАГОВОГО ДВИГАТЕЛЯ, РАБОТАЮЩЕГО В ПОЛНОШАГОВОМ РЕЖИМЕ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2021 |

|

RU2774923C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МОМЕНТА ДОСТИЖЕНИЯ МЕХАНИЧЕСКОГО УПОРА ЭЛЕКТРОПРИВОДОМ С ДВУХОБМОТОЧНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2019 |

|

RU2719604C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МОМЕНТА ДОСТИЖЕНИЯ МЕХАНИЧЕСКОГО УПОРА ЭЛЕКТРОПРИВОДОМ С ДВУХОБМОТОЧНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2019 |

|

RU2725619C1 |

| Трехфазный выпрямитель напряжения с корректором коэффициента мощности | 2023 |

|

RU2813799C1 |

| ИСТОЧНИК ПИТАНИЯ ТОКОМ ОБМОТОК РАЗМАГНИЧИВАНИЯ | 2023 |

|

RU2808773C1 |

| Устройство для дифференциально-фазной защиты | 1982 |

|

SU1113866A1 |

| ПОЛУМОСТОВОЙ АВТОГЕНЕРАТОРНЫЙ ИНВЕРТОР | 2014 |

|

RU2573647C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МОМЕНТА ДОСТИЖЕНИЯ МЕХАНИЧЕСКОГО УПОРА ЭЛЕКТРОПРИВОДОМ С БИПОЛЯРНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2019 |

|

RU2713224C1 |

Изобретение относится к электротехнике. Технический результат заключается в повышении точности стабилизации уровня тока в любой момент его протекания в обмотке шагового двигателя (ШД) при любом возможном случае коммутации ключей силовых мостов. Способ стабилизации уровня тока в обмотке двухобмоточного ШД, работающего в полношаговом режиме, при котором питание обмотки осуществляется с помощью двух силовых полумостов. При увеличении тока в нижнем плече того силового полумоста, в котором замкнут нижний ключ, выше заданного первого верхнего порогового значения при разомкнутых верхних ключах обоих силовых полумостов сравнивают уровень тока в нижнем плече того силового полумоста, в котором замкнут нижний ключ, с заданным вторым верхним пороговым значением, при превышении которого размыкают этот нижний ключ. После чего контроль уровня тока осуществляют в нижнем плече того силового полумоста, в котором ток течет в отрицательном направлении. И, когда уровень тока достигнет заданного второго нижнего порогового значения, замыкают нижний ключ того силового полумоста, который обеспечивает протекание тока в обмотке в прежнем направлении. При этом, заданное второе верхнее пороговое значение выбирают выше заданного первого верхнего порогового значения. А заданное второе нижнее пороговое значение выбирают выше заданного первого нижнего порогового значения. Для реализации способа стабилизации уровня тока в обмотке двухобмоточного ШГ, в его драйвер введены два сумматора, три программно управляемых ключа, третий компаратор, второй, третий и четвертый источники опорного напряжения и логический элемент НЕ в блок формирования сигнала стабилизации тока. 2 н.п ф-лы, 6 ил.

1. Способ стабилизации уровня тока в обмотке двухобмоточного шагового двигателя, работающего в полношаговом режиме, при котором питание обмотки осуществляется с помощью двух силовых полумостов, причем нужное направление тока в обмотке достигается одновременным замыканием верхнего ключа одного полумоста и нижнего ключа другого, а для стабилизации уровня тока в обмотке при превышении током в нижнем плече того силового полумоста, в котором замкнут нижний ключ, некоторого заданного первого верхнего порогового значения размыкают верхний ключ другого силового полумоста, отключая напряжение питания на промежуток времени, пока уровень тока не опустится до заданного первого нижнего порогового значения, после чего производят очередное включение напряжения питания, вновь замыкая верхний ключ другого силового полумоста, отличающийся тем, что при увеличении тока в нижнем плече того силового полумоста, в котором замкнут нижний ключ, выше заданного первого верхнего порогового значения при разомкнутых верхних ключах обоих силовых полумостов сравнивают уровень тока в нижнем плече того силового полумоста, в котором замкнут нижний ключ, с заданным вторым верхним пороговым значением, при превышении которого размыкают этот нижний ключ, после чего контроль уровня тока осуществляют в нижнем плече того силового полумоста, в котором ток течет в отрицательном направлении, и, когда уровень тока достигнет заданного второго нижнего порогового значения, замыкают нижний ключ того силового полумоста, который обеспечивает протекание тока в обмотке в прежнем направлении, при этом заданное второе верхнее пороговое значение выбирают выше заданного первого верхнего порогового значения, а заданное второе нижнее пороговое значение выбирают выше заданного первого нижнего порогового значения.

2. Драйвер двухобмоточного шагового двигателя, контур стабилизации уровня тока в обмотке которого содержит последовательно соединенные первый источник опорного напряжения, первый компаратор, блок формирования сигнала стабилизации тока и блок формирования управляющих сигналов, а также второй компаратор, первый и второй измерительные резисторы, драйверы левого и правого полумостов и два силовых полумоста, причем первый и второй выходы блока формирования управляющих сигналов соединены с соответствующими входами драйвера левого полумоста, третий и четвертый выходы блока формирования управляющих сигналов соединены с соответствующими входами драйвера правого полумоста, одновременно первый и второй выходы каждого драйвера соединены с управляющими входами соответствующих силовых полумостов, верхние точки которых соединены с положительным выводом источника питания шагового двигателя, а средние точки - с обмоткой шагового двигателя, при этом нижняя точка левого силового полумоста через первый измерительный резистор и нижняя точка правого силового полумоста через второй измерительный резистор соединены с отрицательным выводом источника питания шагового двигателя, третьи и четвертые входы обоих драйверов соединены соответственно с положительным и отрицательным выводами источника питания драйверов, а их третьи выходы - соответственно со средними точками левого и правого силовых полумостов, а блок формирования сигнала стабилизации тока содержит логический элемент 2И и логический элемент 2ИЛИ, чей выход является выходом блока формирования сигнала стабилизации тока, а первый вход логического элемента 2И является первым входом блока формирования сигнала стабилизации тока и соединен с выходом первого компаратора, второй вход блока формирования сигнала стабилизации тока соединен с выходом второго компаратора и отрицательные выводы всех источников питания соединены между собой, отличающийся тем, что в него введены два сумматора, три программно управляемых ключа, третий компаратор, второй, третий и четвертый источники опорного напряжения и логический элемент НЕ в блок формирования сигнала стабилизации тока, при этом дополнительный выход блока формирования сигнала стабилизации тока, которым является выход логического элемента 2ИЛИ, соединен с дополнительным входом блока формирования управляющих сигналов, выход логического элемента 2ИЛИ соединен со входом логического элемента НЕ, выход которого соединен со вторым входом логического элемента 2И, первый вход логического элемента 2ИЛИ соединен со вторым входом блока формирования сигнала стабилизации тока, а его второй вход - с третьим входом блока формирования сигнала стабилизации тока, с которым соединен выход третьего компаратора, инвертирующий вход первого компаратора соединен с выходом первого программно управляемого ключа, неинвертирующий вход второго компаратора соединен с выходом второго программно управляемого ключа, а его инвертирующий вход соединен с выходом второго источника опорного напряжения, неинвертирующий вход третьего компаратора соединен с выходом третьего источника опорного напряжения, а его инвертирующий вход соединен с выходом третьего программно управляемого ключа, первые и вторые входы программно управляемых ключей соединены соответственно с выходами первого и второго сумматоров, первые входы которых соединены с выходом четвертого источника опорного напряжения, причем второй вход первого сумматора соединен с верхним выводом первого измерительного резистора, а второй вход второго сумматора соединен с верхним выводом второго измерительного резистора.

| СПОСОБ СТАБИЛИЗАЦИИ УРОВНЯ ТОКА В ОБМОТКЕ ДВУХФАЗНОГО БИПОЛЯРНОГО ШАГОВОГО ДВИГАТЕЛЯ В ПОЛНОШАГОВОМ РЕЖИМЕ И ДРАЙВЕР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2019 |

|

RU2708073C1 |

| ШАГОВЫЙ ЭЛЕКТРОПРИВОД | 2015 |

|

RU2610713C1 |

| Устройство для управления шаговым электродвигателем | 1986 |

|

SU1410266A1 |

| ВЗРЫВОЗАЩИТНАЯ РАЗРУШАЮЩАЯСЯ КОНСТРУКЦИЯ ОГРАЖДЕНИЯ ЗДАНИЙ | 2014 |

|

RU2572868C1 |

| JP 2000184789 A, 30.06.2000 | |||

| CN 102025308 A, 20.04.2011. | |||

Авторы

Даты

2020-12-02—Публикация

2020-06-15—Подача