ОБЛАСТЬ ТЕХНИКИ

[0001] Варианты осуществления настоящего изобретения относятся к области связи и, в частности, к способу и устройству обработки информации и устройству связи.

ПРЕДШЕСТВУЩИЙ УРОВЕНЬ ТЕХНИКИ

[0002] Код проверки четности низкой плотности (low density parity check, LDPC) является типом линейного компактного кодирования с разреженной проверочной матрицей и характеризуется гибкой структурой и низкой сложностью декодирования. Поскольку для LDPC кода используется алгоритм частично параллельного итерационного декодирования, LDPC код имеет более высокую пропускную способность, чем обычный турбо код. LDPC код может быть использован в коде с исправлением ошибок в системе связи, чтобы улучшить надежность передачи канала и использование мощности. LDPC код может также широко использоваться в космической связи, волоконно-оптической связи, системе персональной связи, ADSL, устройстве магнитной записи и т.п. В настоящее время, в мобильной связи пятого поколения, использование LDPC кода рассматривается в качестве одной из схем канального кодирования.

[0003] В процессе действительного использования, может быть использована LDPC матрица со специальным структурным признаком. LDPC матрица H со специальным структурным признаком может быть получена путем расширения LDPC базовой матрицы квазициклической (quasi cycle, QC) структуры.

[0004] Обычно, длина подлежащей кодированию информационной битовой последовательности варьируется от десятков до сотен битов, и система связи требует гибких и изменяемых кодовых скоростей. То, каким образом поддерживать кодирование информационных битовых последовательностей множества длин и удовлетворять требование кодовой скорости системы, становится проблемой, требующей решения.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] Варианты осуществления настоящего изобретения обеспечивают способ и устройство обработки информации, устройство связи и систему связи, чтобы поддерживать кодирование и декодирование информационных битовых последовательностей множества длин и удовлетворять системному требованию для гибкой длины кода и кодовой скорости.

[0006] В соответствии с первым аспектом, обеспечен способ кодирования, включающий в себя:

кодирование информационной битовой последовательности с использованием матрицы проверки четности низкой плотности, LDPC.

[0007] В соответствии с вторым аспектом, обеспечен способ декодирования, включающий в себя:

декодирование принятого сигнала с использованием матрицы проверки четности низкой плотности, LDPC.

[0008] В первой реализации первого аспекта или второго аспекта,

базовый граф LDPC матрицы представлен как матрица с m строками и n столбцами, m является целым числом, большим или равным 5, и n является целым числом, большим или равным 16; и

базовый граф включает в себя подматрицу A и подматрицу B, причем

подматрица A является матрицей A0, или подматрица A включает в себя первые 16 столбцов матрицы A0, где матрица A0 является матрицей с пятью строками и 22 столбцами; и

подматрица B является матрицей с пятью строками и пятью столбцами, и подматрица B включает в себя один столбец, вес которого равен 3, и подматрицу Bʹ бидиагональной структуры.

[0009] В матрице A0, имеется одна строка, вес которой больше, чем 0, и меньше, чем 5, две строки, веса которых больше, чем 9, и меньше, чем 15, и две строки, веса которых больше, чем 19, и меньше, чем 22.

[0010] В одной реализации, в матрице A0, имеется одна строка, вес которой равен 2, две строки, веса которых равны 12, и две строки, веса которых равны 21.

[0011] В этой реализации, матрица A0 может включать в себя пять строк от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец в базовом графе 30a, строки могут быть взаимозаменяемыми, и столбцы могут также быть взаимозаменяемыми.

[0012] На основе вышеописанной реализации, базовая матрица LDPC матрицы включает в себя матрицу сдвига подматрицы A и матрицу сдвига подматрицы B, матрица сдвига подматрицы B может быть представлена в качестве базовой матрицы 30b-0; и

матрица сдвига подматрицы A является матрицей сдвига матрицы A0, или матрица сдвига подматрицы A включает в себя первые 16 столбцов матрицы сдвига матрицы A0, где матрица сдвига матрицы A0 может быть от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец любой одной из базовых матриц 30b-1, 30b-2, 30b-3, 30b-4, 30b-5, 30b-6, 30b-7 и 30b-8.

[0013] Для поддержки различных длин блока, LDPC код требует различных коэффициентов поднятия Z. На основе вышеописанной реализации, в возможной реализации, базовые матрицы, соответствующие различным коэффициентам поднятия Z, могут быть использованы на основе различных коэффициентов поднятия Z. Коэффициент поднятия может быть представлен как Z=a⋅2n, где a является любым целым числом в диапазоне от 8 до 15, и используется базовая матрица, соответствующая значению a.

[0014] Например,

если значение а равно 8, матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-1 на фиг. 3b.

[0015] Если значение а равно 9, матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-2 на фиг. 3b.

[0016] Если значение а равно 10, матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-3 на фиг. 3b.

[0017] Если значение а равно 11, матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-4 на фиг. 3b.

[0018] Если значение а равно 12, the матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-й строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-5 на фиг. 3b.

[0019] Если значение а равно 13, матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-6 на фиг. 3b.

[0020] Если значение а равно 14, матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-7 на фиг. 3b.

[0021] Если значение а равно 15, матрица сдвига матрицы A0 может быть представлена как от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-8 на фиг. 3b.

[0022] Подматрица A может дополнительно включать в себя два столбца встроенных выколотых битов.

[0023] Дополнительно, чтобы получить гибкие кодовые скорости, подматрица C, подматрица D и подматрица E в соответствующих размерах могут добавляться, основываясь на матрице ядра, чтобы получать различные кодовые скорости.

[0024] Подматрица C является нулевой матрицей с пятью строками и mD столбцами;

подматрица D включает в себя mD строк и 27 столбцов матрицы F, или подматрица D включает в себя mD строк и 21 столбец матрицы F, где матрица F является матрицей с 85 строками и 27 столбцами;

подматрица E является единичной матрицей с mD строками и mD столбцами; и

mD является целым числом и 0≤mD≤85.

[0025] Весами строк для строк матрицы F являются, соответственно, 5, 7, 7, 7, 6, 6, 6, 6, 6, 5, 6, 5, 4, 5, 5, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 3, 4, 3, 5, 4, 3, 4, 3, 3, 3, 4, 3, 3, 4, 4, 4, 3, 3, 4, 3, 3, 3, 3, 2, 2, 3, 3, 3, 3, 3, 3, 3, 2, 3, 2, 3, 3, 3, 3, 3, 2, 3, 3, 3, 2, 3, 3, 3, 4, 3, 3, 2, 3, 2, 3, 3, 3, 4, 3, 3.

[0026] В возможной реализации, матрица F является матрицей, составленной из 5-й строки по 89-ю строку и 0-го столбца по 26-й столбец базового графа 30a.

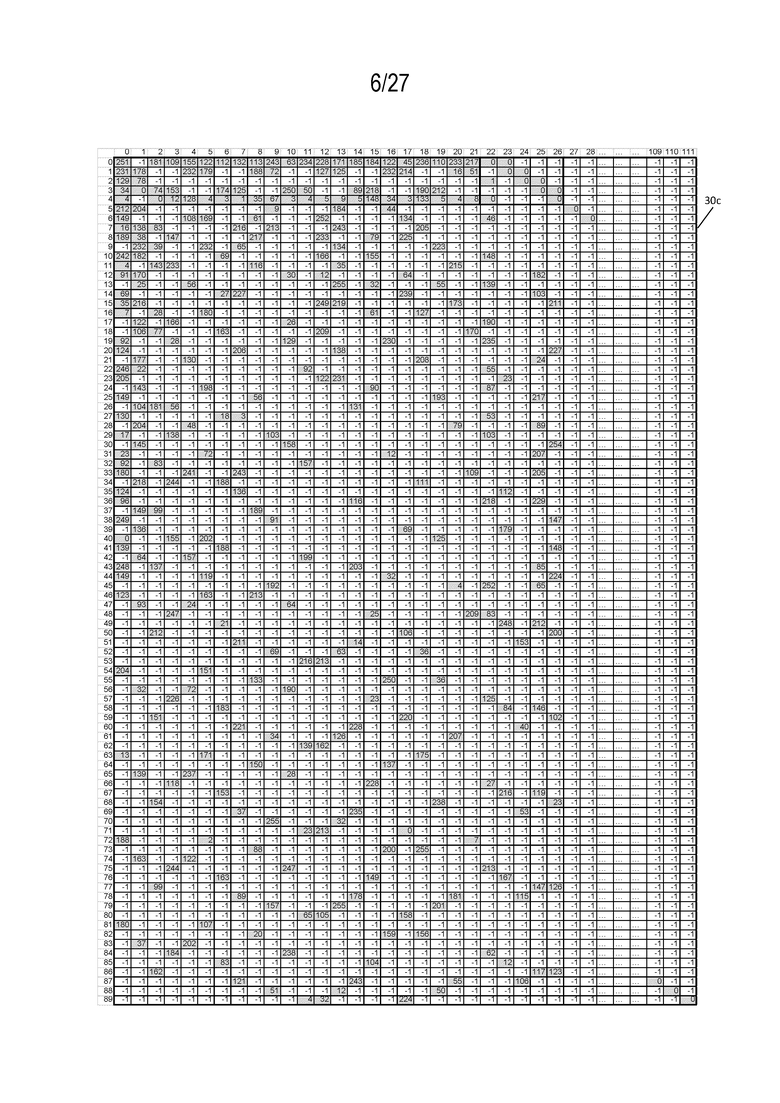

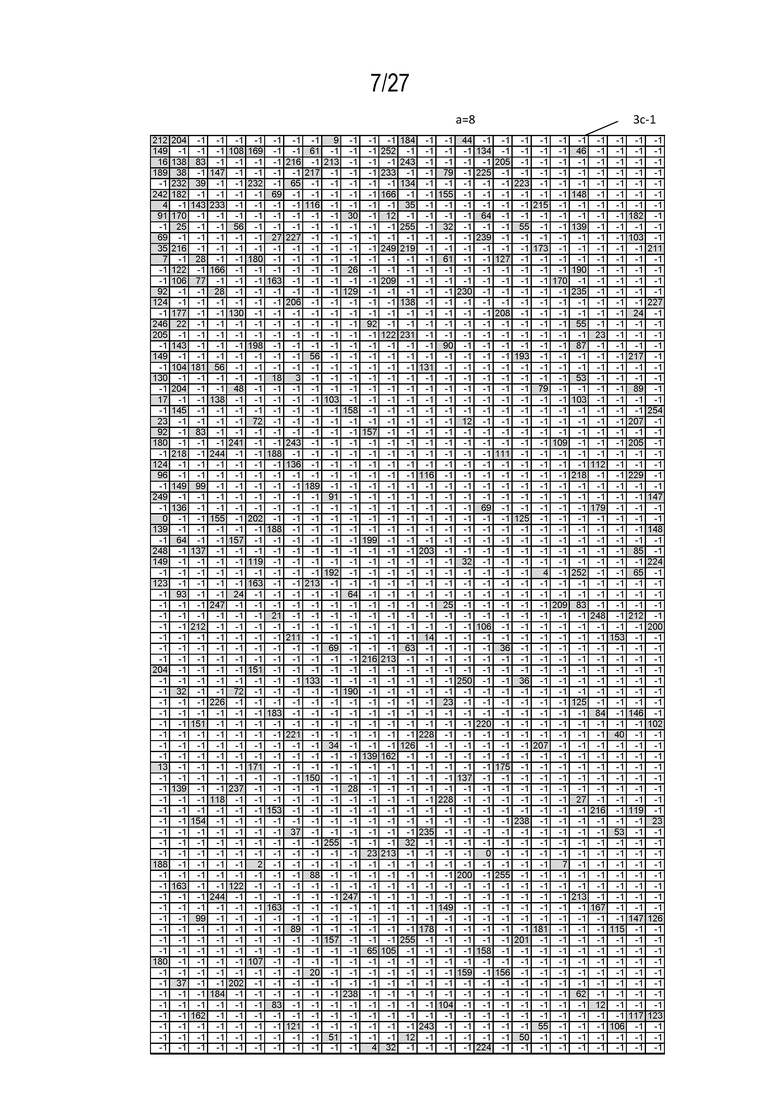

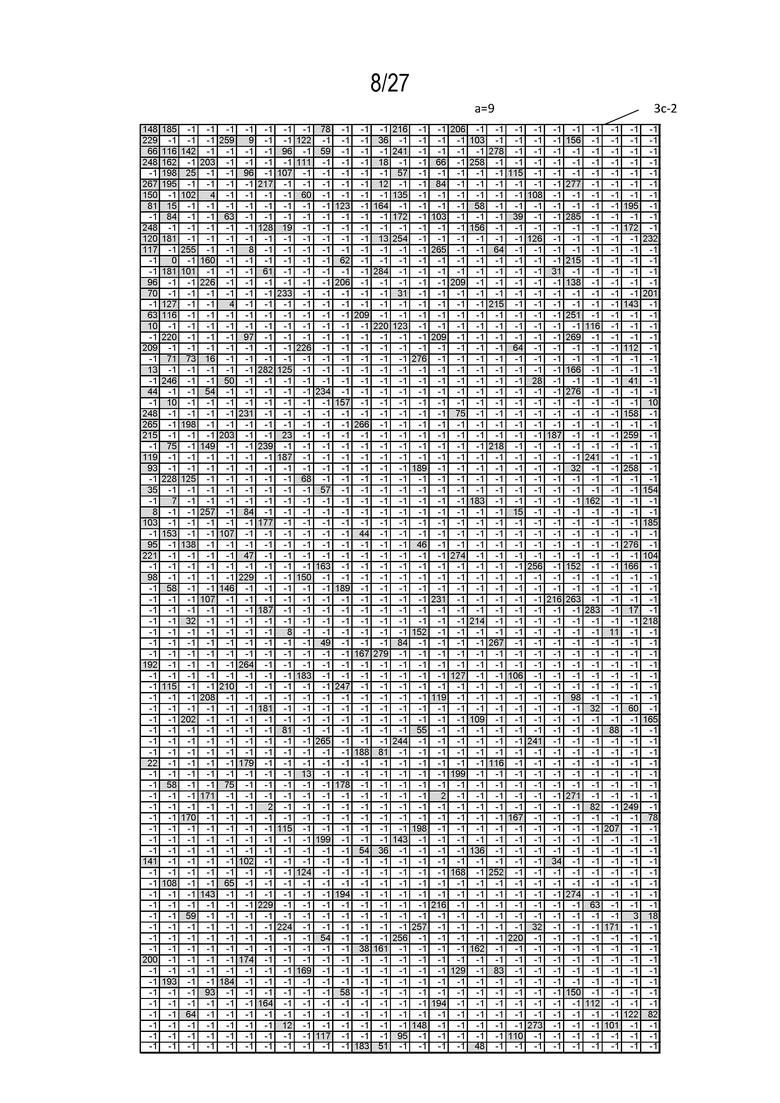

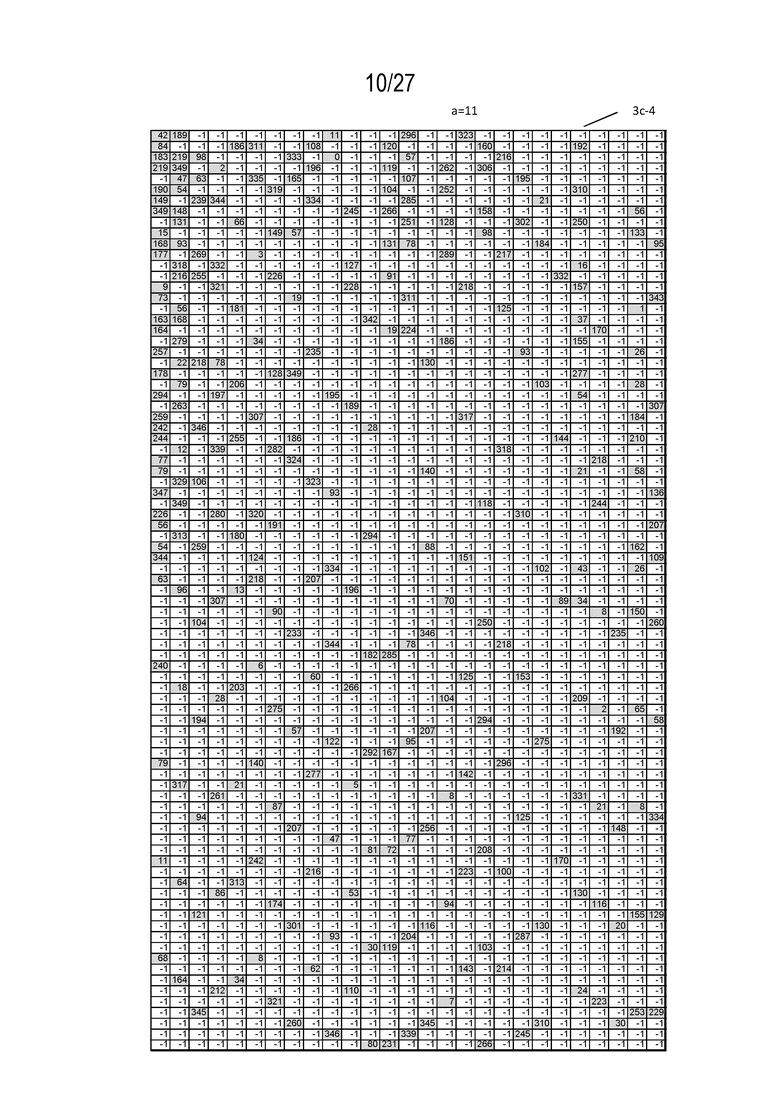

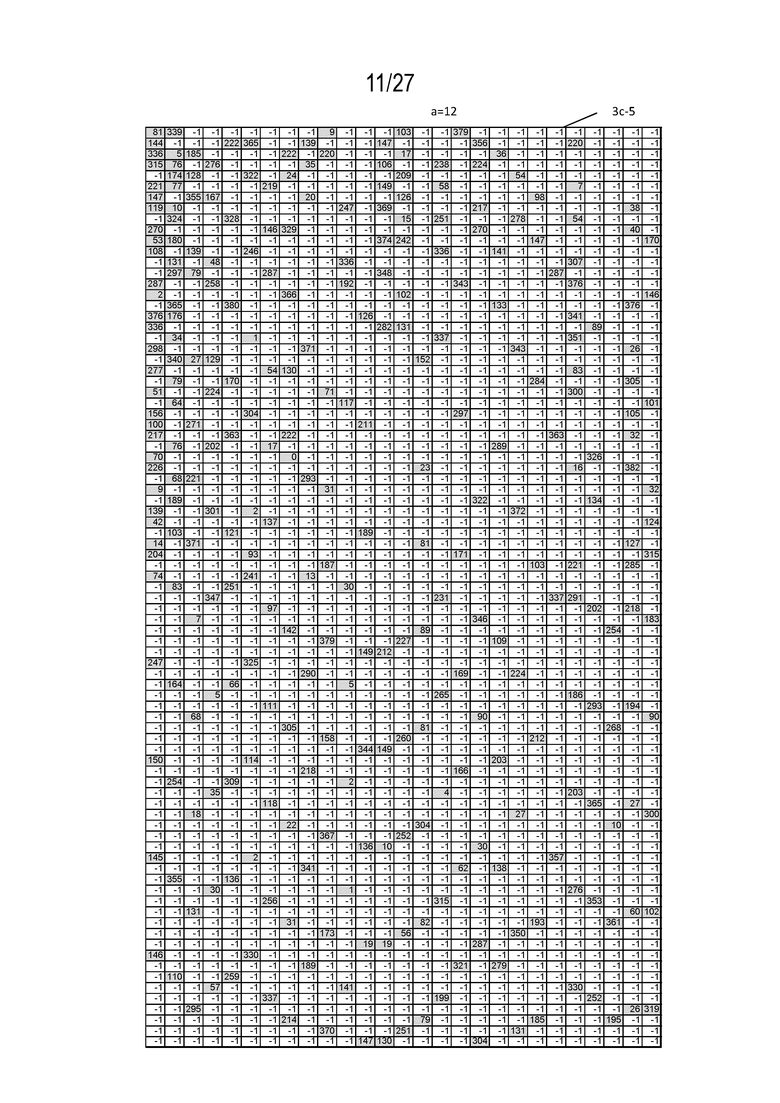

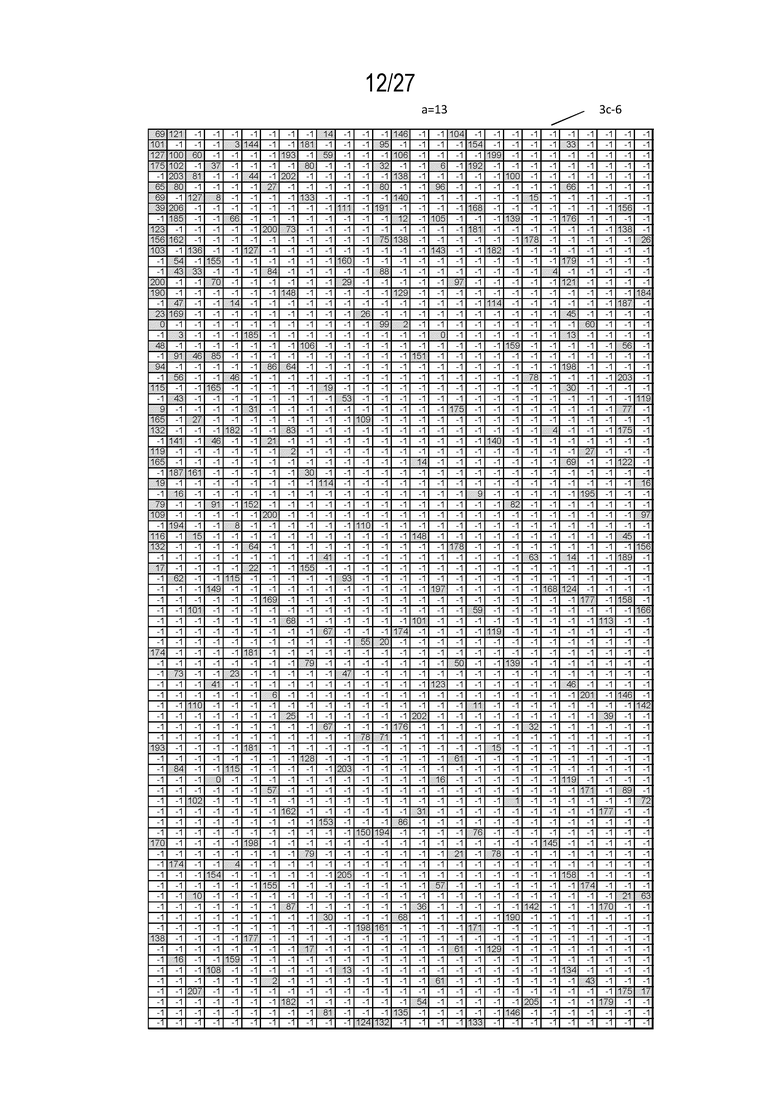

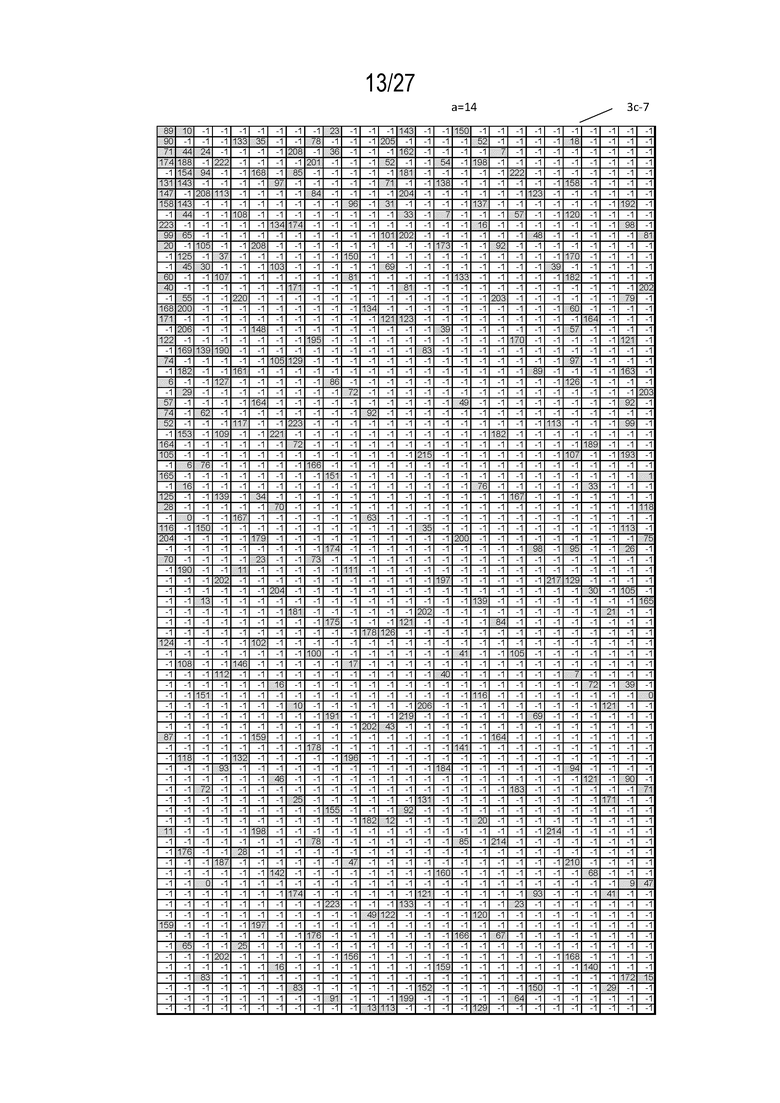

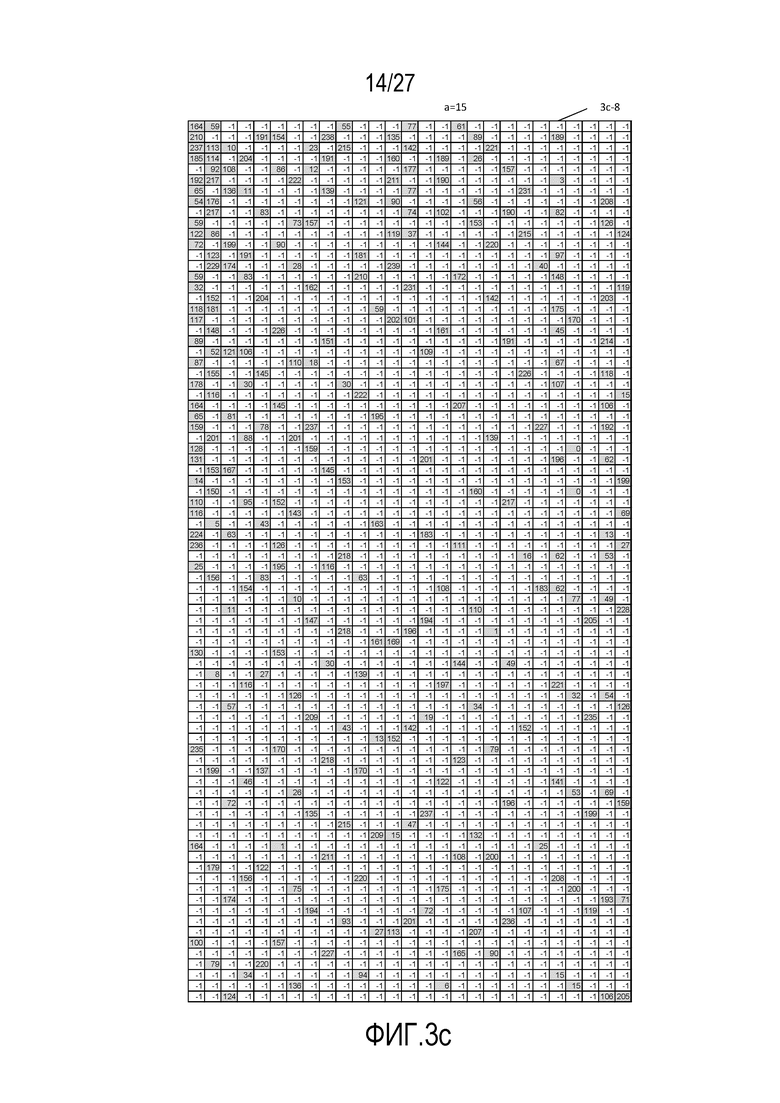

[0027] В возможной реализации, матрица сдвига матрицы F может быть представлена как любая одна из базовых матриц 3c-1, 3c-2, 3c-3, 3c-4, 3c-5, 3c-6, 3c-7 и 3c-8.

[0028] Для поддержки различных длин блока, LDPC код требует различных коэффициентов поднятия Z. На основе вышеописанной реализации, в возможной реализации, базовые матрицы, соответствующие различным коэффициентам поднятия Z, могут быть использованы на основе различных коэффициентов поднятия Z. Например,

значение а может быть определено на основе Z, и может быть использована базовая матрица, соответствующая значению a.

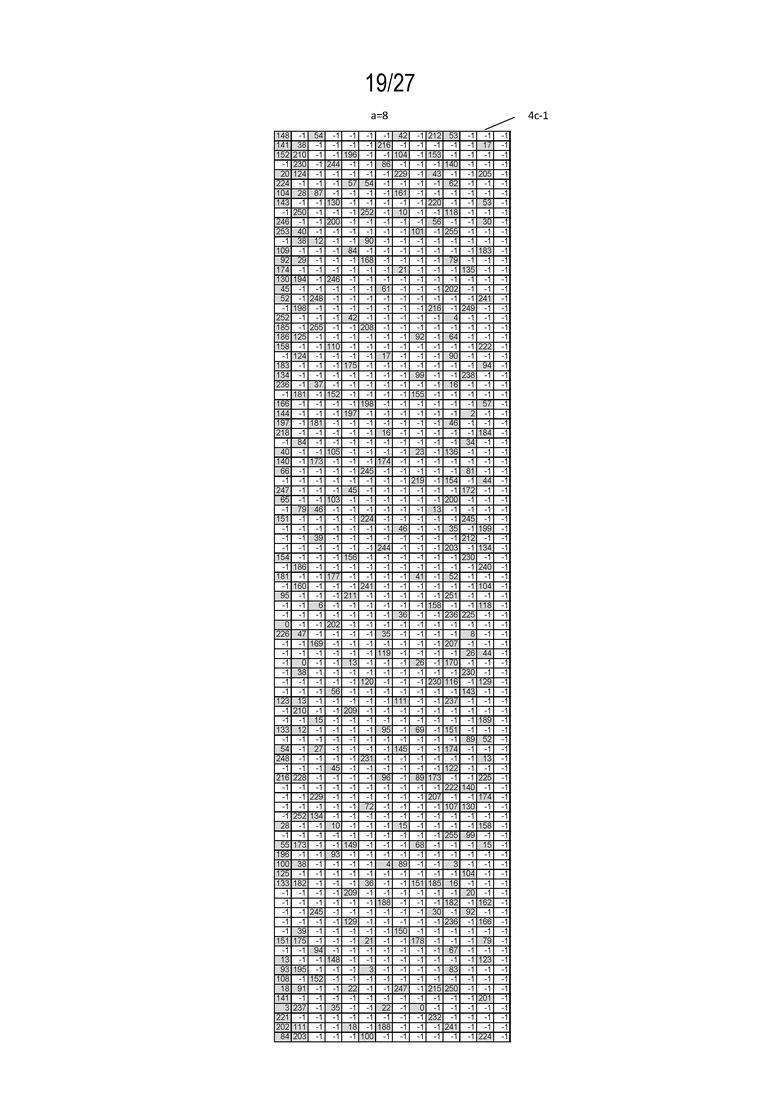

[0029] Если значение а равно 8, матрица сдвига матрицы F может быть представлена как 3c-1.

[0030] Если значение а равно 9, матрица сдвига матрицы F может быть представлена как 3c-2.

[0031] Если значение а равно 10, матрица сдвига матрицы F может быть представлена как 3c-3.

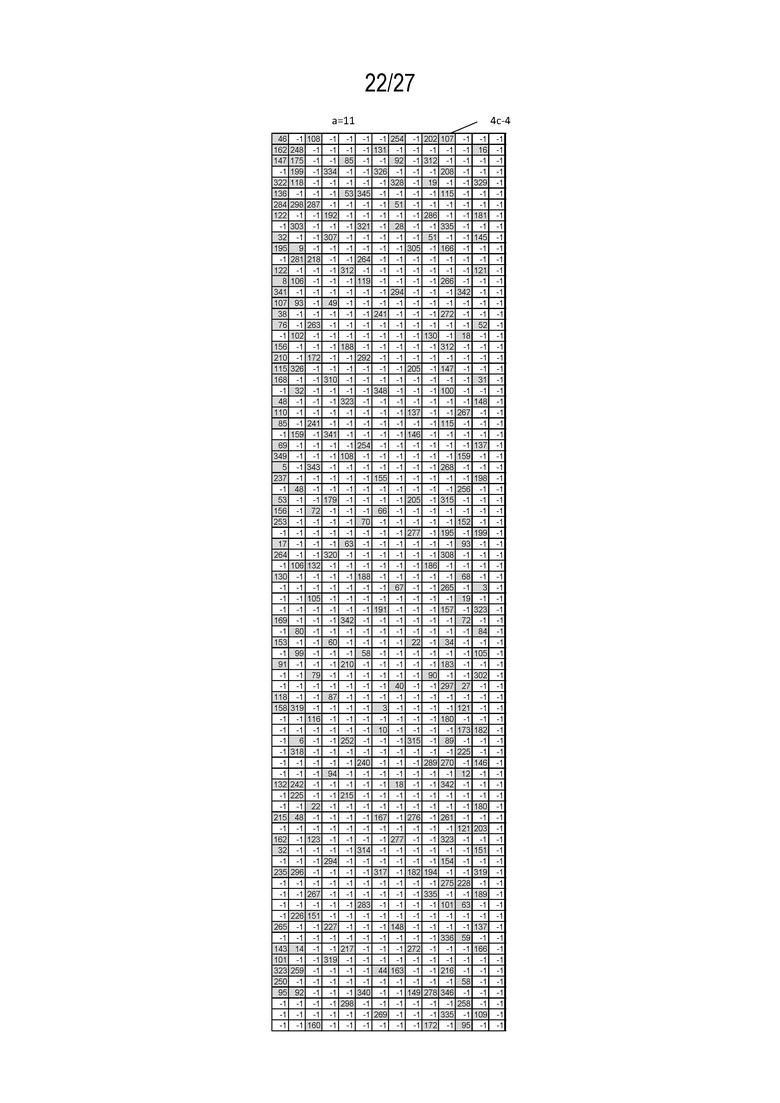

[0032] Если значение а равно 11, матрица сдвига матрицы F может быть представлена как 3c-4.

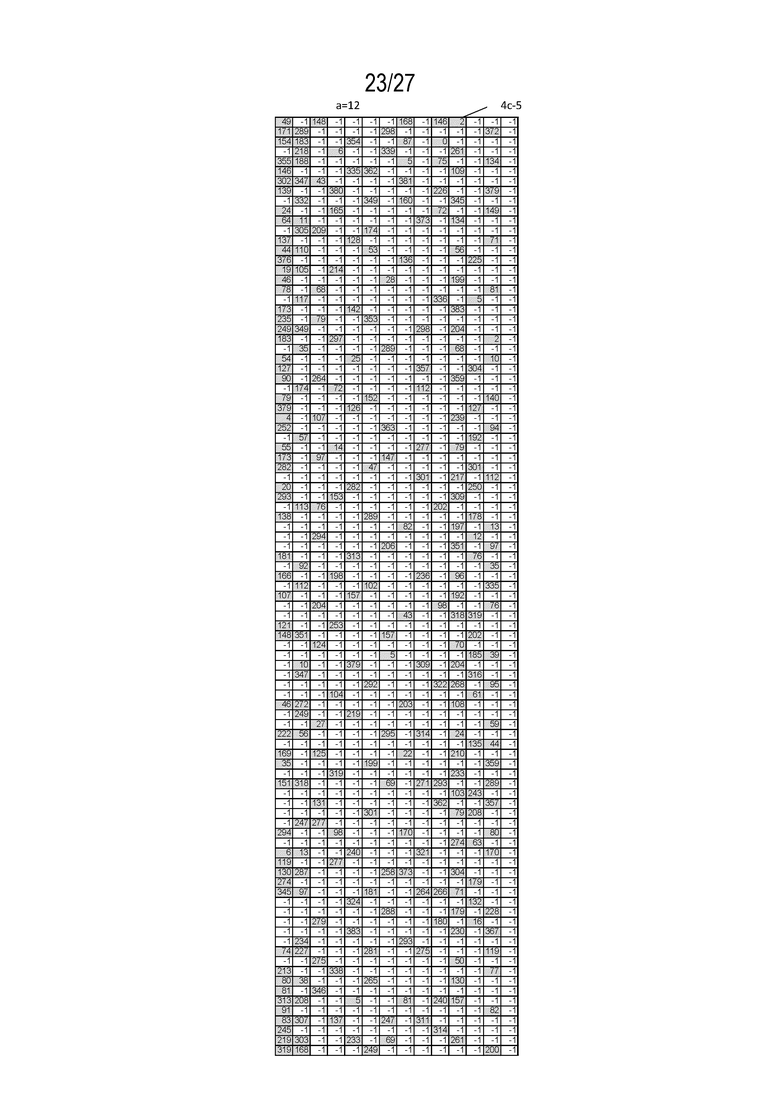

[0033] Если значение а равно 12, матрица сдвига матрицы F может быть представлена как 3c-5.

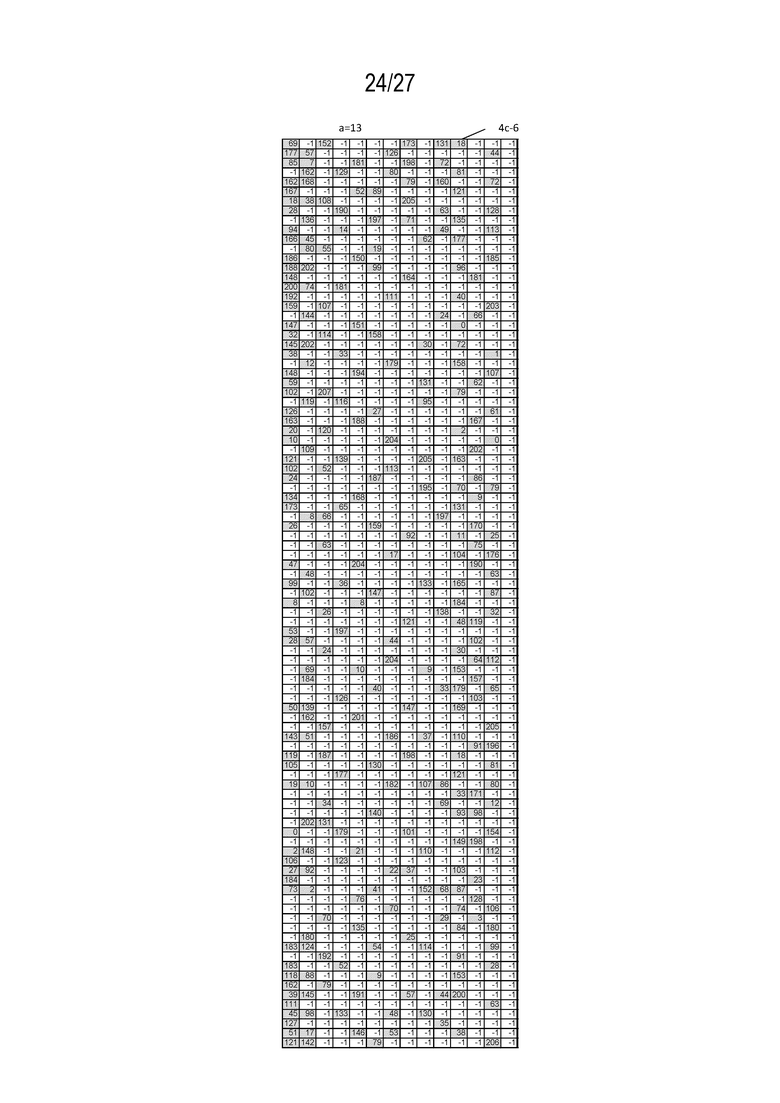

[0034] Если значение а равно 13, матрица сдвига матрицы F может быть представлена как 3c-6.

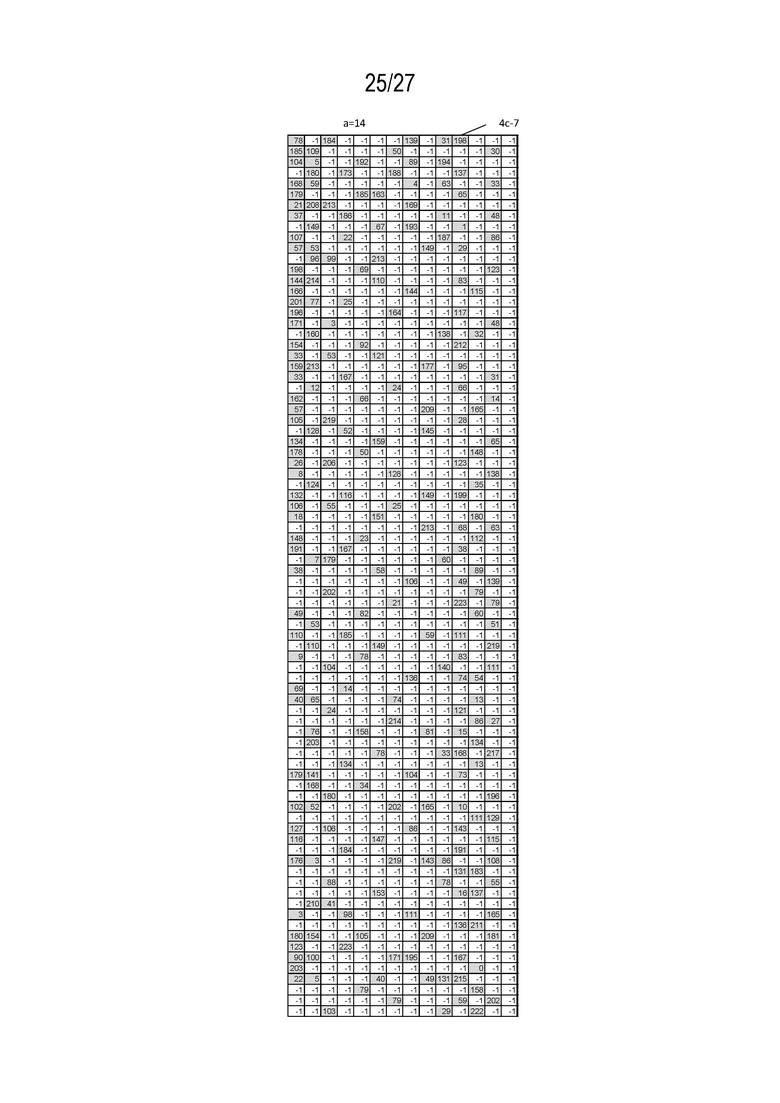

[0035] Если значение а равно 14, матрица сдвига матрицы F может быть представлена как 3c-7.

[0036] Если значение а равно 15, матрица сдвига матрицы F может быть представлена как 3c-8.

[0037] Во второй реализации первого аспекта или второго аспекта,

базовый граф LDPC матрицы представлен как матрица с m строками и n столбцами, m является целым числом, большим или равным 4, и n является целым числом, большим или равным 14; и

базовый граф включает в себя по меньшей мере подматрицу A и подматрицу B, причем

подматрица A является матрицей с четырьмя строками и 10 столбцами; и

подматрица B является матрицей с четырьмя строками и четырьмя столбцами, и подматрица B включает в себя один столбец, вес которого равен 3, один столбец, вес которого равен 1, и подматрицу Bʹ бидиагональной структуры.

[0038] В матрице, состоящей из подматрицы A и подматрицы B, имеется одна строка, вес которой больше или равен 1 и меньше или равен 5, и веса остальных трех строк, каждый, больше или равны 10 и меньше или равны 13.

[0039] В одной реализации, в матрице, составленной из подматрицы A и подматрицы B, имеется одна строка, вес которой равен 3, и три строки, веса которых равны 12.

[0040] В этой реализации, матрица, составленная из подматрицы A и подматрицы B, может включать в себя четыре строки от 0-й строки по 3-ю строку и от 0-го столбца по 13-й столбец в базовом графе 40a, строки могут быть взаимозаменяемыми, и столбцы могут также быть взаимозаменяемыми.

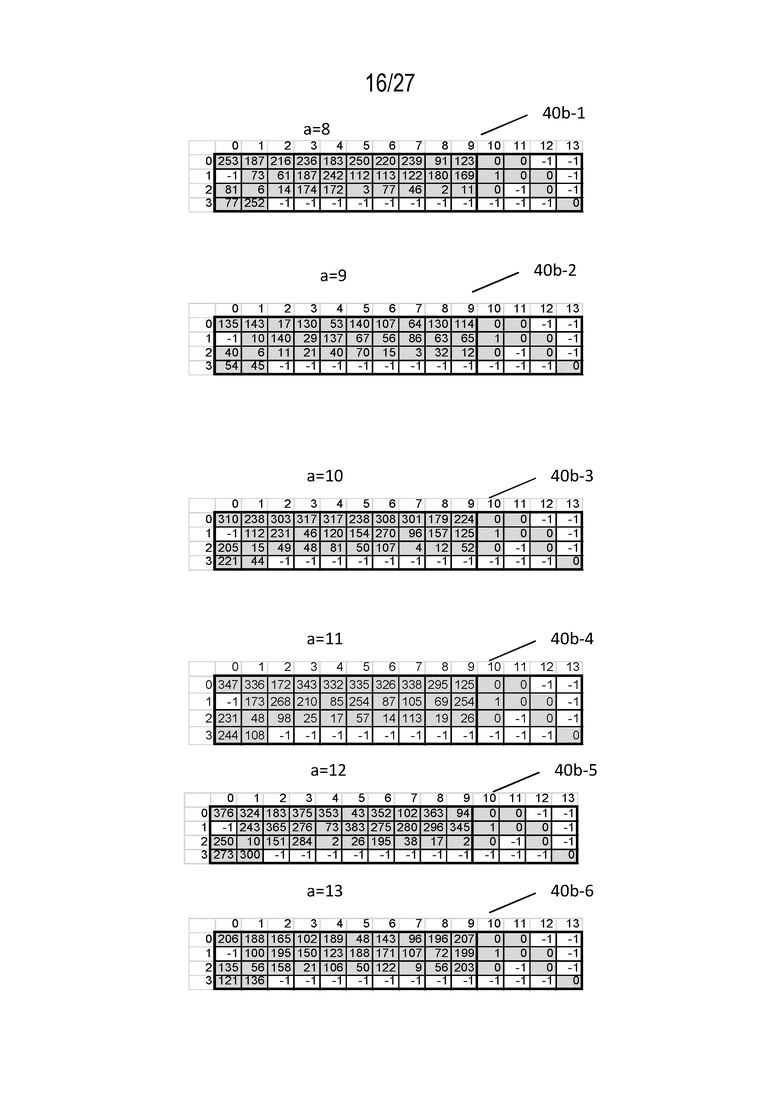

[0041] На основе вышеописанной реализации, часть, которая является базовой матрицей LDPC матрицы и соответствует матрице, составленной из подматрицы A и подматрицы B, может быть представлена как любая одна из базовых матриц 40b-1, 40b-2, 40b-3, 40b-4, 40b-5, 40b-6, 40b-7 и 40b-8.

[0042] Для поддержки различных длин блока, LDPC код требует различных коэффициентов поднятия Z. На основе вышеописанной реализации, в возможной реализации, базовые матрицы, соответствующие различным коэффициентам поднятия Z, могут быть использованы на основе различных коэффициентов поднятия Z.

[0043] Например,

коэффициент поднятия может быть представлен как Z=a⋅2n, где a является любым целым числом от 8 до 15, и используется базовая матрица, соответствующая значению а.

[0044] Если значение а равно 8, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-1 на фиг. 4b.

[0045] Если значение а равно 9, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-2 на фиг. 4b.

[0046] Если значение а равно 10, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-3 на фиг. 4b.

[0047] Если значение а равно 11, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-4 на фиг. 4b.

[0048] Если значение а равно 12, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-5 на фиг. 4b.

[0049] Если значение а равно 13, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-6 на фиг. 4b.

[0050] Если значение а равно 14, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-7 на фиг. 4b.

[0051] Если значение а равно 15, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-8 на фиг. 4b.

[0052] Подматрица A может дополнительно включать в себя два столбца встроенных выколотых битов.

[0053] Дополнительно, для получения гибких кодовых скоростей, подматрица C, подматрица D и подматрица E в соответствующих размерах могут быть добавлены на основе матрицы ядра, чтобы получить различные кодовые скорости.

[0054] Подматрица C является нулевой матрицей с четырьмя строками и mD столбцами;

подматрица D является матрицей с mD строками и 14 столбцами;

подматрица E является единичной матрицей с mD строками и mD столбцами; и

mD является целым числом и 0≤mD≤113.

[0055] Подматрица D включает в себя mD строк матрицы F, матрица F имеет 113 строк и 14 столбцов, и веса строк для строк матрицы F, соответственно, равны 5, 4, 5, 4, 5, 4, 4, 4, 4, 4, 4, 3, 3, 4, 3, 3, 3, 3, 3, 3, 3, 4, 3, 3, 3, 3, 3, 3, 3, 3, 3, 3, 2, 4, 3, 3, 3, 3, 3, 3, 3, 3, 2, 3, 3, 2, 4, 3, 3, 3, 3, 2, 4, 2, 3, 4, 2, 4, 2, 4, 2, 2, 5, 2, 4, 3, 2, 6, 2, 3, 3, 2, 4, 2, 5, 2, 5, 2, 6, 2, 3, 3, 3, 2, 5, 2, 3, 4, 2, 6, 2, 5, 2, 5, 4, 3, 3, 2, 4, 4, 2, 3, 2, 6, 2, 3, 3, 4, 2, 2, 6, 2, 3.

[0056] В возможной реализации, матрица F является матрицей, составленной из 4-й строки по 116-ю строку и 0-го столбца по 13-й столбец в базовом графе 40a.

[0057] В возможной реализации, матрица сдвига матрицы F может быть представлена как любая одна из базовых матриц 4c-1, 4c-2, 4c-3, 4c-4, 4c-5, 4c-6, 4c-7 и 4c-8.

[0058] Для поддержки различных длин блока, LDPC код требует различных коэффициентов поднятия Z. На основе вышеописанной реализации, в возможной реализации, базовые матрицы, соответствующие различным коэффициентам поднятия Z, могут быть использованы на основе различных коэффициентов поднятия Z. Например,

если значение а равно 8, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-1;

если значение а равно 9, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-2;

если значение а равно 10, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-3;

если значение а равно 11, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-4;

если значение а равно 12, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-5;

если значение а равно 13, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-6;

если значение а равно 14, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-7; и

если значение а равно 15, подматрица D в базовой матрице может включать в себя mD строк матрицы сдвига, показанной в 4c-8.

[0059] Базовый граф и базовая матрица LDPC матрицы в первой реализации могут удовлетворять KB=22 и требование к рабочим характеристикам кодового блока с длиной блока от 640 до 8448 битов и удовлетворять KB=16 и требование к рабочим характеристикам кодового блока с длиной блока от 40 до 2560 битов. Базовый граф и базовая матрица LDPC матрицы во второй реализации могут удовлетворять KB=10 и требование к рабочим характеристикам кодового блока с длиной блока от 40 до 2560 битов.

[0060] На основе любого из вышеописанных аспектов или возможных реализаций аспектов, в другой возможной реализации, способ дополнительно включает в себя: определение коэффициента поднятия Z. Например, значение коэффициента поднятия Z определяется в соответствии с длиной K информационной битовой последовательности. Например, если длина информационной битовой последовательности равна K, минимальное значение, которое удовлетворяет 22×Z≥K, может быть определено во множестве коэффициентов поднятия, определенных в системе.

[0061] Для устройства связи на передающем конце, кодирование информационной битовой последовательности с использованием LDPC матрицы включает в себя:

кодирование информационной битовой последовательности с использованием LDPC матрицы, соответствующей коэффициенту поднятия Z.

[0062] Для устройства связи на приемном конце, декодирование принятого сигнала с использованием LDPC матрицы включает в себя:

декодирование принятого сигнала с использованием LDPC матрицы, соответствующей коэффициенту поднятия Z.

[0063] На основе любого из предыдущих аспектов или возможных реализаций аспектов, в другой возможной реализации, базовая матрица LDPC матрицы сохранена в памяти.

[0064] На основе любого из предыдущих аспектов или возможных реализаций аспектов, в другой возможной реализации, базовый граф LDPC матрицы сохранен в памяти, и значения сдвига ненулевых элементов в базовой матрице LDPC матрицы сохранены в памяти от строки к строке и от столбца к столбу.

[0065] В соответствии с третьим аспектом, обеспечено устройство обработки информации в системе связи, и устройство может быть сконфигурировано для выполнения способа в соответствии с первым аспектом или возможными реализациями первого аспекта. В отношении деталей, можно сослаться на описание для предыдущего аспекта.

[0066] Дополнительно, устройство включает в себя:

блок определения, сконфигурированный, чтобы определять коэффициент поднятия Z для кодирования информационной битовой последовательности; и

блок обработки, сконфигурированный, чтобы кодировать информационную битовую последовательность с использованием LDPC матрицы, соответствующей коэффициенту поднятия Z.

[0067] В возможном варианте, устройство обработки информации, обеспеченное в настоящей заявке, может включать в себя соответствующий модуль, который сконфигурирован, чтобы выполнять любое из первого аспекта или возможных реализаций первого аспекта в вышеописанном варианте способа. Модуль может представлять собой программное обеспечение и/или аппаратное средство.

[0068] В соответствии с четвертым аспектом, обеспечено устройство обработки информации в системе связи, и устройство может быть сконфигурировано, чтобы выполнять способ в соответствии с любым из второго аспекта или возможных реализаций второго аспекта. В отношении деталей, можно сослаться на описание для вышеописанного аспекта.

[0069] Дополнительно, устройство включает в себя:

блок получения, сконфигурированный, чтобы получать мягкое значение LDPC кода и коэффициент поднятия Z; и

блок обработки, сконфигурированный, чтобы декодировать мягкое значение LDPC кода на основе базовой матрицы HB, соответствующей коэффициенту поднятия Z, чтобы получить информационную битовую последовательность.

[0070] В возможной реализации, устройство обработки информации, обеспеченное в настоящей заявке, может включать в себя соответствующий модуль, который сконфигурирован, чтобы выполнять любое из второго аспекта или возможных реализаций второго аспекта в вышеописанном варианте способа. Модуль может представлять собой программное обеспечение и/или аппаратное средство.

[0071] В соответствии с пятым аспектом, обеспечено устройство связи, которое включает в себя кодер и приемопередатчик.

[0072] Кодер включает в себя устройство обработки информации в соответствии с третьим аспектом и сконфигурирован, чтобы кодировать информационные данные.

[0073] Приемопередатчик сконфигурирован, чтобы передавать сигнал, соответствующий кодированным информационным данным.

[0074] В соответствии с шестым аспектом, обеспечено устройство связи, включающее в себя декодер и приемопередатчик.

[0075] Декодер включает в себя устройство обработки информации в соответствии с четвертым аспектом и сконфигурирован, чтобы декодировать принятый сигнал.

[0076] Приемопередатчик сконфигурирован, чтобы принимать сигналы, включающие в себя сигнал, кодированный на основе LDPC.

[0077] В соответствии с седьмым аспектом, вариант осуществления настоящего изобретения обеспечивает систему связи, и система включает в себя устройство связи в соответствии с пятым аспектом и устройство связи в соответствии с шестым аспектом.

[0078] В соответствии с другим аспектом, вариант осуществления настоящего изобретения обеспечивает компьютерный носитель хранения данных, и компьютерный носитель хранения данных включает в себя программы, созданные для осуществления вышеописанных аспектов.

[0079] Еще один аспект настоящей заявки обеспечивает компьютерный программный продукт, включающий в себя инструкцию, и когда компьютерный программный продукт исполняется на компьютере, компьютер выполняет способы в соответствии с вышеописанными аспектами.

[0080] Способ и устройство обработки информации, устройство связи и система связи в вариантах осуществления настоящего изобретения являются адаптируемыми к системным требованиям для гибких и изменяемых длин кода и кодовых скоростей в показателях рабочих характеристик кода и минимальных уровней ошибок.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

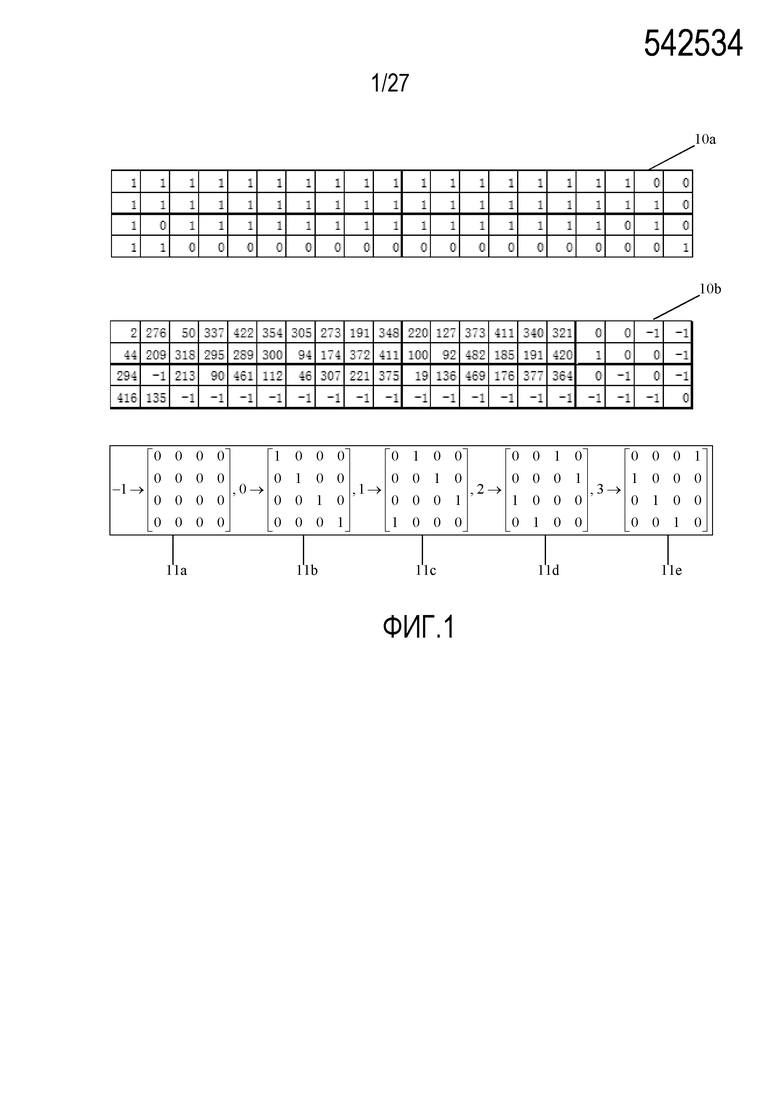

[0081] Фиг. 1 является схематичной диаграммой базового графа, базовой матрицы и циркулянтной матрицы перестановок LDPC кода;

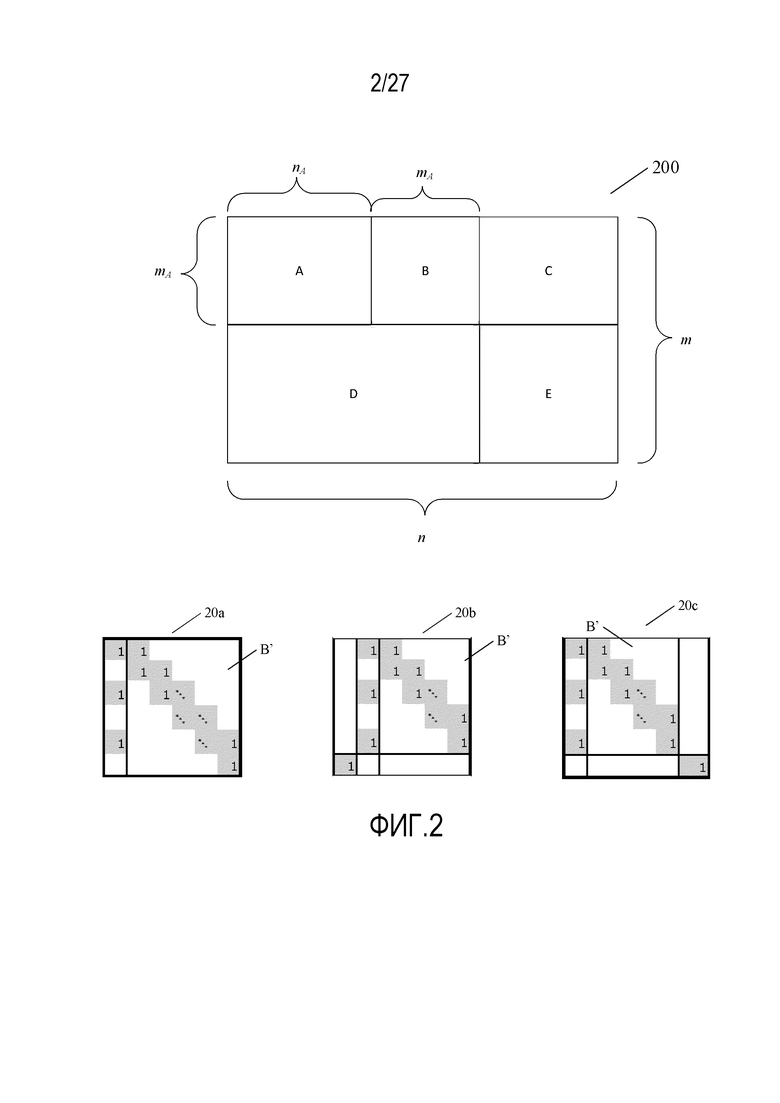

[0082] Фиг. 2 является схематичной структурной диаграммой базового графа LDPC кода;

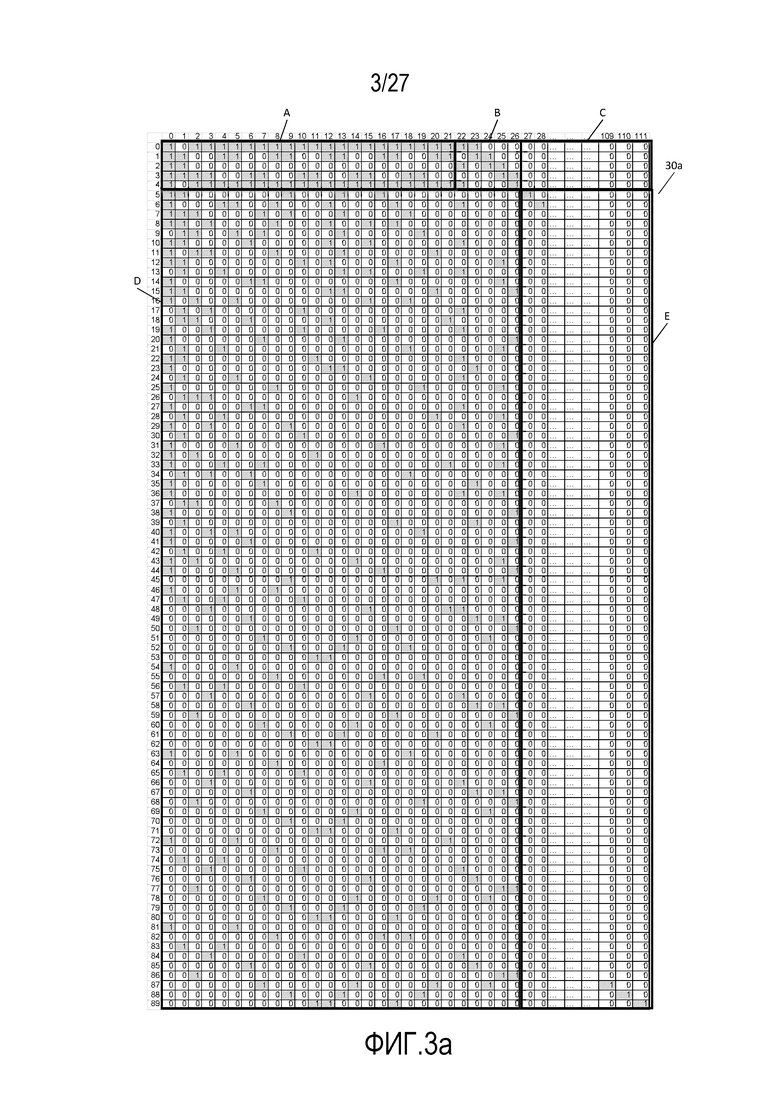

[0083] Фиг. 3a является схематичной структурной диаграммой базового графа LDPC кода в соответствии с вариантом осуществления настоящего изобретения;

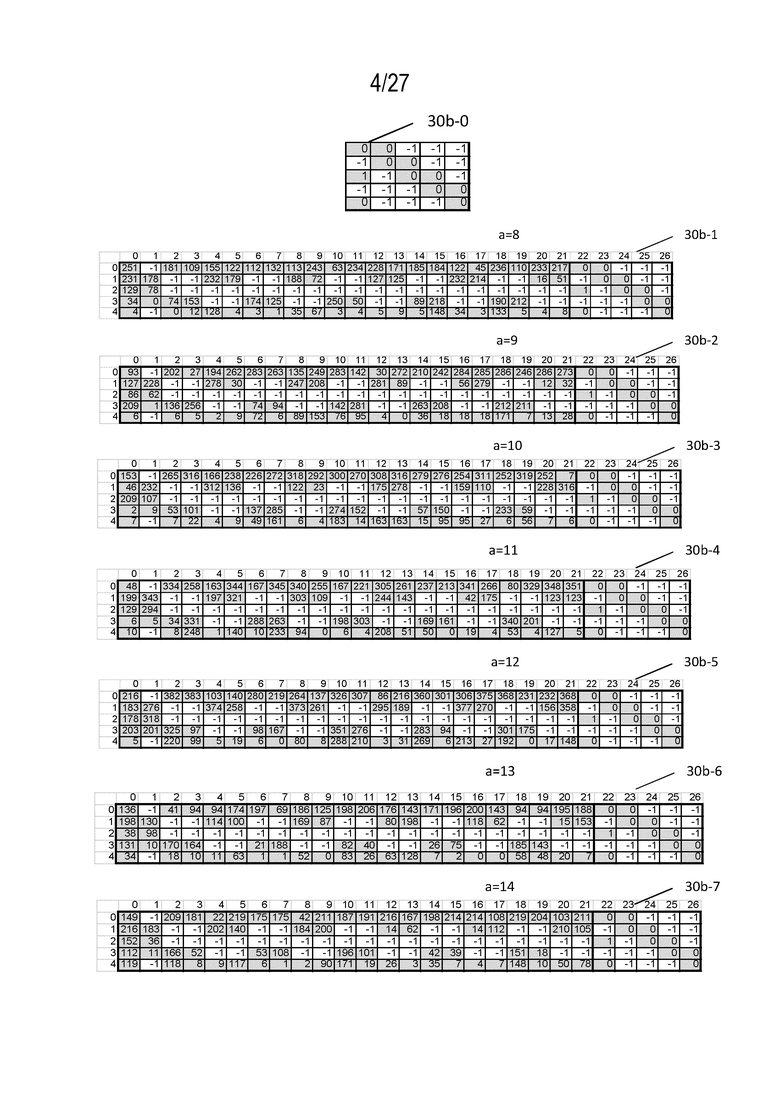

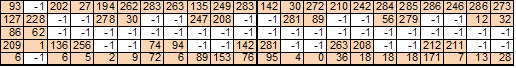

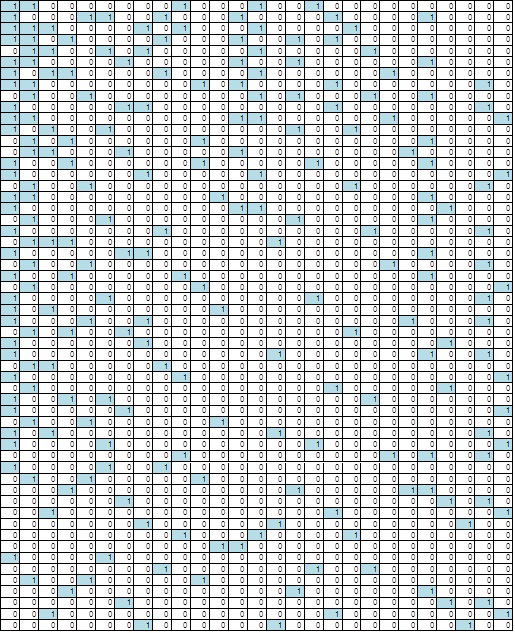

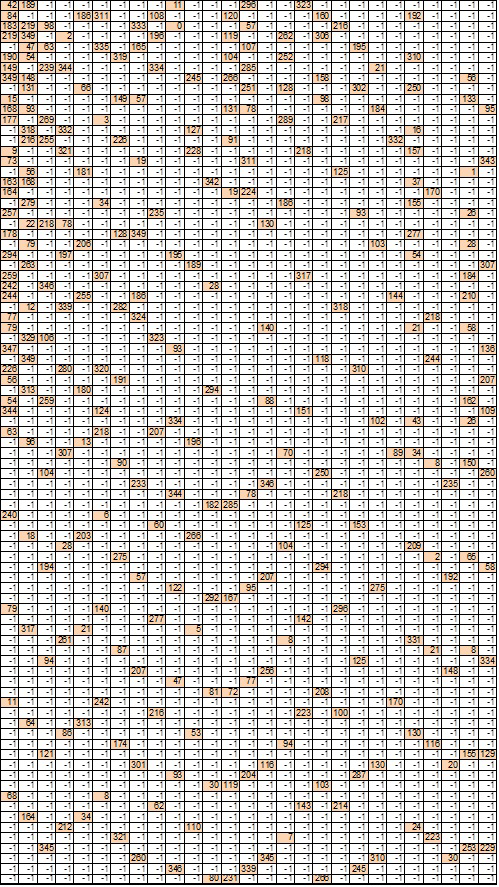

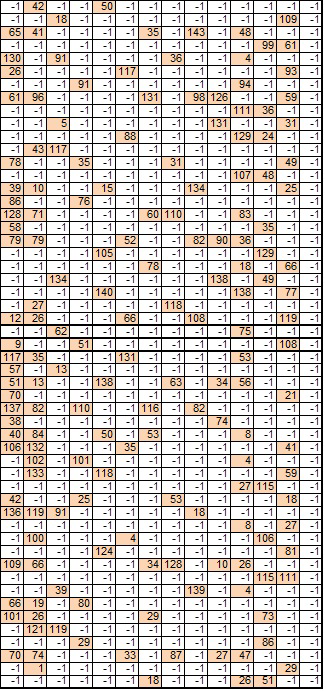

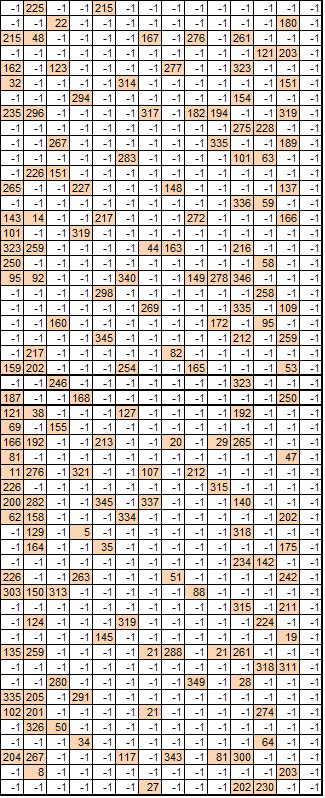

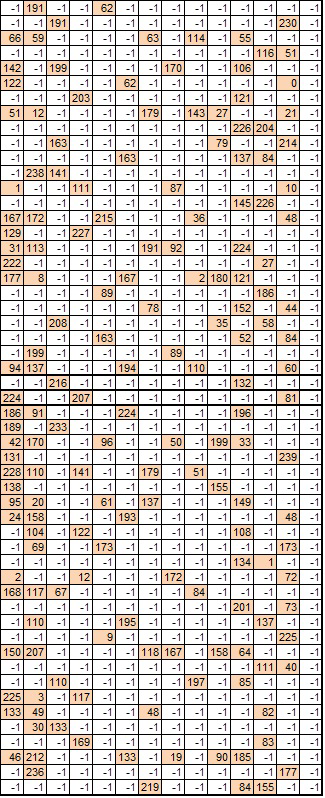

[0084] Фиг. 3b является схематичной диаграммой базовой матрицы LDPC кода в соответствии с другим вариантом осуществления настоящего изобретения;

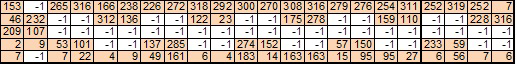

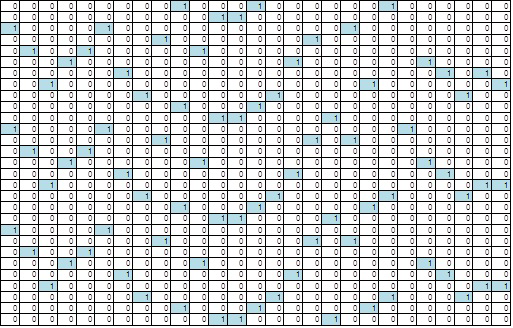

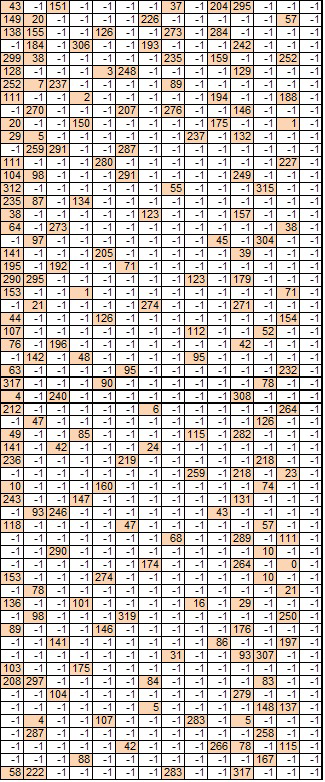

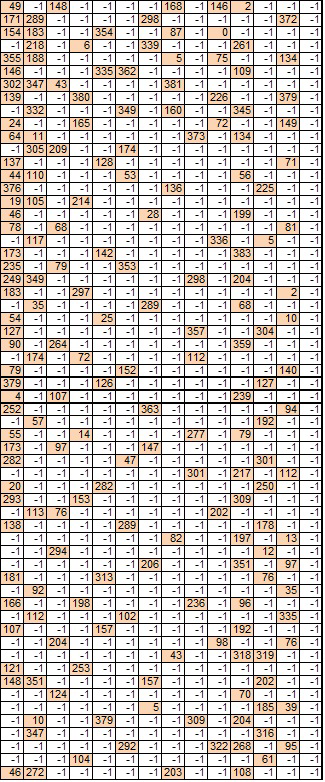

[0085] Фиг. 3c является схематичной диаграммой базовой матрицы LDPC кода в соответствии с другим вариантом осуществления настоящего изобретения;

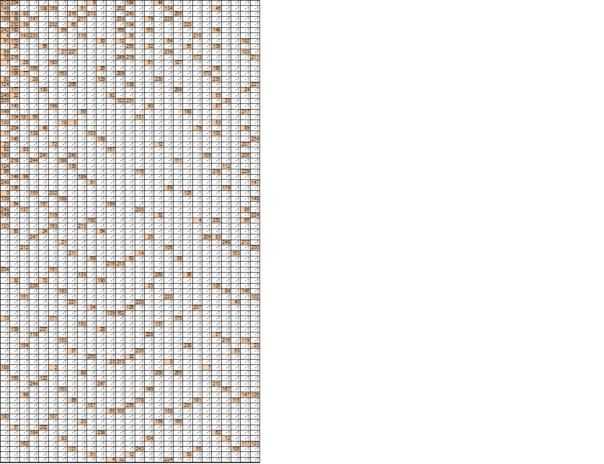

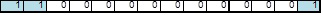

[0086] Фиг. 4a является схематичной диаграммой базового графа LDPC кода в соответствии с другим вариантом осуществления настоящего изобретения;

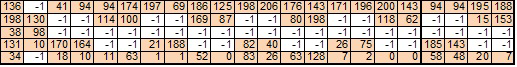

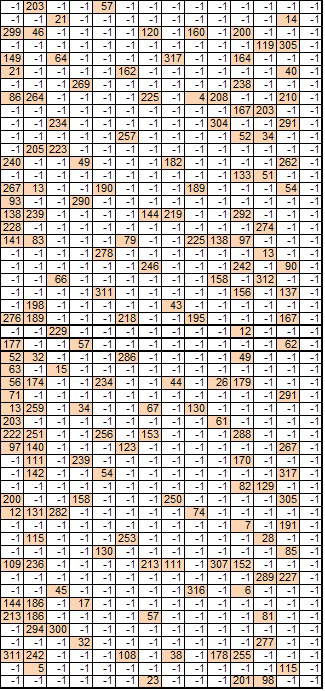

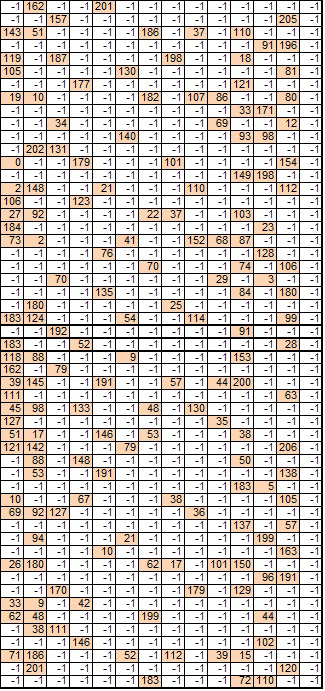

[0087] Фиг. 4b является схематичной диаграммой базовой матрицы LDPC кода в соответствии с другим вариантом осуществления настоящего изобретения;

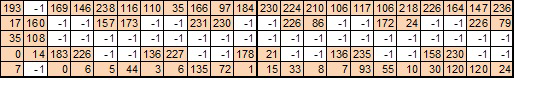

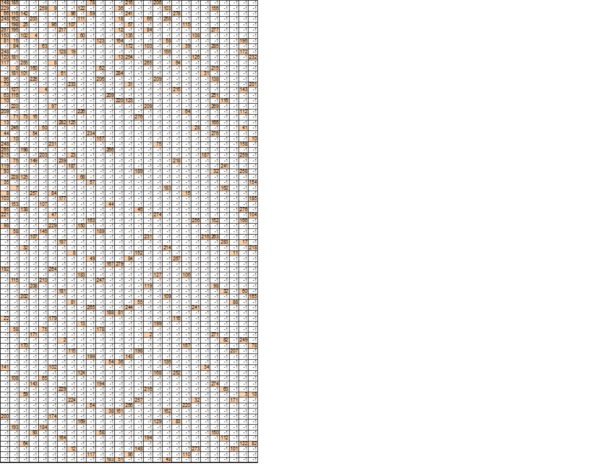

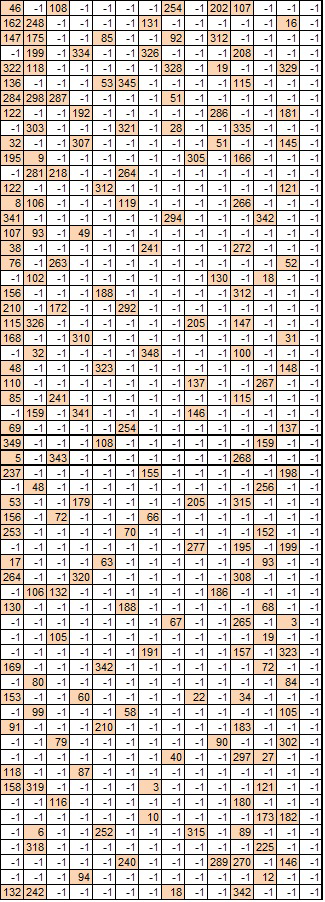

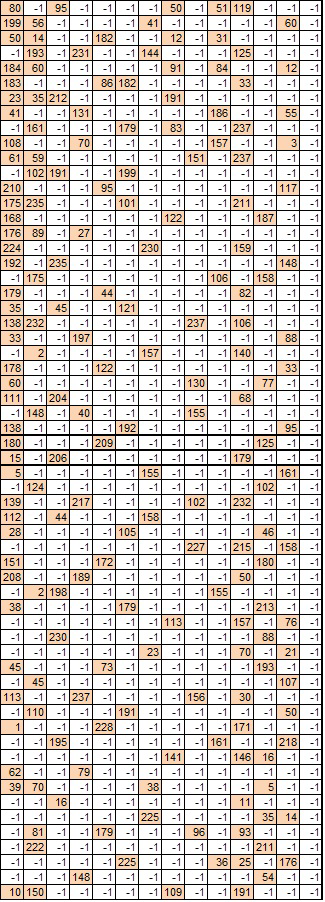

[0088] Фиг. 4c является схематичной диаграммой базовой матрицы LDPC кода в соответствии с другим вариантом осуществления настоящего изобретения;

[0089] Фиг. 5 является структурной схемой устройства обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

[0090] Фиг. 6 является структурной схемой устройства обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

[0091] Фиг. 7 является структурной схемой устройства связи в соответствии с другим вариантом осуществления настоящего изобретения; и

[0092] Фиг. 8 является структурной схемой устройства связи в соответствии с другим вариантом осуществления настоящего изобретения.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0093] Ниже описаны технические решения в вариантах осуществления настоящего изобретения со ссылкой на приложенные чертежи в вариантах осуществления настоящего изобретения.

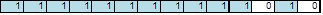

[0094] Обычно, LDPC код может быть представлен как матрица Н проверки четности. Матрица Н проверки четности LDPC кода может быть получена с использованием базового графа (base graph) и значения сдвига (shift). Базовый граф может обычно включать в себя m×n матричных элементов и может быть представлен как матрица с m строками и n столбцами. Значением матричного элемента является 0 или 1. Элемент со значением 0 иногда упоминается как нулевой элемент, и это указывает, что элемент может быть заменен Z×Z нулевой матрицей (zero matrix). Элемент со значением 1 иногда упоминается как ненулевой элемент, и это указывает, что элемент может быть заменен Z×Z циркулянтной матрицей перестановок (circulant permutation matrix). Как показано на фиг. 1, 10a является примером элементов базового графа LDPC кода QC структуры, когда m=4 и n=20.

[0095] Если значение элемента в i-й строке и j-м столбце в базовом графе равно 1, значением сдвига элемента является Pi,j, и Pi,j является целым числом, большим или равным 0, это указывает, что элемент со значением 1 в i-й строке и j-м столбце может быть заменен Z×Z циркулянтной матрицей перестановок, соответствующей Pi,j. Циркулянтная матрица перестановок может быть получена путем выполнения Pi,j циклических сдвигов над Z×Z единичной матрицей вправо. Можно видеть, что, в базовом графе, каждый элемент со значением 0 заменяется Z×Z нулевой матрицей, и каждый элемент со значением 1 заменяется Z×Z циркулянтной матрицей перестановок соответственно значению сдвига элемента, так что может быть получена матрица проверки четности LDPC кода. Z является положительным целым числом и может также упоминаться как коэффициент поднятия (lifting) и может быть определен в соответствии с размером кодового блока и размером информационных данных, которые поддерживаются системой. Можно видеть, что размером матрицы Н проверки четности является (m×Z)×(n×Z). Например, если коэффициент поднятия Z=4, каждый нулевой элемент заменяется нулевой матрицей 11a, размером которой является 4×4. Если P2,3=2, ненулевой элемент во второй строке и третьем столбце заменяется 4×4 циркулянтной матрицей перестановок 11d. Матрица получается путем выполнения двух циклических сдвигов над 4×4 единичной матрицей 11b вправо. Если P2,4=0, ненулевой элемент во второй строке и третьем столбце заменяется единичной матрицей 11b. Следует отметить, что это является только примером для описания в настоящем документе и не используется в качестве ограничения.

[0096] Поскольку Pi,j может быть получено на основе коэффициента поднятия Z, для элемента со значением 1 в том же самом местоположении, могут быть различные Pi,j при использовании различных коэффициентов поднятия Z. Чтобы упростить реализацию, обычно, m×n базовая матрица (base matrix) дополнительно определяется в системе. Местоположение каждого элемента в базовой матрице находится в однозначном соответствии с таковым для каждого элемента в базовом графе. Нулевой элемент в базовом графе находится в том же самом местоположении, что и нулевой элемент в базовой матрице, и представлен как -1. Ненулевой элемент со значением 1 в i-й строке и j-м столбце базовой матрицы находится в том же самом местоположении, что и ненулевой элемент в базовом графе, и может быть представлен как Pi,j, где Pi,j является положительным целым числом, большим или равным 0. В вариантах осуществления настоящей заявки, базовая матрица иногда упоминается как матрица сдвига матрицы базового графа.

[0097] 10b на фиг. 1 показывает базовую матрицу, соответствующую базовому графу 10a.

[0098] В общем, базовый граф или базовая матрица LDPC кода может дополнительно включать в себя p столбцов встроенных выколотых (built-in puncture) битов, и p может быть целым числом от 0 до 2. Столбцы участвуют в кодировании, но системный бит, соответствующий кодированию столбцов, не отправляется. В этом случае, кодовая скорость базовой матрицы LDPC кода удовлетворяет R=(n-m)/(n-p). Для базовой матрицы с четырьмя строками и 20 столбцами (4×20), если имеется два столбца встроенных выколотых битов, кодовая скорость равна (20-4)/(20-2)=8/9.

[0099] Размер базового графа LDPC кода, используемого в системе беспроводной связи, равен m×n, и базовый граф может включать в себя пять подматриц A, B, C, D и E. Вес матрицы определяется в соответствии с количеством ненулевых элементов. Вес строки (a row weight) является количеством ненулевых элементов, включенных в строку. Вес столбца (a column weight) является количеством ненулевых элементов, включенных в столбец. Как показано в 200 на фиг. 2,

подматрица A является матрицей с mA строками и nA столбцами, и размер подматрицы A может быть mA×nA. Каждый столбец соответствует Z системным битам в LDPC коде. Системный бит иногда упоминается как информационный бит.

[0100] Подматрица B является матрицей с mA строками и mA столбцами, размер подматрицы B может быть mA×mA, и каждый столбец соответствует Z проверочным битам в LDPC коде. Подматрица B включает в себя подматрицу Bʹ бидиагональной структуры и один столбец матрицы, вес столбца которого равен 3 (кратко упоминается как столбец с весом столбца, равным 3). Как показано в 20a на фиг. 2, столбец матрицы, у которого вес столбца равен 3, расположен перед подматрицей Bʹ. Подматрица B может дополнительно включать в себя столбец матрицы, у которого вес столбца равен 1 (кратко упоминается как столбец с единичным весом столбца). Как показано в 20b или 20c на фиг. 2, столбец с единичным весом столбца может быть расположен в первом столбце или последнем столбце подматрицы B, и ненулевой элемент в столбце с единичным весом столбца находится в последней строке подматрицы B, так что вес строки последней строки подматрицы B равен 1.

[0101] Обычно, матрица, которая генерируется на основе подматриц A и B, является матрицей ядра и может быть использована для поддержки кодирования с высокой кодовой скоростью.

[0102] Подматрица C является нулевой матрицей, и размер подматрицы C равен (mA×(n-(mA+nA)).

[0103] Подматрица E является единичной матрицей, и размер подматрицы E равен (m-mA)×(m-mA).

[0104] Размер подматрицы D равен (m-mA)(nA+mA), и подматрица D может обычно использоваться для генерации бита проверки низкой кодовой скорости.

[0105] Поскольку структуры подматриц B, C и E являются относительно определенными, структуры двух подматриц A и D являются одним из факторов, которые влияют на рабочие характеристики кодирования/декодирования LDPC кода.

[0106] Обычно, LDPC код определяется в соответствии с базовым графом и базовой матрицей. Верхний предел рабочих характеристик LDPC кода может быть определен с использованием метода эволюции плотности на базовом графе или базовой матрице, и минимальный уровень ошибок LDPC кода определяется в соответствии со значением сдвига в базовой матрице. Улучшение рабочих характеристик кодирования/декодирования и уменьшение минимального уровня ошибок является одной из целей определения базового графа и базовой матрицы. В системе беспроводной связи применяются гибкие и изменяемые длины кода. Кодовый блок может быть кодовым блоком с малой длиной блока, такой как 40 битов или 1280 битов, или может быть кодовым блоком с большой длиной блока, такой как 5000 битов или 8448 битов. Фиг. 3a, фиг. 3b и фиг. 3c являются, соответственно, примерами базовых графов и базовых матриц LDPC кода, которые получены в соответствии с методом эволюции плотности и могут удовлетворять KB=22 и требование к рабочим характеристикам кодового блока с длиной блока от 640 до 8448 битов. Если удалены с 16-го столбца по 21-й столбец, то есть только первые 16 столбцов взяты для подматрицы A, и соответственно, только первые 16 столбцов взяты для подматрицы D, матрица, составленная из первых 16 столбцов для подматрицы A, первых 16 столбцов для подматрицы D, подматрицы B, подматрицы C и подматрицы D, может удовлетворять KB=16 и требование к рабочим характеристикам кодового блока с длиной блока от 40 до 2560 битов. Фиг. 4a, фиг. 4b и фиг 4c являются, соответственно, примерами базовых графов и базовых матриц, которые соответствуют другому LDPC коду и матрице ядра LDPC кода и которые получены в соответствии с методом эволюции плотности и могут удовлетворять KB=10 и требование к рабочим характеристикам кодового блока с длиной блока от 40 до 2560 битов.

[0107] Фиг. 3a показывает пример базового графа 30a LDPC кода. Числа от 0 до 111 в самой верхней строке на этой фигуре представляют номера столбцов, и числа от 0 до 89 в крайнем левом столбце представляют номера строк.

[0108] Подматрица A соответствует системным битам, то есть информационным битам, и KB является количеством столбцов системных битов в базовом графе.

[0109] Матрица, составленная из элементов в 0-й строке по 4-ю строку и 0-м столбце по 21-й столбец в базовом графе 30a, может упоминаться как A0. Если KB=22, подматрица A является матрицей A0, то есть включает в себя все столбцы матрицы A0. Если KB=16, подматрица A включает в себя первые 16 столбцов матрицы A0.

[0110] Поэтому размер подматрицы A равен пяти строкам и 22 столбцам или пяти строкам и 16 столбцам.

[0111] Подматрица A и подматрица B составляют части матрицы ядра базового графа LDPC кода, то есть составляют матрицу с пятью строками и 27 столбцами или с пятью строками и 21 столбцом и могут быть использованы для кодирования с высокой кодовой скоростью.

[0112] Подматрица A может включать в себя два столбца встроенных выколотых битов. После выкалывания, кодовая скорость, которая может поддерживаться матрицей ядра с пятью строками и 27 столбцами, равна 22/(27-2)=0,88 и кодовая скорость, которая может поддерживаться матрицей ядра с пятью строками и 16 столбцами (с 0-го столбца по 15-й столбец и с 22-го столбца по 26-й столбец) равна 16/(21-2)=16/19.

[0113] Подматрица B соответствует битам проверки, имеет размер пяти строк и пяти столбцов и составлена из элементов в 0-й строке по 4-ю строку и в 22-м столбце по 26-й столбец в базовом графе 30a.

[0114] Подматрица B включает в себя один столбец с весом столбца, равным 3, то есть вес столбца 0-го столбца подматрицы B (22-го столбца матрицы ядра) равен 3. С 1-го по 4-й столбцы (с 23-го по 26-й столбцы матрицы ядра) и с 0-й по 4-ю строки подматрицы B имеют бидиагональную структуру.

[0115] В базовом графе 30a, матрица A0 включает в себя одну строку, вес которой равен 2, две строки, веса которых равны 12, и две строки, веса которых равны 21, и значения весов строк равны, соответственно, 21, 12, 2, 12 и 21. Строка, вес которой равен 2, может быть представлена как 2-я строка и с 0-го по 22-й столбцы матрицы ядра в базовом графе 30a. Строки, веса которых равны 12, могут быть отдельными строками, представленными как 1-я строка или 3-ья строка и с 0-го по 22-й столбец матрицы ядра в базовом графе 30a. Строки, веса которых равны 21, могут быть отдельными строками, представленными как 0-я строка или 4-я строка и с 0-го по 22-й столбцы матрицы ядра в базовом графе 30a. Порядок строк может быть взаимозаменяемым, и порядок столбцов может также быть взаимозаменяемым, и это не влияет на рабочие характеристики кодирования/декодирования.

[0116] Матрица ядра с пятью строками и 27 столбцами в базовом графе 30a использована в качестве примера. Матрица ядра включает в себя одну строку, вес которой равен 5, две строки, веса которых равны 14, и две строки, веса которых равны 23. то есть значения весов строк матрицы ядра, составленной из подматрицы A и подматрицы B, равны, соответственно, 23, 14, 5, 14 и 23. Следует отметить, что порядок строк матрицы ядра является взаимозаменяемым. Например, 0-я строка является взаимозаменяемой с 2-й строкой, и 1-я строка является взаимозаменяемой с 3-й строкой. Строка, вес которой равен 5, может быть представлена как 2-я строка и с 0-го по 26-й столбцы матрицы ядра в базовом графе 30a. Строки, веса которых равны 14, могут быть отдельными строками, представленными как 1-я строка или 3-ья строка и с 0-го по 26-й столбцы матрицы ядра в базовом графе 30a. Строки, веса которых равны 23, могут быть отдельными строками, представленными как 0-я строка или 4-я строка и с 0-го по 26-й столбцы матрицы ядра в базовом графе 30a. Порядок строк может быть взаимозаменяемым, и порядок столбцов может также быть взаимозаменяемым, и это не влияет на рабочие характеристики кодирования/декодирования.

[0117] В общем, для данного базового графа или базовой матрицы LDPC кода, несколько модификаций на элементах матрицы оказывают допустимое воздействие на рабочие характеристики. Для базового графа 30a, выполнено несколько модификаций, например, вес одной строки матрицы A0 сделан большим, чем 0, и меньшим, чем 5, веса двух строк сделаны большими, чем 9, и меньшими, чем 15, и веса двух строк сделаны большими, чем 19, и меньшими, чем 22, так что относительно малое влияние оказывается на рабочие характеристики.

[0118] Для поддержки различных длин блока, LDPC код должен поддерживать различные коэффициенты поднятия Z. Чтобы гарантировать рабочие характеристики LDPC кода для различных длин блока, базовые матрицы, соответствующие различным коэффициентам поднятия Z, могут быть соответственно использованы на основе различных коэффициентов поднятия Z.

[0119] Например, набор поддерживаемых коэффициентов поднятия составляет {8:1:16} υ {16:2:32} υ {32:4:64} υ {64:8:128} υ {128:16:256} υ {256:32:384}. {8:1:16} представляет, что набор коэффициентов поднятия Z соответствует от 8 до 16, и что интервал между соседними коэффициентами поднятия равен 1, например, 8, 9, 10, …, 15 и 16. {16:2:32} представляет, что набор коэффициентов поднятия Z соответствует от 16 до 32, и что интервал между соседними коэффициентами поднятия равен 2, например, 16, 18, 20, …, 30 и 32. По аналогии, {256:32:384} представляет, что набор коэффициентов поднятия Z соответствует от 256 до 384, и что интервал между соседними коэффициентами поднятия равен 32, например, 256, 288, 320,…, 352, 384 и т.п.

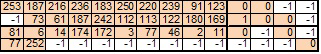

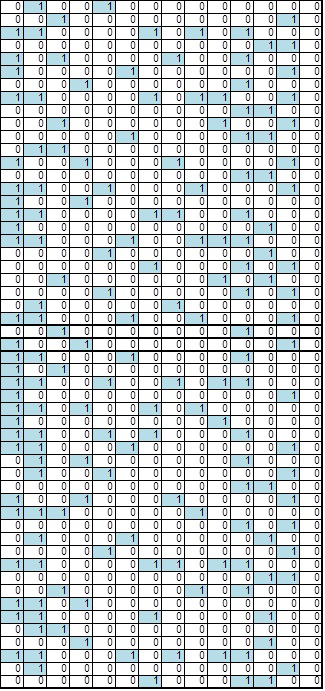

[0120] Фиг. 3b показывает пример множества базовых матриц матрицы ядра в базовом графе 30a. Базовые матрицы получены на основе матрицы ядра в базовом графе 30a и коэффициента поднятия Z. Ненулевой элемент в i-й строке и j-м столбце в базовом графе 30a является значением сдвига Pi,j в i-й строке и j-м столбце базовой матрицы. Нулевой элемент в базовом графе 30a представлен как -1 или нуль в матрице сдвига. Аналогично, строки базовой матрицы могут быть взаимозаменяемыми, и столбцы могут также быть взаимозаменяемыми.

[0121] Базовая матрица матрицы ядра включает в себя матрицу сдвига подматрицы A и матрицу сдвига подматрицы B.

[0122] Коэффициент поднятия может быть представлен как Z=a⋅2n, где a является любым целым числом от 8 до 15, и используется базовая матрица, соответствующая значению а. Набор поддерживаемых коэффициентов поднятия может быть представлен как {8×2n:2n:15*2n}, где n является целым числом, и значение равно от 0 до 5.

[0123] Матрица сдвига подматрицы B является той же самой для всех коэффициентов поднятия, как показано в 0-й строке по 4-ю строку и 22-м столбце по 26-й столбец базовой матрицы 30b-1 на фиг. 3b.

[0124] Матрица сдвига подматрицы A может быть матрицей сдвига матрицы A0 в соответствии с различными KB. Например, в базовой матрице 30b-1, матрица сдвига матрицы A0 может быть от 0-й строки по 4-ю строку и от 0-го столбца по 22-й столбец базовой матрицы 30b-1. В этом случае, когда KB=22, матрица сдвига подматрицы A является матрицей сдвига матрицы A0; когда KB=16, матрица сдвига подматрицы A включает в себя первые 16 столбцов матрицы сдвига матрицы A0, то есть от 0-й строки по 4-ю строку и от 0-го столбца по 16-й столбец базовой матрицы 30b-1.

[0125] Если значение а равно 8, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-1 на фиг. 3b.

[0126] Если значение а равно 9, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-2 на фиг. 3b.

[0127] Если значение а равно 10, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-3 на фиг. 3b.

[0128] Если значение а равно 11, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-4 на фиг. 3b.

[0129] Если значение а равно 12, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-5 на фиг. 3b.

[0130] Если значение а равно 13, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-6 на фиг. 3b.

[0131] Если значение а равно 14, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-7 на фиг. 3b.

[0132] Если значение а равно 15, матрица сдвига матрицы A0 может быть представлена как 0-я строка по 4-ю строку и 0-й столбец по 22-й столбец базовой матрицы 30b-8 на фиг. 3b.

[0133] Для получения гибких кодовых скоростей, подматрица C, подматрица D и подматрица E в соответствующих размерах могут добавляться, основываясь на матрице ядра, чтобы получать различные кодовые скорости. Подматрица C является нулевой матрицей, подматрица является единичной матрицей, размеры подматриц определяются, главным образом, в соответствии с кодовой скоростью, и структуры являются относительно фиксированными. Поэтому, частями, которые влияют на рабочие характеристики кодирования/декодирования, являются, главным образом, матрица ядра и подматрица D. строка и столбец добавляются, основываясь на матрице ядра, чтобы формировать соответствующие части C, D и E, так что могут быть получены различные кодовые скорости.

[0134] Количество столбцов подматрицы D является суммой количеств столбцов подматриц A и B, и количество строк подматрицы D, главным образом, связано с кодовой скоростью. Базовый граф 30a и KB=22 использованы в качестве примера. В этом случае, соответствующее количество столбцов mD подматрицы D равно (nA+mA)=27 столбцов. Если кодовая скорость, поддерживаемая LDPC кодом, равна Rm, размер базового графа или базовой матрицы LDPC кода равен m×n, где n=nA/Rm+p и m=n-nA= nA/Rm+p-nA. Если самая низкая кодовая скорость Rm=1/5, количество встроенных выколотых столбцов p=2, и базовый граф 30a используется в качестве примера, n=112, m=90, и максимальное значение количества строк mD подматрицы D может быть m-mA=90-5=85, то есть 0≤mD≤85.

[0135] Количество столбцов подматрицы D является тем же самым, что и количество столбцов подматрицы A, то есть когда подматрица A имеет 22 столбца, подматрица D также имеет соответствующие 22 столбца, и когда подматрица A имеет 16 столбцов, подматрица D также имеет соответствующие 16 столбцов.

[0136] Для удобства описания, может быть определена матрица F, размер которой соответствует 85 строкам и 27 столбцам. В этом случае, подматрица D может включать в себя mD строк и 27 столбцов или mD строк и 21 столбец матрицы F и составлять базовый граф LDPC кода вместе с подматрицами A и B и подматрицами C и E в соответствующих размерах. В базовом графе 30a, когда mD=85 и подматрица A имеет 27 столбцов, размер подматрицы D составляет, соответственно, 85 строк и 27 столбцов, то есть подматрица D является матрицей F, и соответствующая кодовая скорость, поддерживаемая LDPC кодом, равна 22/110=1/5. Можно видеть, что матрица, составленная 5-й строкой по 89-ю строку и 0-ым столбцом по 26-й столбец в базовом графе 30a, является матрицей F.

[0137] Весами строк матрицы F, показанной в графе 30a, являются последовательно 5, 7, 7, 7, 6, 6, 6, 6, 6, 5, 6, 5, 4, 5, 5, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 3, 4, 3, 5, 4, 3, 4, 3, 3, 3, 4, 3, 3, 4, 4, 4, 3, 3, 4, 3, 3, 3, 3, 2, 2, 3, 3, 3, 3, 3, 3, 3, 2, 3, 2, 3, 3, 3, 3, 3, 2, 3, 3, 3, 2, 3, 3, 3, 4, 3, 3, 2, 3, 2, 3, 3, 3, 4, 3, 3.

[0138] Поскольку подматрица E является единичной матрицей, вес каждой строки в базовом графе 30a равен весу строки каждой строки матрицы F плюс 1.

[0139] Следует отметить, что, в базовом графе и базовой матрице LDPC кода, строки могут быть взаимозаменяемыми и столбцы могут также быть взаимозаменяемыми.

[0140] Для подматрицы D при каждой кодовой скорости, от 1 до 2 ненулевых элементов или от 1 до 2 нулевых элементов в каждой строке могут быть модифицированы, не оказывая влияния на рабочие характеристики подматрицы D.

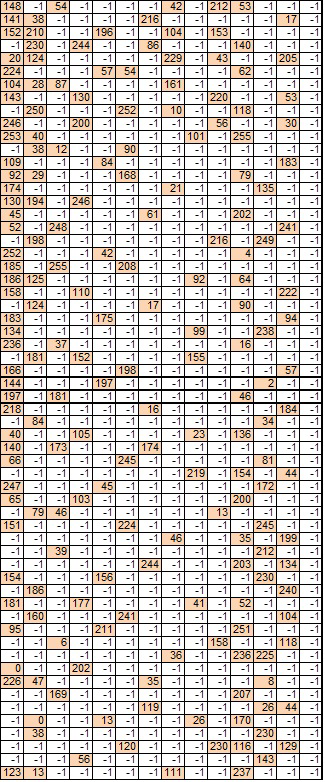

[0141] Базовая матрица 30c, показанная на фиг. 3c, является примером базовой матрицы базового графа 30a. Ненулевой элемент в i-й строке и j-м столбце в базовом графе 30a находится в том же самом местоположении, что и ненулевой элемент в базовой матрице 30c, и значение является значением сдвига Pi,j. Подматрица D включает в себя mD строк матрицы сдвига матрицы F. Для базовой матрицы 30c, показанной на фиг. 3c, mD=85. Значение mD может быть выбрано в соответствии с различными кодовыми скоростями, и 22 столбца или 16 столбцов выбираются в соответствии с KB. Матрица сдвига, соответствующая подматрице D, является матрицей сдвига матрицы F. Здесь, матрица сдвига матрицы F является матрицей, полученной путем замены ненулевого элемента в i-й строке и j-м столбце матрицы F значением сдвига Pi,j, и нулевой элемент представлен как -1 или нуль в матрице сдвига.

[0142] Значение а может быть определено на основе Z, и может быть использована базовая матрица, соответствующая значению a.

[0143] Если значение а равно 8, матрица сдвига матрицы F может быть представлена как 3c-1.

[0144] Если значение а равно 9, матрица сдвига матрицы F может быть представлена как 3c-2.

[0145] Если значение а равно 10, матрица сдвига матрицы F может быть представлена как 3c-3.

[0146] Если значение а равно 11, матрица сдвига матрицы F может быть представлена как 3c-4.

[0147] Если значение а равно 12, матрица сдвига матрицы F может быть представлена как 3c-5.

[0148] Если значение а равно 13, матрица сдвига матрицы F может быть представлена как 3c-6.

[0149] Если значение а равно 14, матрица сдвига матрицы F может быть представлена как 3c-7.

[0150] Если значение а равно 15, матрица сдвига матрицы F может быть представлена как 3c-8.

[0151] Когда подматрица D базовой матрицы 30c заменяется mD строками каждой из вышеуказанных матриц сдвига матрицы F, то могут быть получены базовые матрицы, которые имеют различные кодовые скорости и являются соответствующими базовому графу 30a. Если mD=85 и KB=22, часть матрицы, составленная из 5-й строки по 89-ю строку и 0-го столбца по 26-й столбец базовой матрицы 30c, заменяется каждой матрицей сдвига матрицы F, и может быть получена каждая базовая матрица, размер которой соответствует 90 строкам и 112 столбцам, и которая является соответствующей базовому графу 30a. В этом случае, кодовая скорость равна 1/5. Если mD=71 и KB=16, часть матрицы, составленная из 5-й строки по 75-ю строку и 0-го столбца по 16-й столбец базовой матрицы 30c, заменяется первыми 16 столбцами и первыми 71 строками каждой матрицы сдвига матрицы F, 0-я по 4-ю строки и 0-й по 15-й столбцы подматрицы базовой матрицы 30c выбираются в качестве матрицы сдвига подматрицы A, и затем матрица сдвига подматрицы A объединяется с матрицей сдвига подматрицы B, матрицей сдвига, которая относится к подматрице C и которая имеет пять строк и 71 столбец, и матрицей сдвига, которая относится к подматрице E и которая имеет 71 строку и 71 столбец, так что может быть получена каждая базовая матрица, которая соответствует базовому графу и у которой кодовая скорость равна 1/5.

[0152] Фиг. 4a показывает пример базового графа 40a LDPC кода. Числа от 0 до 126 в самой верхней строке на фигуре представляют номера столбцов, и числа от 0 до 116 в крайнем левом столбце представляют номера строк.

[0153] Подматрица A соответствует системным битам, имеет размер четырех строк и 10 столбцов и составлена из элементов 0-й строки по 3-ю строку и 0-го столбца по 9-й столбец в базовом графе 40a.

[0154] Подматрица B соответствует битам проверки, имеет размер четырех строк и четырех столбцов и составлена из элементов 0-й строки по 3-ю строку и 10-го столбца по 13-й столбец в базовом графе 40a.

[0155] Подматрица A и подматрица B составляют часть матрицы ядра базового графа 40a LDPC кода, то есть составляют матрицу с четырьмя строками и 14 столбцами и могут быть использованы для кодирования высокой кодовой скорости.

[0156] Подматрица A может включать в себя два столбца встроенных выколотых битов. После выкалывания, кодовая скорость, которая может поддерживаться матрицей ядра, равна 10/(14-2)=5/6.

[0157] Подматрица B включает в себя один столбец с весом столбца, равным 3, то есть вес столбца 0-го столбца подматрицы B (10-го столбца матрицы ядра) равен 3, и с 1-го по 2-й столбцы (с 11-го по 12-й столбец матрицы ядра) и с 0-й по 3-ю строку подматрицы B являются бидиагональной структурой. Подматрица B включает в себя один столбец с единичным весом столбца, и в подматрице B, как вес строки последней строки (3-й строки), так и вес столбца последнего столбца (3-го столбца подматрицы B, 13-го столбца матрицы ядра) равны 1.

[0158] Матрица ядра в базовом графе 40a включает в себя одну строку, вес которой равен 3, и три строки, веса которых равны 12. То есть значения весов строк матрицы ядра, составленной из подматрицы A и подматрицы B, равны соответственно 12, 12, 12 и 3. Следует отметить, что порядок строк матрицы ядра является взаимозаменяемым. Например, 0-я строка является взаимозаменяемой с 2-й строкой, и 1-я строка является взаимозаменяемой с 3-й строкой. Строка, вес которой равен 3, может быть представлена как 3-ья строка и с 0-го по 13-й столбцы матрицы ядра в базовом графе 40a. Строки, веса которых равны 12, могут быть отдельно 0-й строкой, 1-й строкой или 2-й строкой и с 0-го по 13-й столбцы матрицы ядра в базовом графе 40a. Порядок строк может быть взаимозаменяемым, и порядок столбцов может также быть взаимозаменяемым, и это не влияет на рабочие характеристики кодирования/декодирования.

[0159] В общем, для данного базового графа или базовой матрицы LDPC кода, несколько модификаций на элементах матрицы оказывают допустимое влияние на рабочие характеристики. Для матрицы ядра в базовом графе 40a выполнено несколько модификаций, например, вес одной строки матрицы ядра сделан большим или равным 1 и меньшим или равным 5, и веса оставшихся трех строк, каждый, больше или равны 10 и меньше или равны 13, так что относительно малое влияние оказывается на рабочие характеристики.

[0160] Для поддержки различных длин блока, LDPC код требует различных коэффициентов поднятия Z. Например, коэффициент поднятия Z может включать в себя один или несколько в наборе коэффициентов поднятия. Набор поддерживаемых коэффициентов поднятия, соответствующий {8:1:16} υ {16:2:32} υ {32:4:64} υ {64:8:128} υ {128:16:256} υ {256:32:384}, используется в качестве примера.

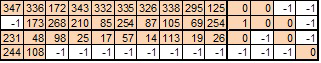

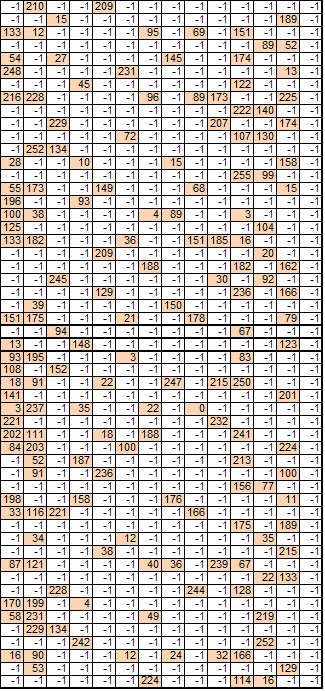

[0161] Чтобы гарантировать рабочие характеристики LDPC кода для различных длин блока, базовые матрицы, соответствующие различным коэффициентам поднятия Z, могут быть соответственно использованы на основе различных коэффициентов поднятия Z. Фиг. 4b показывает пример множества базовых матриц матрицы ядра в базовом графе 40a. Базовые матрицы получаются на основе матрицы ядра в базовом графе 40a и коэффициента поднятия Z. Ненулевой элемент в i-й строке и j-м столбце в базовом графе 40a является значением сдвига в i-й строке и j-м столбце базовой матрицы. Нулевой элемент в базовом графе 40a представлен как -1 или нуль в матрице сдвига. Аналогичным образом, строки базовой матрицы могут быть взаимозаменяемыми, и столбцы могут также быть взаимозаменяемыми.

[0162] Коэффициент поднятия может быть представлена как Z=a⋅2n, где a является любым целым числом от 8 до 15, и используется базовая матрица, соответствующая значению а.

[0163] Если значение а равно 8, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-1 на фиг. 4b.

[0164] Если значение а равно 9, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-2 на фиг. 4b.

[0165] Если значение а равно 10, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-3 на фиг. 4b.

[0166] Если значение а равно 11, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-4 на фиг. 4b.

[0167] Если значение а равно 12, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-5 на фиг. 4b.

[0168] Если значение а равно 13, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-6 на фиг. 4b.

[0169] Если значение а равно 14, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-7 на фиг. 4b.

[0170] Если значение а равно 15, часть, которая находится в базовой матрице в базовом графе 40a и соответствует подматрице A и подматрице B, может быть представлена как базовая матрица 40b-8 на фиг. 4b.

[0171] Для получения гибких кодовых скоростей, подматрица C, подматрица D и подматрица E в соответствующих размерах могут добавляться, основываясь на матрице ядра, чтобы получать различные кодовые скорости. Подматрица C является нулевой матрицей, подматрица является единичной матрицей, размеры подматриц, главным образом, определяются в соответствии с кодовой скоростью, и структуры являются относительно фиксированными. Поэтому части, которые влияют на рабочие характеристики кодирования/декодирования, являются, главным образом, матрицей ядра и подматрицей D. Строка и столбец добавляются, основываясь на матрице ядра, чтобы сформировать соответствующие части C, D и E, так что могут быть получены различные кодовые скорости.

[0172] Количество столбцов подматрицы D является суммой количеств столбцов подматриц A и B, количество строк подматрицы D, главным образом, связано с кодовой скоростью. Базовый граф 40a используется в качестве примера. В этом случае, соответствующее количество столбцов mD подматрицы D равно (nA+mA)=14 столбцов. Если кодовая скорость, поддерживаемая LDPC кодом, равна Rm, размер базового графа или базовой матрицы LDPC кода равен m×n, где n=nA/Rm+p и m=n-nA=nA/Rm+p-nA. Если самая низкая кодовая скорость Rm=0,08, количество встроенных выколотых столбцов p=2, и базовый граф 40a используется в качестве примера, n=127, m=117, и максимальное значение количества строк mD подматрицы D может быть m-mA=117-4=113, то есть 0≤mD≤113.

[0173] Для удобства описания, может быть определена матрица F, размер которой составляет 113 строк и 14 столбцов. В этом случае, подматрица D может включать в себя mD строк матрицы F и составлять базовый граф LDPC кода с кодовой скоростью 10/(12+mD) вместе с подматрицами A и B и подматрицами C и E в соответствующих размерах. В базовом графе 40a, когда mD=113, размер подматрицы D соответственно составляет 113 строк и 14 столбцов, то есть подматрица D является матрицей F, и соответствующая кодовая скорость, поддерживаемая LDPC кодом, равна 10/125=0,08. Можно видеть, что матрица, составленная из 4-й строки по 116-ю строку и 0-го столбца по 13-й столбец в базовом графе 40a, является матрицей F.

[0174] Весами строк матрицы F, показанной в графе 40a, являются последовательно 5, 4, 5, 4, 5, 4, 4, 4, 4, 4, 4, 3, 3, 4, 3, 3, 3, 3, 3, 3, 3, 4, 3, 3, 3, 3, 3, 3, 3, 3, 3, 3, 2, 4, 3, 3, 3, 3, 3, 3, 3, 3, 2, 3, 3, 2, 4, 3, 3, 3, 3, 2, 4, 2, 3, 4, 2, 4, 2, 4, 2, 2, 5, 2, 4, 3, 2, 6, 2, 3, 3, 2, 4, 2, 5, 2, 5, 2, 6, 2, 3, 3, 3, 2, 5, 2, 3, 4, 2, 6, 2, 5, 2, 5, 4, 3, 3, 2, 4, 4, 2, 3, 2, 6, 2, 3, 3, 4, 2, 2, 6, 2, 3.

[0175] Поскольку подматрица E является единичной матрицей, вес каждой строки в базовом графе 40a равен весу строки каждой строки матрицы F плюс 1.

[0176] Если mD=13, размер подматрицы D в базовом графе LDPC кода соответствует 13 строкам и 14 столбцам, и подматрица D может быть составлена из матрицы с 0-й по 12-ю строками, то есть с 4-й строки по 16-ю строку в базовом графе 40a и с 0-го столбца по 13-й столбец матрицы F в базовом графе 40a, и соответствующая кодовая скорость, поддерживаемая LDPC кодом, равна 10/25=0,4. То есть при этой кодовой скорости, базовый граф LDPC кода соответствует части матрицы, составленной из 0-й строки по 12-ю строку и 0-го столбца по 13-й столбец в базовом графе 40a. Подматрица E является единичной матрицей с 13 строками и 13 столбцами, и подматрица C является нулевой матрицей с четырьмя строками и 13 столбцами.

[0177] Если mD=18, размер подматрицы D в базовом графе LDPC кода соответствует 18 строкам и 14 столбцам, и подматрица D может быть составлена из матрицы с 0-й по 17-ю строками, то есть с 4-й строки по 21-ю строку в базовом графе 40a и 0-ым столбцом по 13-й столбец матрицы F в базовом графе 40a, и соответствующая кодовая скорость, поддерживаемая LDPC кодом, равна 10/30=1/3. То есть при этой кодовой скорости, базовый граф LDPC кода соответствует части матрицы, составленной из 0-й строки по 21-ю строку и 0-го столбца по 31-й столбец в базовом графе 40a. Подматрица E является единичной матрицей с 18 строками и 18 столбцами, и подматрица C является нулевой матрицей с четырьмя строками и 18 столбцами.

[0178] Остальное может быть выведено по аналогии и не описывается отдельно.

[0179] Следует отметить, что, в базовом графе и базовой матрице LDPC кода, строки могут быть взаимозаменяемыми, и столбцы могут также быть взаимозаменяемыми.

[0180] Для подматрицы D в каждой кодовой скорости, от 1 до 2 ненулевых элементов или от 1 до 2 нулевых элементов в каждой строке могут быть модифицированы, не оказывая влияния на рабочие характеристики подматрицы D.

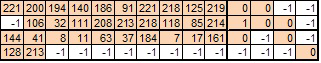

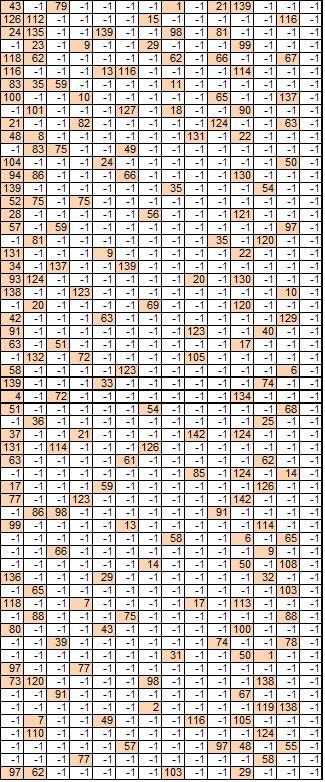

[0181] Как показано на фиг. 4c, базовая матрица 40c является примером базовой матрицы в базовом графе 40a. Ненулевой элемент в i-й строке и j-м столбце в базовом графе 40a находится в том же самом местоположении, что и ненулевой элемент в базовой матрице 30c, и значение равно значению сдвига Pi,j. Подматрица D включает в себя mD строк матрицы сдвига матрицы F. Для базовой матрицы 40c, показанной на фиг. 4c, mD=41, и значение mD может быть выбрано в соответствии с различными кодовыми скоростями. Матрица сдвига, соответствующая подматрице D, является матрицей сдвига матрицы F. Здесь, матрица сдвига матрицы F является матрицей, полученной путем замены ненулевого элемента в i-й строке и j-м столбце матрицы F значением сдвига Pi,j, и нулевой элемент представлен как -1 или нуль в матрице сдвига.

[0182] Если значение а равно 8, матрица сдвига матрицы F может быть представлена как 4c-1.

[0183] Если значение а равно 9, матрица сдвига матрицы F может быть представлена как 4c-2.

[0184] Если значение а равно 10, матрица сдвига матрицы F может быть представлена как 4c-3.

[0185] Если значение а равно 11, матрица сдвига матрицы F может быть представлена как 4c-4.

[0186] Если значение а равно 12, матрица сдвига матрицы F может быть представлена как 4c-5.

[0187] Если значение а равно 13, матрица сдвига матрицы F может быть представлена как 4c-6.

[0188] Если значение а равно 14, матрица сдвига матрицы F может быть представлена как 4c-7.

[0189] Если значение а равно 15, матрица сдвига матрицы F может быть представлена как 4c-8.

[0190] Когда подматрица D в базовой матрице 40c заменяется mD строками каждой из вышеописанных матриц сдвига матрицы F, могут быть получены базовые матрицы, которые имеют различные кодовые скорости и которые соответствуют базовому графу 40a. Если mD=113, часть матрицы, составленная из 4-й строки по 116-ю строку и 0-го столбца по 13-й столбец базовой матрицы 40c, заменяется каждой матрицей сдвига матрицы F, и может быть получена каждая базовая матрица, которая соответствует базовому графу 40a и размер которой соответствует 117 строкам и 126 столбцам. В этом случае, кодовая скорость равна 0.08.

[0191] Способ кодирования, обеспеченный в варианте осуществления настоящего изобретения, включает в себя: кодирование информационной битовой последовательности с использованием LDPC матрицы. Базовый граф LDPC матрицы может быть любым базовым графом из вышеописанных примеров, и базовая матрица HB LDPC матрицы может быть любой базовой матрицей из вышеописанных примеров.

[0192] Дополнительно, способ дополнительно включает в себя: определение коэффициента поднятия Z.

[0193] Например, значение коэффициента поднятия Z может быть определено в соответствии с длиной K информационной битовой последовательности. Информационная битовая последовательность иногда упоминается как кодовый блок (code block) и может быть получена путем выполнения разделения на кодовые блоки на транспортном блоке. Если длина информационной битовой последовательности равна K, минимальное значение, которое удовлетворяет 22×Z≥K, может быть определено во множестве коэффициентов поднятия, определенных в системе. Например, если K=3800 и коэффициенты поднятия, определенные в системе, включают в себя 16, 18, 20, 22, 24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352 и 384, может быть определено, что Z равен 176. Следует отметить, что это является только примером и не используется в качестве ограничения.

[0194] В другом примере, набор поддерживаемых коэффициентов поднятия соответствует {8:1:16} υ {16:2:32} υ {32:4:64} υ {64:8:128} υ {128:16:256} υ {256:32:384}, и исходный коэффициент поднятия Zorig может быть получен в соответствии с Zorig=⎡K/KB⎤, где ⎡ ⎤ указывает округление, и K является длиной информационной битовой последовательности. Восемь минимальных значений, больших или равных Zorig, выбираются из набора поддерживаемых коэффициентов поднятия и обозначаются как Z0, Z1,…, Z7 в восходящем порядке. ΔZ выбирается из набора {Z0-Zorig, Z1-Zorig,…, Z7-Zorig} в соответствии со значением ΔZ index.

[0195] Когда ΔZ index=1, выбирается ΔZ=Zi-Zorig, и фактически используемым коэффициентом поднятия является Z=Zorig+ΔZ.

[0196] Для базового графа или базовой матрицы, используемых на фиг. 3a, фиг. 3b и фиг. 3c, если KB=22, Z может быть определен в соответствии с Таблицей 1. Параметры в каждом столбце в параметрах вычисления могут быть получены с помощью справочной таблицы или могут быть вычислены в соответствии с Zorig и ΔZ index.

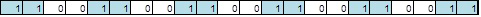

Таблица 1

(3 бита)

[0197] Для базового графа или базовой матрицы, используемых на фиг. 3a, фиг. 3b и фиг. 3c, если KB=16, Z может быть определен в соответствии с Таблицей 2. Параметры в каждом столбце в параметрах вычисления могут быть получены с помощью справочной таблицы или могут быть вычислены в соответствии с Zorig и ΔZ index.

Таблица 2

(3 бита)

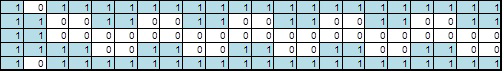

[0198] Для базового графа или базовой матрицы, используемых на фиг. 4a, фиг. 4b и фиг. 4c, например, если KB=10, Z может быть определен в соответствии с Таблицей 3. Параметры в каждом столбце в параметрах вычисления могут быть получены с помощью справочной таблицы или могут быть вычислены в соответствии с Zorig и ΔZ index.

Таблица 3

[0199] Кодирование информационной битовой последовательности с использованием LDPC матрицы может быть кодированием информационной битовой последовательности с использованием LDPC матрицы, соответствующей коэффициенту поднятия Z.

[0200] Базовая матрица HB LDPC матрицы может быть любой базовой матрицей, проиллюстрированной в вышеуказанных вариантах осуществления, и базовый граф LDPC матрицы включает в себя по меньшей мере подматрицу A и подматрицу B и может дополнительно включать в себя подматрицу C, подматрицу D и подматрицу E. В отношении каждой части, можно сослаться на описания для приведенных выше вариантов осуществления. Детали здесь не описываются.

[0201] Базовая матрица HB LDPC кода может быть сохранена в памяти, выводится LDPC матрица, соответствующая коэффициенту поднятия Z, и информационная битовая последовательность может кодироваться.

[0202] В другой возможной реализации, поскольку имеется множество базовых матриц HB LDPC кода, относительно большое пространство памяти заполняется, когда базовые матрицы сохраняются в соответствии со структурой матрицы. Альтернативно, базовый граф LDPC кода может быть сохранен в памяти, значения сдвигов ненулевых элементов в каждой базовой матрице сохраняются от строки к строке или от столбца к столбцу, и затем получается LDPC матрица в соответствии с базовым графом и значениями сдвигов базовой матрицы, соответствующей коэффициенту поднятия Z.

[0203] Следует отметить, что это только пример и не используется в качестве ограничения.

[0204] Значение a может быть получено в соответствии с коэффициентом поднятия Z, и информационная битовая последовательность кодируется с использованием каждой базовой матрицы, соответствующей значению a в вышеописанных вариантах осуществления. Например, значение a может быть вычислено в соответствии с Z=a⋅2n, или соответствующее значение a может быть найдено на основе соответствий в таблицах 1-3.

[0205] Когда информационная битовая последовательность кодируется, базовая матрица HB может быть расширена в соответствии с Z, чтобы получить кодированную LDPC матрицу H. Для каждого ненулевого элемента Pi,j в базовой матрице HB, определяется циркулянтная матрица перестановок hi,j размера Z×Z, где hi,j является циркулянтной матрицей перестановок, полученной путем выполнения циклических сдвигов Pi,j над единичной матрицей. Ненулевой элемент Pi,j заменяется на hi,j, и нулевой элемент в базовой матрице HB заменяется нулевой матрицей размера Z×Z, чтобы получить матрицу Н проверки четности.

[0206] В системе связи, LDPC код получается после того, как кодирование выполняется с использованием вышеописанного способа. После получения LDPC кода, согласование скорости может дополнительно выполняться над LDPC кодом, LDPC код, который подвергается согласованию скорости, перемежается в соответствии с решением перемежения, перемеженный LDPC код модулируется в соответствии со схемой модуляции, чтобы получить битовую последовательность B, и битовая последовательность B отправляется.

[0207] Способ декодирования, обеспеченный в другом варианте осуществления настоящего изобретения, включает в себя: декодирование принятого сигнала с использованием LDPC матрицы. Базовый граф LDPC матрицы может быть любым базовым графом из вышеописанных примеров, и базовая матрица HB LDPC матрицы может быть любой базовой матрицей из вышеописанных примеров.

[0208] Кроме того, способ дополнительно включает в себя: определение коэффициента поднятия Z. Устройство связи на приемной стороне может принимать сигналы, включающие в себя сигнал, кодированный на основе LDPC, получать мягкое значение LDPC кода в нем и определять соответствующий коэффициент поднятия Z.

[0209] Декодирование принятого сигнала с использованием LDPC матрицы может представлять собой декодирование мягкого значения LDPC кода с использованием LDPC матрицы, соответствующей коэффициенту поднятия Z.

[0210] Базовая матрица HB LDPC матрицы может быть любой базовой матрицей, проиллюстрированной в вышеописанных вариантах осуществления, и базовый граф LDPC матрицы включает в себя по меньшей мере подматрицу A и подматрицу B и может дополнительно включать в себя подматрицу C, подматрицу D и подматрицу E. В отношении каждой части, можно сослаться на описания приведенных выше вариантов осуществления. Детали здесь не описываются.

[0211] Базовая матрица HB LDPC кода может быть сохранена в памяти, и выводится LDPC матрица, соответствующая коэффициенту поднятия Z, и мягкое значение LDPC кода может быть декодировано.

[0212] В другой возможной реализации, поскольку имеется множество базовых матриц LDPC кода, относительно большое пространство памяти заполняется, когда базовые матрицы сохраняются в соответствии со структурой матрицы. Альтернативно, базовый граф LDPC кода может быть сохранен в памяти, значения сдвигов ненулевых элементов в каждой базовой матрицей сохраняются, и затем получается LDPC матрица в соответствии с базовым графом и значениями сдвигов базовой матрицы, соответствующей коэффициенту поднятия Z.

[0213] Следует отметить, что это является только примером и не используется в качестве ограничения.

[0214] Декодирование является процессом, обратным кодированию. Базовая матрица HB, используемая при декодировании, имеет тот же самый признак, что и базовая матрица в варианте осуществления способа кодирования. В отношении получения LDPC матрицы H путем расширения базовой матрицы HB, также можно сослаться на вариант осуществления способа кодирования.

[0215] В системе связи, перед упомянутым способом, способ может дополнительно включать в себя: прием сигналов, включающих в себя сигнал, кодированный на основе LDPC, демодуляцию сигнала и выполнение обращенного перемежения и обращенного согласования скорости, чтобы получить мягкое значение LDPC кода.

[0216] Фиг. 5 является структурной схемой устройства 500 обработки информации. Устройство 500 может также упоминаться как устройство кодирования. Устройство 500 может быть сконфигурировано, чтобы осуществлять способ кодирования. В отношении деталей, можно сослаться на описание варианта осуществления способа. Детали здесь не описываются.

[0217] Дополнительно, устройство 500 может включать в себя блок 501 определения и блок 502 обработки.

[0218] Блок 501 определения сконфигурирован, чтобы определять коэффициент подъема Z для кодирования информационной битовой последовательности.

[0219] Блок 502 обработки сконфигурирован, чтобы кодировать информационную битовую последовательность с использованием LDPC матрицы, соответствующей коэффициенту поднятия Z.

[0220] Здесь можно сослаться на описание варианта осуществления способа. Детали дополнительно не описываются.

[0221] Фиг. 6 является структурной схемой устройства 600 обработки информации. Устройство 600 может также упоминаться как устройство декодирования. Устройство 600 может быть сконфигурировано, чтобы осуществлять способ кодирования. Здесь можно сослаться на описание варианта осуществления способа. Детали дополнительно не описываются.

[0222] Дополнительно, устройство 600 может включать в себя блок 601 получения и блок 602 обработки.

[0223] Блок 601 получения сконфигурирован, чтобы получать мягкое значение LDPC кода и коэффициент поднятия Z.

[0224] Блок обработки 602 сконфигурирован, чтобы декодировать мягкое значение LDPC кода на основе базовой матрицы HB, соответствующей коэффициенту поднятия Z, чтобы получить информационную битовую последовательность.

[0225] Здесь можно сослаться на описание варианта осуществления способа. Детали дополнительно не описываются.

[0226] Фиг. 7 является структурной схемой устройства связи. Устройство связи может применяться в системе связи. Устройство 700 связи может включать в себя кодер 701 и приемопередатчик 702. Кодер 701 может также упоминаться как блок кодирования, схема кодирования и т.п., может, главным образом, быть сконфигурирован, чтобы кодировать информационные данные, и может включать в себя, например, устройство 500 согласно фиг. 5. Приемопередатчик 702 может также упоминаться как приемопередающий блок, приемопередатчик, приемопередающая схема и т.п. и может, главным образом, быть сконфигурирован, чтобы принимать и отправлять радиочастотный сигнал, например, чтобы отправлять сигнал, соответствующий кодированным информационным данным, такой как модулированный LDPC код. Устройство связи 700 может дополнительно включать в себя другой компонент, такой как компонент, сконфигурированный, чтобы генерировать CRC транспортного блока, компонент, используемый для разделения на кодовые блоки и проверки CRC, перемежитель или модулятор.

[0227] Следует отметить, что устройство 700 связи может включать в себя один или несколько блоков памяти и один или несколько процессоров. Память хранит инструкцию. Процессор связан с памятью, чтобы активировать инструкцию в памяти для выполнения этапов, описанных в варианте осуществления способа. Память может дополнительно включать в себя другие инструкции, так что процессор активирует и выполняет функции других частей устройства 700 связи, такие как разделение на кодовые блоки и проверка CRC, перемежение или модуляция.

[0228] Фиг. 8 является структурной схемой устройства связи. Устройство связи может применяться в системе связи. Устройство 800 связи может включать в себя декодер 801 и приемопередатчик 802. Декодер 801 может также упоминаться как блок декодирования или схема декодирования, может быть сконфигурировано, чтобы декодировать принятый сигнал и может включать в себя, например, устройство 600 согласно фиг. 6. Приемопередатчик 802 может также упоминаться как приемопередающий блок, приемопередатчик, приемопередающая схема и т.п. и может быть сконфигурирован, чтобы принимать и передавать радиочастотный сигнал, например, чтобы принимать сигналы, включающие в себя сигнал, кодированный на основе LDPC. Устройство 800 связи может дополнительно включать в себя другой компонент, такой как компонент, используемый для проверки CRC транспортного блока, компонент, используемый для объединения кодовых блоков, обращенный перемежитель или демодулятор.

[0229] Следует отметить, что устройство 800 связи может включать в себя один или несколько блоков памяти и один или несколько процессоров. Память хранит инструкцию. Процессор связан с памятью, чтобы активировать инструкцию в памяти для выполнения этапов, описанных в варианте осуществления способа. Память может дополнительно включать в себя другие инструкции, так что процессор активирует и выполняет функции других частей устройства 800 связи, такие как объединение кодовых блоков, обращенное перемежение или демодуляция.

[0230] Специалистам в данной области техники может быть понятно, что различные иллюстративные логические блоки (illustrative logic block) и этапы (step), которые перечислены в вариантах осуществления настоящего изобретения, могут быть реализованы с использованием электронных аппаратных средств, компьютерного программного обеспечения или их комбинации. То, реализуются ли функции с использованием аппаратных средств или программного обеспечения, зависит от конкретных приложений и ограничений проектирования системы в целом. Специалисты в данной области техники могут использовать различные способы, чтобы реализовать описанные функции для каждого конкретного приложения, но не должно считаться, что такая реализация выходит за пределы объема защиты вариантов осуществления настоящего изобретения.

[0231] Различные иллюстративные логические блоки и схемы, описанные в вариантах осуществления настоящего изобретения, могут реализовывать или приводить в действие описанные функции с использованием процессора общего назначения, цифрового сигнального процессора, специализированной интегральной схемы (ASIC), программируемой вентильной матрицы (FPGA) или другого программируемого логического устройства, дискретной вентильной или транзисторной логики, дискретного компонента аппаратных средств или структуры из любой комбинации указанных средств. Процессор общего назначения может быть микропроцессором. Опционально, процессор общего назначения также может быть обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован комбинацией вычислительных устройств, таких как сигнальный процессор и микропроцессор, несколько микропроцессоров, один или несколько микропроцессоров с ядром цифрового сигнального процессора, или любой другой подобной конфигурацией.

[0232] Этапы способов или алгоритмов, описанные в вариантах осуществления настоящего изобретения, могут быть непосредственно встроены в аппаратные средства, инструкцию, исполняемую процессором, или их комбинацию. Память может представлять собой RAM-память, флэш-память, ROM-память, EPROM-память, EEPROM-память, регистр, жесткий диск, съемный магнитный диск, CD-ROM или носитель хранения данных любой другой формы, известной в технике. Например, память может соединяться с процессором, так что процессор может считывать информацию из памяти и записывать информацию в память. Альтернативно, память может дополнительно встраиваться в процессор. Процессор и память могут находиться в ASIC, и ASIC может находиться в UE. Альтернативно, процессор и память могут находиться в различных компонентах UE.

[0233] На основе описаний приведенных выше вариантов осуществления, специалистам в данной области техники может быть понятно, что настоящее изобретение может быть реализовано аппаратными средствами, встроенным программным обеспечением или их комбинацией. Если настоящее изобретение реализовано с использованием программного обеспечения, все настоящее изобретение или его часть может быть реализовано в форме компьютерного программного продукта. Компьютерный программный продукт включает в себя одну или несколько компьютерных инструкций. Когда компьютерные инструкции загружаются и исполняются на компьютере, процедуры или функции в соответствии с вариантами осуществления настоящего изобретения генерируются полностью или частично. Когда настоящее изобретение реализуется с использованием программного обеспечения, вышеописанные функции могут сохраняться на считываемом компьютером носителе или могут передаваться как одна или несколько инструкций или код на считываемом компьютером носителе. Компьютер может быть компьютером общего назначения, специализированным компьютером, компьютерной сетью или другим программируемым устройством. Компьютерные инструкции могут быть сохранены на считываемом компьютером носителе хранения данных или могут передаваться от одного считываемого компьютером носителя хранения данных на другой считываемый компьютером носитель хранения данных. Считываемый компьютером носитель включает в себя компьютерный носитель хранения данных и коммуникационную среду, причем коммуникационная среда включает в себя любую среду, которая обеспечивает возможность передачи компьютерной программы из одного места в другое. Носитель хранения данных может быть любым носителем, доступным для компьютера. Нижеследующее приведено в качестве примера, но не накладывает ограничения: считываемый компьютером носитель может включать в себя RAM, ROM, EEPROM, CD-ROM или другой носитель хранения на оптическом диске или магнитном диске или другое магнитное запоминающее устройство, или любой другой носитель, который может переносить или хранить ожидаемый программный код в форме инструкции или структуры данных и к которому можно осуществлять доступ посредством компьютера. Кроме того, любое соединение может быть надлежащим образом определено как считываемый компьютером носитель. Например, если программное обеспечение передается с веб-сайта, сервера или другого удаленного источника с использованием коаксиального кабеля, оптического волокна/кабеля, скрученной пары, цифровой абонентской линии (DSL) или беспроводных технологий, таких как инфракрасное излучение, радио или микроволны, то коаксиальный кабель, оптическое волокно/кабель, скрученная пара, DSL или беспроводные технологии, такие как инфракрасное излучение, радио и микроволны, включаются в определение носителя, к которому они относятся. Например, магнитный диск (disk) и оптический диск (disc), используемые настоящим изобретением, включают в себя компакт-диск (CD), лазерный диск, оптический диск, цифровой многофункциональный диск (DVD), гибкий диск и Blu-ray диск, где магнитный диск обычно копирует данные магнитным способом, а оптический диск копирует данные оптическим способом посредством лазерного средства. Вышеописанная комбинация должна также быть включена в объем защиты считываемого компьютером носителя.