Изобретение относится к области радиоизмерений, позволяет измерять временные интервалы путем анализа их эмпирического распределения и может быть использовано при построении цифровых измерителей временных параметров различных процессов, обогащенных помехами.

Для измерения временных интервалов на протяжении уже многих десятилетий широко применяют устройства, представляющие собой объединение счетного блока (схемы измерения единичных интервалов) с блоком усреднения единичных результатов. Примером подобного измерителя является схема, приведенная в [Патент РФ 2615159. Способ измерения временного интервала и варианты устройства его реализующего / Г.Р. Аванесян. - Опубл. 04.04.2017, Бюл. №10]. Измеритель эффективен в условиях, когда исследуемый параметр не подвергается существенным искажениям, а отклонения единичных результатов от ожидаемого значения имеют характер распределения близкий к гауссовому. При появлении в выборке единичных результатов сильно отличающихся от остальных оценка временного интервала будет получена с большой погрешностью, что предопределено особенностью классического метода усреднения.

Значительно большую точность позволяет получить подход, основанный на аппаратурном определении закона распределения исследуемых временных интервалов с последующим нахождением их моды. Такой метод был применен в устройстве, описанном в работе [Аванесян Г.Р., Антоненков В.Б., Богомолов Ю.А. Статистический анализатор временных интервалов. - «Приборы и техника эксперимента», 1993, №1] и показал высокую эффективность при кратковременном воздействии импульсных помех, результаты воздействия которых следует отнести к явным артефактам. Одним из вариантов реализации указанного метода является статистический анализатор, описанный в [Патент РФ 2208836. Статистический анализатор / А.Г. Морозов. - Опубл. 20.07.2003, Бюл. №20], принятый в качестве прототипа, техническая суть которого наиболее близка к заявленному техническому решению, и содержащий оперативное запоминающее устройство (ОЗУ), входной буфер в составе входного аналого-цифрового преобразователя, блок инкрементирования, счетчик, выходной регистр и блок управления, причем адресный вход ОЗУ, выход входного буфера и выход счетчика подключены к единой шине данных, информационный вход оперативного запоминающего устройства соединен с выходом блока инкрементирования, вход которого соединен с выходом оперативного запоминающего устройства, выходом анализатора является выход выходного регистра, вход которого подключен к единой шине данных, первый обнуляющий вход блока управления является входом обнуления анализатора, запускающий вход блока управления является запускающим входом анализатора, входом анализатора является вход аналого-цифрового преобразователя, в состав блока инкрементирования входят сумматор, триггер и регистр.

Недостатком анализатора является невозможность его применения при мультимодальном законе распределения исследуемой случайной величины. При нескольких модах анализатор определяет наибольшую из них, что ограничивает функциональные возможности устройства и не позволяет его применять в ситуациях, когда исследуемый информативный параметр может закономерно изменяться во времени. Другим недостатком анализатора является относительная алгоритмическая сложность процесса поиска моды по набранным данным, поскольку в процессе поиска моды ОЗУ анализатора требуется многократно переводить из режима чтения в режим записи и наоборот.

Технический результат, достигаемый при использовании настоящего изобретения, состоит, главным образом, в расширении функциональных возможностей анализатора и упрощении процесса поиска моды.

Технический результат по первому варианту достигается тем, что в статистический анализатор временных интервалов, содержащий входной буфер, оперативное запоминающее устройство, счетчик, блок инкрементирования, выходной регистр и блок управления, адресный вход оперативного запоминающего устройства, выход входного буфера и выход счетчика подключены к единой шине данных, информационный вход оперативного запоминающего устройства соединен с выходом блока инкрементирования, вход которого соединен с выходом оперативного запоминающего устройства, выходом анализатора является выход выходного регистра, вход которого подключен к единой шине данных, первый обнуляющий вход блока управления является входом обнуления анализатора, запускающий вход блока управления является запускающим входом анализатора, согласно изобретению, введен блок поиска максимума, вход которого подключен к выходу оперативного запоминающего устройства, первый выход блока поиска максимума соединен с тактовым входом выходного регистра, второй выход блока поиска максимума соединен со вторым обнуляющим входом блока управления, выход управления записью/чтения которого соединен со входом записи/чтения оперативного запоминающего устройства, выход переполнения счетчика соединен с тактовым входом блока поиска максимума, вход управления разрешением выхода входного буфера и инвертирующий вход управления разрешением выхода счетчика объединены и подключены к разрешающему выходу блока управления, к обнуляющему выходу которого подключены обнуляющие входы счетчика, блока инкрементирования и блока поиска максимума, счетный вход счетчика подключен к тактовому выходу блока управления, выход управления записью которого подключен к соответствующему входу блока инкрементирования, входом анализатор является вход входного буфера.

Кроме того, технический результат достигается тем, что, согласно изобретению, блок поиска максимума содержит вычитающий счетчик и компаратор двоичных кодов, выход которого является выходом блока, информационным входом которого является первый вход компаратора, второй вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом блока, обнуляющий вход которого является обнуляющим входом блока, а выход переполнения является выходом обнуления блока.

Кроме того, технический результат достигается тем, что, согласно изобретению, блок управления содержит два логических элемента 2И, элемент задержки, одновибратор, два логических элемента 2ИЛИ, триггер и генератор тактовых импульсов, выход которого подключен к первому входу элемента первого элемента 2И, выход которого является тактовым выходом блока, второй вход первого элемента 2И соединен с выходом триггера 14, тактовый вход которого соединен с выходом одновибратора 10, вход которого объединен с первыми входами первого и второго элементов 2ИЛИ и образует запускающий вход блока, первым обнуляющим входом которого является установочный вход триггера, с которым объединены первый вход третьего элемента 2ИЛИ и второй вход элемента 2ИЛИ, £>-вход триггера является входом фиксированного уровня логической единицы, вторым обнуляющим входом блока является второй вход первого элемента 2ИЛИ, выход которого соединен с обнуляющим входом триггера, второй вход третьего элемента 2ИЛИ соединен через элемент задержки с выходом второго элемента 2И, первый вход которого является входом сопровождения данных блока, а второй вход второго элемента 2И соединен с выходом одновибратора, причем выход одновибратора является разрешающим выходом блока, выходом управления записью WR1 которого является выход второго элемента 2И, а выходом управления записью/чтения блока служит выход третьего элемента 2ИЛИ, обнуляющим выходом блока служит выход второго элемента 2ИЛИ.

Технический результат по второму варианту достигается тем, что в статистический анализатор временных интервалов, содержащий счетчик, оперативное запоминающее устройство, блок инкрементирования, выходной регистр и блок управления, адресный вход оперативного запоминающего устройства подключен к выходу счетчика, информационный вход оперативного запоминающего устройства соединен с выходом блока инкрементирования, вход которого соединен с выходом оперативного запоминающего устройства, выходом анализатора является выход выходного регистра, вход которого подключен к выходу счетчика, первый обнуляющий вход блока управления является входом обнуления анализатора, запускающий вход блока управления является запускающим входом анализатора, согласно изобретению, введен блок поиска максимума, а счетчик содержит вход асинхронной загрузки данных, вход блока поиска максимума подключен к выходу оперативного запоминающего устройства, первый выход блока поиска максимума соединен с тактовым входом выходного регистра, второй выход блока поиска максимума соединен со вторым обнуляющим входом блока управления, выход управления записью/чтения которого соединен со входом записи/чтения оперативного запоминающего устройства, выход переполнения счетчика соединен с тактовым входом блока поиска максимума, вход управления загрузкой данных счетчика подключен к разрешающему выходу блока управления, к обнуляющему выходу которого подключены обнуляющие входы счетчика, блока инкрементирования и блока поиска максимума, счетный вход счетчика подключен к тактовому выходу блока управления, выход управления записью которого подключен к соответствующему входу блока инкрементирования, входом анализатора является вход асинхронной загрузки данных счетчика.

Сущность изобретения поясняется графическим материалом.

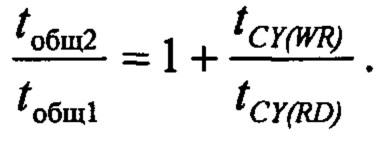

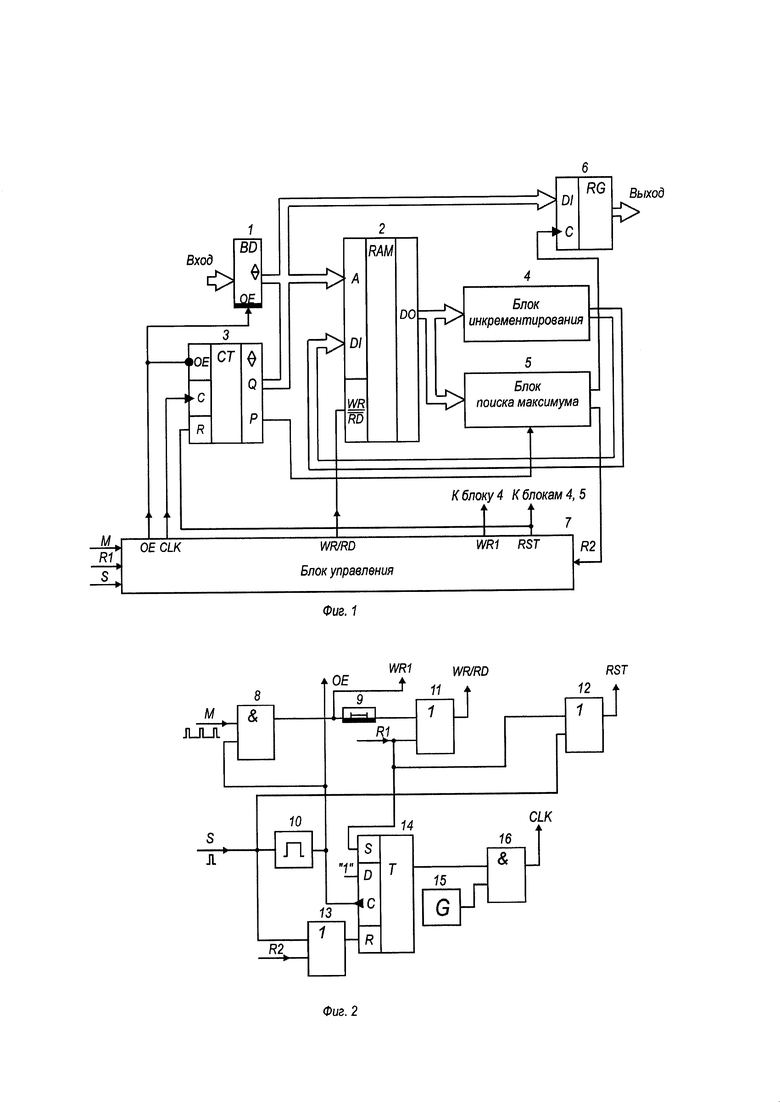

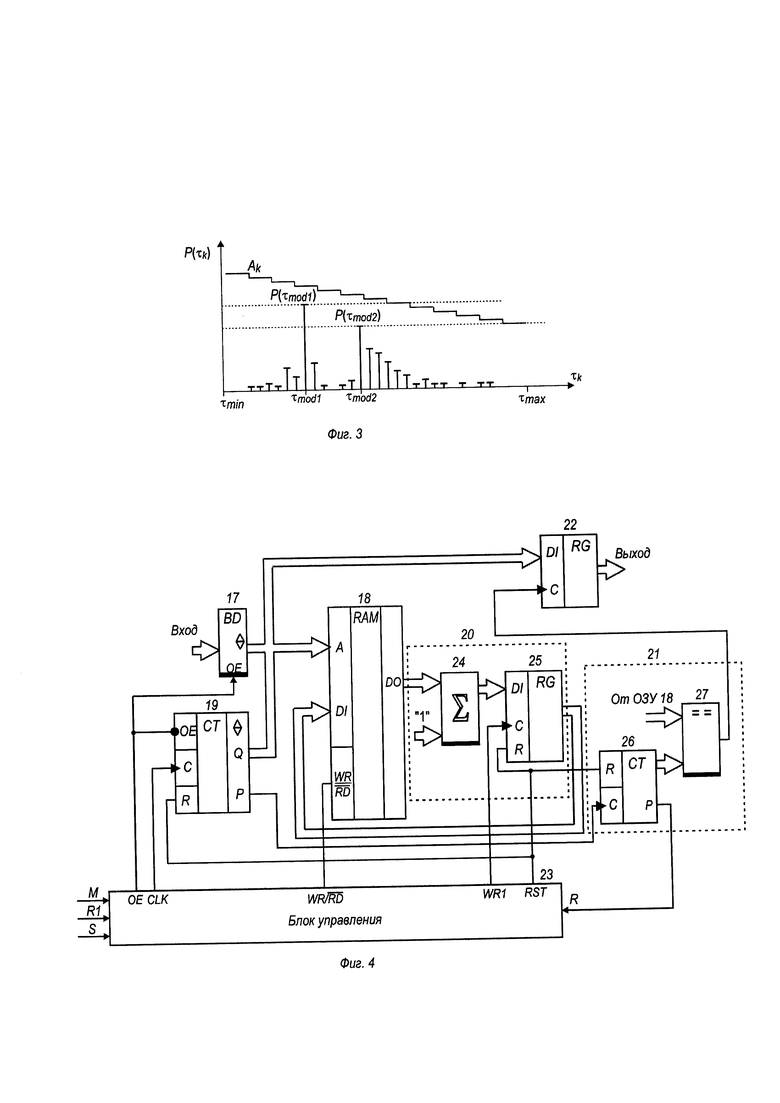

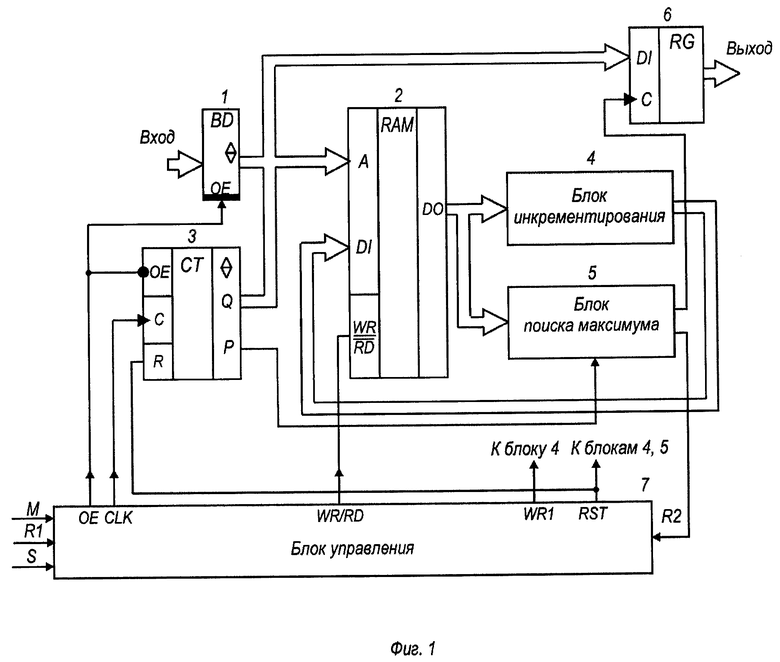

На фиг. 1 приведена функциональная схема первого варианта статистического анализатора временных интервалов, на фиг. 2 - функциональная схема одного из вариантов реализации блока управления, входящего в состав анализатора. На фиг. 3 показан график, иллюстрирующий работу анализатора при поиске двух мод. На фиг. 4 приведена функциональная схема анализатора со схемами блока инкрементирования и блока поиска максимума. На фиг. 5 приведена функциональная схема второго варианта статистического анализатора временных интервалов

Функциональная схема по фиг. 1 содержит входной буфер 1 с высокоимпедансным состоянием выхода, ОЗУ 2, счетчик 3 с высокоимпедансным состоянием выхода, блок 4 инкрементирования, блок 5 поиска максимума, выходной регистр 6 и блок 7 управления, адресный вход ОЗУ 2, выход буфера 1 и выход счетчика 3 подключены к единой шине данных, информационный вход ОЗУ 2 соединен с выходом блока 4 инкрементирования, вход которого соединен с выходом ОЗУ 2, выходом анализатора является выход выходного регистра 6, вход которого подключен к единой шине данных, первый обнуляющий вход R1 блока 7 управления является входом обнуления анализатора, запускающий вход S блока 7 управления является запускающим входом анализатора, вход блока 5 поиска максимума подключен к выходу ОЗУ 2, первый выход блока 5 поиска максимума соединен с тактовым входом выходного регистра 6, второй выход блока 5 поиска максимума соединен со вторым обнуляющим входом R2 блока 7 управления, выход управления записью/чтения WR/RD которого соединен со входом записи/чтения ОЗУ 2, выход переполнения счетчика 3 соединен с тактовым входом блока 5 поиска максимума, вход управления разрешением выхода входного буфера 1 и инвертирующий вход управления разрешением выхода счетчика 3 объединены и подключены к разрешающему выходу ОЕ блока 7 управления, к обнуляющему выходу RST которого подключены обнуляющие входы счетчика 3, блока 4 инкрементирования и блока 5 поиска максимума, счетный вход счетчика 3 подключен к тактовому выходу CLK блока 7 управления, выход управления записью WR1 которого подключен к соответствующему входу блока 4 инкрементирования, входом анализатор является вход входного буфера 1, вход М (Marker) блока 7 управления является входом сопровождения входных данных анализатора, вход S блока 7 управления является запускающим входом анализатора.

Функциональная схема блока 7 по фиг. 2 содержит элементы 2И 8, 16, элемент 9 задержки, одновибратор 10, элементы 2 ИЛИ 11, 12, 13, триггер 14 и генератор 15 тактовых импульсов, выход которого подключен к первому входу элемента 2И 16, выход которого является тактовым выходом CLK блока, второй вход элемента 2И 16 соединен с выходом триггера 14, тактовый вход которого соединен с выходом одновибратора 10, вход которого объединен с первыми входами элементов 2ИЛИ 12, 13 и образует запускающий вход S блока, первым обнуляющим входом R1 которого является установочный вход триггера 14, с которым объединены первый вход элемента 2ИЛИ 11 и второй вход элемента 2ИЛИ 12, D-вход триггера 14 является входом фиксированного уровня логической единицы, вторым обнуляющим входом R2 блока является второй вход элемента 2ИЛИ 13, выход которого соединен с обнуляющим входом триггера 14, второй вход элемента 2ИЛИ 11 соединен через элемент 9 с выходом элемента 2И 8, первый вход которого является входом М сопровождения данных блока, а второй вход элемента 2И 8 соединен с выходом одновибратора 10, причем выход одновибратора 10 является разрешающим выходом ОЕ блока, выходом управления записью WR1 которого является выход элемента 2И 8, а выходом управления записью/чтения WR/RD блока служит выход элемента 2ИЛИ 11, обнуляющим выходом RST блока служит выход элемента 2ИЛИ 12.

На фиг. 3 показан график Р(τk) эмпирического распределения значений временных интервалов τk с выделением мод τmod исследуемых временных интервалов, на котором приведены две моды τmod1 и τmod2, лежащие в диапазоне от τmin до τmax. На приведенном графике Р(τk) - вероятность появления интервала τk, а ступенчато меняющаяся величина Ak - значение адресного кода на адресном входе ОЗУ 2. Величина Ak на график Р(τk) нанесена условно для иллюстрации принципа поиска локальных максимумов.

Функциональная схема по фиг. 4 содержит входной буфер 17 с высокоимпедансным состоянием выхода, ОЗУ 18, счетчик 19 с высокоимпедансным состоянием выхода, блок 20 инкрементирования, блок 21 поиска максимума, выходной регистр 22 и блок 23 управления. В состав блока 20 инкрементирования входит сумматор 24 и регистр 25, в состав блока 21 поиска максимума - вычитающий счетчик 26 и компаратор 27 двоичных кодов. Адресный вход ОЗУ 18, выход буфера 17 и выход счетчика 19 подключены к единой шине данных, информационный вход ОЗУ 18 соединен с выходом регистра 25, первый вход сумматора 20 соединен с выходом ОЗУ 18, выход сумматора 24 соединен с информационным входом регистра 25, выходом анализатора является выход выходного регистра 22, вход которого подключен к единой шине данных, первый обнуляющий вход R1 блока 23 является входом обнуления анализатора, запускающий вход S блока 23 является запускающим входом анализатора, первый вход компаратора 27 подключен к выходу ОЗУ 18, а второй вход подключен к выходу счетчика 26, счетный вход которого соединен с выходом переполнения счетчика 19, выход компаратора 27 соединен с тактовым входом выходного регистра 22, выход переполнения счетчика 26 соединен со вторым обнуляющим входом R2 блока 23 управления, выход управления записью/чтения WR/RD которого соединен со входом записи/чтения ОЗУ 18, вход управления разрешением выхода входного буфера 17 и инвертирующий вход управления разрешением выхода счетчика 19 объединены и подключены к разрешающему выходу ОЕ блока 23 управления, к обнуляющему выходу RST которого подключены обнуляющие входы счетчика 19, регистра 25 и счетчика 26, счетный вход счетчика 19 подключен к тактовому выходу CLK блока 23 управления, выход управления записью WR1 которого подключен к тактовому входу регистра 25, входом анализатора является вход входного буфера 17, вход М блока 23 управления является входом сопровождения входных данных анализатора, вход S блока 23 управления является запускающим входом анализатора.

Функциональная схема по фиг. 5 содержит счетчик 28, ОЗУ 29, блок 30 инкрементирования, блок 31 поиска максимума, выходной регистр 32 и блок 33 управления, адресный вход ОЗУ 29 подключен к выходу счетчика 28, информационный вход ОЗУ 29 соединен с выходом блока 30 инкрементирования, вход которого соединен с выходом ОЗУ 29, выходом анализатора является выход выходного регистра 32, вход которого подключен к выходу счетчика 28, первый обнуляющий вход R1 блока 33 управления является входом обнуления анализатора, запускающий вход S блока 33 управления является запускающим входом анализатора, вход блока 31 поиска максимума подключен к выходу ОЗУ 29, первый выход блока 31 поиска максимума соединен с тактовым входом выходного регистра 32, второй выход блока 31 поиска максимума соединен со вторым обнуляющим входом R2 блока 33 управления, выход управления записью/чтения WR/RD которого соединен со входом записи/чтения ОЗУ 29, выход переполнения счетчика 28 соединен с тактовым входом блока 31 поиска максимума, вход управления асинхронной загрузкой данных счетчика 28 подключен к разрешающему выходу ОЕ блока 33 управления, к обнуляющему выходу RST которого подключены обнуляющие входы счетчика 28, блока 30 инкрементирования и блока 31 поиска максимума, счетный вход счетчика 28 подключен к тактовому выходу CLK блока 33 управления, выход управления записью WR1 которого подключен к соответствующему входу блока 30 инкрементирования, входом анализатора является вход асинхронной загрузки данных счетчика 28, вход М блока 33 управления является входом сопровождения входных данных анализатора, вход S блока 33 управления является запускающим входом анализатора.

Суть способа измерения временных интервалов, который реализуется в рассматриваемых анализаторах (см. фиг. 1, 4, 5), состоит в накоплении единичных результатов измерений (отсчетов) временных интервалов τ, определению эмпирического закона распределения исследуемых временных интервалов и вычислению по полученной выборке отсчетов моды - наиболее вероятного значения τmod, которое является оценкой временных интервалов. При этом предполагается, что временные интервалы τ являются случайной величиной, которая принимает дискретные значения τk в пределах от τmin до τmax. Эмпирическая характеристика Р(τk) в памяти устройства представляется сразу же после появления последнего отсчета, входящего в интервал наблюдения Тн. Достигается такое быстродействие за счет совмещенного алгоритма накопления и сортировки данных, идея которого видна ниже из описания работы первого варианта устройства, схема которого приведена на фиг. 1.

Через буфер 1 на отрезке времени наблюдения Тн на адресный вход ОЗУ 2 подаются отсчеты временных интервалов τk. При этом адресное пространство ОЗУ 2 представляется в виде совокупности значений аргумента τk дискретной функции Р(τk), то есть каждому адресу Ak памяти ставится в соответствие свое значение τk, которое является целым числом. Причем должно выполняться условие

Amax ≥ τmax,

где Amax - максимальное значение адреса ОЗУ.

Для запуска анализатора на его запускающий вход S подают короткий импульс, в ответ на что блок 7 управления формирует на выходе ОЕ разрешающий импульс длительностью Тн, который поступает как на соответствующий вход буфера 1, так и на инвертирующий вход разрешения выхода счетчика 3. В результате выход счетчика 3 отключается от шины данных, а выход буфера 1 подключается. Коды τk, поступающие с выхода буфера 1 на адресный вход ОЗУ 2, вызывают содержимое соответствующих данному адресу ячеек, которое инкрементируется и вновь записывается по имеющемуся адресу. Происходит указанное в цепочке выход ОЗУ 2 - блок 4 инкрементирования - информационный вход ОЗУ 2. Таким образом, если в начальный момент времени ОЗУ 2 было очищено, то по окончании интервала Тн в его ячейках по каждому конкретному адресу будет содержаться количество появлений значений τk. При этом указанное количество - величина, прямо пропорциональная вероятности Р(τk). Нахождение моды τmod сводится к поиску ячейки ОЗУ 2, в которой зафиксировано наибольшее значение сР(τk) (с - коэффициент пропорциональности). Адрес ячейки, для которой выполняется условие сР(τk) = max и будет соответствовать величине τmod.

После того, как получены значения сР(τk), анализатор переходит в режим нахождения моды, который характеризуется отключением от шины данных буфера 1 и подключением к ней счетчика 3, назначением которого является перебор адресов ОЗУ 2 на этапе нахождения моды. Указанное происходит в связи с прекращением действия импульса длительностью Тн на разрешающем выходе ОЕ блока 7 управления. При этом на выходе WR/RD блока 7 устанавливается постоянный на время выполнения этапа уровень логического нуля, переключающий ОЗУ 2 в режим чтения, а на выходе CLK блока 7 появляется последовательность тактовых импульсов, подаваемая на счетный вход счетчика 3. Перебор адресов Ak осуществляется с частотой, задаваемой тактовой последовательностью CLK. Для поиска максимального значения служит блок 5, на вход которого последовательно поступают данные с выхода ОЗУ 2. При обнаружении первого максимального значения сР(τk) на тактовый вход регистра 6 с выхода блока 5 направляется скачок напряжения, который записывает находящийся на шине данных код τk=τmod. Поскольку закон распределения исследуемой величины τk может быть мультимодальным, то после получения первого результата анализатор, оставаясь в режиме нахождения моды, продолжает поиск следующего локального максимума, при нахождении которого соответствующий ему код τk записывается в регистр 6, сменяя ранее найденный. Указанный процесс поиска мод продолжается до тех пор, пока не будет пройден весь диапазон возможных значений τk. По окончании поиска на нижнем по схеме (см. фиг. 1) выходе блока 5 появляется перепад напряжений, который, поступая на вход R2 блока 7 управления, обнуляет его, переводя в режим ожидания следующего запускающего импульса.

Для корректной работы анализатора требуется перед каждым очередным циклом анализа очищать его память. Наиболее простой способ - это перебор адресов ОЗУ 2 с предустановленным на его входе нулем и включением ОЗУ в режим записи (на входе записи/чтения устанавливают уровень логической единицы). Для этого на входе R1 блока 7 управления устанавливают высокий логический уровень, в ответ на что на его выходе WR/RD также устанавливается высокий логический уровень, переводя ОЗУ 2 в режим записи а на выходе CLK блока 7 появляется последовательность тактовых импульсов, подаваемая на счетный вход счетчика 3. Для установки на входе ОЗУ 2 кода нуля блок 4 инкрементирования по импульсу, поступающему с выхода RST блока 7 обнуляется, устанавливая таким образом на своем выходе код нуля. Запись в ОЗУ 2 «нулей» будет происходить до тех пор, пока на входе R1 установлен высокий логический уровень, следовательно, его длительность должна быть достаточной для перебора всех адресов ОЗУ 2, то есть при периоде счетных импульсов равном Δt указанная длительность должна быть больше произведения (Amax+1)Δt.

Работа блока 7 управления (см. фиг. 2) сводится к получению внешних управляющих сигналов и формированию ответных воздействий, необходимых для управления основными функциональными блоками анализатора. В исходном состоянии, характеризующемся низкими логическими уровнями на всех входах блока, на всех его выходах также присутствуют уровни логических нулей. Блок 7 может находиться в одном из трех режимов: в режиме очистки памяти анализатора, в режиме накопления данных и режиме поиска моды. Для очистки памяти анализатора, как уже указывалось выше, на вход R1 подают импульс длительностью более (Amax+1)Δt. Указанный импульс поступает через входы элементов 2ИЛИ 11 и 12 на их выходы, соответственно на выходы WR/RD и RST блока, а также на 5-вход триггера 14, переводя его в состояние высокого логического уровня на выходе. Последнее приводит к установке разрешающего уровня на верхнем по схеме входе элемента 2И 16, в результате чего тактовые импульсы с выхода генератора 15 проходят на выход указанного логического элемента, а, следовательно, на выход CLK блока. Режим очистки завершается с окончанием действия импульса на входе R1, однако тактовые импульсы с выхода CLK блока снимаются только после перевода блока в режим накопления данных. Для перевода в указанный режим на вход S блока подают короткий запускающий импульс, а на входе R1 поддерживают уровень логического нуля. Поступивший импульс возвращает в исходное состояние триггер 14, поступает на выход RST блока и запускает одновибратор 10, который выдает импульс, длительность Тн которого определяет отрезок времени отводимый для получения отсчетов τk исследуемых временных интервалов. Подача на вход анализатора отсчетов τk должна сопровождаться импульсами, направляемыми на вход М блока управления, что необходимо для синхронизации анализатора с источником данных. Указанные импульсы сопровждения поступают через элемент 2И 8 на выход управления записью WR1 блока 7 и далее на соответствующий вход блока 4 инкрементирования, где используются как импульсы синхронизации записи инкрементированных данных. С некоторой задержкой во времени, достаточной для получения инкрементированных данных на выходе блока 4, импульсы записи/чтения поступают с выхода элемента 9 задержки через элемент 2ИЛИ 11 на выход WR/RD блока которые переводят ОЗУ 2 в режим записи данных, поступающих с выхода блока 4 инкрементирования. По завершении этапа накопления данных блок 7 управления переходит в режим поиска моды. Переход в этот режим происходит по отрицательному фронту импульса на выходе одновибратора 10. Указанный фронт переводит триггер 14 в состояние высокого логического уровня на выходе, в результате чего тактовые импульсы с выхода генератора 15 направляются на выход CLK блока 7. Завершается этап поиска моды появлением на входе R2 обнуляющего импульса, который возвращает триггер 14 в исходное состояние.

Процесс поиска моды сводится к поиску максимального значения эмпирической характеристики распределения временных интервалов τk, если распределение унимодальное и локальных максимумов, если распределение мультимодальное. В качестве иллюстрации на фиг. 3 показан пример двухмодального распределения величины τk. Поиск моды происходит путем пошагового снижения уровня Ak и сравнения с ним всех операндов, поступающих с выхода ОЗУ 2, при наступлении равенства формируют перепад напряжений, указывающий на нахождение одной из мод. Значение контрольного уровня Ak можно задать выражением

A(ΔkT)=Amax-(k-1),

где А(kΔТ) - значение контрольного уровня на интервале от (k-1)ΔТ до kΔТ;

k - порядковый номер контрольного уровня (k=1, 2, 3, … K);

ΔT - период смены уровней (длительность поддержания уровня фиксированным). Разумеется, период ΔT должен быть достаточным для перебора всех адресов ОЗУ 2 в режиме чтения данных. Отметим, что если исходить из принятых в работе обозначений, то несложно видеть, что K=Amax, а общее число адресов ОЗУ, включая нулевой, составит K+1. Причем K определяет и диапазон значений τk.

Время tобщ1, затрачиваемое анализатором на поиск моды, зависит от числа K, то есть от диапазона измеряемых значений τk, от максимально возможного значения cP(Uk), от времени цикла чтения tCY(RD) ОЗУ, от абсолютного значения τmod и от скорости смены уровней (от ΔT). Величина сР(τk) численно равна количеству интервалов τk, накопленных за время Тн. Для сравнения быстродействия анализатора с прототипом рассмотрим простой пример, в котором τmod = Amax. Это значит, что совпадение операнда с выхода ОЗУ 2 с контрольным уровнем Amax должно произойти при k=1 на интервале от 0 до ΔT, если при этом учесть, что перебор адресов ОЗУ начинается с нулевого адреса, то несложно получить выражение для tобщ1:

tобщ1=(K+1)tCY(RD).

В данном примере время tобщ2, затрачиваемое прототипом на поиск моды определится так:

tобщ2=(K+1)(tCY(RD)+tCY(WR)),

где tCY(WR) - время цикла записи ОЗУ.

Взяв отношение представленных выражений, получим:

Последняя запись позволяет без труда увидеть, что выигрыш в быстродействии, за счет исключения операций записи в ОЗУ и упрощения, таким образом, процесса поиска моды, очевиден и в случае равенства длительностей циклов чтения и записи составляет 2 раза. Причем здесь введено упрощающее допущение, исключающее время, необходимое на перевод ОЗУ прототипа из одного режима в другой.

Варианты реализации блоков 20 и 21 инкрементирования и поиска максимума соответственно, показаны на объединенной схеме анализатора по фиг. 4. Принцип действия всего анализатора аналогичен принципу действия вышерассмотренного устройства (см. фиг. 1), что же касается блоков 20 и 21, то особенности их функционирования состоят в следующем.

Работа блока 20 инкрементирования заключается в сложении поступающего на верхний по схеме вход сумматора 24 операнда с единицей, код которой зафиксирован на нижнем по схеме входе сумматора 24. Результат сложения направляется на информационный вход синхронного регистра 25, в который заносится по фронту импульса на его тактовом входе. Указанный импульс поступает с выхода WR1 блока 23 управления и играет роль импульса записи, который приводит к появлению инкрементированных данных на информационном входе ОЗУ 18, после чего на входе управления записью/чтения ОЗУ появляется импульс, переводящий ОЗУ в режим записи.

В блоке 21 поиска максимума происходит сравнение кода с выхода счетчика 26 с кодом, поступающим с выхода ОЗУ 18. Сравнение происходит в режиме поиска моды, когда ОЗУ 18 находится в состоянии чтения данных. Поиск максимума происходит путем пошагового снижения контрольного уровня от значения Amax до 0, который поступает с выхода счетчика 26, работающего в режиме вычитания. На счетный вход указанного счетчика подаются импульсы переполнения с соответствующего выхода адресного счетчика 19, коэффициент пересчета которого выбирается равным количеству адресов ОЗУ 18. В этом случае после перебора всех адресов ОЗУ 18 на выходе переполнения счетчика 19 появляется перепад напряжений, который играет роль счетного для вычитающего счетчика 26. Если последний имеет также коэффициент пересчета равный количеству адресов ОЗУ 18, то процесс вычитания будет начинаться с фиксации на его разрядных выходах кода, соответствующего максимальному адресу ОЗУ 18, который со следующим счетным импульсом уменьшится на единицу и т.д., последовательно снижая указанным образом контрольный уровень. В свою очередь, в компараторе 27 происходит сравнение чередующихся значений сР(τk) с контрольным уровнем (см. иллюстрацию по фиг. 3) и при наступлении равенства на его выходе формируется перепад напряжений (индикатор нахождения моды), поступающий на тактовый вход выходного регистра 22. При мультимодальном законе распределения исследуемой величины таким образом последовательно будут выявляться локальные максимумы, указывающие на соответствующие им моды. Завершается процесс поиска появлением на выходе переполнения счетчика 26 скачка напряжений, который, поступая на вход R2 блока 23 управления, останавливает подачу счетных импульсов на вход счетчика 19.

Второй вариант анализатора (см. фиг. 5) отличается от первого отсутствием входного буфера и введением счетчика с асинхронной загрузкой данных. Причем некоторое усложнение счетчика позволяет отказаться не только от входного буфера, но и от устройств с высокоимпедансным состоянием выходов. Входные данные, коды τk, в настоящей схеме поступают на вход DI асинхронной загрузки данных счетчика 28, который в режиме накопления данных работает как управляемый многоразрядный ключ, передающий данные со входа на выход при наличии высокого логического уровня на управляющем входе L счетчика. Указанный уровень устанавливается на выходе ОЕ блока 33 управления сразу же после запуска анализатора. По истечении времени Тн, то есть по окончании режима накопления данных, высокий логический уровень на выходе ОЕ сменяется на низкий, и счетчик переводится, таким образом, в обычный режим счета импульсов, поступающих с выхода CLK блока 33 управления. В остальном работа анализатора, включая алгоритм работы блока управления, не отличается от работы ранее рассмотренного устройства, показанного на фиг. 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ АМПЛИТУДЫ ИМПУЛЬСОВ И ИЗМЕРИТЕЛЬ ЕГО РЕАЛИЗУЮЩИЙ (ВАРИАНТЫ) | 2021 |

|

RU2773621C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Изобретение относится к области радиоизмерений. Технический результат заключается в расширении функциональных возможностей анализатора и упрощении процесса поиска моды, необходимой для получения оценки исследуемых временных интервалов. Статистический анализатор содержит входной буфер, счетчик, оперативное запоминающее устройство, блок инкрементирования, блок поиска максимума, выходной регистр и блок управления. В вариантном исполнении из анализатора может быть исключен входной буфер. Принцип действия анализатора предусматривает аппаратурное определение характеристики распределения исследуемых временных интервалов как случайной величины и поиск моды эмпирического распределения. Причем анализатор позволяет работать с временными интервалами, характеристики распределений которых являются как унимодальными, так и мультимодальными. 2 н. и 2 з.п. ф-лы, 5 ил.

1. Статистический анализатор временных интервалов, содержащий входной буфер с высокоимпедансным состоянием выхода, оперативное запоминающее устройство, счетчик с высокоимпедансным состоянием выхода, блок инкрементирования, выходной регистр и блок управления, адресный вход оперативного запоминающего устройства, выход входного буфера и выход счетчика подключены к единой шине данных, информационный вход оперативного запоминающего устройства соединен с выходом блока инкрементирования, вход которого соединен с выходом оперативного запоминающего устройства, выходом анализатора является выход выходного регистра, вход которого подключен к единой шине данных, первый обнуляющий вход блока управления является входом обнуления анализатора, запускающий вход блока управления является запускающим входом анализатора, отличающийся тем, что в него введен блок поиска максимума, вход которого подключен к выходу оперативного запоминающего устройства, первый выход блока поиска максимума соединен с тактовым входом выходного регистра, второй выход блока поиска максимума соединен со вторым обнуляющим входом блока управления, выход управления записью/чтения которого соединен с входом записи/чтения оперативного запоминающего устройства, выход переполнения счетчика соединен с тактовым входом блока поиска максимума, вход управления разрешением выхода входного буфера и инвертирующий вход управления разрешением выхода счетчика объединены и подключены к разрешающему выходу блока управления, к обнуляющему выходу которого подключены обнуляющие входы счетчика, блока инкрементирования и блока поиска максимума, счетный вход счетчика подключен к тактовому выходу блока управления, выход управления записью которого подключен к соответствующему входу блока инкрементирования, входом анализатора является вход входного буфера.

2. Статистический анализатор по п. 1, отличающийся тем, что блок поиска максимума содержит вычитающий счетчик и компаратор двоичных кодов, выход которого является выходом блока, информационным входом которого является первый вход компаратора, второй вход которого соединен с выходом счетчика, счетный вход которого является тактовым входом блока, обнуляющий вход которого является обнуляющим входом блока, а выход переполнения является выходом обнуления блока.

3. Статистический анализатор по п. 1, отличающийся тем, что блок управления содержит два логических элемента 2И, элемент задержки, одновибратор, два логических элемента 2ИЛИ, триггер и генератор тактовых импульсов, выход которого подключен к первому входу элемента первого элемента 2И, выход которого является тактовым выходом блока, второй вход первого элемента 2И соединен с выходом триггера 14, тактовый вход которого соединен с выходом одновибратора 10, вход которого объединен с первыми входами первого и второго элементов 2ИЛИ и образует запускающий вход блока, первым обнуляющим входом которого является установочный вход триггера, с которым объединены первый вход третьего элемента 2ИЛИ и второй вход элемента 2ИЛИ, D-вход триггера является входом фиксированного уровня логической единицы, вторым обнуляющим входом блока является второй вход первого элемента 2ИЛИ, выход которого соединен с обнуляющим входом триггера, второй вход третьего элемента 2ИЛИ соединен через элемент задержки с выходом второго элемента 2И, первый вход которого является входом сопровождения данных блока, а второй вход второго элемента 2И соединен с выходом одновибратора, причем выход одновибратора является разрешающим выходом блока, выходом управления записью WR1 которого является выход второго элемента 2И, а выходом управления записью/чтения блока служит выход третьего элемента 2ИЛИ, обнуляющим выходом блока служит выход второго элемента 2ИЛИ.

4. Статистический анализатор временных интервалов, содержащий счетчик, оперативное запоминающее устройство, блок инкрементирования, выходной регистр и блок управления, адресный вход оперативного запоминающего устройства подключен к выходу счетчика, информационный вход оперативного запоминающего устройства соединен с выходом блока инкрементирования, вход которого соединен с выходом оперативного запоминающего устройства, выходом анализатора является выход выходного регистра, вход которого подключен к выходу счетчика, первый обнуляющий вход блока управления является входом обнуления анализатора, запускающий вход блока управления является запускающим входом анализатора, отличающийся тем, что в него введен блок поиска максимума, а счетчик содержит вход асинхронной загрузки данных, вход блока поиска максимума подключен к выходу оперативного запоминающего устройства, первый выход блока поиска максимума соединен с тактовым входом выходного регистра, второй выход блока поиска максимума соединен со вторым обнуляющим входом блока управления, выход управления записью/чтения которого соединен с входом записи/чтения оперативного запоминающего устройства, выход переполнения счетчика соединен с тактовым входом блока поиска максимума, вход управления загрузкой данных счетчика подключен к разрешающему выходу блока управления, к обнуляющему выходу которого подключены обнуляющие входы счетчика, блока инкрементирования и блока поиска максимума, счетный вход счетчика подключен к тактовому выходу блока управления, выход управления записью которого подключен к соответствующему входу блока инкрементирования, входом анализатора является вход асинхронной загрузки данных счетчика.

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2010 |

|

RU2429515C1 |

| Машина для расстила льна | 1931 |

|

SU26146A1 |

| US 4534041 A, 06.08.1985. | |||

Авторы

Даты

2021-08-23—Публикация

2020-11-06—Подача