Изобретение относится к области автоматики и вычислительной техники и предназначено для повышения отказоустойчивости оперативного запоминающего устройства (ОЗУ) в управляющих системах реального времени.

Известно устройство [1], содержащее избыточные разряды кода Хэмминга и контроллер этого кода, позволяющее обнаруживать одиночные и двойные ошибки в словах памяти ОЗУ и корректировать одиночные ошибки. Эти функции являются стандартными для контроллера кода Хэмминга и применяются во многих ЭВМ повышенной надежности.

Недостатком устройства является невозможность восстановления физически отказавших ячеек ОЗУ (за возможным исключением одной - двух резервных ячеек, иногда применяемых в ОЗУ), что из-за роста со временем кратности ошибки ведет к отказу устройства или к ошибочной коррекции. Даже при наличии резервной строки или столбца в ОЗУ восстановление возможно только для одного отказа ОЗУ, что для ответственных систем, работающих в тяжелых неблагоприятных внешних условиях, явно недостаточно. Кроме того, появление двойного и тройного устойчивого отказа в слове ОЗУ ведет к отказу всего устройства или одного из его каналов, если система многоканально резервирована, что также понижает характеристики отказоустойчивости устройства.

Известно устройство [2], представляющее собой сервер высокопроизводительной вычислительной системы pSeries 690 фирмы IBM (США), построенной на базе микропроцессора POWER4, имеющее высокопроизводительную отказоустойчивую многоуровневую память (ОЗУ), спроектированную в технологии RAS (высокая надежность, готовность и обслуживаемость) для работы в условиях возникновения аппаратурных сбоев и отказов. В известном устройстве высокая отказоустойчивость памяти достигается за счет хранения результатов текущих вычислений в кэш-памяти трех уровней (помимо ОЗУ), при этом 64KB кэш-команд и 32KB кэш-данных внутри чипа защищены битами паритета, а кэш межмодульной связи и кэш-директорий связи с ОЗУ (до 32 MB) и само ОЗУ защищены кодом Хэмминга. При невосстановимом отказе (например, кратном) в кэш уровня i(i=1, 2, 3) корректный результат в реальном времени берется из уровня i+1, вплоть до «уровня» ОЗУ.

Недостатком устройства является невозможность восстановления физически отказавших ячеек кэш-памяти и ОЗУ, что из-за роста со временем кратности ошибки ведет к деградации памяти отключением отказавших разделов, к отказу устройства или к ошибочной коррекции. При этом основной негативный вклад в снижение надежности памяти вносят двойные и тройные устойчивые отказы, поскольку борьба с двойными сбоями ведется известными системными методами: профилактической очисткой памяти от одиночных сбоев (так называемый scrubbing) с помощью контроллеров-«чистильщиков», постоянно или периодически собирающих «мусор» в виде слов с одиночной ошибкой типа сбоя в ОЗУ для восстановления правильного значения и записи его на прежнее место в памяти; введением программных точек возврата и перезагрузок из более высокого уровня памяти вплоть до постоянного запоминающего устройства команд и сохраненных критических данных.

Наиболее близким по техническому решению к предлагаемому изобретению является отказоустойчивое оперативное запоминающее устройство [3], содержащее избыточное ОЗУ, снабженное кодом Хэмминга, контроллер кода Хэмминга, регистр адреса памяти, регистр данных памяти и сумматор по модулю два, вычисляющий синдром устойчивой ошибки.

Известное устройство позволяет восстанавливать информацию при возникновении кратных устойчивых отказов в ОЗУ. В известном устройстве используется алгоритм восстановления информации за счет повторной записи по тому же адресу инвертированного считанного из избыточного ОЗУ слова, предложенный в [4]. В [3] этот алгоритм расширен для коррекции скрытых устойчивых отказов в ОЗУ.

Недостатком известного устройства является снижение быстродействия основного вычислительного канала за счет постоянной обработки искаженных слов при неоднократной адресации к ним в ОЗУ. Кроме того, сохранение обращений к физически отказавшим ячейкам памяти ведет со временем к повышению вероятности увеличения кратности ошибки в слове ОЗУ как за счет сбоев, так и устойчивых отказов, что, в свою очередь, ведет к ошибочной коррекции информации и к отказу устройства. Предложенный в известном устройстве [3] механизм вычисления и применения поправок требует добавочной памяти, емкостью, как минимум, равной основной памяти. Последнее может быть приемлемым только для очень маленьких ОЗУ (в [3] - восемь слов), дублирование же ОЗУ, реально в системах управления имеющего емкость порядка 0,5-50 Мегабайт статической памяти в рамках одного канала, обычно неприемлемо по соображениям надежности, потребления энергии и стоимости.

Техническим результатом изобретения является повышение степени отказоустойчивости ОЗУ систем управления реального времени по отношению к одиночным, двойным и тройным комбинированным отказам и сбоям при одновременном упрощении устройства и расширении его функциональных возможностей. В целом изобретение позволяет парировать до нескольких сотен отказавших ячеек памяти с подобным типом отказов.

Указанный технический результат достигается тем, что в известное оперативное запоминающее устройство, содержащее избыточное ОЗУ, снабженное кодом Хэмминга, контроллер кода Хэмминга, регистр адреса памяти, регистр данных памяти, сумматор по модулю два, вычисляющий синдром устойчивой ошибки, дополнительно введены диагностическая кэш-память емкостью порядка 1 Кслово, первый и второй регистры-инверторы, входной и выходной мультиплексоры соответственно на два и три направления, элемент ИЛИ, элемент И, сумматор порога ошибочных битов слова и автомат управления, при этом адресные входы диагностической кэш-памяти подсоединены к индексной части адреса слова памяти ОЗУ, а входы данных диагностической кэш-памяти подсоединены к слову данных ОЗУ и к тэговой части адреса слова памяти ОЗУ, входы управления кэш-памятью соединены с входами управления ОЗУ, входы регистров-инверторов подсоединены к шине данных ОЗУ и к нулевому направлению выходного мультиплексора, выход диагностической кэш-памяти подсоединен в выходу выходного мультиплексора, а выходы регистров-инверторов подсоединены к первому и второму направлениям выходного мультиплексора и к сумматору по модулю два, выходы которого подключены к многовходовому элементу ИЛИ и ко входам сумматора порога ошибочных битов слова, выход элемента ИЛИ подсоединен ко входу элемента И, выходы элемента И, контроллера кода Хэмминга, бита корректности слова ОЗУ и два выхода сумматора порога ошибочных битов слов подключены ко входу автомата управления, управляющие выходы которого заведены на входы управления контроллера кода Хэмминга, управляющие входы мультиплексоров, вход разрешения выдачи содержимого вышеуказанных регистров, на входы Чт./Зап. ОЗУ и диагностической кэш-памяти, и на вход элемента И, при этом выход выходного мультиплексора подключен через регистр данных памяти к первому входу входного мультиплексора и к его второму входу непосредственно, третий выход сумматора порога ошибочных битов слов выведен на сигнал «авария», а второй выход сумматора по модулю два подключен ко второму входу входного мультиплексора 9.

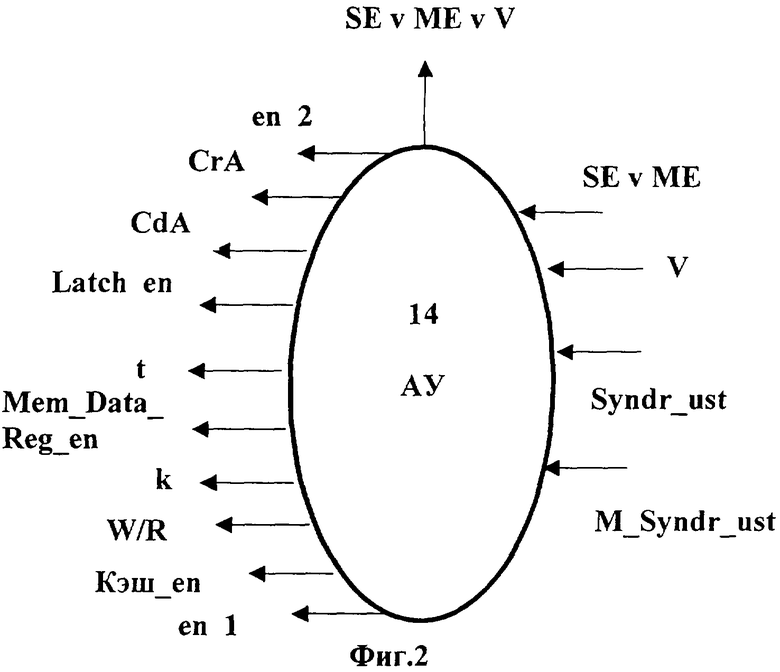

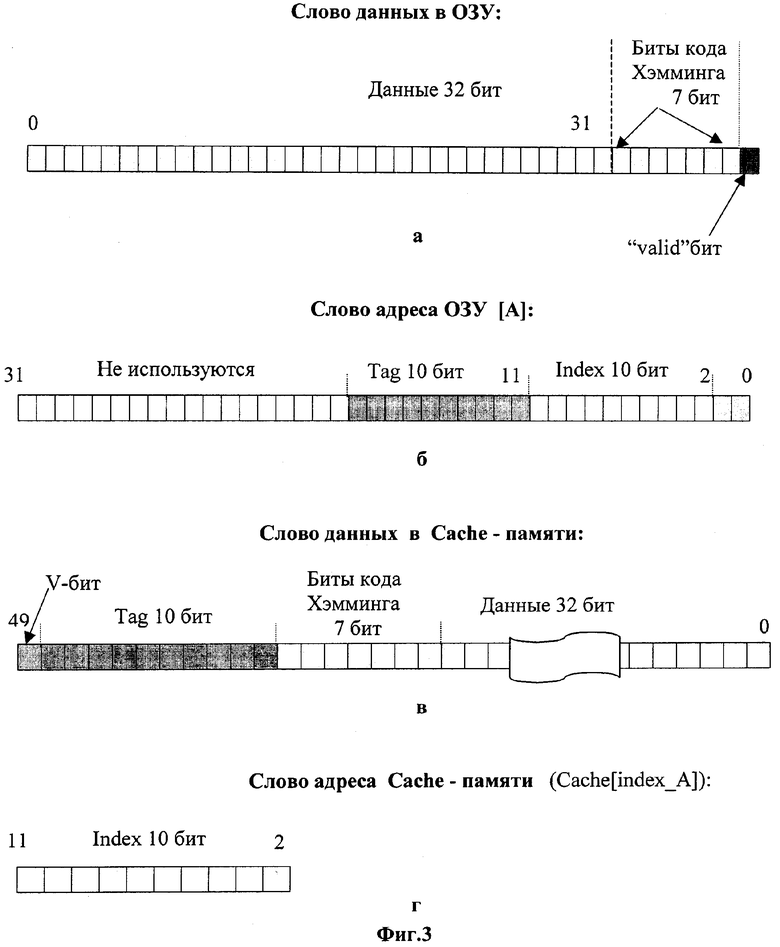

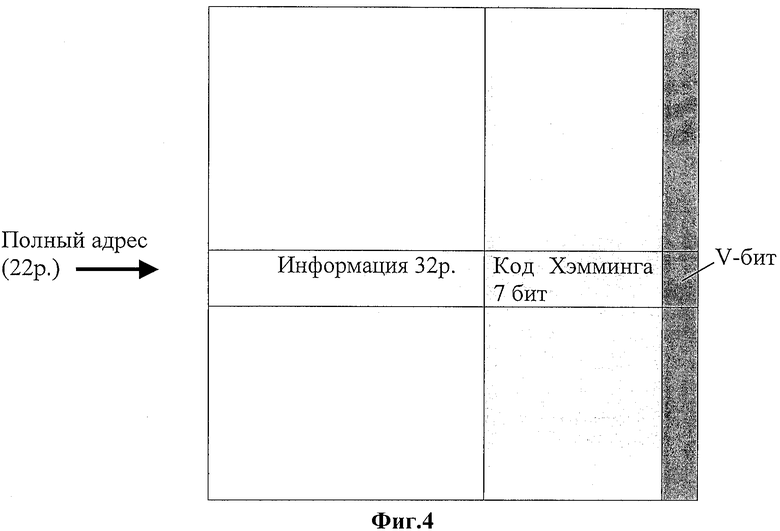

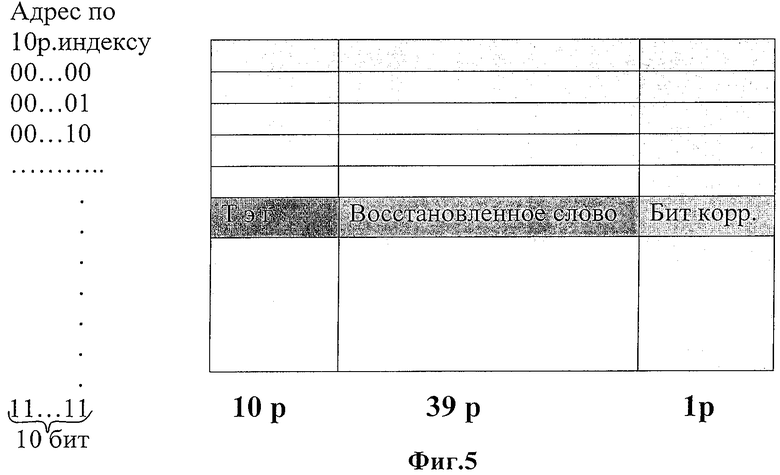

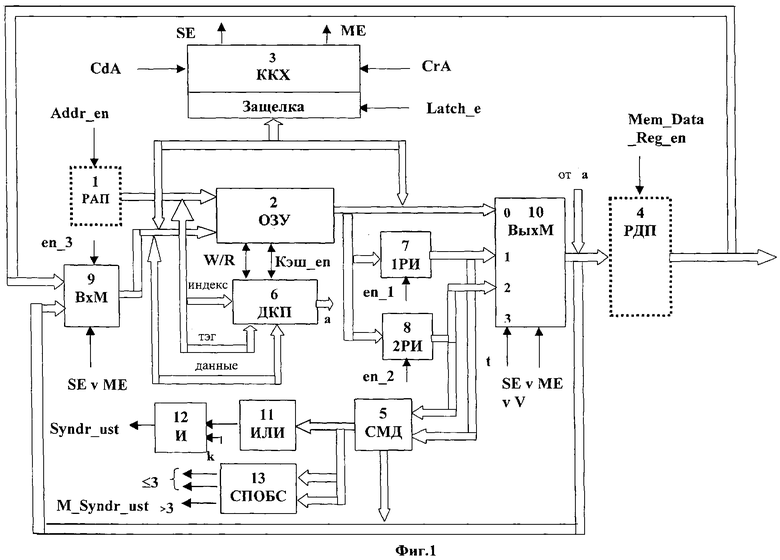

На фиг.1 представлена структурная схема оперативного запоминающего устройства с высокой степенью отказоустойчивости; на фиг.2 - автомат управления; на фиг.3 представлена структура данных контроллера кода Хэмминга, где а - Слово данных в избыточном ОЗУ, б - Слово адреса избыточного ОЗУ, в - Слово данных в диагностической кэш-памяти, г - Слово адреса диагностической кэш-памяти; на фиг.4 - ячейка памяти, отвечающая 22-разрядному адресу в избыточном ОЗУ; на фиг.5 - формат слова в диагностической кэш-памяти.

Оперативное запоминающее устройство с высокой степенью отказоустойчивости (фиг.1) содержит регистр адреса памяти 1 (РАП), избыточное оперативное запоминающее устройство 2 (ОЗУ), снабженное кодом Хэмминга, контроллер кода Хэмминга 3 (ККХ), регистр данных памяти 4 (РДП), сумматор по модулю два 5 (СМД), вычисляющий синдром устойчивой ошибки, диагностическую кэш-память 6 (ДКП) емкостью порядка 1 Кслово, первый 7 (1РИ) и второй 8 (2РИ) регистры-инверторы, входной мультиплексор 9 (В×М) на два направления и выходной мультиплексор 10 (ВыхМ) на три направления, элемент ИЛИ 11, элемент И 12, сумматор порога ошибочных битов слова 13 (СПОБС) и автомат управления 14 (АУ). Блоки 5, 7, 8, 9, 10, 11, 12, 13 вместе с автоматом управления 14 по сути составляют второй контроллер памяти. Адресные входы диагностической кэш-памяти 6 подсоединены к индексной части адреса слова памяти избыточного ОЗУ 2, а входы данных диагностической кэш-памяти 6 подсоединены к слову данных ОЗУ 2 и к тэговой части адреса слова памяти ОЗУ 2, входы управления кэш-памятью 6 соединены с входами управления ОЗУ 2, выход диагностической кэш-памяти 6 подсоединен в выходу выходного мультиплексора 10, входы регистров-инверторов 7, 8 подсоединены к шине данных ОЗУ 2 и к нулевому направлению выходного мультиплексора 10, а выходы регистров-инверторов 7 и 8 подсоединены соответственно к первому и второму направлениям выходного мультиплексора 10 и к входам сумматора по модулю два 5, выходы которого подключены к многовходовому элементу ИЛИ 11 и ко входам сумматора 13, выход элемента ИЛИ 11 подсоединен ко входу элемента И 12. Выход мультиплексора 10 подключен через регистр данных памяти 4 по шине данных к первому входу мультиплексора 9 и к его второму входу непосредственно. Выходы контроллера кода Хэмминга 3 (SE v ME), бита корректности слова избыточного ОЗУ 2 (V), элемента И 12 (Syndr_ust) и два выхода сумматора порога ошибочных битов слова 13 (M_Syndr_ust) подключены ко входам автомата управления 14. Третий выход сумматора порога ошибочных битов слова 13 выведен на сигнал «авария». Второй выход сумматора по модулю два 5 подключен ко второму входу входного мультиплексора 9. Выходы автомата управления 14 подключены соответственно к управляющим входам контроллера кода Хэмминга 3 (CdA, CrA, Latch_en), регистров-инверторов 7 и 8 (en_1, en_2), регистра данных памяти 4 (Mem Data Reg_en), регистра адреса памяти 1 (Addr_en), входного 9 (SE v ME, en_3) и выходного 10 (SE v ME v V, t) мультиплексоров, элемента И 12 (k), избыточного ОЗУ 2 и диагностической кэш-памяти 6 (W/R, Кэш_en).

Автомат управления 14 (фиг.2) предназначен для выдачи циклической последовательности управляющих сигналов, зависящей от значений, принимаемых при считывании из избыточного ОЗУ 2 контрольными сигналами SE, ME, Syndr_ust, M Syndr_ust. Автомат управления 14 синтезируется по стандартным методам на основе управляющей таблицы 1. Управляющие сигналы с выхода автомата управления 14:

SE (single error) - одиночная ошибка;

ME (multiple error) - кратная ошибка;

V (valid) - считываемое из ОЗУ корректное слово;

CrA - разрешение коррекции;

CdA - разрешение кодирования;

Latch_en - защелка разрешена;

Mem_Data Reg_en - выдача данных на шину разрешена;

Addr_en - разрешение выдачи адреса;

t - управляющий сигнал мультиплексора 10;

W/R - сигнал записи/чтения;

Кэш_en - разрешение работы с диагностической кэш-памятью;

k - фаза тактового сигнала.

Сигналы обратной связи, поступающие на вход автомата управления 14:

Syndr_ust - наличие устойчивого отказа;

M_Syndr_ust>3 (восстановление не гарантировано) или «авария»;

SE, МБ, V - см. выше.

Устройство работает следующим образом.

Автомат управления 14 создает последовательность управляющих сигналов на управляющих входах контроллера кода Хэмминга 3 (CrA, CdA, Latch_en), разрешения выдачи содержимого первого 7 (en_1) и второго 8 (en_2) регистров-инверторов, регистра данных памяти 4 (Mem_Data Reg_en), регистра адреса памяти 1 (Addr_en), входного 9 (SE v ME, en_3) и выходного 10 (SE v ME v V, t) мультиплексоров, избыточного ОЗУ 2 и диагностической кэш-памяти 6 (W/R, Кэш_en), и элемента И 12 (k).

Оперативное запоминающее устройство с высокой степенью отказоустойчивости исходно загружено данными (или командными кодами): информационными и контрольными разрядами. Для информации, загружаемой в память в процессе работы (если это - данные), контроллер кода Хэмминга 3 добавляет избыточные контрольные биты. При считывании из памяти тот же контроллер 3 проверяет правильность хранения информации в памяти и сигнализирует о возникших ошибках. В качестве контроллера кода Хэмминга 3 могут быть использованы EDAC-контроллеры (Error Deletion And Correction - обнаружение и коррекция ошибок), которые давно и многократно описаны в литературе, например [1], и широко применяются в компьютерах повышенной надежности. Следует отметить, что известные EDAC- контроллеры генерируют синдром ошибки и два управляющих сигнала SE (single error - одиночная ошибка) и ME (multiple error - кратная ошибка). Пользуясь этой информацией, они способны обнаруживать появление одиночной и двойной ошибки при хранении или считывании и скорректировать одиночную ошибку. При этом кратная ошибка, в частности двойная, рассматривается как невосстановимая катастрофическая, требующая прерывания работы и обращения на уровень операционной системы. Повышение корректирующей способности по сравнению с известными EDAC-контроллерами за счет расширения мощности кода представляет значительные трудности и в промышленных системах применяется крайне редко.

В предлагаемом устройстве, как и в прототипе, расширение корректирующей способности достигается за счет временной и алгоритмической избыточности и работает по отношению к устойчивым отказам в памяти. Это расширение оказывается возможным благодаря цепям выработки сигналов Syndr_ust и M_Syndr_ust (блоки 5, 7, 8, 9, 10, 11, 12, 13), которые вместе с автоматом управления 14 по сути составляют второй контроллер памяти и который по получению сигнала ошибки от контроллера кода Хэмминга 3 реализует проверку на присутствие устойчивых отказов в битах считанного слова. При этом в изобретении достигается незначительная задержка на три-четыре цикла обращения к статической памяти при первом обнаружении контроллером кода Хэмминга 3 отказавшей ячейки памяти. Второй контроллер памяти восстановит корректное значение ошибочного слова и запишет его в небольшую дополнительную память, работающую в режиме «инверсного кэш», которую мы условно назвали диагностической кэш-памятью 6.

Введение кэш-памяти 6 для целей диагностики и восстановления корректной информации на физическом уровне (конечно, в другом информационном носителе, здесь - в кэш-памяти) является одним из центральных моментов изобретения, поскольку традиционное использование кэш-памяти в компьютерах преследует совершенно другие цели, а именно согласование быстродействия процессора и главной памяти. Если в ЭВМ эффективность кэш-технологии проявляется при преимущественной по времени работе процессора с кэш-памятью (не менее 70% времени), а не с ОЗУ, то в изобретении обращение к диагностической кэш-памяти производится только в случае запроса к отказавшей ячейке памяти, т.е. достаточно редко. При втором и последующих обращениях по адресу этой ошибочной ячейки в ОЗУ она будет считываться на шину памяти не из ОЗУ, а из кэш-памяти, не внося заметных задержек в работу системы.

Главное преимущество введения диагностической кэш-памяти 6 для хранения восстановленной информации перед многочисленными другими способами введения резервной памяти - это применение механизма отображения очень большого адресного пространства основного ОЗУ 2 (десятки MB) на сравнительно небольшое (порядка 1 KB) адресное пространство диагностической кэш-памяти. Этот механизм был, по существу, единственным революционным изобретением в ЭВМ, поскольку именно он вносит основной вклад в быстродействие современных ЭВМ с динамическим ОЗУ, и он был отработан до совершенства. В изобретении механизмы реализации отказоустойчивой памяти также очень близки к механизмам работы кэш-памяти. Они «прозрачны» для пользователя, как и наличие кэш-памяти, о существовании которой многие пользователи даже не подозревают.

В изобретении расширение корректирующей способности достигается за счет выработки дополнительных управляющих переменных Syndr_ust, M_Syndr_ust, которые вместе с переменными SE и ME позволяют реализовать управляющую таблицу 1.

0

0

1

0

Считать исправным.

1

1

0

0

Исправимо только перезаписью из другой грани.

1

1

1

0

Прежде всего выясняется - произошел сбой, устойчивый отказ или их комбинация. Процедура проверки [4] дана ниже. Реакция автомата управления 14 показана в 5-м столбце таблицы 1.

Если процедура определила, что имеет место устойчивый отказ, то второй контроллер памяти восстанавливает правильное значение считанной ячейки, которое и используется для продолжения работы. Задержка будет порядка нескольких команд и двух обращений к ОЗУ 2.

Процедура восстановления от устойчивого отказа осуществляется следующим образом.

Предположим, при считывании из ОЗУ 2 получен сигнал отказа (т.е. сработал контроллер кода Хэмминга 3). В память ОЗУ 2 (когда-то ранее!) была записана информация X0X1X2...Xk...Xn-1. Однако при хранении (или при считывании) возникла ошибка в k-ом разряде, вместо Xk стало  . Схема проверки обнаружила при считывании эту ошибку и взвела соответствующий триггер. Итак, считано:

. Схема проверки обнаружила при считывании эту ошибку и взвела соответствующий триггер. Итак, считано:

a: X0X1X2... ...Xn-1.

...Xn-1.

Сохраним это значение на регистре 7. Проинвертируем поразрядно все считанное слово:

b:  .

.

Запишем проинвертированное слово назад в память по тому же адресу и считаем его на другой регистр 8:

с:  .

.

Поскольку k-ый разряд в памяти неисправен, он опять исказит при хранении и считывании записываемое Xk в  .

.

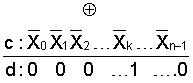

Далее сравним по модулю два слова b и с:

b:

В результате получен синдром отказавшего разряда. Сложим этот синдром по модулю два с первоначально считанным словом a:

В результате получено правильное значение считываемого слова. Восстановление всегда происходит корректно, если в слове устойчивый одиночный отказ.

Сложнее дело с двойными отказами. Двойные отказы устойчивого типа и смешанные отказы типа (одновременных) одного сбоя и одного отказа могут восстанавливаться неправильно. Это происходит, когда одна ошибка активно проявляется, а вторая - не проявляется, т.к. совпадает в момент срабатывания контроля с правильным значением в этом разряде. Однако в самом важном случае двойного отказа, когда оба отказа активно проявляются, они корректно восстанавливаются приведенным алгоритмом.

Легко проверить, что, если был не устойчивый отказ, а сбой, то согласно алгоритму, синдром окажется нулевым, т.е. не укажет номера сбойного разряда, но засвидетельствует, что устойчивого отказа - нет. Поэтому, если структура зафиксированного двойного отказа - это двойной сбой, то восстановить слово не представляется возможным иначе как через перезапись из корректного источника. Алгоритм, не найдя устойчивых отказов в слове, укажет на необходимость перезаписи из надежного источника.

Если двойной отказ, замеченный контролем по Хэммингу, имеет структуру из одного устойчивого и одного сбоя (одновременно), то согласно изложенному алгоритму (он «увидит» только устойчивый отказ) будет изменено на правильное значение в разряде устойчивого отказа, а сбойный разряд - алгоритмом будет «не замечен». В результате слово окажется с одной ошибкой в этом бите, но это будет замечено и правильно восстановлено уже контроллером кода Хэмминга 3 и записано в диагностическую кэш-память 6, поскольку туда перезаписываются все слова с устойчивыми отказами.

Если при двойном отказе один из них активно проявляется, а другой - скрытый, то согласно алгоритму будут исправлены значения в обоих разрядах, причем в одном (активном) правильно, а в скрытом отказе - неправильно. Однако, хотя кратность отказа не изменится (проявление отказа останется одиночным), но уже контроллер кода Хэмминга 3 исправит оставшийся одиночный отказ, и корректное слово будет переписано в диагностическую кэш-память 6.

Подобное двухстадийное восстановление корректного значения с помощью второго контроллера памяти возможно и в более сложных случаях трехкратных отказов, которые раньше не поддавались восстановлению. Эти случаи относятся к строкам таблицы 1, в которых SE=ME=1. Если в тройном отказе все отказы устойчивые и активно проявляющиеся, то информация восстанавливается правильно и переписывается в диагностическую кэш-память 6. Если в тройном устойчивом отказе два отказа - активно проявляющиеся, а один - скрытый, то информация восстанавливается правильно и также переписывается в кэш-память 6. Если в тройном отказе два отказа устойчивых и активно проявляющиеся, а один - сбой, то информация восстанавливается вторым контроллером памяти правильно и также переписывается в кэш-память 6. В более сложном случае тройного отказа, когда один отказ - активно проявляется, а два других - скрытые (см. предпоследнюю строку таблицы 1), срабатывает одностадийное восстановление: второй контроллер памяти разрешит контроллеру кода Хемминга 3 исправить значение «активного» ошибочного разряда и записать корректное слово в кэш-память 6. Однако при числе сбойных разрядов более одного восстановление контроллером кода Хэмминга 3 невозможно, в этом аварийном случае необходима перепись правильного значения из корректного источника.

Ввиду малого объема предполагаемых отказавших ячеек (никак не больше 0,5-1,0 Кслов) "диагностический кэш" может быть спроектирован на сравнительно дорогой, но существенно более надежной элементной базе - например, КМОП КНС или на флэш-памяти (хотя в последней нужно преодолеть некоторые трудности с записью информации). Поскольку обращение к кэш-памяти - в среднем редкое событие, то задержки из-за снижения быстродействия в среднем незначительны. Такое решение может оказаться на порядки экономичнее и эффективнее, чем применение дорогой элементной базы для всей памяти, как в современных зарубежных системах в технологии "SOS" (кремний на сапфире "_Silicon_on_Sapphfire").

Рассмотрим архитектуру отказоустойчивой памяти.

Структура данных контроллера кода Хэмминга 3 представлена на фиг.3 (а, 6, в, г), где обозначены переменные:

SE (=1 одиночная ошибка);

ME (=1 кратная ошибка);

valid (=0 истина);

cache_valid_bit (=1 истина);

Syndr_ust (=1 наличие устойчивого отказа);

M_Syndr_ust>3 (восстановление не гарантировано).

Контроллер кода Хэмминга 3 исправляет при считывании одиночный «мягкий» сбой или одиночный устойчивый отказ, однако в последнем случае он не восстанавливает истинную информацию, хранящуюся в памяти. Поэтому появление второй ошибки в слове, имеющей как устойчивый, так и сбойный характер, приводит к отказу грани (канала) или системы. Для противодействия появлению двойных ошибок в слове памяти в космических бортовых машинах (фирма Honeywell в бортовом компьютере RH-32SBC, фирма ВАЕ) применяют специальный «фоновый» контроллер-чистильщик памяти (ОЗУ) от одиночных «мягких» сбоев. Для флеш-памяти использование подобного контроллера гораздо проблематичнее из-за трудностей оперативной перезаписи. Эта процедура снижает вероятность накопления кратных сбоев, но, тем не менее, появление в грани (канале) ячейки с кратными (две и больше) устойчивыми неисправностями (или в комбинации: устойчивая+сбой) вызывают отказ грани. Появление таких отказов в каждой грани вызовет полный отказ системы. С целью преодоления этого недостатка предлагается расширить возможности известного контроллера кода Хэмминга.

Предполагается, что в ОЗУ 2 информация хранится в виде 32 информационных бит +7 проверочных бит расширенного кода Хэмминга +1 бит «корректности слова», итого 40 бит. Контроллер кода Хэмминга 3 вырабатывает две переменных: одноразрядные флаги SE (одиночная ошибка) и ME (кратная ошибка). Во втором контроллере памяти вырабатываются еще две переменные: «Syndr_ust», «M_Syndr_ust>3» и «бит корректности» или, короче, «valid» бит, последнее - это еще один разряд памяти (см. выше). Резервируются три вспомогательных регистра R1temp, R2temp, Rsynd.

Рассмотрим на примере ОЗУ емкостью 4MB с адресацией слова памяти в 22 разряда. Поскольку при защите памяти кодом Хэмминга адресация производится к словам, а не к байтам памяти, то в предположении общего объема памяти 4MB это будет 1М слово. Слово адреса разбивается на две части, имеющие свои имена: index (биты 2÷11, т.е. 0 и 1 биты, дающие адресацию к байту, не используются) и tag адреса - старшие 10 битов. Index и tag - это переменные, с которыми будет манипулировать второй контроллер памяти.

Вводится дополнительная память Cache с адресным пространством, определяемым полем Index (10 бит) в адресе (т.е. на 1024 слова), с шириной слов, равной 32+7+|tag|+«cache_valid_bit»=32+7+10+1=50 бит.

При чтении слова из ОЗУ 2 дополнительный бит слова (бит корректности слова памяти) используется в качестве управляющего. Если этот бит равен 0, то чтение производится из основной памяти (ОЗУ 2), если он равен 1, то чтение аппаратно перенаправляется к диагностической кэш-памяти 6 по адресу индекса.

Второй контроллер памяти проектируется в соответствии с рассмотренной ранее управляющей таблицей 1. Как уже упоминалось, расширение корректирующей способности предлагаемой в изобретении новой памяти достигается за счет выработки вторым контроллером памяти дополнительных управляющих переменных Syndr_ust, M_Syndr_ust, которые вместе с переменными SE и ME позволяют реализовать управляющую таблицу 1.

Переадресация отказавших ячеек памяти происходит следующим образом.

Для устойчивых отказов, используя информацию от контроллера кода Хэмминга 3 и второго контроллера памяти, можно восстановить искаженное значение в считанном слове и переадресовать это слово в дополнительную (резервную) память - диагностическую кэш-память 6 для хранения восстановленного исправного значения. Всякое обращение к искаженному слову по старому адресу должно автоматически переадресовываться к новому расположению этого слова без заметного увеличения времени обращения.

В прототипе (и, вообще, во многих современных системах) информационное восстановление реализуют через резервную (зеркальную) память, не отличающуюся от основной по своим объемам. Подобный подход для космических бортовых систем выглядит крайне дорогостоящим. Здесь предлагается другая идея - резервная память очень маленькой емкости. Ведь надо отдавать себе отчет, что устойчиво отказавших ячеек не может быть очень много, сравнительно со всей памятью. Отмечалось, что сейчас их, в худшем случае, единицы. Наша задача - постараться увеличить это критическое значение до нескольких десятков или сотен. В предлагаемом варианте механизмы реализации отказоустойчивой памяти отчасти напоминают механизмы работы обычной кэш-памяти, только в обратной («инверсной») последовательности с другими системными целями, и реализуя другие алгоритмы.

Рассмотрим основные действия второго контроллера памяти.

Пусть 22-разрядному адресу в ОЗУ 2 отвечает некоторая ячейка памяти, (фиг.4):

- если при считывании из ОЗУ 2 по указанному адресу обнаружен одиночный сбой, то он корректируется контроллером кода Хемминга 3 и правильное значение поступает в интерфейс и перезаписывается в ОЗУ 2 по старому адресу;

- если при считывании из ОЗУ 2 обнаружен кратный сбой, то корректная информация восстанавливается переписью из другой грани (из корректного источника);

- если при считывании из ОЗУ 2 обнаружен одиночный отказ (т.е. SE=1, МЕ=0), который оказался устойчивым, то информация восстанавливается контроллером кода Хемминга 3, а второй контроллер памяти разрешает ее поступление в интерфейс. Одновременно эта информация+тег адреса (10 бит) заносятся в диагностическую кэш-память 6 по адресу индекса (10 бит), а в ОЗУ 2 по полному адресу - в бит корректности заносится 1;

- если при считывании из ОЗУ 2 обнаружен устойчивый двойной отказ (т.е. SE=0, ME=1), то информация восстанавливается вторым контроллером памяти, дополнительно проверяется контроллером кода Хемминга 3 и поступает в интерфейс. Одновременно эта информация+тег адреса (10 бит) заносятся в диагностическую кэш-память 6 по адресу индекса (10 бит), а в ОЗУ 2 по полному адресу - в бит корректности заносится 1;

- если при считывании из ОЗУ 2 бит корректности оказывается равным 1, то обращение (аппаратно) производится к диагностической кэш-памяти 6.

Формат слова в диагностической кэш-памяти 6 приведен на фиг.5.

Дальнейшая работа происходит следующим образом. При очередном обращении по адресу неисправной ячейки срабатывает контроль за битом некорректности в ОЗУ 2. Одновременно может сработать и контроль по коду Хэмминга. В этом случае чтение слова аппаратно повторяется из диагностической кэш-памяти 6 по адресу индекса. Считывается собственно информация и тэг, который сравнивается с полем тэга полного адреса. При совпадении последних чтение считается корректным. Несовпадение тэгов может произойти в исключительно маловероятном случае, при существовании второй неисправной ячейки ОЗУ 2, имеющей тот же индекс, но отличный тэг. Учитывая, что всего неисправных ячеек - единицы, максимум - несколько десятков, - а различных индексов - более тысячи, такое совпадение маловероятно. С другой стороны, возможность наличия двух неисправных ячеек в ОЗУ 2 с одинаковыми индексами можно учесть, проектируя кэш-память не как 1-ассоциативный (как рассмотрено выше), а как 2-ассоциативный, допускающий совпадение индексов у адресов двух неисправных ячеек. Разрядность такой кэш-памяти в два раза больше. Последний механизм применяется в кэш-памяти практически всех компьютеров, правда, для других целей и потому в другой процедуре.

В целом предложение выглядит как «инверсный кэш», если сравнивать с реальной кэш-технологией. В последней процессор пробует читать информацию по полученному адресу сначала из кэш-памяти, и если ее там не находит, то обращается в ОЗУ 2. Здесь же информация сначала считывается из ОЗУ 2 и, если она корректна, то все идет как обычно. Если обнаруживается, что ячейка ОЗУ 2 неисправна, то правильная информация считывается из диагностического кэш-памяти 6. Учитывая, что отказов не должно быть «много», то заметных потерь производительности не будет. В то же время можно позволить себе «роскошь» иметь сотню отказавших ячеек, сохраняя работоспособность системы.

Источники информации

1. С.L.Chen and M.Y.Hsiao, "Error-Correcting Codes for Semiconductor Memory Applications: A State of-the-Art Review," IBM Journal Res.& Dev., vol. 28, No.3, pp.124-134, March 1984. (Применение корректирующих кодов в полупроводниковой памяти: обзор современного состояния.)

2. D.С.Bossen, A.Kitamorn, К.F.Reick, and M.S.Floyd, "Fault-tolerant design of the IBM pSeries 690 system using POWER4 processor technology," IBM Journal Res.&Dev., vol. 46, No.1, pp.77-86, January 2002. (Отказоустойчивое проектирование системы IBM pSeries 690 на базе технологии процессора POWER4).

3. Патент РФ №2211492, кл. G11С 29/00, G06F 11/07, 2003 г.

4. Коррекция устойчивых ошибок в ОЗУ методом двойной инверсии, Computer Design, v.20, No 12, 1981, pp.187-190.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1985 |

|

SU1277214A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Многопроцессорная вычислительная система | 1987 |

|

SU1792540A3 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

Изобретение относится к области автоматики и вычислительной техники и предназначено для повышения отказоустойчивости оперативного запоминающего устройства в управляющих системах реального времени. Техническим результатом является значительное повышение отказоустойчивости по отношению к одиночным, двойным и тройным комбинированным отказам и сбоям, расширение функциональных возможностей. Устройство содержит регистр адреса памяти (1), избыточное ОЗУ (2), снабженное кодом Хэмминга, контроллер кода Хэмминга (3), регистр данных памяти (4), сумматор по модулю два (5), диагностическую кэш-память (6), два регистра - инверторами (7) и (8), входной (9) и выходной (10) мультиплексоры, элемент ИЛИ (11), элемент И (12), сумматор порога ошибочных битов слова (13) и автомат у правления (14). 5 ил., 1 табл.

Оперативное запоминающее устройство с высокой степенью отказоустойчивости, содержащее избыточное ОЗУ, снабженное кодом Хэмминга, контроллер кода Хэмминга, регистр адреса памяти, регистр данных памяти и сумматор по модулю два, отличающееся тем, что дополнительно содержит диагностическую кэш-память, первый и второй регистры-инверторы, входной и выходной мультиплексоры соответственно на два и три направления, элемент ИЛИ, элемент И, сумматор порога ошибочных битов слова и автомат управления, при этом адресные входы диагностической кэш-памяти подсоединены к индексной части адреса слова памяти ОЗУ, а входы данных диагностической кэш-памяти подсоединены к слову данных ОЗУ и к тэговой части адреса слова памяти ОЗУ, входы управления кэш-памятью соединены с входами управления ОЗУ, входы регистров-инверторов подсоединены к шине данных ОЗУ и к нулевому направлению выходного мультиплексора, выход диагностической кэш-памяти подсоединен к выходу выходного мультиплексора, а выходы регистров-инверторов подсоединены к первому и второму направлениям выходного мультиплексора и к сумматору по модулю два, выходы которого подключены к многовходовому элементу ИЛИ и ко входам сумматора порога ошибочных битов слова, выход элемента ИЛИ подсоединен ко входу элемента И, выходы элемента И, контроллера кода Хэмминга, бита корректности слова ОЗУ и два выхода сумматора порога ошибочных битов слов подключены ко входу автомата управления, управляющие выходы которого заведены на входы управления контроллера кода Хэмминга, управляющие входы мультиплексоров, вход разрешения выдачи содержимого вышеуказанных регистров, на входы Чт./Зап. ОЗУ и диагностической кэш-памяти, и на вход элемента И, при этом выход выходного мультиплексора подключен через регистр данных памяти к первому входу входного мультиплексора и к его второму входу непосредственно, третий выход сумматора порога ошибочных битов слов выведен на сигнал «авария», а второй выход сумматора по модулю два подключен ко второму входу входного мультиплексора.

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2211492C2 |

| US 6892275 A (QUANTUM CORPORATION), 10.05.2005 | |||

| CHEN C.L., HSIAO M.Y | |||

| Error-Correcting Codes for Semiconductor Memory Applications: A State of-the-Art Review | |||

| - IBM Journal Res.&Dev., vol | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

Авторы

Даты

2008-06-20—Публикация

2005-12-29—Подача