Изобретение относится к автоматике и вычислительной техники и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности.

Наиболее близким по технической сущности является мажоритарный блок элементов «3 из 5» [1], при этом вариант реализации им мажоритарной функции «3 из 5» содержит первый элемент первый элемент ИЛИ (14), первый элемент И (15), второй элемент ИЛИ (16), второй элемент И (17), третий элемент И (18), третий элемент ИЛИ (19), четвертый элемент ИЛИ (20), четвертый элемент И (21), пятый элемент ИЛИ (22), пятый элемент И (23), выход первого элемента ИЛИ (14) подсоединен к первому входу третьего элемента И (18), выход первого элемента И (15) подсоединен к первому входу третьего элемента ИЛИ (19), выход второго элемента ИЛИ (16) подсоединен к второму входу третьего элемента И (18), выход второго элемента И (17) подсоединен к второму входу третьего элемента ИЛИ (19), выход которого подсоединен к первому входу четвертого элемента И (21) и к первому входу четвертого элемента ИЛИ (20), выход третьего элемента И (18) подсоединен к второму входу четвертого элемента И (21) и к второму входу четвертого элемента ИЛИ (20), выход которого подсоединен к первому входу пятого элемента И (23), выход четвертого элемента И (21) подсоединен к первому входу пятого элемента ИЛИ (22), выход которого подсоединен к второму входу пятого элемента И (23), выход которого является выходом 24 устройства.

Недостатком данного устройства является невозможность переключения на режимы реализации им мажоритарной функции «2 из 3» при функционировании адаптивных вычислительных систем.

Задача изобретения - создать устройство, обеспечивающее при отказах в системе переключение блока элементов «3 из 5» на режим реализации им мажоритарной функции «2 из 3» при функционировании адаптивных вычислительных систем.

Это решение достигается тем, что в адаптивный мажоритарный блок элементов «3 из 5», содержащий первый элемент ИЛИ (14), первый элемент И (15), второй элемент ИЛИ (16), второй элемент И (17), третий элемент И (18), третий элемент ИЛИ (19), четвертый элемент ИЛИ (20), четвертый элемент И (21), пятый элемент ИЛИ (22), пятый элемент И (23), выход первого элемента ИЛИ (14) подсоединен к первому входу третьего элемента И (18), выход первого элемента И (15) подсоединен к первому входу третьего элемента ИЛИ (19), выход второго элемента ИЛИ (16) подсоединен к второму входу третьего элемента И (18), выход второго элемента И (17) подсоединен к второму входу третьего элемента ИЛИ (19), выход которого подсоединен к первому входу четвертого элемента И (21) и к первому входу четвертого элемента ИЛИ (20), выход третьего элемента И (18) подсоединен к второму входу четвертого элемента И (21) и к второму входу четвертого элемента ИЛИ (20), выход которого подсоединен к первому входу пятого элемента И (23), выход четвертого элемента И (21) подсоединен к первому входу пятого элемента ИЛИ (22), выход которого подсоединен к второму входу пятого элемента И (23), выход которого является выходом 24 устройства, введены группа шестых элементов И (11, … 15), группа элементов сложения по mod 2 (21, … 25) группа седьмых элементов И (31, … 35), группа шестых элементов ИЛИ (41, … 45), элемент задержки (5), группа первых схем сравнения (61, … 65), группа счетчиков (71, … 75), регистр (8), группа вторых схем сравнения (91, … 95) седьмой элемент ИЛИ (10), первый триггер (11), группа восьмых элементов И (121, … 125), группа вторых триггеров (131, … 135), входы (271, … 275) устройства подсоединены к одноименным первым входам шестых элементов И (11, … 15), выходы которых подсоединены к одноименным первым входам шестых элементов ИЛИ (41, … 45), выходы седьмых элементов И (31, … 35), подсоединены к одноименным вторым входам шестых элементов ИЛИ (41, … 45), выход шестого элемента ИЛИ (41) подсоединен к первым входам первого элемента ИЛИ (14), первого элемента И (15) и к первому входу первой схемы сравнения (61), выход шестого элемента ИЛИ (42) подсоединен к вторым входам первого элемента ИЛИ (14), первого элемента И (15) и к первому входу первой схемы сравнения (62), выход шестого элемента ИЛИ (43) подсоединен к первым входам второго элемента ИЛИ (16), второго элемента И (17) и к первому входу первой схемы сравнения (63), выход шестого элемента ИЛИ (44) подсоединен к вторым входам второго элемента ИЛИ (16), второго элемента И (17) и к первому входу первой схемы сравнения (64), выход шестого элемента ИЛИ (45) подсоединен к второму входу пятого элемента ИЛИ (22) и к первому входу первой схемы сравнения (65), вход (28) устройства подсоединен к вторым входам элементов И (11, … 15) и к входу элемента задержки (5), выход которого подсоединен к вторым входам элементов первых схем сравнения (61, … 65), третьи входы которых подсоединены к выходу пятого элемента И (23), выходы первых схем сравнения (61, … 65) подсоединены к одноименным первым входам счетчиков (71, … 75), выходы которых подсоединены к одноименным первым входам вторых схем сравнения (91, … 95), вторые входы которых подсоединены к выходу регистра (8), выходы вторых схем сравнения (91, … 95) подсоединены к одноименным входам седьмого элемента ИЛИ (10), к входам вторых триггеров (131, … 135) и к первым входам восьмых элементов И (121, … 125), выходы вторых триггеров (131, … 135) подсоединены к одноименным третьим входам шестых элементов И (11, … 15), к первым входам элементов сложения по mod 2 (21, … 25) и седьмых элементов И (31, … 35), выход седьмого элемента ИЛИ (10) подсоединен к входу первого триггера (11), выход которого является выходом (25) устройства и подсоединен к вторым входам восьмых элементов И (121, … 125), выходы которых подсоединены к одноименным вторым входам счетчиков (71, … 75), вход 26 устройства подсоединен к второму входу элемента сложения по mod 2 (21), выход которого подсоединен к второму входу седьмого элемента И (31) и к второму входу элемента сложения по mod 2 (22), выход которого подсоединен к второму входу седьмого элемента И (32) и к второму входу элемента сложения по mod 2 (23), выход которого подсоединен к второму входу седьмого элемента И (33) и к второму входу элемента сложения по mod 2 (24), выход которого подсоединен к второму входу седьмого элемента И (34) и к второму входу элемента сложения по mod 2 (25), выход которого подсоединен к второму входу седьмого элемента И (35).

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

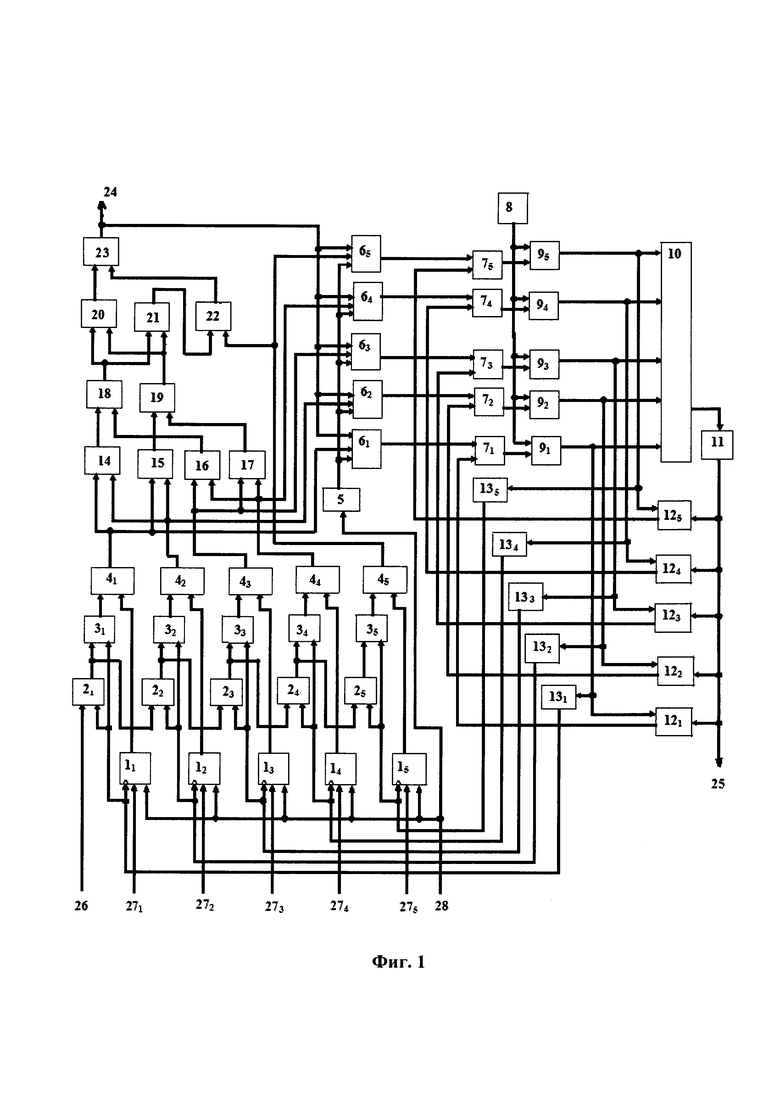

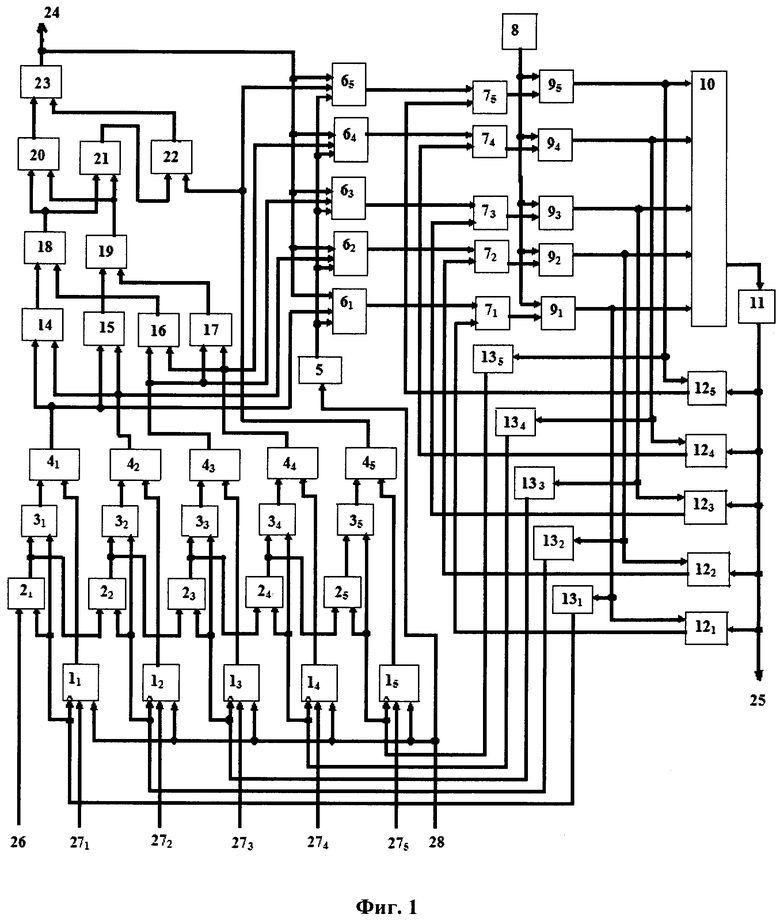

Сущность изобретения поясняется чертежом. На фиг. 1 представлено схематичное изображение адаптивного мажоритарного блока элементов «3 из 5».

Сущность изобретения поясняется чертежом. Адаптивный мажоритарный блок элементов «3 из 5» (фиг. 1) содержит: группа элементов И (11, … 15), группа элементов сложения по mod 2 (21, … 25), группа элементов И (31 … 35), группа элементов ИЛИ (41, … 45), элемент задержки (5), группа схем сравнения (61, … 65), группа счетчиков (71, … 75), регистр 8, группа схем сравнения (91, … 95), элемент ИЛИ (10), триггер (11), группа элементов И (121, … 125), группа триггеров (131, … 135), элемент ИЛИ (14), элемент И (15), элемент ИЛИ (16), элемент И (17), элемент И (18), элемент ИЛИ (19), элемент ИЛИ (20), элемент И (21), элемент ИЛИ (22), элемент И (23).

Устройство работает следующим образом. В исходном состоянии все триггеры (131, … 135), триггер (11), счетчики (71, … 75) находятся в нулевом состоянии. На регистре 8 хранится код допустимого числа сбоев в работе любого канала в мажоритируемой системе.

Во время работы устройства на его входы (271-275) поступает произвольная последовательность двоичных символов «1» и «0» значений x1, x2, х3, x4 и x5 соответственно, а на вход (28) устройства поступает последовательность тактирующих импульсов.

При отсутствии устойчивого отказа в каналах устройства нулевой сигнал с выхода триггера (11) подается на вторые входы группы элементов И (121, … 125). Нулевые сигналы с выходов триггеров (131, … 135) подаются на третьи инверсные входы группы элементов И (11, … 15).

Адаптивный мажоритарный блок элементов «3 из 5» может работать в двух режимах. При наличии единичного сигнала на входе 26 устройство работает в дублированном режиме по схеме И. При наличии нулевого сигнала на входе 26 устройство работает в режиме по схеме ИЛИ двух оставшихся исправных каналов.

1). При наличии единичного сигнала на входе 26 устройства на втором входе элемента сложения по mod 2 (21) будет единичный сигнал, а на всех первых входах элементов сложения по mod 2 (21, … 25) при отсутствии неисправностей в системе будут нулевые сигналы с выходов триггеров (131, … 135). Поэтому на выходе элемента сложения по mod 2 (21) будет единичный сигнал, который подается на вторые входы элемента сложения по mod 2 (22) и элемента И (31). Аналогично далее с выхода элементов сложения по mod 2 (22, … 24) единичные сигналы подаются на вторые входы элементов сложения по mod 2 (23, … 25) и элементов И (32, … 35). На первом входе элементов И (31, … 35) будет нулевой сигнал с выхода одноименного триггера (131, … 135). Поэтому на выходе элемента И (31, … 35) будет нулевой сигнал, который подается на первый вход элемента ИЛИ (41, … 45), с выхода которого сигнал подается на первые входы одноименных элементов сравнения (61, … 65) и соответствующие входы мажоритарного блока элементов (14)-(23).

При наличии сигнала на тактирующем входе 28 устройства сигналы с входов (271, … 215) устройства поступают на первые входы элементов И (11, … 15), с выходов которых сигнал подается на первые входы одноименных элементов ИЛИ (41, … 45), с выходов которых сигналы подаются на первые входы одноименных схем сравнения (61, … 65) и входы мажоритарного блока элементов «3 из 5», выполненного на группе элементов (14)-(23).

Элементы (14)-(23) реализуют функцию F мажоритарного органа «три из пяти» в соответствии с таблицей 1.

Элемент задержки 5 задерживает сигнал на время надежного срабатывания элементов И (11-15), И (31-35), ИЛИ (41-45), элементов сложения по mod 2 (21, … 25), после чего он подается на вторые входы схем сравнения (61-63).

При выходе из строя одного из пяти каналов (например, первого, то есть x1=0, а x2=х3=x4=x5=1) на выходе мажоритарного блока (24) будет единичный сигнал, который подается на третьи входы всех схем сравнения (61, … 65). Единичный сигнал с выхода соответствующей схемы сравнения (61) поступает на счетный вход одноименного счетчика (71).

При достижении счетчиком (71) порогового значения, хранящимся на регистре 8, на выходе соответствующей схемы сравнения (91) появляется единичный сигнал, который устанавливает в единичное состояние одноименный триггер (131), подается на одноименный вход элемента ИЛИ 10 и на первый вход одноименного элемента И (121). С выхода элемента ИЛИ 10 единичный сигнал устанавливает триггер (И) в единичное состояние. Единичный сигнал с выхода триггера (11) поступает на вторые входы элементов И (121-125).

При появлении единичного сигнала на выходе триггера (131) он подается на инверсный вход элемента И (11), на первый вход элемента сложения по mod 2 (21) и на первый вход одноименного элемента И (31), на другой вход которого подается нулевой сигнал с выхода элемента сложения по mod 2 (21). Поэтому на выходе элемента И (31) будет нулевой сигнал, который подается на второй вход элемента ИЛИ (41). На первом входе элемента ИЛИ (41) с выхода элемента И (11) будет нулевой сигнал, поэтому на выходе элемента ИЛИ (41) будет нулевой сигнал.

Нулевой сигнал с выхода элемента сложения по mod 2 (21) подается на второй вход элемента сложения по mod 2 (22), затем нулевой сигнал с выхода элемента сложения по mod 2 (22) подается на второй вход элемента сложения по mod 2 (23) и далее по цепочке до элемента сложения по mod 2 (25).

Единичный сигнал с выхода элемента И (121) сбрасывает счетчик (71) в нулевое состояние.

При выходе из строя еще одного из пяти каналов (например, второго, то есть x1=x2=0, а х3=x4=x5=1) на выходе мажоритарного блока (24) будет единичный сигнал, который подается на третьи входы всех схем сравнения (61, … 65). Единичный сигнал с выхода соответствующей схемы сравнения (62) поступает на счетный вход одноименного счетчика (72).

При достижении счетчиком (72) порогового значения, хранящимся на регистре 8, на выходе соответствующей схемы сравнения (92) появляется единичный сигнал, который устанавливает в единичное состояние одноименный триггер (132), подается на одноименный вход элемента ИЛИ 10 и на второй вход одноименного элемента И (122).

При появлении единичного сигнала на выходе триггера (132) он подается на инверсный вход элемента И (12), на первый вход элемента сложения по mod 2 (22) и на первый вход одноименного элемента И (32), на второй вход которого подается единичный сигнал с выхода элемента сложения по mod 2 (22). Поэтому на выходе элемента И (32) будет единичный сигнал, который подается на второй вход элемента ИЛИ (42). На первом входе элемента ИЛИ (42) с выхода элемента И (b) будет нулевой сигнал, поэтому на выходе элемента ИЛИ 42 будет единичный сигнал, который подается на соответствующий вход мажоритарного блока элементов «3 из 5», выполненного на группе элементов (14)-(23).

Единичный сигнал с выхода элемента сложения по mod 2 (22) подается на второй вход элемента сложения по mod 2 (23) и далее по цепочке до элемента сложения по mod 2 (25). Единичный сигнал с выхода элемента И (122) сбрасывает счетчик (72) в нулевое состояние.

Таким образом, при последовательном выходе из строя двух из пяти каналов мажоритарный блок элементов «3 из 5» будет работать исправно. Однако, на один неисправный вход мажоритарного блока «3 из 5» будет подаваться нулевой сигнал, а на второй вход - единичный сигнал, исходная система мажоритарный блок элементов «3 из 5» автоматически перестраивается в систему мажоритарный блок элементов «2 из 3», что существенно повышает достоверность обрабатываемой мажоритарном блоком информации.

2). При наличии нулевого сигнала на входе 26 устройства на втором входе элемента сложения по mod 2 (21) будет нулевой сигнал, и на всех первых входах элементов сложения по mod 2 (21, … 25) при отсутствии неисправностей в системе будут нулевые сигналы с входов триггеров (131, … 135). Поэтому на выходе элемента сложения по mod 2 (21) будет нулевой сигнал, который подается на вторые входы элемента сложения по mod 2 (22) и элемента И (31). Аналогично далее с выхода элементов сложения по mod 2 (22, … 24) нулевые сигналы подаются на вторые входы элементов сложения по mod 2 (23, … 25) и элементов И (32, … 35).

При наличии сигнала на тактирующем входе 28 устройства сигналы с входов (271, … 275) поступают на первые входы элементов И (11 … 15), с выходов которых сигнал подается на первые входы одноименных элементов ИЛИ (41, … 45), с выходов которых сигналы подаются на первые входы одноименных схем сравнения (61, … 65) и мажоритарного блока элементов «3 из 5» выполненного на группе элементов (14)-(23). Элементы (14)-(23) реализуют функцию F мажоритарного органа «три из пяти» в соответствии с таблицей 1.

При выходе из строя одного из пяти каналов (например, первого, то есть x1=0, а x2=х3=x4=x5=1) на выходе мажоритарного блока (24) будет единичный сигнал, который подается на третьи входы всех схем сравнения (61, … 65). Единичный сигнал с выхода соответствующей схемы сравнения (61) поступает на счетный вход одноименного счетчика (71).

При достижении счетчиком (71) порогового значения, хранящимся на регистре 8, на выходе соответствующей схемы сравнения (91) появляется единичный сигнал, который устанавливает в единичное состояние одноименный триггер (131), подается на одноименный вход элемента ИЛИ (10) и на первый вход одноименного элемента И (121). С выхода элемента ИЛИ (10) единичный сигнал устанавливает триггер (11) в единичное состояние. Единичный сигнал с выхода триггера (11) поступает на вторые входы элементов И (121-125).

При появлении единичного сигнала на выходе триггера (131) он подается на инверсный вход элемента И (11), на первый вход элемента сложения по mod 2 (21) и на первый вход одноименного элемента И (31), на второй вход которого подается единичный сигнал с выхода элемента сложения по mod 2 (21). Поэтому на выходе элемента И (31) будет единичный сигнал, который подается на второй вход элемента ИЛИ (41). На первом входе элемента ИЛИ (41) с выхода элемента И (11) будет нулевой сигнал, поэтому на выходе элемента ИЛИ (41) будет единичный сигнал, который подается на соответствующий вход мажоритарного блока элементов «3 из 5» выполненного на группе элементов (14)-(23).

Единичный сигнал с выхода элемента сложения по mod 2 (21) подается на второй вход элемента сложения по mod 2 (22), затем единичный сигнал с выхода элемента сложения по mod 2 (22) подается на второй вход элемента сложения по mod 2 (23) и далее по цепочке до элемента сложения по mod 2 (25).

Единичный сигнал с выхода элемента И (121) сбрасывает счетчик (71) в нулевое состояние.

При выходе из строя еще одного из пяти каналов (например, второго, то есть x1=х2=0, а х3=x4=x5=1) на выходе мажоритарного блока (24) будет единичный сигнал, который подается на третьи входы всех схем сравнения (61, … 65). Единичный сигнал с выхода соответствующей схемы сравнения (62) поступает на счетный вход одноименного счетчика (72).

При достижении счетчиком (72) порогового значения, хранящимся на регистре 8, на выходе соответствующей схемы сравнения (92) появляется единичный сигнал, который устанавливает в единичное состояние одноименный триггер (132), подается на одноименный вход элемента ИЛИ (10) и на первый вход одноименного элемента И (122).

При появлении единичного сигнала на выходе триггера (132) он подается на инверсный вход элемента И (12), на первый вход элемента сложения по mod 2 (22) и на первый вход одноименного элемента И (32), на второй вход которого подается нулевой сигнал с выхода элемента сложения по mod 2 (22). Поэтому на выходе элемента И (32) будет нулевой сигнал, который подается на второй вход элемента ИЛИ (42). На первом входе элемента ИЛИ (42) с выхода элемента И (12) будет нулевой сигнал, поэтому на выходе элемента ИЛИ (42) будет нулевой сигнал, который подается на соответствующий вход мажоритарного блока элементов «3 из 5» выполненного на группе элементов (14)-(23).

Единичный сигнал с выхода элемента сложения по mod 2 (21) подается на второй вход элемента сложения по mod 2 (22), затем нулевой сигнал с выхода элемента сложения по mod 2 (22) подается на второй вход элемента сложения по mod 2 (23) и далее по цепочке до элемента сложения по mod 2 (25).

Единичный сигнал с выхода элемента И (122) сбрасывает счетчик (72) в нулевое состояние.

Таким образом, при последовательном выходе из строя двух из пяти каналов мажоритарный блок элементов «3 из 5» будет работать исправно. Однако, на один неисправный вход мажоритарного блока будет подаваться единичный сигнал, а на второй вход - нулевой сигнал, исходная система мажоритарный блок элементов «3 из 5» автоматически перестраивается в систему мажоритарный блок элементов «2 из 3», что существенно повышает достоверность обрабатываемой мажоритарным блоком информации.

1. АС №2701461, кл. G06F 12/14, 2017.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный мажоритарный блок элементов "n и более из (2n-1)" | 2023 |

|

RU2818031C1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Устройство для моделирования графика работы сотрудников учреждения | 2018 |

|

RU2685980C1 |

| Устройство для решения задачи о назначениях | 2016 |

|

RU2613523C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ГРАФИКА РАБОТЫ СОТРУДНИКОВ УЧРЕЖДЕНИЯ | 2011 |

|

RU2480827C1 |

| Адаптивный мажоритарный блок элементов "5 и более из 9" | 2019 |

|

RU2716061C1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ГРАФИКА РАБОТЫ СОТРУДНИКОВ УЧРЕЖДЕНИЯ | 2010 |

|

RU2434273C1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство для определения характеристик связности ориентированного графа | 1983 |

|

SU1133596A1 |

Изобретение относится к автоматике и вычислительной техники и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности. Техническим результатом является повышение достоверности обрабатываемой информации за счет переключения на режим реализации функции «2 из 3» при отказах в системе. Устройство содержит шесть элементов ИЛИ, пять элементов И, три группы элементов И, группу элементов ИЛИ, группу элементов сложения по mod 2, две группы схем сравнения, группу счетчиков, регистр, триггер, группу триггеров, элемент задержки. 1 ил., 1 табл.

Адаптивный мажоритарный блок элементов «3 из 5», содержащий первый элемент ИЛИ (14), первый элемент И (15), второй элемент ИЛИ (16), второй элемент И (17), третий элемент И (18), третий элемент ИЛИ (19), четвертый элемент ИЛИ (20), четвертый элемент И (21), пятый элемент ИЛИ (22), пятый элемент И (23), выход первого элемента ИЛИ (14) подсоединен к первому входу третьего элемента И (18), выход первого элемента И (15) подсоединен к первому входу третьего элемента ИЛИ (19), выход второго элемента ИЛИ (16) подсоединен к второму входу третьего элемента И (18), выход второго элемента И (17) подсоединен к второму входу третьего элемента ИЛИ (19), выход которого подсоединен к первому входу четвертого элемента И (21) и к первому входу четвертого элемента ИЛИ (20), выход третьего элемента И (18) подсоединен к второму входу четвертого элемента И (21) и к второму входу четвертого элемента ИЛИ (20), выход которого подсоединен к первому входу пятого элемента И (23), выход четвертого элемента И (21) подсоединен к первому входу пятого элемента ИЛИ (22), выход которого подсоединен к второму входу пятого элемента И (23), выход которого является выходом 24 устройства, отличающийся тем, что в него введены группа шестых элементов И (11, … 15), группа элементов сложения по mod 2 (21, … 25), группа седьмых элементов И (31, … 35), группа шестых элементов ИЛИ (41, … 45), элемент задержки (5), группа первых схем сравнения (61, … 65), группа счетчиков (71, … 75), регистр (8), группа вторых схем сравнения (91, … 95) седьмой элемент ИЛИ (10), первый триггер (11), группа восьмых элементов И (121, … 125), группа вторых триггеров (131, … 135), входы (271, … 275) устройства подсоединены к одноименным первым входам шестых элементов И (11, … 15), выходы которых подсоединены к одноименным первым входам шестых элементов ИЛИ (41, … 4s), выходы седьмых элементов И (31, … 35), подсоединены к одноименным вторым входам шестых элементов ИЛИ (41, … 45), выход шестого элемента ИЛИ (41) подсоединен к первым входам первого элемента ИЛИ (14), первого элемента И (15) и к первому входу первой схемы сравнения (61), выход шестого элемента ИЛИ (42) подсоединен к вторым входам первого элемента ИЛИ (14), первого элемента И (15) и к первому входу первой схемы сравнения (62), выход шестого элемента ИЛИ (43) подсоединен к первым входам второго элемента ИЛИ (16), второго элемента И (17) и к первому входу первой схемы сравнения (63), выход шестого элемента ИЛИ (44) подсоединен к вторым входам второго элемента ИЛИ (16), второго элемента И (17) и к первому входу первой схемы сравнения (64), выход шестого элемента ИЛИ (45) подсоединен к второму входу пятого элемента ИЛИ (22) и к первому входу первой схемы сравнения (65), вход (28) устройства подсоединен к вторым входам элементов И (11, … 15) и к входу элемента задержки (5), выход которого подсоединен к вторым входам элементов первых схем сравнения (61, … 65), третьи входы которых подсоединены к выходу пятого элемента И (23), выходы первых схем сравнения (61, … 65) подсоединены к одноименным первым входам счетчиков (71, … 75), выходы которых подсоединены к одноименным первым входам вторых схем сравнения (91, … 95), вторые входы которых подсоединены к выходу регистра (8), выходы вторых схем сравнения (91, … 95) подсоединены к одноименным входам седьмого элемента ИЛИ (10), к входам вторых триггеров (131, … 135) и к первым входам восьмых элементов И (121, … 125), выходы вторых триггеров (131, … 135) подсоединены к одноименным третьим входам шестых элементов И (11, … 15), к первым входам элементов сложения по mod 2 (21, … 25) и седьмых элементов И (31, … 35), выход седьмого элемента ИЛИ (10) подсоединен к входу первого триггера (11), выход которого является выходом (25) устройства и подсоединен к вторым входам восьмых элементов И (121, … 125), выходы которых подсоединены к одноименным вторым входам счетчиков (71, … 75), вход 26 устройства подсоединен к второму входу элемента сложения по mod 2 (21), выход которого подсоединен к второму входу седьмого элемента И (31) и к второму входу элемента сложения по mod 2 (22), выход которого подсоединен к второму входу седьмого элемента И (32) и к второму входу элемента сложения по mod 2 (23), выход которого подсоединен к второму входу седьмого элемента И (33) и к второму входу элемента сложения по mod 2 (24), выход которого подсоединен к второму входу седьмого элемента И (34) и к второму входу элемента сложения по mod 2 (25), выход которого подсоединен к второму входу седьмого элемента И (35).

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2701461C1 |

| Мажоритарно-резервированное устройство | 1980 |

|

SU1032600A1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ "ТРИ ИЗ ПЯТИ" | 2016 |

|

RU2628117C1 |

| Мажоритарный блок элементов "два из трех" | 2019 |

|

RU2711726C1 |

| US 5680408 A1, 21.10.1997 | |||

| JP 6342381 A, 13.12.1994. | |||

Авторы

Даты

2022-01-21—Публикация

2021-04-14—Подача