Изобретение относится к автоматике и вычислительной технике и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности функционирования.

Наиболее близким по технической сущности является мажоритарный блок элементов «5 и более из 9» [1].

Недостатком данного устройства является невозможность идентификации часто сбоящего или вышедшего из строя канала при реализации им мажоритарной функции в адаптивных вычислительных системах.

Задача изобретения - создать устройство, обеспечивающее идентификацию часто сбоящего или вышедшего из строя канала при реализации им мажоритарной функции в адаптивных вычислительных системах.

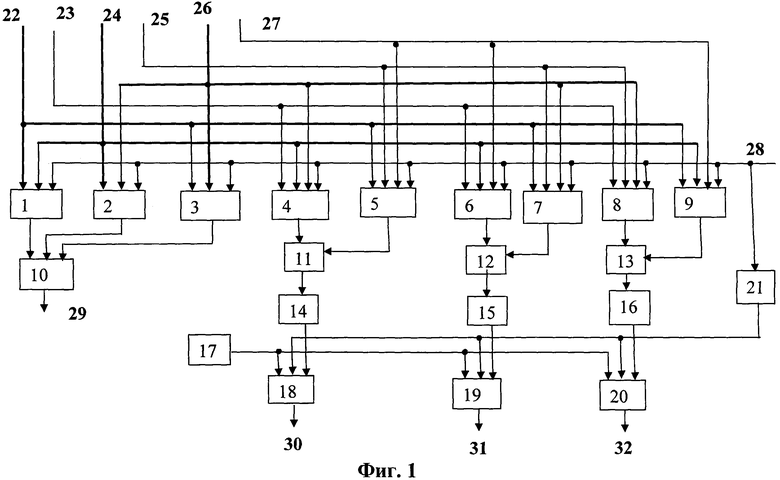

Это решение достигается тем, что в мажоритарный блок, содержащий три элемента И 1, И 2, И 3, первый элемент ИЛИ 10, входы 22 и 24 блока подсоединены к первым двум входам первого элемента И 1, выход которого подсоединен к первому входу первого элемента ИЛИ 10, входы 24 и 26 блока подсоединены к первым двум входам второго элемента И 2, выход которого подсоединен к второму входу первого элемента ИЛИ 10, входы 22 и 26 блока подсоединены к первым двум входам третьего элемента И 3, выход которого подсоединен к третьему входу первого элемента ИЛИ 10, выход которого является первым выходом 29 блока, отличающееся тем, что в него дополнительно включены - четвертый элемент И 4, пятый элемент И 5, шестой элемент И 6, седьмой элемент И 7, восьмой элемент И 8, девятый элемент И 9, второй элемент ИЛИ 11, третий элемент ИЛИ 12, четвертый элемент ИЛИ 13, первый счетчик 14, второй счетчик 15 и третий счетчик 16, регистр 17, первая схема сравнения 18, вторая схема сравнения 19 и третья схема сравнения 20, элемент задержки 21, входы 23, 24 и 26 блока подсоединены к первым трем входам четвертого элемента И 4, выход которого подсоединен к первому входу второго элемента ИЛИ 11, входы 22, 25 и 27 блока подсоединены к первым трем входам пятого элемента И 5, выход которого подсоединен к второму входу второго элемента ИЛИ 11, выход которого подсоединен к входу первого счетчика 14, входы 23, 24 и 27 блока подсоединены к первым трем входам шестого элемента И 6, выход которого подсоединен к первому входу третьего элемента ИЛИ 12, входы 22, 25 и 26 блока подсоединены к первым трем входам седьмого элемента И 7, выход которого подсоединен к второму входу третьего элемента ИЛИ 12, выход которого подсоединен к входу второго счетчика 15, входы 23, 25 и 26 блока подсоединены к первым трем входам восьмого элемента И 8, выход которого подсоединен к первому входу четвертого элемента ИЛИ 13, входы 22, 24 и 27 блока подсоединены к первым трем входам девятого элемента И 9, выход которого подсоединен к второму входу четвертого элемента ИЛИ 13, выход которого подсоединен к входу третьего счетчика 16, вход 28 блока подсоединен к третьим входам элементов И1, И2, И3, к четвертым входам элементов И4, И5, И6, И7, И8, И9, выход регистра 17 подсоединен к первым входам первой 18, второй 19 и третьей 20 схем сравнения, выход первого счетчика 14 подсоединен к второму входу первой схемы сравнения 18, выход которой является вторым выходом 30 блока, выход второго счетчика 15 подсоединен к второму входу второй схемы сравнения 19, выход которой является третьим выходом 31 блока, выход третьего счетчика 16 подсоединен к второму входу третьей схемы сравнения 20, выход которой является четвертым выходом 32 блока, вход элемента задержки 21 подсоединен к входу 28 блока, а выход -к третьим входам схем сравнения 18, 19 и 20.

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

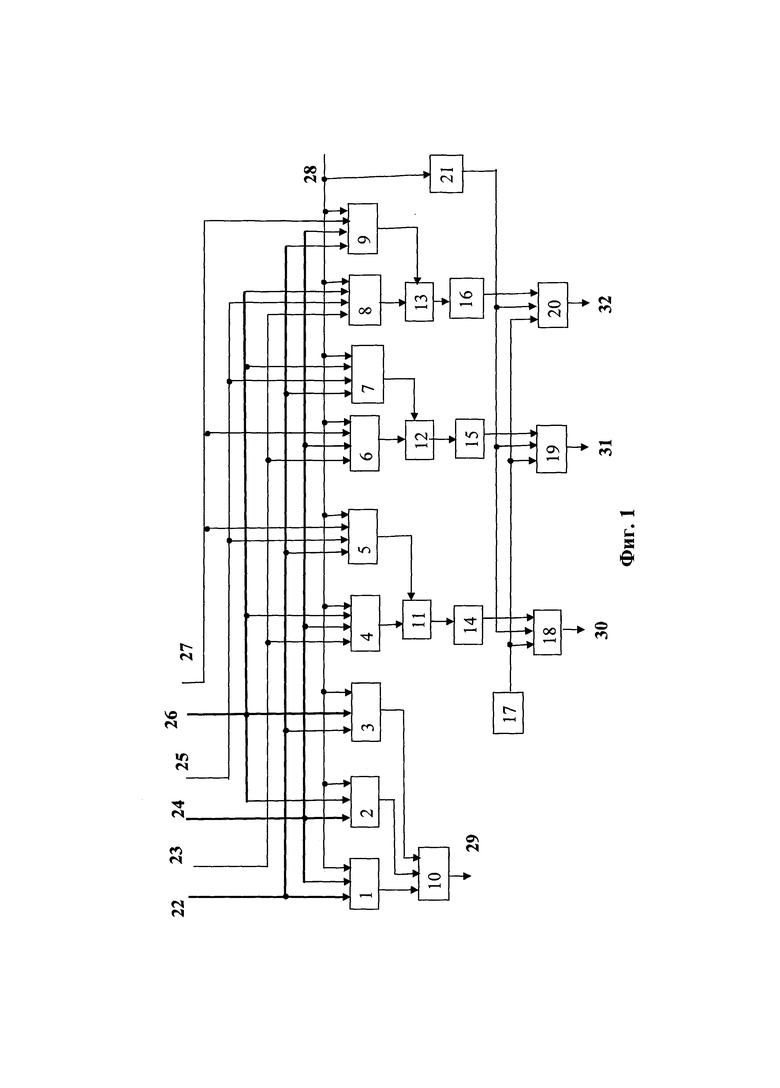

Сущность изобретения поясняется чертежом. На фиг. 1 представлено схематичное изображение предлагаемого блока.

Блок содержит элементы И 1 - И 9, элементы ИЛИ 10 - ИЛИ 13, счетчики 14, 15 и 16, регистр 17, схемы сравнения 18, 19 и 20, входы 21-27, выходы 28-31 устройства. На регистре 17 хранится код допустимого числа сбоев в работе канала в мажоритируемой вычислительной системе.

Во время работы устройства на его входы 21, 23 и 25 поступает произвольная последовательность двоичных символов «1» и «0» значений X1, Х2 и Х3 соответственно, а на входы 22, 24 и 26 устройства поступает произвольная последовательность двоичных символов «1» и «0» инверсных значений  ,

,  и

и  соответственно. На вход 27 устройства поступает последовательность тактирующих импульсов.

соответственно. На вход 27 устройства поступает последовательность тактирующих импульсов.

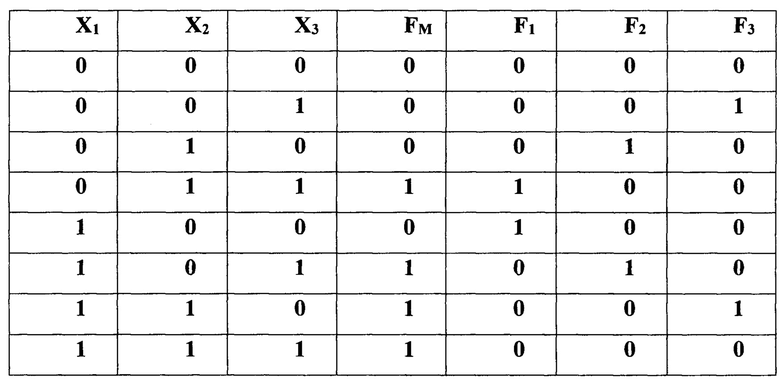

Таблица истинности работы устройства

На выходе устройства 28 появляется сигнал значения FM в соответствии с приведенной таблицей истинности

FM=X2X3∨X1X3∨X1X2

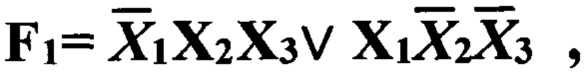

На выходе элемента ИЛИ 11 появляется сигнал значения

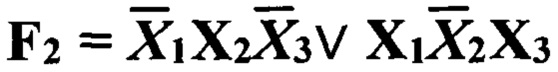

На выходе элемента ИЛИ 12 появляется сигнал значения F2,

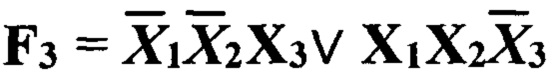

На выходе элемента ИЛИ 13 появляется сигнал значения F3 в соответствии с приведенной таблицей истинности

При достижении счетчиком 14, 15 или 16 значения, хранящимся на регистре 17, на выходе соответствующей схемы сравнения 18, 19 или 20 появляется единичный сигнал тревоги.

Таким образом, мажоритарный блок элементов «два из трех» обеспечивает определение часто сбоящего или вышедшего из строя канала при функционировании высоконадежных вычислительных систем с мажоритированием.

Литература

1. SU №2665226, 2018.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Адаптивный мажоритарный блок элементов "3 из 5" | 2021 |

|

RU2764839C1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1991 |

|

SU1820385A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2023348C1 |

| Устройство для решения задачи о рюкзаке | 2015 |

|

RU2613854C1 |

| Устройство для контроля и реконфигурации резервируемых блоков | 1990 |

|

SU1800456A1 |

| Устройство для контроля параметров | 1990 |

|

SU1742790A1 |

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

Изобретение относится к автоматике и вычислительной техники. Технический результат заключается в обеспечении идентификации часто сбоящего или вышедшего из строя канала при реализации им мажоритарной функции в адаптивных вычислительных системах. Устройство содержит элементы И 1 – И 9, элементы ИЛИ 10 – ИЛИ 13, три счетчика, регистр, три схемы сравнения. 1 ил.

Мажоритарный блок «два из трех», содержащий три элемента И 1, И 2, И 3, первый элемент ИЛИ 10, входы 22 и 24 блока подсоединены к первым двум входам первого элемента И 1, выход которого подсоединен к первому входу первого элемента ИЛИ 10, входы 24 и 26 блока подсоединены к первым двум входам второго элемента И 2, выход которого подсоединен к второму входу первого элемента ИЛИ 10, входы 22 и 26 блока подсоединены к первым двум входам третьего элемента И 3, выход которого подсоединен к третьему входу первого элемента ИЛИ 10, выход которого является первым выходом 29 блока, отличающийся тем, что в него дополнительно включены четвертый элемент И 4, пятый элемент И 5, шестой элемент И 6, седьмой элемент И 7, восьмой элемент И 8, девятый элемент И 9, второй элемент ИЛИ 11, третий элемент ИЛИ 12, четвертый элемент ИЛИ 13, первый счетчик 14, второй счетчик 15 и третий счетчик 16, регистр 17, первая схема сравнения 18, вторая схема сравнения 19 и третья схема сравнения 20, элемент задержки 21, входы 23, 24 и 26 блока подсоединены к первым трем входам четвертого элемента И 4, выход которого подсоединен к первому входу второго элемента ИЛИ 11, входы 22, 25 и 27 блока подсоединены к первым трем входам пятого элемента И 5, выход которого подсоединен к второму входу второго элемента ИЛИ 11, выход которого подсоединен к входу первого счетчика 14, входы 23, 24 и 27 блока подсоединены к первым трем входам шестого элемента И 6, выход которого подсоединен к первому входу третьего элемента ИЛИ 12, входы 22, 25 и 26 блока подсоединены к первым трем входам седьмого элемента И 7, выход которого подсоединен к второму входу третьего элемента ИЛИ 12, выход которого подсоединен к входу второго счетчика 15, входы 23, 25 и 26 блока подсоединены к первым трем входам восьмого элемента И 8, выход которого подсоединен к первому входу четвертого элемента ИЛИ 13, входы 22, 24 и 27 блока подсоединены к первым трем входам девятого элемента И 9, выход которого подсоединен к второму входу четвертого элемента ИЛИ 13, выход которого подсоединен к входу третьего счетчика 16, вход 28 блока подсоединен к третьим входам элементов И 1, И 2, И 3, к четвертым входам элементов И 4, И 5, И 6, И 7, И 8, И 9, выход регистра 17 подсоединен к первым входам первой 18, второй 19 и третьей 20 схем сравнения, выход первого счетчика 14 подсоединен к второму входу первой схемы сравнения 18, выход которой является вторым выходом 30 блока, выход второго счетчика 15 подсоединен к второму входу второй схемы сравнения 19, выход которой является третьим выходом 31 блока, выход третьего счетчика 16 подсоединен к второму входу третьей схемы сравнения 20, выход которой является четвертым выходом 32 блока, вход элемента задержки 21 подсоединен к входу 28 блока, а выход - к третьим входам схем сравнения 18, 19 и 20.

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "5 И БОЛЕЕ ИЗ 9" | 2016 |

|

RU2665226C2 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2013 |

|

RU2533079C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2015 |

|

RU2580801C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2012 |

|

RU2473954C1 |

| US 5383950 A, 17.01.1995. | |||

Авторы

Даты

2020-01-21—Публикация

2019-03-12—Подача