Изобретение относится к области радиотехники, а конкретно к способам и устройствам формирования псевдослучайных сигналов, и может быть использовано при формировании ансамблей псевдослучайных сигналов, используемых в радиоэлектронных системах связи для решения задач защиты информации.

В качестве аналога способа формирования псевдослучайных сигналов рассмотрен патент способ для генерирования псевдослучайной последовательности и способ для кодирования или декодирования потока данных RU 2609098 C2, опубликованный 23.05.2013, в котором последовательность чисел с плавающей запятой xk формируется путем вычисления численного решения x(t) дифференциального уравнения x'=f(x,t) динамической системы, которая будет использоваться для генерирования псевдослучайной последовательности, затем из xk=0,d0d1d2d3…dr…dw⋅10e, (где e - показатель степени, w - длина мантиссы, d0 - старший разряд мантиссы, и dr - некоторый разряд, который вместе с разрядами слева от него в приближении для решения xk совпадает с точным значением решения дифференциального уравнения, f(x,t)) генерируют псевдослучайную последовательность с разрядами di…dr из набора последовательности значений xk, где i - предопределенное целочисленное значение, удовлетворяющее условию 0<i≤r; то есть, используются разряды фактического числа, которые соответствуют следующим требованиям:

- они принадлежат мантиссе,

- они являются разрядами, совпадающими с точным решением xk,

- они не являются старшими.

Выбор из набора xk имеет результатом совокупность значений, которые будут более некоррелированными, когда они будут больше разнесены на временной шкале. Последнее свойство - не являться старшими разрядами фактического числа xk - обеспечивает преимущество генерирования последовательности значений, которые не коррелированы относительно друг друга, в самое короткое возможное время. После устранения зависимости между старшими разрядами получается последовательность, значения которой являются некоррелированными.

В качестве аналога устройства формирования псевдослучайных сигналов рассмотрен патент генератор псевдослучайных чисел RU 2740339 C1, опубликованный 05.03.2020, в котором генератор псевдослучайных чисел, состоящий из N регистров разрядности n, (N-1) блоков сложения в GF(2n), где n>1 - целое, N блоков умножения в GF(2n), причем величина, на которую происходит умножение в (i+1)-м блоке умножения, равна коэффициенту ai характеристического многочлена ϕ(x)=(х+1)λ(х)=xN+aN-1+…+а2х1+а1х+а0, где i=0, 1, 2, …, (N-1), ai∈GF(2n), λ(х) - многочлен степени (N-1), примитивный над GF(2n), выходы N-го регистра соединены со входами всех блоков умножения, выходы (j+1)-х блоков умножения и выходы j-х регистров соединены соответственно с первыми и вторыми входами j-x блоков сложения, выходы которых соединены со входами (j+1)-х регистров, где j=1, 2, (N-1), причем устройство дополнительно содержит блок управляющих воздействий и N-й блок сложения в GF(2n), первые входы которого подключены к выходам первого блока умножения, а выходы соединены со входами первого регистра, вторые входы N-го блока сложения и третьи входы j-x блоков сложения подключены к соответствующим выходам блока управляющих воздействий.

Наиболее близкими к предполагаемым изобретениям является способ генерирования псевдослучайных сигналов на основе системы Лоренца и устройство для его осуществления, описанные в статье "Practical Implementation of a Pseudo-Random Signal Generator Based on the Lorenz System Realized on FPGA", опубликованной в сборнике материалов конференции Systems of Signal Synchronization Generating and Processing in Telecommunications (SYNCHROINFO) 2019. Данные способ и устройство выбраны в качестве прототипа заявленных изобретений.

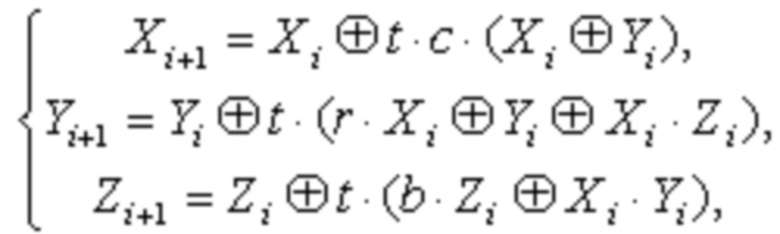

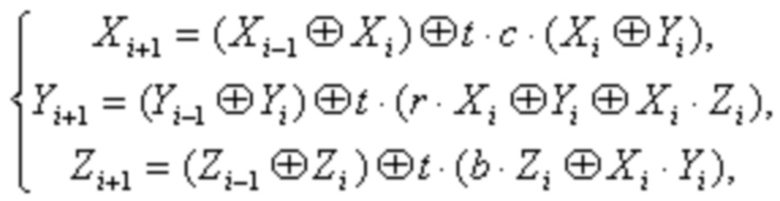

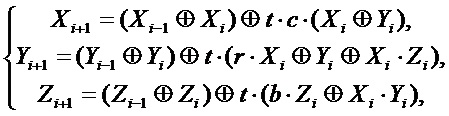

Характеристика прототипа способа, описанного в статье, опубликованной в 2019 заключается в том, что псевдослучайный сигнал формируется путем вычисления трех уравнений модифицированной динамической системы Лоренца:

где ⊕ - операция исключающее «ИЛИ», ⋅ - операция умножения, которая производится над полем Галуа GF(2p), где р - целое число больше единицы, Xi, Yi, Zi - текущие отсчеты псевдослучайных сигналов, двоичные p-разрядные числа, Xi+1, Yi+1, Zi+1 - вычисляемые отсчеты псевдослучайных сигналов, двоичные p - разрядные числа, t - шаг интегрирования динамической системы, двоичное p - разрядное число, с - число Прандтля, двоичное p - разрядное число, r - число Рэлея, двоичное p - разрядное число, b - геометрический параметр динамической системы, двоичное p - разрядное число, для формирования псевдослучайных сигналов задают начальные отсчеты псевдослучайных сигналов модифицированной системы X0, Y0, Z0, шаг интегрирования динамической системы t, число Прандтля c, число Рэлея r, геометрический параметр динамической системы b и примитивный полином, образующий поле Галуа g(2p) - двоичное p+1 - разрядное число, i - номер текущего отсчета, целое число от нуля до количества отсчетов формируемого псевдослучайного сигнала N, затем при формировании псевдослучайного сигнала производится генерация отсчетов путем вычисления N отсчетов псевдослучайного сигнала, где N - целое число больше 1, результатом каждого вычисления является следующий отсчет псевдослучайного сигнала, особенностью данного генератора является то, что при вычислениях все арифметические операции выполняются над полем Галуа GF(2p), результатом вычислений являются псевдослучайные сигналы, описываемые последовательностями:

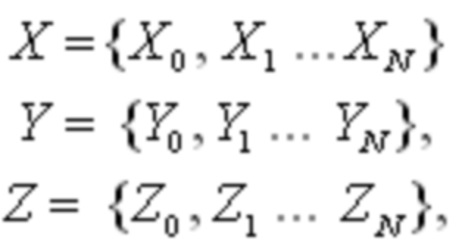

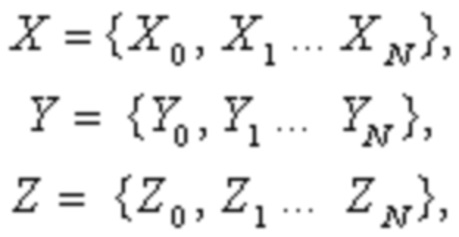

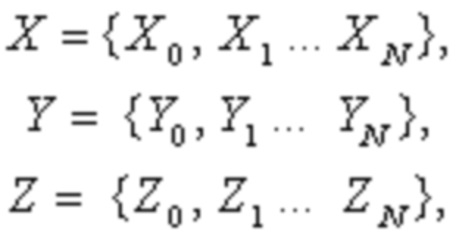

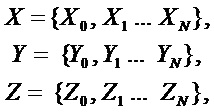

где X, Y, Z - последовательности отсчетов формируемых псевдослучайных сигналов.

Характеристика прототипа устройства, описанного в статье, опубликованной в 2019, заключается в том, что устройство формирования псевдослучайных сигналов содержит восемь умножителей в GF(2p), четыре регистра, пять элементов исключающее «ИЛИ» и один трехвходовый элемент исключающее «ИЛИ», имеющие вход для подачи тактовых сигналов, при этом первый вход устройства является входом для подачи текущего отсчета Xi псевдослучайного сигнала, второй вход устройства является входом для подачи текущего отсчета Yi псевдослучайного сигнала, третий вход устройства является входом для подачи текущего отсчета Zi псевдослучайного сигнала, первый выход устройства является выходом для съема вычисляемого отсчета Xi+1 псевдослучайного сигнала, второй выход устройства является выходом для съема вычисляемого отсчета Yi+1 псевдослучайного сигнала, третий выход устройства является выходом для съема вычисляемого отсчета Zi+1 псевдослучайного сигнала, первый и второй входы первого элемента исключающее «ИЛИ» соединены со вторым и первым входами устройства соответственно, выход первого элемента исключающее «ИЛИ» соединен со вторым входом первого умножителя в GF(2p), первый вход которого соединен с выходом первого регистра, выход первого умножителя в GF(2p) соединен со вторым входом второго умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход второго умножителя в GF(2p) соединен с первым входом второго элемента исключающее «ИЛИ», второй вход которого соединен с первым входом устройства, выход второго элемента исключающее «ИЛИ» соединен с первым выходом устройства, первый вход третьего умножителя в GF(2p) соединен с выходом третьего регистра, второй вход третьего умножителя в GF(2p) соединен с первым входом устройства, выход третьего умножителя в GF(2p) соединен с первым входом трехвходового элемента исключающее «ИЛИ», второй вход которого соединен с выходом четвертого умножителя в GF(2p), первый и второй входы которого соединены с первым и третьим входами устройства соответственно, третий вход трехвходового элемента исключающее «ИЛИ» соединен со вторым входом устройства, выход трехвходового элемента исключающее «ИЛИ» соединен со вторым входом пятого умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход пятого умножителя в GF(2p) соединен с первым входом третьего элемента исключающее «ИЛИ», второй вход которого соединен со вторым входом устройства, выход третьего элемента исключающее «ИЛИ» соединен со вторым выходом устройства, первый и второй входы шестого умножителя в GF(2p) соединены с первым и вторым входами устройства соответственно, выход шестого умножителя в GF(2p) соединен с первым входом четвертого элемента исключающее «ИЛИ», второй вход которого соединен с выходом седьмого умножителя в GF(2p), первый вход которого соединен с выходом четвертого регистра, второй вход седьмого умножителя в GF(2p) соединен с третьим входом устройства, выход четвертого элемента исключающее «ИЛИ» соединен со вторым входом восьмого умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход восьмого умножителя в GF(2p) соединен с первым входом пятого элемента исключающее «ИЛИ», второй вход которого соединен с третьим входом устройства, выход пятого элемента исключающее «ИЛИ» соединен с третьим выходом устройства.

Недостатком данных способа и устройства является небольшой период повторения псевдослучайных сигналов, обусловленный ограниченным количеством состояний поля Галуа.

Техническая проблема заключается в неизменном исходном полиноме, образующем поле Галуа, что приводит к установлению периодичности и последующей генерации сигнала в пределах установившегося периода последовательности.

Технический результат предлагаемого способа формирования псевдослучайных сигналов и устройство для его осуществления заключается в увеличении периода повторяемости псевдослучайного сигнала и достигается условным переключением полинома, образующего поле, на следующий примитивный полином поля из заранее отобранного ансамбля примитивных полиномов.

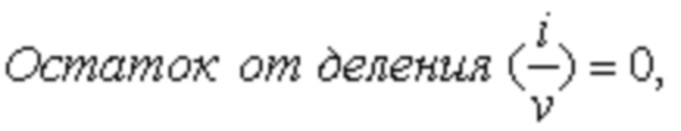

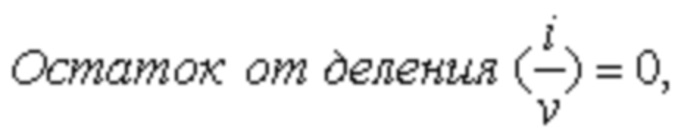

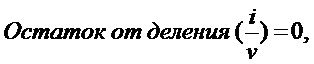

Технический результат в способе формирования псевдослучайных сигналов, заключающемся в формировании псевдослучайных сигналов путем вычисления трех уравнений модифицированной динамической системы Лоренца в арифметике над полем Галуа GF(2p), достигается тем, что при формировании псевдослучайных сигналов, когда остаток от деления номера формируемого отсчета сигнала i на период смены примитивного полинома образующего поле Галуа v, равен нулю согласно уравнению:

производят изменение примитивного полинома, образующего поле Галуа gj(2p), где p - целое число больше единицы, на следующий примитивный полином, образующий поле Галуа gj+1(2p), из отобранного ансамбля полиномов {g0(2p), g1(2p), …, gj+1(2p) … gK(2p)}, где j меняется от нуля до К, где К - целое число равное количеству полиномов в отобранном ансамбле, далее формируют псевдослучайные сигналы описываемые последовательностями:

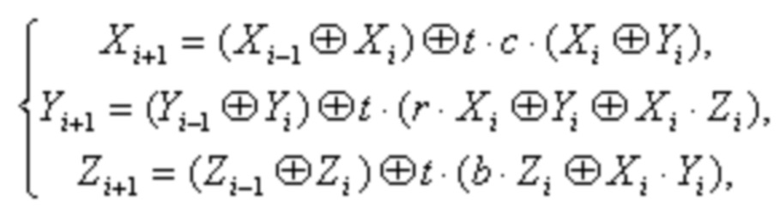

путем вычисления трех уравнений модифицированной динамической системы Лоренца:

где

⊕ - операция исключающее «ИЛИ»,

⋅ - операция умножения, которая производится над полем Галуа GF(2p),

р - целое число больше единицы,

X, Y, Z - последовательности отсчетов псевдослучайных сигналов,

Xi+1, Yi+1, Zi+1 - вычисляемые отсчеты псевдослучайных сигналов, двоичные p-разрядные числа,

Xi, Yi, Zi - текущие отсчеты псевдослучайных сигналов, двоичные p-разрядные числа,

Xi-1, Yi-1, Zi-1 - предыдущие отсчеты псевдослучайных сигналов, двоичные p-разрядные числа, в начальный момент времени предыдущие отсчеты псевдослучайных сигналов Xi-1, Yi-1, Zi-1 системы равны нулю,

N - количество отсчетов формируемого псевдослучайного сигнала, целое число больше единицы,

i - номер формируемого отсчета, целое число от единицы до количества отсчетов формируемого псевдослучайного сигнала N,

K - количество примитивных полиномов, образующих поле Галуа, целое число больше нуля,

j - номер используемого примитивного полинома, образующего поле Галуа, целое число от нуля до количества примитивных полиномов, образующих поле Галуа K,

t - шаг интегрирования динамической системы, двоичное p-разрядное число,

с - ослабляющий коэффициент, двоичное p-разрядное число,

r - усиливающий коэффициент, двоичное p-разрядное число,

b - геометрический параметр динамической системы, двоичное p-разрядное число,

v - период смены примитивного полинома образующего поле Галуа, целое число больше единицы, меньше N,

gj(2p) - примитивный полином, образующий поле Галуа, двоичное p+1-разрядное число,

GF(2p) - поле Галуа, образованное полиномом степени p.

Технический результат в устройстве формирования псевдослучайных сигналов, содержащем пять элементов исключающее «ИЛИ», восемь умножителей в GF(2p), четыре регистра, и один трехвходовый элемент исключающее «ИЛИ», имеющие вход для подачи тактовых сигналов, при этом первый выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Xi+1, второй выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Yi+1, третий выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Zi+1, выход первого элемента исключающее «ИЛИ» соединен со вторым входом первого умножителя в GF(2p), первый вход которого соединен с выходом первого регистра, выход первого умножителя в GF(2p) соединен со вторым входом второго умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход второго умножителя в GF(2p) соединен с первым входом второго элемента исключающее «ИЛИ», выход которого соединен с первым выходом устройства, первый вход третьего умножителя в GF(2p) соединен с выходом третьего регистра, выход третьего умножителя в GF(2p) соединен с первым входом трехвходового элемента исключающее «ИЛИ», второй вход которого соединен с выходом четвертого умножителя в GF(2p), выход трехвходового элемента исключающее «ИЛИ» соединен со вторым входом пятого умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход пятого умножителя в GF(2p) соединен с первым входом третьего элемента исключающее «ИЛИ», выход которого соединен со вторым выходом устройства, выход шестого умножителя в GF(2p) соединен с первым входом четвертого элемента исключающее «ИЛИ», второй вход которого соединен с выходом седьмого умножителя в GF(2p), первый вход которого соединен с выходом четвертого регистра, выход четвертого элемента исключающее «ИЛИ» соединен со вторым входом восьмого умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход восьмого умножителя в GF(2p) соединен с первым входом пятого элемента исключающее «ИЛИ», выход которого соединен с третьим выходом устройства, отличающееся тем, что в устройство дополнительно введены три элемента исключающее «ИЛИ», три линии задержки, вычислитель, счетчик отсчетов псевдослучайного сигнала, четыре регистра, три переключателя и блок памяти примитивных полиномов, имеющие вход для подачи тактовых сигналов, второй вход второго элемента исключающее «ИЛИ» соединен с выходом шестого элемента исключающее «ИЛИ», первый вход которого соединен с выходом первого переключателя, второй вход шестого элемента исключающее «ИЛИ» соединен с выходом первой линии задержки, вход которой соединен с выходом первого переключателя, первый вход первого переключателя соединен с выходом пятого регистра, второй вход первого переключателя соединен с первым выходом устройства, второй вход третьего элемента исключающее «ИЛИ» соединен с выходом седьмого элемента исключающее «ИЛИ», первый вход которого соединен с выходом второго переключателя, второй вход седьмого элемента исключающее «ИЛИ» соединен с выходом второй линии задержки, вход которой соединен с выходом второго переключателя, первый вход второго переключателя соединен с выходом шестого регистра, второй вход второго переключателя соединен со вторым выходом устройства, второй вход пятого элемента исключающее «ИЛИ» соединен с выходом восьмого элемента исключающее «ИЛИ», первый вход которого соединен с выходом третьего переключателя, второй вход восьмого элемента исключающее «ИЛИ» соединен с выходом третьей линии задержки, вход которой соединен с выходом третьего переключателя, первый вход третьего переключателя соединен с выходом седьмого регистра, второй вход третьего переключателя соединен со вторым выходом устройства, первый вход вычислителя соединен с выходом счетчика отсчетов псевдослучайного сигнала, второй вход вычислителя соединен с выходом восьмого регистра, выход вычислителя соединен со входом блока памяти примитивных полиномов, выход которого соединен с третьим входом первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого умножителей в GF(2p), третий вход первого, второго и третьего переключателей соединены с выходом счетчика отсчетов псевдослучайного сигнала, первый вход первого элемента исключающее «ИЛИ» соединен с выходом первого переключателя, второй вход первого элемента исключающее «ИЛИ» соединен с выходом второго переключателя, второй вход третьего умножителя в GF(2p) соединен с выходом первого переключателя, первый вход четвертого умножителя в GF(2p) соединен с выходом первого переключателя, второй вход четвертого умножителя в GF(2p) соединен с выходом третьего переключателя, третий вход трехвходового элемента исключающее «ИЛИ» соединен с выходом второго переключателя, первый вход шестого умножителя в GF(2p) соединен с выходом первого переключателя, второй вход шестого умножителя в GF(2p) соединен с выходом второго переключателя, второй вход седьмого умножителя в GF(2p) соединен с выходом третьего переключателя,

где

р - целое число больше единицы,

Xi+1, Yi+1, Zi+1 - вычисляемые отсчеты псевдослучайных сигналов, двоичные p-разрядные числа,

GF(2p) - поле Галуа, образованное полиномом степени p, где р - целое число больше единицы.

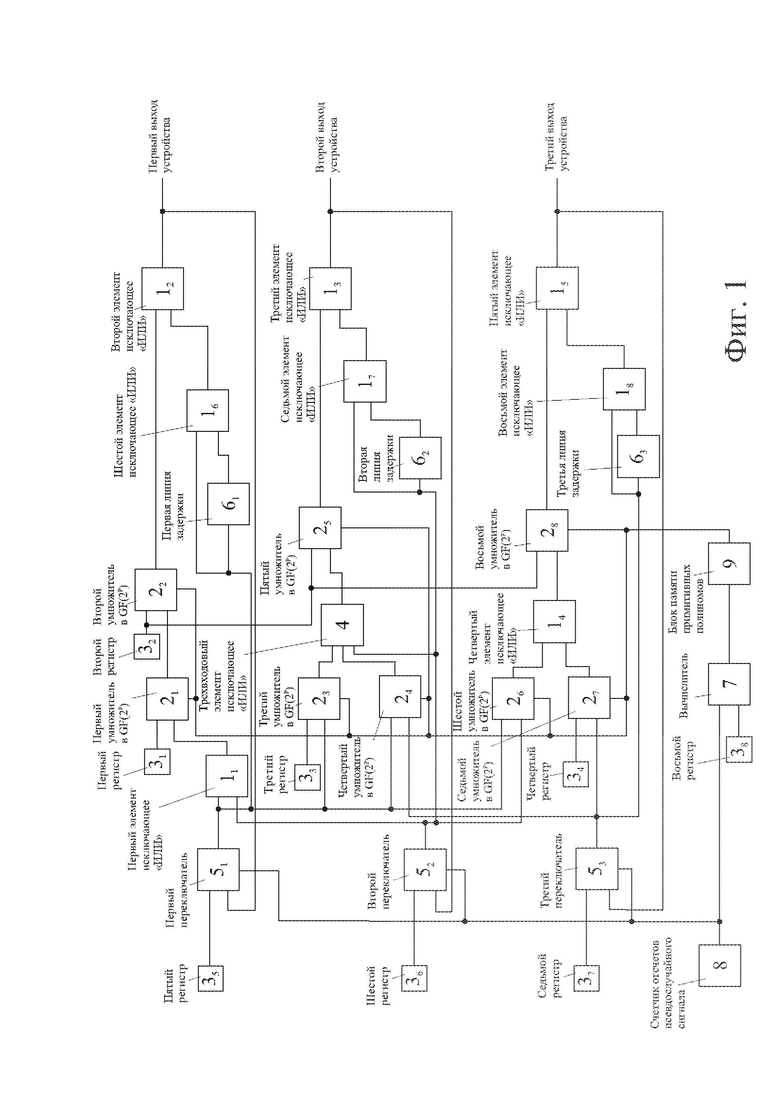

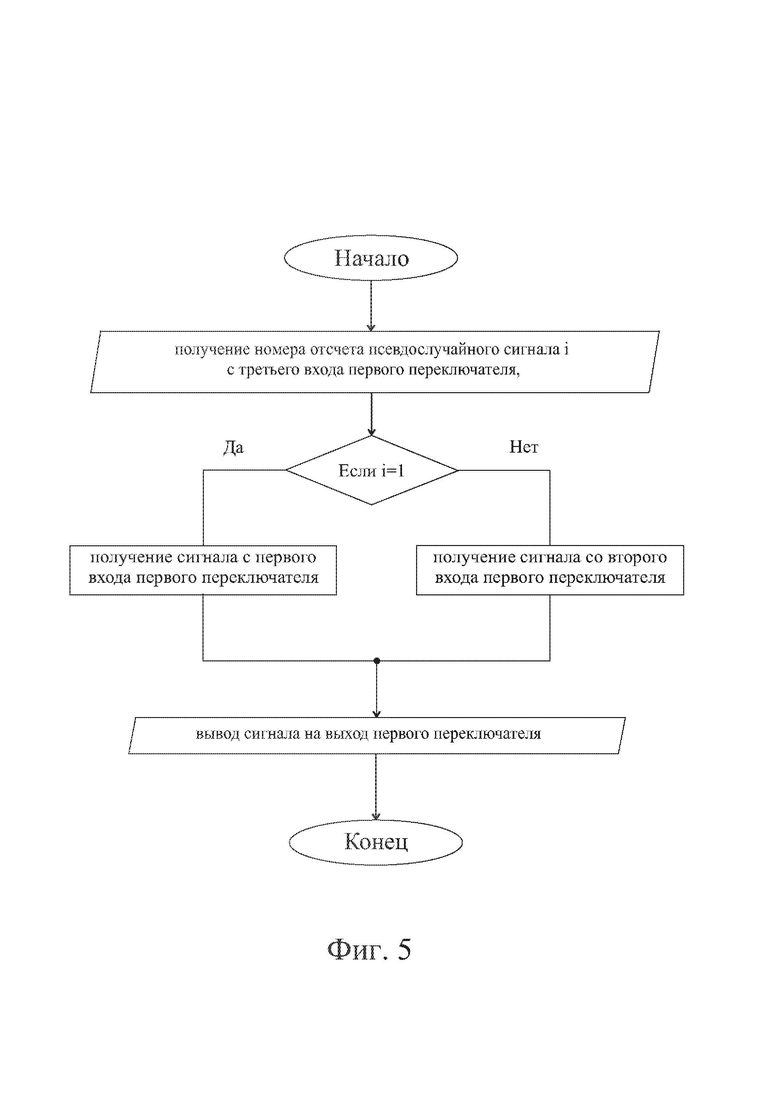

На фиг. 1 приведена структурная схема устройства формирования псевдослучайных сигналов для реализации предлагаемого способа.

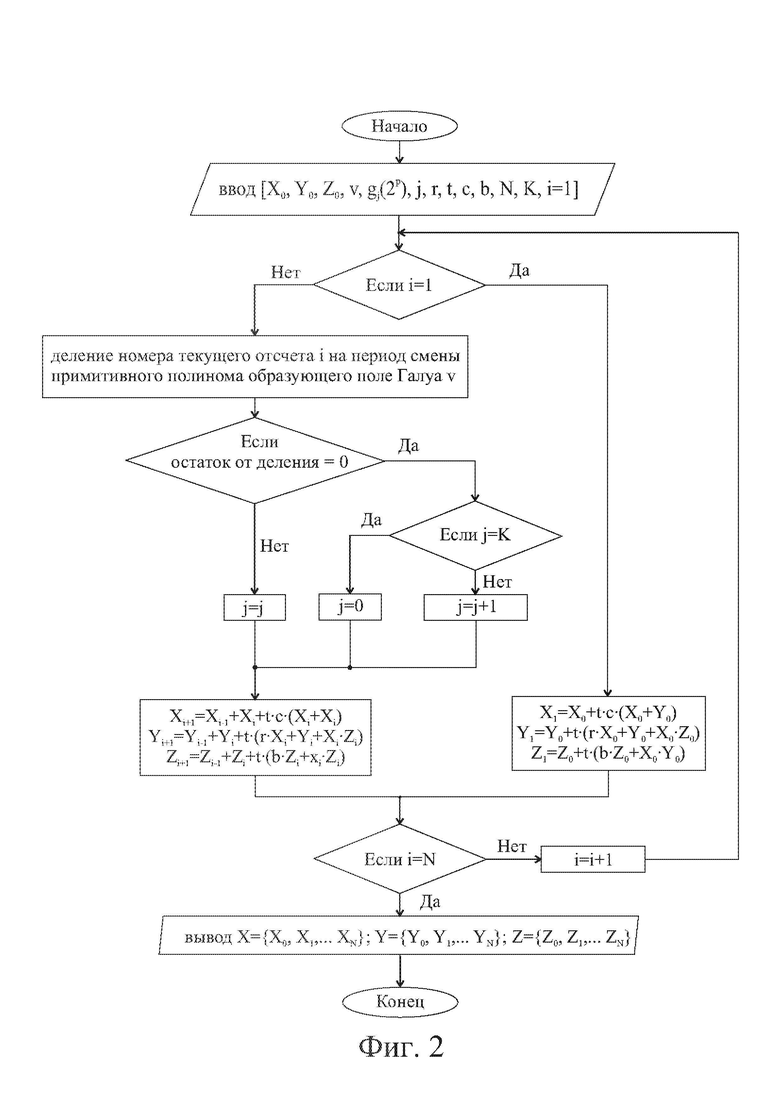

На фиг. 2 приведен алгоритм работы устройства формирования псевдослучайных сигналов.

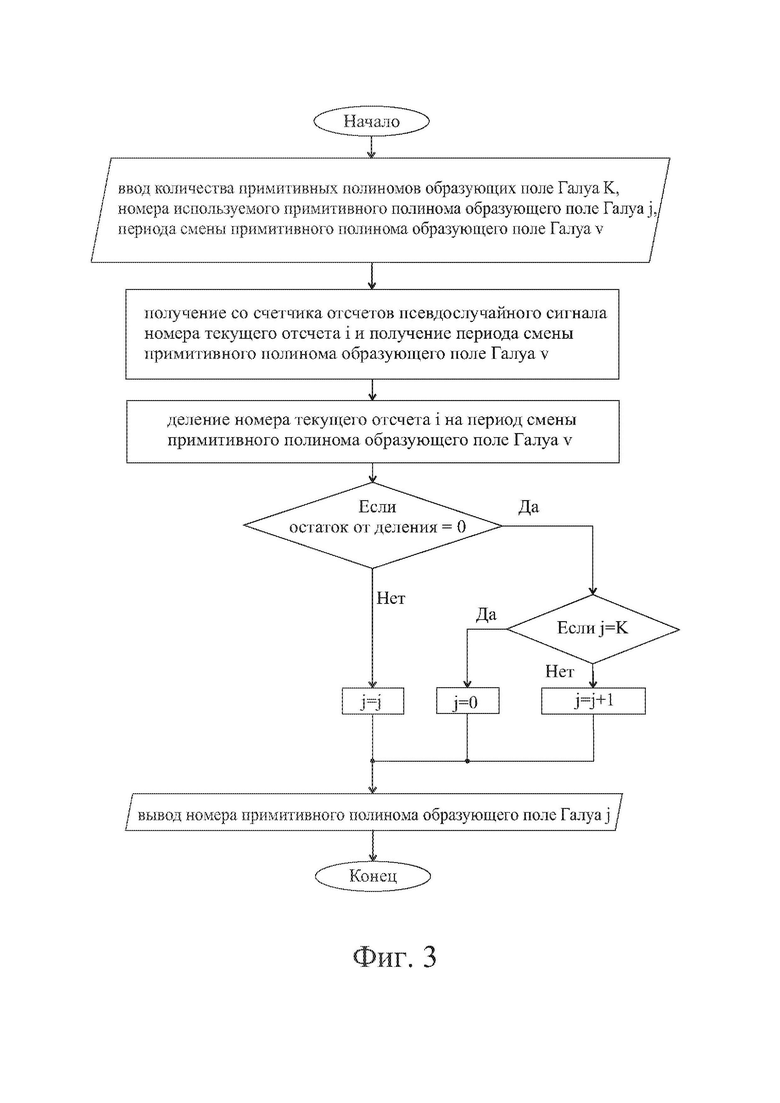

На фиг. 3 приведен алгоритм работы вычислителя.

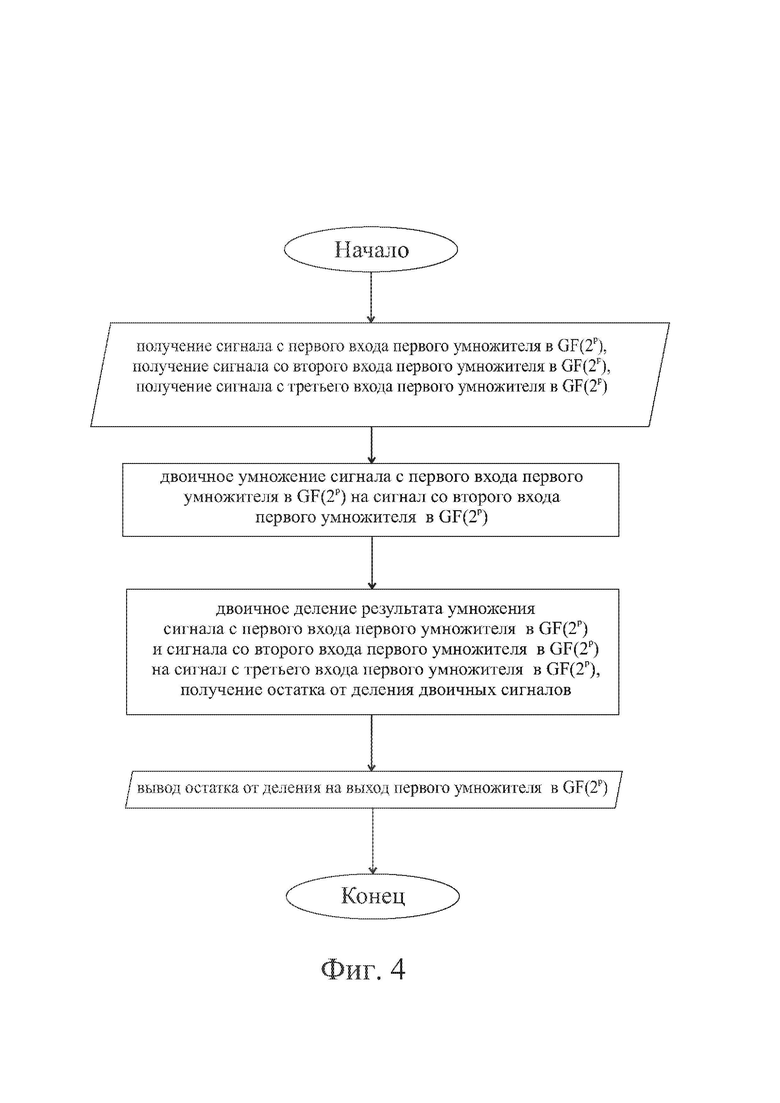

На фиг. 4 приведен алгоритм работы первого умножителя в GF(2p).

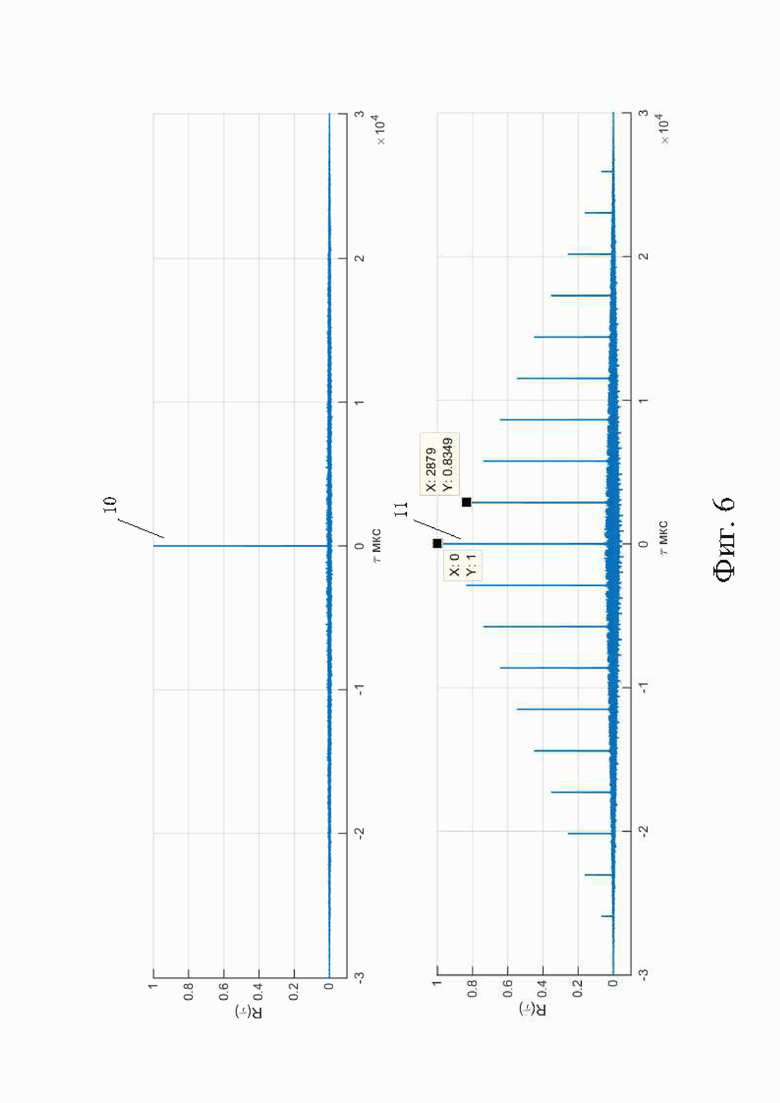

На фиг. 5 приведен алгоритм работы первого переключателя.

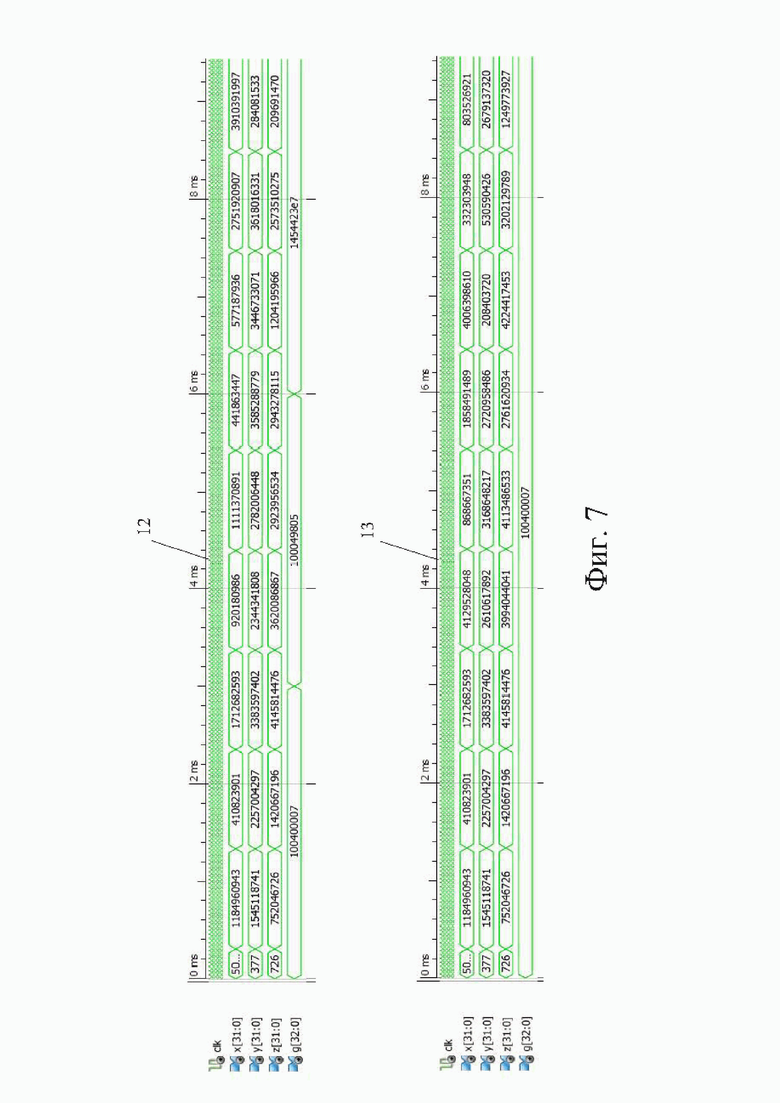

На фиг. 6 приведены автокорреляционные функции псевдослучайного сигнала с выхода предлагаемого устройства и устройства, описанного в прототипе.

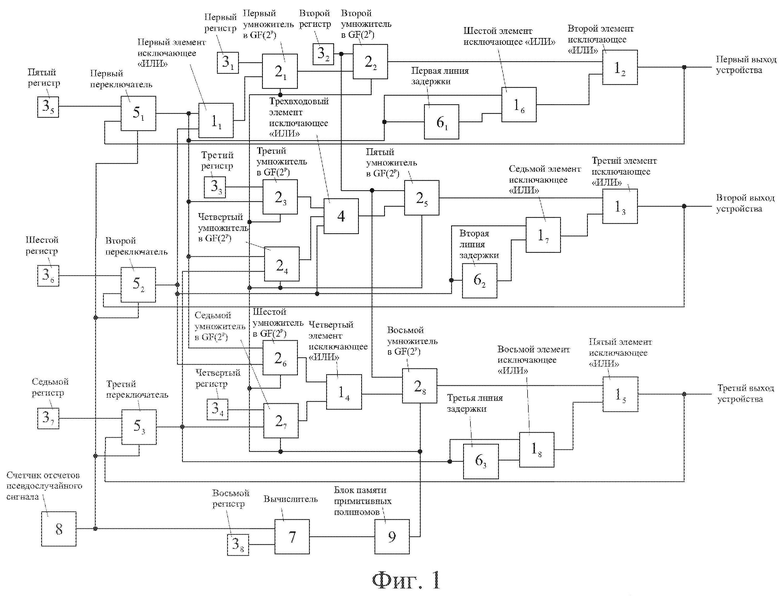

На фиг. 7 приведены временные диаграммы псевдослучайных сигналов с выхода предлагаемого устройства и устройства, описанного в прототипе.

На фиг. 1 приведена структурная схема устройства формирования псевдослучайных сигналов для реализации предлагаемого способа. На всех блоках устройства формирования псевдослучайных сигналов имеется не приведенный на фиг. 1 вход, для подачи тактовых сигналов, на который подается тактовый сигнал, частота которого может составлять от 1 до 200 МГц. Устройство формирования псевдослучайных сигналов (фиг. 1) имеет три выхода, первый выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Xi+1, второй выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Yi+1, третий выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Zi+1, Устройство содержит: первый элемент исключающее «ИЛИ» 11, второй элемент исключающее «ИЛИ» 12, третий элемент исключающее «ИЛИ» 13, четвертый элемент исключающее «ИЛИ» 14, пятый элемент исключающее «ИЛИ» 15, шестой элемент исключающее «ИЛИ» 16, седьмой элемент исключающее «ИЛИ» 17 восьмой элемент исключающее «ИЛИ» 18, первый умножитель в GF(2p) 21, второй умножитель в GF(2p) 22, третий умножитель в GF(2p) 23, четвертый умножитель в GF(2p) 24, пятый умножитель в GF(2p) 25, шестой умножитель в GF(2p) 26, седьмой умножитель в GF(2p) 27, восьмой умножитель в GF(2p) 28, первый регистр 31, второй регистр 32, третий регистр 33, четвертый регистр 34, пятый регистр 35, шестой регистр 36, седьмой регистр 37, восьмой регистр 38, трехвходовый элемент исключающее «ИЛИ» 4, первый переключатель 51, второй переключатель 52, третий переключатель 53, первую линию задержки 61, вторую линию задержки 62, третью линию задержки 63, вычислитель 7, счетчик отсчетов псевдослучайного сигнала 8, блок памяти примитивных полиномов 9, выход первого элемента исключающее «ИЛИ» 11 соединен со вторым входом первого умножителя в GF(2p) 21, первый вход которого соединен с выходом первого регистра 31, выход первого умножителя в GF(2p) 21 соединен со вторым входом второго умножителя в GF(2p) 22, первый вход которого соединен с выходом второго регистра 32, выход второго умножителя в GF(2p) 22 соединен с первым входом второго элемента исключающее «ИЛИ» 12, выход которого соединен с первым выходом устройства, первый вход третьего умножителя в GF(2p) 23 соединен с выходом третьего регистра 33, выход третьего умножителя в GF(2p) 23 соединен с первым входом трехвходового элемента исключающее «ИЛИ» 4, второй вход которого соединен с выходом четвертого умножителя в GF(2p) 24, выход трехвходового элемента исключающее «ИЛИ» 4 соединен со вторым входом пятого умножителя в GF(2p) 25, первый вход которого соединен с выходом второго регистра 32, выход пятого умножителя в GF(2p) 25 соединен с первым входом третьего элемента исключающее «ИЛИ» 13, выход которого соединен со вторым выходом устройства, выход шестого умножителя в GF(2p) 26 соединен с первым входом четвертого элемента исключающее «ИЛИ» 14, второй вход которого соединен с выходом седьмого умножителя в GF(2p) 27, первый вход которого соединен с выходом четвертого регистра 34, выход четвертого элемента исключающее «ИЛИ» 14 соединен со вторым входом восьмого умножителя в GF(2p) 28, первый вход которого соединен с выходом второго регистра 32, выход восьмого умножителя в GF(2p) 28 соединен с первым входом пятого элемента исключающее «ИЛИ» 15, выход которого соединен с третьим выходом устройства, второй вход второго элемента исключающее «ИЛИ» 12 соединен с выходом шестого элемента исключающее «ИЛИ» 16, первый вход которого соединен с выходом первого переключателя 51, второй вход шестого элемента исключающее «ИЛИ» 16 соединен с выходом первой линии задержки 61, вход которой соединен с выходом первого переключателя 51, первый вход первого переключателя 51 соединен с выходом пятого регистра 35, второй вход первого переключателя 51 соединен с первым выходом устройства, второй вход третьего элемента исключающее «ИЛИ» 13 соединен с выходом седьмого элемента исключающее «ИЛИ» 17, первый вход которого соединен с выходом второго переключателя 52, второй вход седьмого элемента исключающее «ИЛИ» 17 соединен с выходом второй линии задержки 62, вход которой соединен с выходом второго переключателя 52, первый вход второго переключателя 52 соединен с выходом шестого регистра 36, второй вход второго переключателя 52 соединен со вторым выходом устройства, второй вход пятого элемента исключающее «ИЛИ» 15 соединен с выходом восьмого элемента исключающее «ИЛИ» 18, первый вход которого соединен с выходом третьего переключателя 53, второй вход восьмого элемента исключающее «ИЛИ» соединен с выходом третьей линии задержки 63, вход которой соединен с выходом третьего переключателя 53, первый вход третьего переключателя 53 соединен с выходом седьмого регистра 37, второй вход третьего переключателя 53 соединен со вторым выходом устройства, первый вход вычислителя 7 соединен с выходом счетчика отсчетов псевдослучайного сигнала 8, второй вход вычислителя 7 соединен с выходом восьмого регистра 38, выход вычислителя 7 соединен со входом блока памяти примитивных полиномов 9, выход которого соединен с третьим входом первого 21, второго 22, третьего 23, четвертого 24, пятого 25, шестого 26, седьмого 27 и восьмого 28 умножителей в GF(2p), третьи входы первого 51, второго 52 и третьего 53 переключателей соединены с выходом счетчика отсчетов псевдослучайного сигнала 8, первый вход первого элемента исключающее «ИЛИ» 11 соединен с выходом первого переключателя 51, второй вход первого элемента исключающее «ИЛИ» 11 соединен с выходом второго переключателя 52, второй вход третьего умножителя в GF(2p) 23 соединен с выходом первого переключателя 51, первый вход четвертого умножителя в GF(2p) 24 соединен с выходом первого переключателя 51, второй вход четвертого умножителя в GF(2p) 24 соединен с выходом третьего переключателя 53, третий вход трехвходового элемента исключающее «ИЛИ» 4 соединен с выходом второго переключателя 52, первый вход шестого умножителя в GF(2p) 26 соединен с выходом первого переключателя 51, второй вход шестого умножителя в GF(2p) 26 соединен с выходом второго переключателя 52, второй вход седьмого умножителя в GF(2p) 27 соединен с выходом третьего переключателя 53. Перечисленные выше блоки имеют стандартные, опубликованные в литературе схемы и имеют соответствующие системы электропитания.

Способ формирования псевдослучайных сигналов заключается в формировании псевдослучайных сигналов путем вычисления трех уравнений модифицированной динамической системы Лоренца в арифметике над полем Галуа GF(2p), причем при формировании псевдослучайных сигналов, когда остаток от деления номера формируемого отсчета сигнала i на период смены примитивного полинома образующего поле Галуа v, равен нулю согласно уравнению:

производят изменение примитивного полинома, образующего поле Галуа gj(2p), где p - целое число больше единицы, на следующий примитивный полином, образующий поле Галуа gj+1(2p), из отобранного ансамбля полиномов {g0(2p), g1(2p), …, gj+1(2p) … gK(2p)}, где j меняется от нуля до К, где К - целое число равное количеству полиномов в отобранном ансамбле, далее формируют псевдослучайные сигналы описываемые последовательностями:

путем вычисления трех уравнений модифицированной динамической системы Лоренца:

где

⊕ - операция исключающее «ИЛИ»,

⋅ - операция умножения, которая производится над полем Галуа GF(2p),

р - целое число больше единицы,

X, Y, Z - последовательности отсчетов псевдослучайных сигналов,

Xi+1, Yi+1, Zi+1 - вычисляемые отсчеты псевдослучайных сигналов, двоичные p-разрядные числа,

Xi, Yi, Zi - текущие отсчеты псевдослучайных сигналов, двоичные p-разрядные числа,

Xi-1, Yi-1, Zi-1 - предыдущие отсчеты псевдослучайных сигналов, двоичные p-разрядные числа, в начальный момент времени предыдущие отсчеты псевдослучайных сигналов Xi-1, Yi-1, Zi-1 системы равны нулю,

N - количество отсчетов формируемого псевдослучайного сигнала, целое число больше единицы,

i - номер формируемого отсчета, целое число от единицы до количества отсчетов формируемого псевдослучайного сигнала N,

K - количество примитивных полиномов, образующих поле Галуа, целое число больше нуля,

j - номер используемого примитивного полинома, образующего поле Галуа, целое число от нуля до количества примитивных полиномов, образующих поле Галуа K,

t - шаг интегрирования динамической системы, двоичное p-разрядное число,

с - ослабляющий коэффициент, двоичное p-разрядное число,

r - усиливающий коэффициент, двоичное p-разрядное число,

b - геометрический параметр динамической системы, двоичное p-разрядное число,

v - период смены примитивного полинома образующего поле Галуа, целое число больше единицы, меньше N,

gj(2p) - примитивный полином, образующий поле Галуа, двоичное p+1 - разрядное число (может составлять, например: "1011" для p = 4, "1000001010011" для p = 12, ….),

GF(2p) - поле Галуа, образованное полиномом степени p.

Рассмотрим осуществление способа формирования псевдослучайных сигналов и работу устройства для его осуществления. Все блоки устройства подключаются к сети электропитания, на все блоки устройства подается тактовый сигнал (например с частотой 50 МГц), в блок вычислителя, блоки умножителей в GF(2p) и переключателей загружают программы согласно приведенным на фиг. 3, фиг. 4 и фиг. 5 алгоритмам работы данных блоков, далее в первый регистр 31 вносится значение ослабляющего коэффициента с (например: "00001111"), во второй регистр 32 вносится значение шага интегрирования динамической системы t (например: "00001100"), в третий регистр 33 вносится значение усиливающего коэффициента r (например: "00001010"), в четвертый регистр 34 вносится значение геометрического параметра динамической системы b (например: "00000001"), в пятый регистр 35 вносится значение нулевого отсчета X0 псевдослучайного сигнала (например: "00000101"), в шестой регистр 36 вносится значение нулевого отсчета Y0 псевдослучайного сигнала (например: "00000110"), в седьмой регистр 37 вносится значение нулевого отсчета Z0 псевдослучайного сигнала (например: "00000100"), в восьмой регистр 38 вносится значение периода смены примитивного полинома, образующего поле v (например: 57, что в двоичном представлении равно "00111001"), в блок памяти примитивных полиномов 8 вносится K значений примитивных полиномов, образующих поле Галуа (например: значение первого полинома "101100011", значение второго полинома "100011101" …), затем значения значение отсчета псевдослучайного сигнала Xi с выхода первого переключателя 51 и значение отсчета псевдослучайного сигнала Yi с выхода второго переключателя 52 в первом элементе исключающее «ИЛИ» 11 проходят операцию исключающее «ИЛИ», затем в первом умножителе в GF(2p) 21 умножаются на значение ослабляющего коэффициента с, которое хранится в первом регистре 31, затем во втором умножителе в GF(2p) 22 результат умножается на значение шага интегрирования динамической системы t, которое хранится во втором регистре 32, результат во втором элементе исключающее «ИЛИ» 12 проходит операцию исключающее «ИЛИ» с прошедшими в шестом элементе исключающее «ИЛИ» 16 операцию исключающее «ИЛИ» значение отсчета сигнала Xi с выхода первого переключателя 51 и задержанным первой линией задержки 61 на один отсчет значением псевдослучайного сигнала Xi-1 с выхода первого переключателя 51, таким образом на первом выходе устройства получаем значение вычисляемого отсчета псевдослучайного сигнала Xi+1, значение отсчета псевдослучайного сигнала Xi с выхода первого переключателя 51 в третьем умножителе в GF(2p) 23 проходит операцию умножения на значение усиливающего коэффициента r, которое хранится в третьем регистре 33, затем результат в трехвходовом элементе исключающее «ИЛИ» 4 проходит операцию исключающее «ИЛИ» со значением отсчета псевдослучайного сигнала Yi с выхода второго переключателя 52 и с умноженными в четвертом умножителе в GF(2p) 24 значением отсчета псевдослучайного сигнала Xi с выхода первого переключателя 51 и значением отсчета псевдослучайного сигнала Zi с выхода третьего переключателя 53, затем полученный результат в пятом умножителе в GF(2p) 25 проходит операцию умножения на значение шага интегрирования динамической системы t, который хранится во втором регистре 32, затем полученный результат в третьем элементе исключающее «ИЛИ» 13 проходит операцию исключающее «ИЛИ» с прошедшими в седьмом элементе исключающее «ИЛИ» 17 операцию исключающее «ИЛИ» значением отсчета псевдослучайного сигнала Yi с выхода второго переключателя 52 и задержанным второй линией задержки 62 на один отсчет значением псевдослучайного сигнала Yi-1 с выхода второго переключателя 52, таким образом на втором выходе устройства получаем значение вычисляемого отсчета псевдослучайного сигнала Yi+1, значение отсчета псевдослучайного сигнала Xi с выхода первого переключателя 51 и значение отсчета псевдослучайного сигнала Yi с выхода второго переключателя 52 умножаются в шестом умножителе в GF(2p) 26, затем результат умножения поступает на четвертый элемент исключающее «ИЛИ» 14, в котором проходит операцию исключающее «ИЛИ» с умноженным в седьмом умножителе в GF(2p) 27 значением отсчета псевдослучайного сигнала Zi с выхода третьего переключателя 53 на значение геометрического параметра динамической системы b, которое хранится в четвертом регистре 34, результат с четвертого элемента исключающее «ИЛИ» 14 поступает на восьмой умножитель в GF(2p) 28, в котором умножается на значение шага интегрирования динамической системы t, которое хранится во втором регистре 32, результат умножения поступает на пятый элемент исключающее «ИЛИ» 15, в котором проходит операцию исключающее «ИЛИ» с прошедшими в восьмом элементе исключающее «ИЛИ» 18 операцию исключающее «ИЛИ» значением отсчета псевдослучайного сигнала Zi с выхода третьего переключателя 53 и задержанным третьей линией задержки 63 на один отсчет значением псевдослучайного сигнала Zi-1 с выхода третьего переключателя 53, таким образом на третьем выходе устройства получаем вычисляемый отсчет псевдослучайного сигнала Zi+1, при этом значение сигнала со счетчика отсчетов псевдослучайного сигнала 8 поступает на вычислитель 7, в котором делится на значение периода смены примитивного полинома образующего поле v, который хранится в восьмом регистре 38, затем в вычислителе 7 остаток от деления сравнивается с нулем, затем вычислитель согласно алгоритму, приведенному на фиг. 3, выдает значение номера используемого примитивного полинома, образующего поле Галуа j, который поступает на блок памяти примитивных полиномов 9, из которого значение примитивного полинома, образующего поле Галуа gj(2p), поступает на третий вход первого 21, второго 22, третьего 23, четвертого 24, пятого 25, шестого 26, седьмого 27 и восьмого 28 умножителей в GF(2p), значение сигнала с выхода счетчика отсчетов псевдослучайного сигнала 8 поступает на вход первого переключателя 51, который согласно алгоритму приведенному на фиг. 5 пропускает на выход сигнал с выхода пятого регистра 35 или сигнал с первого выхода устройства, значение сигнала с выхода счетчика отсчетов псевдослучайного сигнала 8 поступает на вход второго переключателя 52, который согласно алгоритму приведенному на фиг. 5 пропускает на выход сигнал с выхода шестого регистра 36 или сигнал со второго выхода устройства, значение сигнала с выхода счетчика отсчетов псевдослучайного сигнала 8 поступает на вход третьего переключателя 53, который согласно алгоритму приведенному на фиг. 5 пропускает на выход сигнал с выхода седьмого регистра 37 или сигнал с третьего выхода устройства.

На фиг. 2 приведен алгоритм работы устройства формирования псевдослучайного сигнала, согласно которому сначала вводятся исходные данные: значение ослабляющего коэффициента с, значение шага интегрирования динамической системы t, значение усиливающего коэффициента r, значение геометрического параметра динамической системы b, значение периода смены примитивного полинома образующего поле v, значение начального отсчета псевдослучайного сигнала X0, значение начального отсчета псевдослучайного сигнала Y0, значение начального отсчета псевдослучайного сигнала Z0, в блок памяти примитивных полиномов 9 вносится K значений примитивных полиномов, образующих поле Галуа, при нулевом значении отсчета сигнала производится вычисление последующего значения отсчета при начальных значениях отсчетов, затем при увеличении номера формируемого отсчета последующие значения отсчетов сигналов Xi+1, Yi+1, Zi+1 вычисляются исходя из предыдущих значений отсчетов сигналов Xi, Yi, Zi, причем значение полинома, образующего поле j, изменяется в зависимости от номера формируемого отсчета i.

На фиг. 3 приведен алгоритм работы вычислителя 7, который имеет первый вход для подачи значения номера формируемого отсчета пседослучайного сигнала i, второй вход для подачи значения периода смены примитивного полинома, образующего поле v и выход на который выводится номер используемого примитивного, образующего поле Галуа j, согласно алгоритму сначала вводятся исходные значения периода смены примитивного полинома v, где v - целое число от 1 до 2р-1, количество используемых примитивных полиномов K, номер исходного примитивного полинома j, где j - целое число от 0 до K, затем выполняется деление номера формируемого отсчета i на период смены примитивного полинома v, если остаток от деления равен нулю, то производится сравнение номера используемого примитивного полинома j с количеством примитивных полиномов, образующих поле Галуа K, если количество примитивных полиномов, образующих поле Галуа K равно номеру используемого примитивного полинома j, то вычислитель выдает нулевой номер полинома, образующего поле, в случае неравенства количества примитивных полиномов, образующих поле Галуа K и номера примитивного полинома j производится увеличение номера используемого примитивного полинома, и вычислитель выдает следующий номер примитивного полинома, если остаток от деления номера формируемого отсчета i на период смены примитивного полинома v не равен нулю, то полином не меняется, и вычислитель выдает текущий номер примитивного полинома.

На фиг. 4 приведен алгоритм работы первого умножителя в GF(2p) 21, который имеет первый вход для подачи первого умножаемого значения сигнала, второй вход для подачи второго умножаемого значения сигнала, третий вход для подачи примитивного полинома образующего поле Галуа и выход на который выводится результат умножения в GF(2p), согласно алгоритму сначала производится операция двоичного умножения значения p-разрядного сигнала с первого входа первого умножителя в GF(2p) 21 на значение p-разрядного сигнала со второго входа первого умножителя в GF(2p) 21, затем производится деление результата умножения (2p-1 разрядного сигнала) на значение сигнала с третьего входа первого умножителя в GF(2p) 21 (p+1 - разрядный сигнал), результатом умножения в первом умножителе в GF(2p) 21 является остаток от деления результата умножения на полином образующий поле Галуа gj(2p), результат умножения (p-разрядный сигнал) снимают с выхода первого умножителя в GF(2p) 21, второй 22, третий 23, четвертый 24, пятый 25, шестой 26, седьмой 27 и восьмой 28 умножители в GF(2p) работают по тому же алгоритму.

На фиг. 5 приведен алгоритм работы первого переключателя 51, который имеет первый вход для подачи первого сигнала, второй вход для подачи второго сигнала, третий вход для подачи номера формируемого отсчета пседослучайного сигнала и выход на который выводится результат, один из сигналов, согласно алгоритму при единичном значении номера отсчета псевдослучайного сигнала (i=1), на выход первого переключателя 51 проходит сигнал с первого входа первого переключателя 51, если i не равно единице на выход проходит сигнал со второго входа первого переключателя 51, второй 52 и третий 53 переключатели работают по тому же алгоритму.

На фиг. 6 изображены автокорреляционные функции псевдослучайного сигнала с выхода предлагаемого устройства 10 и устройства прототипа 11, из которых видно, что временной сдвиг τ (показывающий наличие взаимосвязей в псевдослучайной последовательности) между уровнем главного и бокового лепестка автокорреляционной функции для предлагаемого способа составляет более 30000 мкс по сравнению с 2879 мкс для прототипа.

На фиг. 7 изображены временные диаграммы псевдослучайных сигналов с выхода предлагаемого устройства 12 и устройства прототипа 13, из которых видно, что в предлагаемом устройстве в отличии от прототипа нулевой(начальный) примитивный полином, образующий поле Галуа g0(232) = 10040000716 на 3-ей мс меняется на первый примитивный полином, образующий поле Галуа g1(232) = 10004980516, на 6-ой мс на второй примитивный полином, образующий поле Галуа g2(232) = 1454423E716.

По сравнению с прототипом предлагаемый способ формирования псевдослучайных сигналов и устройство для его осуществления позволяют формировать псевдослучайные сигналы с большим периодом повторения.

В качестве устройства формирования псевдослучайных сигналов может быть использована схема, реализуемая в ПЛИС (программируемой логической интегральной схеме).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| Генератор периодических псевдослучайных двоичных последовательностей сложной структуры | 2018 |

|

RU2690765C1 |

| Устройство для вычисления преобразования Фурье-Галуа | 1989 |

|

SU1631554A1 |

| РЕКОНФИГУРИРУЕМЫЙ КОДЕР РИДА-СОЛОМОНА | 2015 |

|

RU2605672C1 |

| Генератор периодических идеальных троичных последовательностей | 2017 |

|

RU2665290C1 |

| СПОСОБ АДАПТИВНОГО ПОТОЧНОГО ШИФРОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2329544C2 |

| РЕКОНФИГУРИРУЕМЫЙ КОДЕР БЧХ КОДОВ | 2015 |

|

RU2601827C1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ЧИСЕЛ | 2021 |

|

RU2776346C1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

| Устройство для кодирования | 1986 |

|

SU1390801A1 |

Изобретение относится к способу и устройству формирования псевдослучайных сигналов. Технический результат заключается в увеличении периода повторяемости псевдослучайного сигнала. Устройство содержит пять элементов исключающее «ИЛИ», восемь умножителей в GF(2p), четыре регистра и один трехвходовый элемент исключающее «ИЛИ», при этом в устройство дополнительно введены три элемента исключающее «ИЛИ», три линии задержки, вычислитель, счетчик отсчетов псевдослучайного сигнала, четыре регистра, три переключателя и блок памяти примитивных полиномов. 2 н.п. ф-лы, 7 ил.

1. Способ формирования псевдослучайных сигналов, заключающийся в формировании псевдослучайных сигналов путем вычисления трех уравнений модифицированной динамической системы Лоренца в арифметике над полем Галуа GF(2p), отличающийся тем, что при формировании псевдослучайных сигналов, когда остаток от деления номера формируемого отсчета сигнала i на период смены примитивного полинома, образующего поле Галуа v, равен нулю согласно уравнению:

производят изменение примитивного полинома, образующего поле Галуа gj(2p), где p – целое число больше единицы, на следующий примитивный полином, образующий поле Галуа gj+1(2p), из отобранного ансамбля полиномов {g0(2p), g1(2p),…, gj+1(2p) … gK(2p)}, где j меняется от нуля до К, где К – целое число, равное количеству полиномов в отобранном ансамбле, далее формируют псевдослучайные сигналы, описываемые последовательностями:

путем вычисления трех уравнений модифицированной динамической системы Лоренца:

где

р – целое число больше единицы,

X, Y, Z – последовательности отсчетов псевдослучайных сигналов,

Xi+1, Yi+1, Zi+1 – вычисляемые отсчеты псевдослучайных сигналов, двоичные p–разрядные числа,

Xi, Yi, Zi – текущие отсчеты псевдослучайных сигналов, двоичные p-разрядные числа,

Xi-1, Yi-1, Zi-1 – предыдущие отсчеты псевдослучайных сигналов, двоичные p-разрядные числа, в начальный момент времени предыдущие отсчеты псевдослучайных сигналов Xi-1, Yi-1, Zi-1 системы равны нулю,

N – количество отсчетов формируемого псевдослучайного сигнала, целое число больше единицы,

i – номер формируемого отсчета, целое число от единицы до количества отсчетов формируемого псевдослучайного сигнала N,

K – количество примитивных полиномов, образующих поле Галуа, целое число больше нуля,

j – номер используемого примитивного полинома, образующего поле Галуа, целое число от нуля до количества примитивных полиномов, образующих поле Галуа K,

t – шаг интегрирования динамической системы, двоичное p-разрядное число,

с – ослабляющий коэффициент, двоичное p-разрядное число,

r – усиливающий коэффициент, двоичное p-разрядное число,

b – геометрический параметр динамической системы, двоичное p-разрядное число,

v – период смены примитивного полинома, образующего поле Галуа, целое число больше единицы, меньше N,

gj(2p) – примитивный полином, образующий поле Галуа, двоичное p+1-разрядное число,

GF(2p) – поле Галуа, образованное полиномом степени p.

2. Устройство формирования псевдослучайных сигналов для осуществления способа по п. 1, содержащее пять элементов исключающее «ИЛИ», восемь умножителей в GF(2p), четыре регистра и один трехвходовый элемент исключающее «ИЛИ», имеющие вход для подачи тактовых сигналов, при этом первый выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Xi+1, второй выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Yi+1, третий выход устройства является выходом для съема вычисляемого отсчета псевдослучайного сигнала Zi+1, выход первого элемента исключающее «ИЛИ» соединен со вторым входом первого умножителя в GF(2p), первый вход которого соединен с выходом первого регистра, выход первого умножителя в GF(2p) соединен со вторым входом второго умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход второго умножителя в GF(2p) соединен с первым входом второго элемента исключающее «ИЛИ», выход которого соединен с первым выходом устройства, первый вход третьего умножителя в GF(2p) соединен с выходом третьего регистра, выход третьего умножителя в GF(2p) соединен с первым входом трехвходового элемента исключающее «ИЛИ», второй вход которого соединен с выходом четвертого умножителя в GF(2p), выход трехвходового элемента исключающее «ИЛИ» соединен со вторым входом пятого умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход пятого умножителя в GF(2p) соединен с первым входом третьего элемента исключающее «ИЛИ», выход которого соединен со вторым выходом устройства, выход шестого умножителя в GF(2p) соединен с первым входом четвертого элемента исключающее «ИЛИ», второй вход которого соединен с выходом седьмого умножителя в GF(2p), первый вход которого соединен с выходом четвертого регистра, выход четвертого элемента исключающее «ИЛИ» соединен со вторым входом восьмого умножителя в GF(2p), первый вход которого соединен с выходом второго регистра, выход восьмого умножителя в GF(2p) соединен с первым входом пятого элемента исключающее «ИЛИ», выход которого соединен с третьим выходом устройства, отличающееся тем, что в устройство дополнительно введены три элемента исключающее «ИЛИ», три линии задержки, вычислитель, счетчик отсчетов псевдослучайного сигнала, четыре регистра, три переключателя и блок памяти примитивных полиномов, имеющие вход для подачи тактовых сигналов, второй вход второго элемента исключающее «ИЛИ» соединен с выходом шестого элемента исключающее «ИЛИ», первый вход которого соединен с выходом первого переключателя, второй вход шестого элемента исключающее «ИЛИ» соединен с выходом первой линии задержки, вход которой соединен с выходом первого переключателя, первый вход первого переключателя соединен с выходом пятого регистра, второй вход первого переключателя соединен с первым выходом устройства, второй вход третьего элемента исключающее «ИЛИ» соединен с выходом седьмого элемента исключающее «ИЛИ», первый вход которого соединен с выходом второго переключателя, второй вход седьмого элемента исключающее «ИЛИ» соединен с выходом второй линии задержки, вход которой соединен с выходом второго переключателя, первый вход второго переключателя соединен с выходом шестого регистра, второй вход второго переключателя соединен со вторым выходом устройства, второй вход пятого элемента исключающее «ИЛИ» соединен с выходом восьмого элемента исключающее «ИЛИ», первый вход которого соединен с выходом третьего переключателя, второй вход восьмого элемента исключающее «ИЛИ» соединен с выходом третьей линии задержки, вход которой соединен с выходом третьего переключателя, первый вход третьего переключателя соединен с выходом седьмого регистра, второй вход третьего переключателя соединен со вторым выходом устройства, первый вход вычислителя соединен с выходом счетчика отсчетов псевдослучайного сигнала, второй вход вычислителя соединен с выходом восьмого регистра, выход вычислителя соединен со входом блока памяти примитивных полиномов, выход которого соединен с третьим входом первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого умножителей в GF(2p), третий вход первого, второго и третьего переключателей соединены с выходом счетчика отсчетов псевдослучайного сигнала, первый вход первого элемента исключающее «ИЛИ» соединен с выходом первого переключателя, второй вход первого элемента исключающее «ИЛИ» соединен с выходом второго переключателя, второй вход третьего умножителя в GF(2p) соединен с выходом первого переключателя, первый вход четвертого умножителя в GF(2p) соединен с выходом первого переключателя, второй вход четвертого умножителя в GF(2p) соединен с выходом третьего переключателя, третий вход трехвходового элемента исключающее «ИЛИ» соединен с выходом второго переключателя, первый вход шестого умножителя в GF(2p) соединен с выходом первого переключателя, второй вход шестого умножителя в GF(2p) соединен с выходом второго переключателя, второй вход седьмого умножителя в GF(2p) соединен с выходом третьего переключателя,

где

р – целое число больше единицы,

Xi+1, Yi+1, Zi+1 – вычисляемые отсчеты псевдослучайных сигналов, двоичные p–разрядные числа,

GF(2p) – поле Галуа, образованное полиномом степени p.

| "Practical Implementation of a Pseudo-Random Signal Generator Based on the Lorenz System Realized on FPGA", IEEE, 2019, доступно по ссылке: https://zh.booksc.eu/dl/77136749/f0e52c | |||

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ЧИСЕЛ | 2020 |

|

RU2740339C1 |

| СПОСОБ ДЛЯ ГЕНЕРИРОВАНИЯ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ И СПОСОБ ДЛЯ КОДИРОВАНИЯ ИЛИ ДЕКОДИРОВАНИЯ ПОТОКА ДАННЫХ | 2013 |

|

RU2609098C2 |

| Генератор периодических псевдослучайных двоичных последовательностей сложной структуры | 2018 |

|

RU2690765C1 |

| US 10078493 B2, 18.09.2018. | |||

Авторы

Даты

2022-04-01—Публикация

2021-04-13—Подача