Изобретение относится к вычисли- тельной технике и может быть использовано для автоматизации отладки программ в реальном масштабе времеии для специализированных программных устройств на базе однокристальной микроэвм (ОМЭ), для записи отлаженнъп программ пользователя во внутреннее .постоянное запоминающее устройство (ПЗУ) ОМЭ и для отладки аппаратной части Программных устройств на базе ОМЭ. .

Целью изобретения является повышение производительности процесса от- ладки.

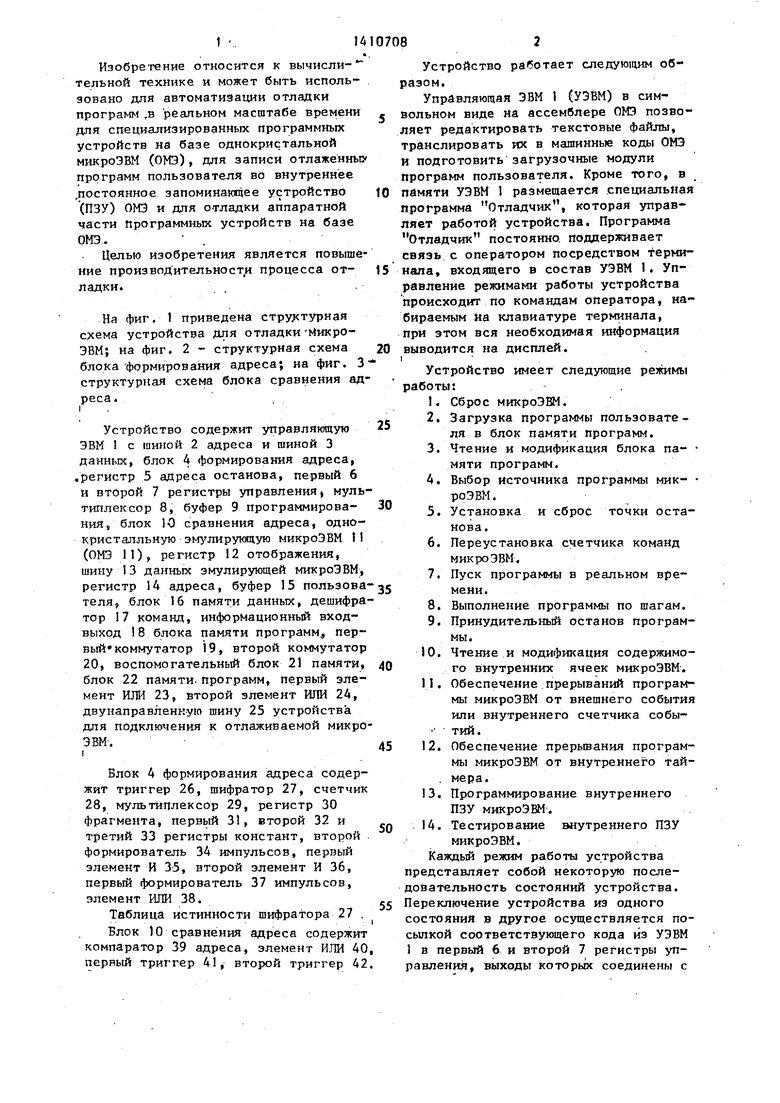

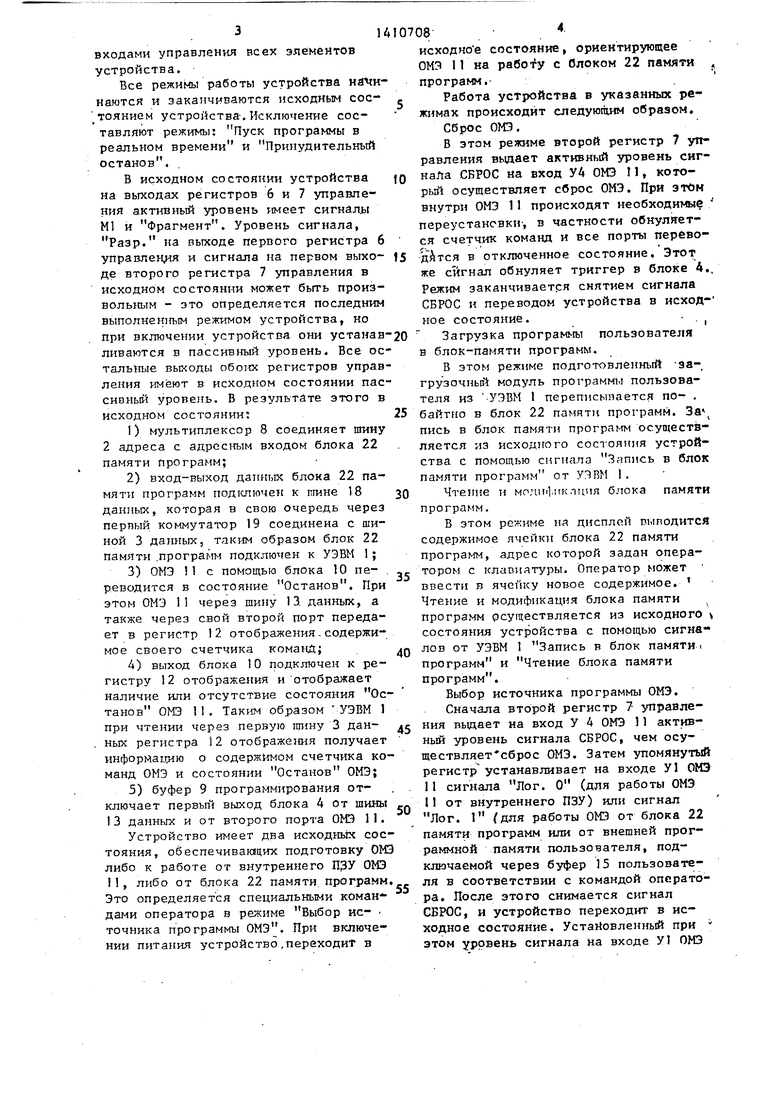

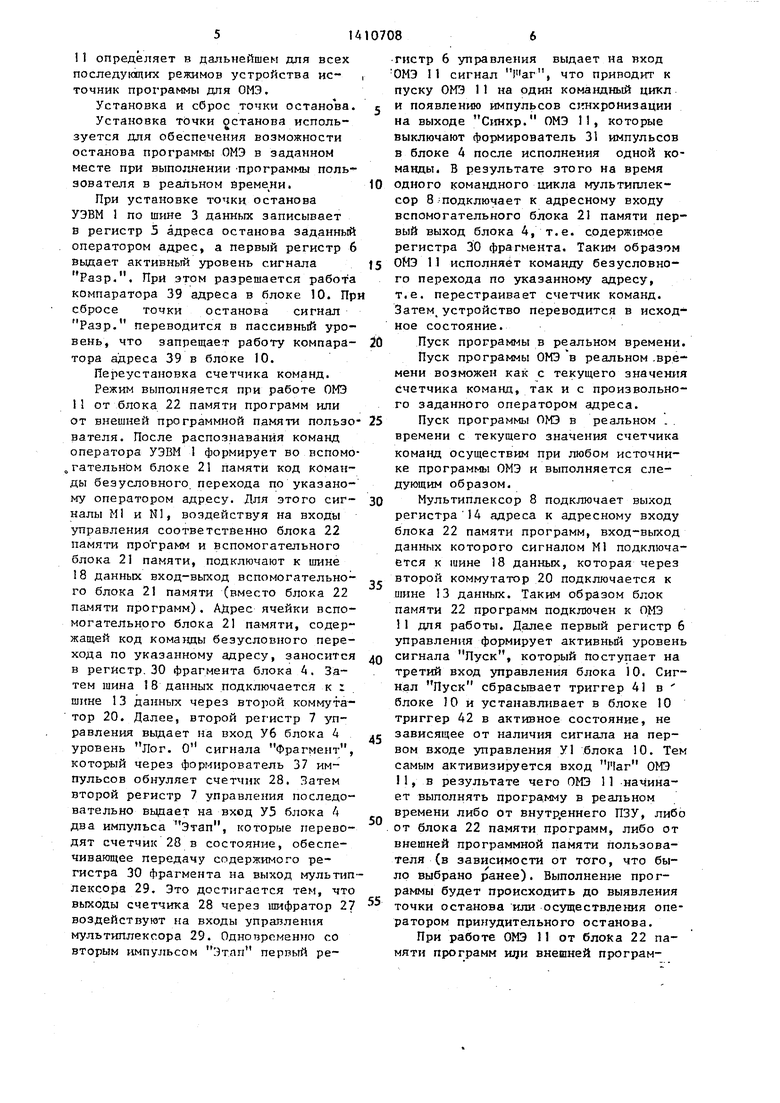

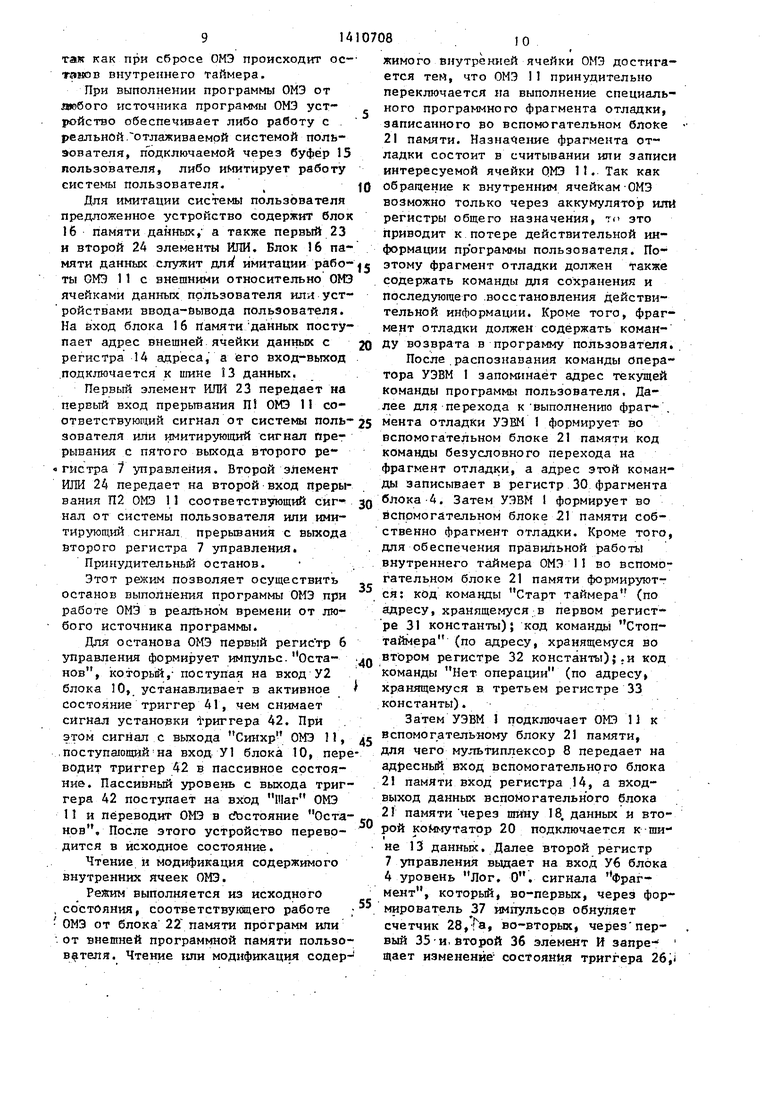

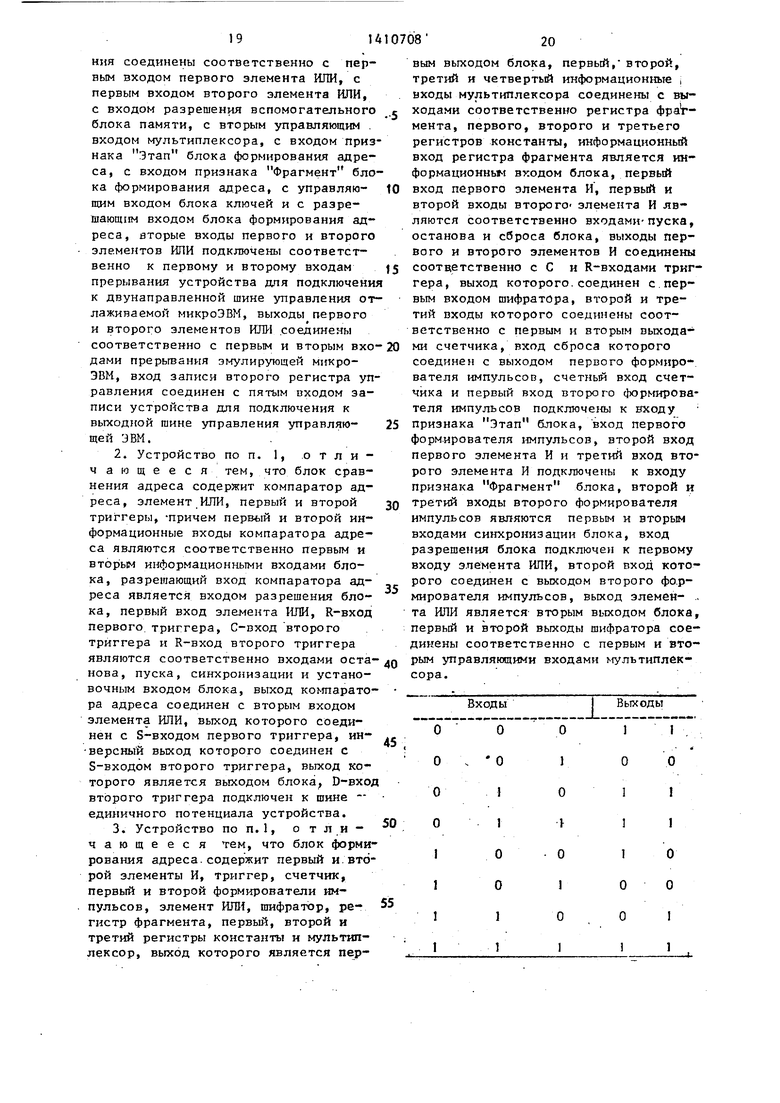

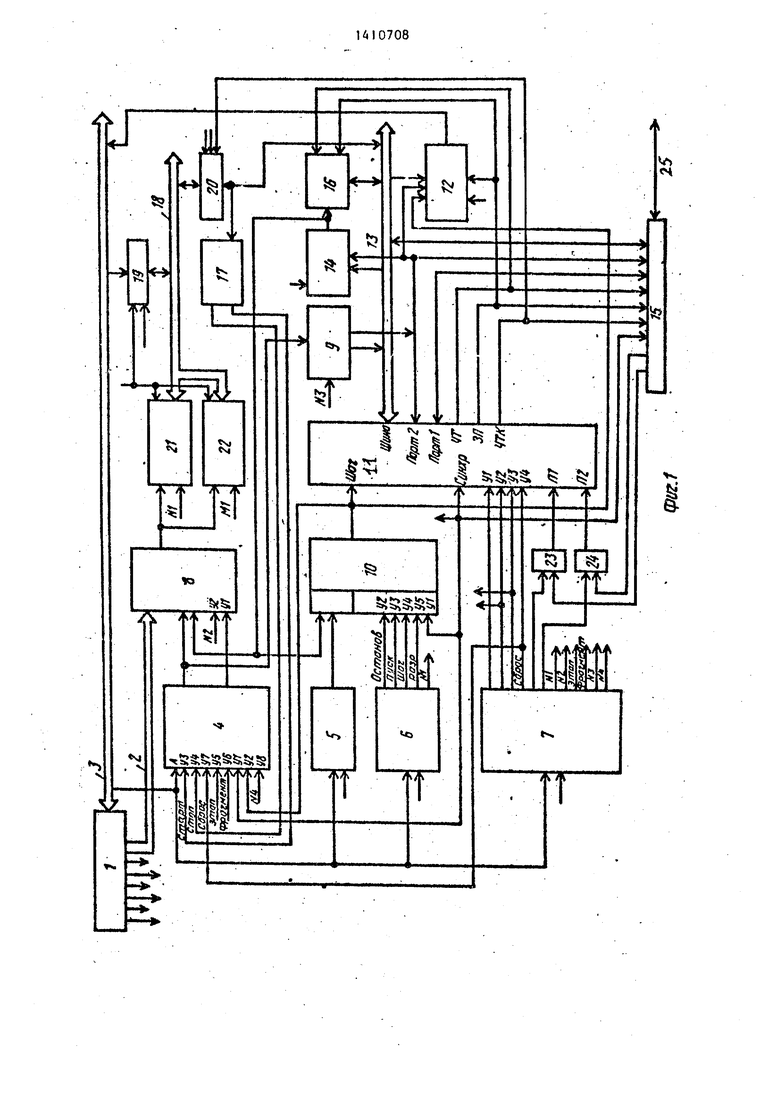

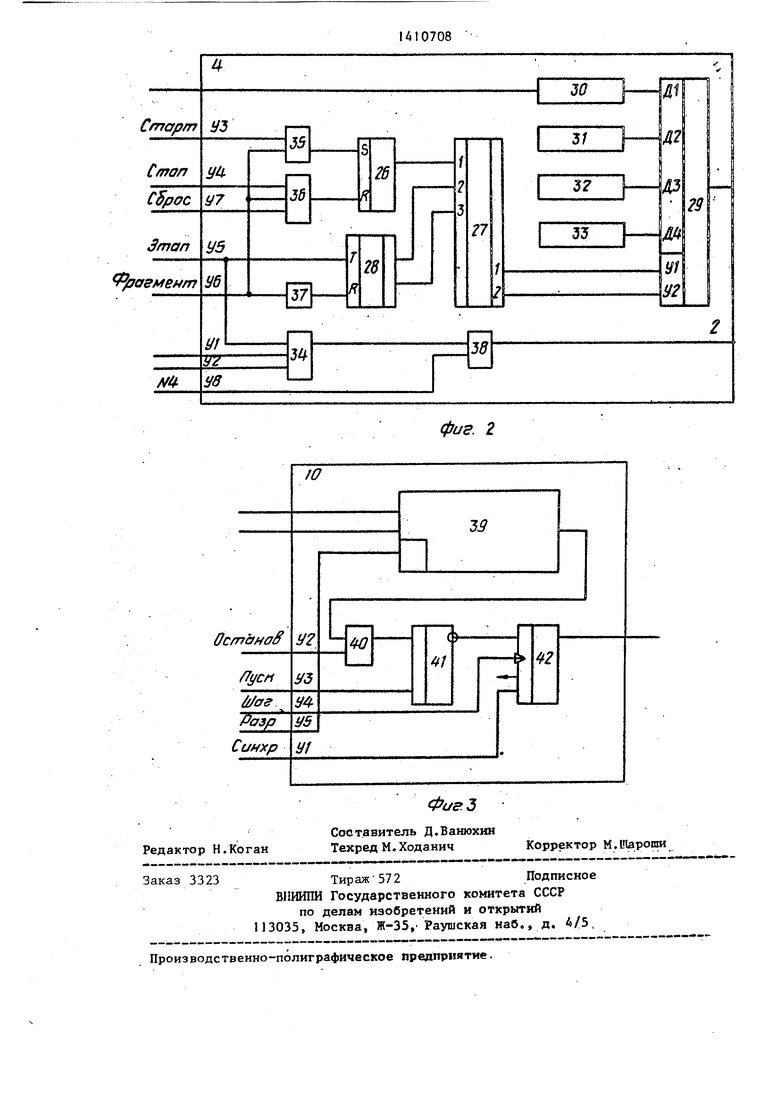

На фиг, 1 приведена стру стурная схема устройства для отладки Микро- ЭВМ; на фиг. 2 - структурная схема блока формирования адреса; на фиг. З структурная схема блока сравнения адреса. I .

Устройство содержит управляющую ЭВМ 1 с шиной 2 адреса и шиной 3 данных, блок А формирования адреса, .регистр 5 адреса останова, первый 6 и второй 7 регистры управления, мультиплексор 8, буфер 9 программирова- ния, блок 10 сравнения адреса, одно- кристалльную эмулирующую микроЭВМ П (ОМЭ 11), регистр 12 отображения, шину 13 данных эмулирующей микроЭВМ, регистр 14 адреса, буфер 15 пользователя, блок 16 памяти данных, дешифратор 17 команд, инфорМационньй вход- выход 8 блока памяти программ, первый коммутатор 19, второй коммутатор 20, воспомогательный блок 21 памяти, блок 22 памяти, программ, первый элемент ИЛИ 23, второй элемент ИЛИ 24, двунаправленную шину 25 устройства для подключения к отлаживаемой микроЭВМ-. - 1

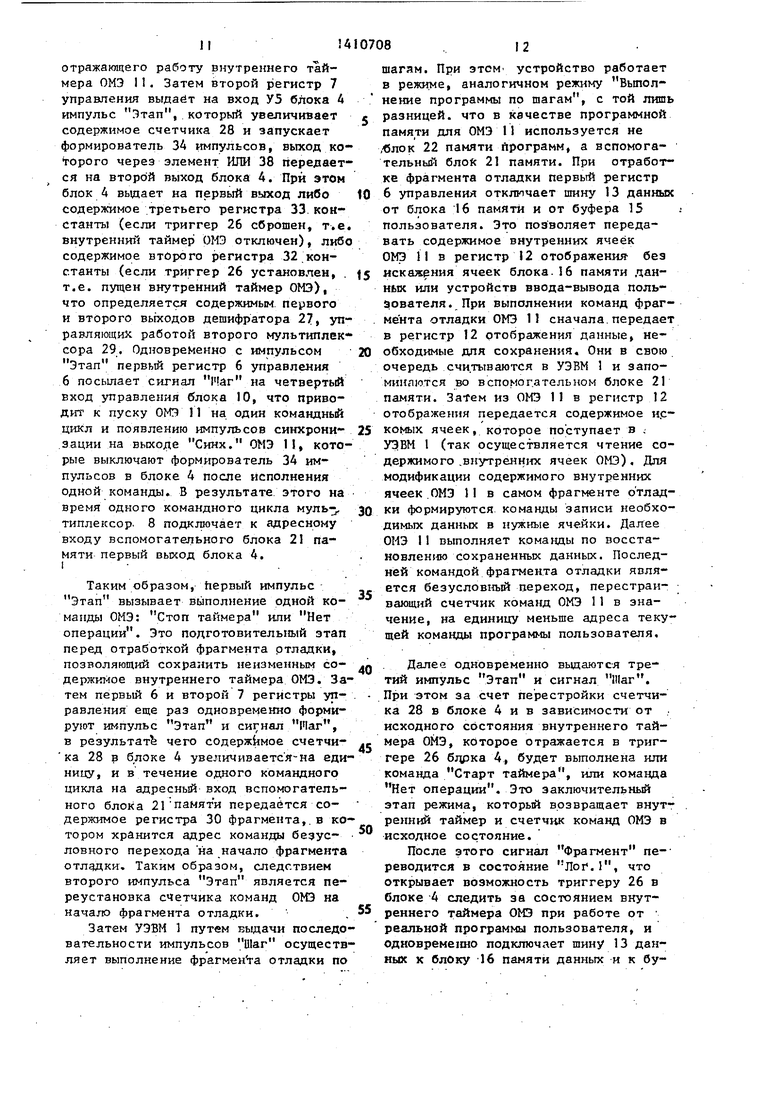

Блок 4 формирования адреса содержит триггер 26, шифратор 27, счетчик 28, мультиплексор 29, регистр 30 фрагмента, первь1Й 31, второй 32 и третий 33 регистры констант, второй формирователь 34 импульсов, первый элемент И 35, второй элемент И 36, первый формирователь 37 импульсов, элемент ИЛИ 38.

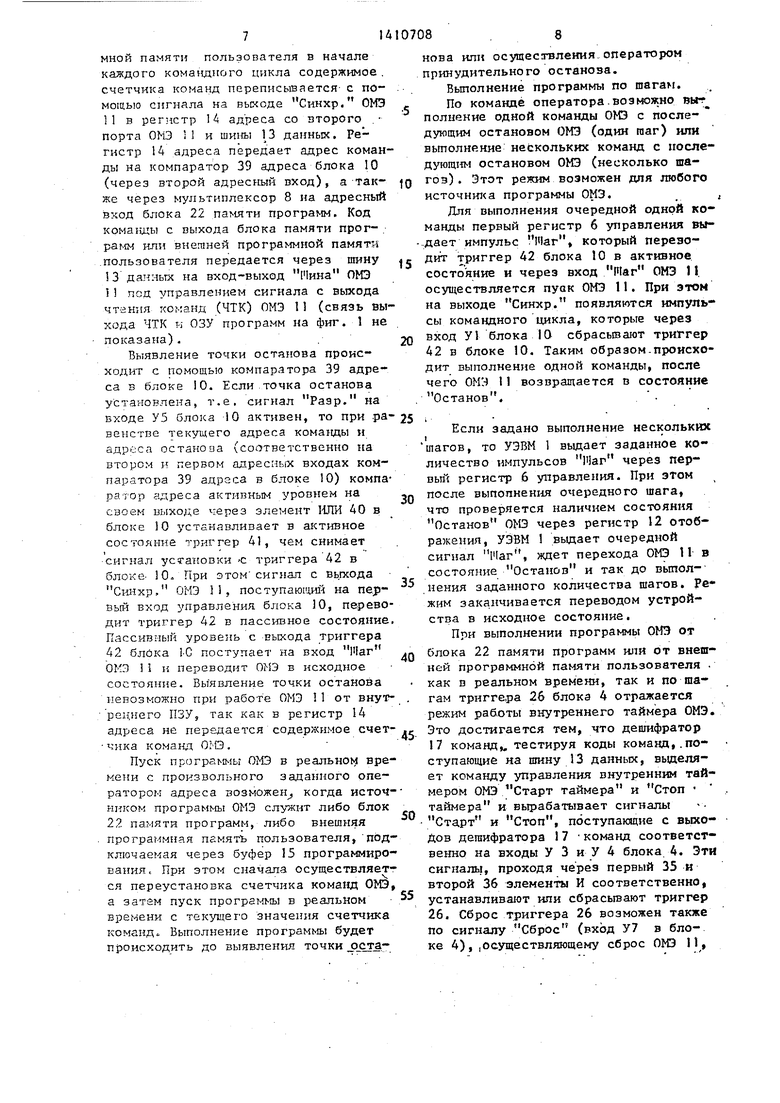

Таблица истинности шифратора 27 .

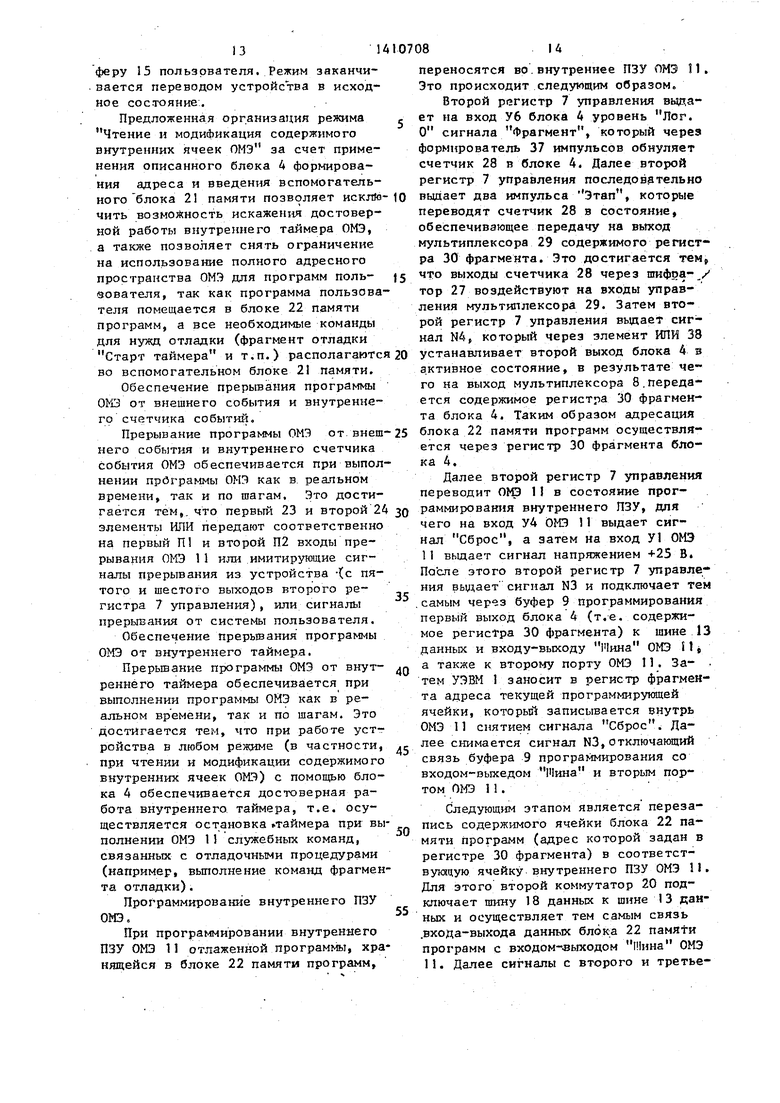

Блок 10 сравнения адреса содержит компаратор 39 адреса, элемент ИЛИ 40, первый триггер 41, второй триггер 42,

5

0

5 0 5 0

5

0

5

Устройство работает следуюнщм образом.

Управляющая ЭВМ 1 (УЭВМ) в символьном виде на ассемблере ОМЭ позволяет редактировать текстовые файлы, транслировать их в машинные коды ОМЭ И подготовить загрузочные модули программ пользователя. Кроме того, в памяти УЭВМ 1 размещается специальная программа Отладчик, которая управляет работой устройства. Программа Отладчик постоянно, поддерживает связь с оператором посредством терминала, входящего в состав УЭВМ 1. Управление режимами работы устройства происходит по командам оператора, набираемым на клавиатуре терминала, при этом вся необходимая информация

выводится на дисплей.

I

Устройство имеет следующие режимы работы:

1.Сброс микроэвм.

2.Загрузка программы пользователя в блок памяти программ.

3.Чтение и модификация блока па- мяти программ.

4.Выбор источника программы мик- роЭВМ.

3. Установка и сброс точки останова.

6.Переустановка счетчика команд микроэвм.

7.Пуск программы в реальном времени.

8.Выполнение программы по шагам.

9.Принудительньй останов программы.

10.Чтение и модификация содержимого внутренних ячеек микроЭВМ.

11.Обеспечение прерываний программы микроэвм от внешнего события или внутреннего счетчика событий.

12.Обеспечение прерьгоания программы микроэвм от внутреннего тай. мера.

13.Программирование внутреннего ПЗУ микроэвм.

14.Тестирование внутреннего ПЗУ микроэвм.

Каждый режим работы устройства представляет собой некоторую последовательность состояний устройства. Переключение устройства из одного состояния в другое осуществляется посылкой соответствующего кода из УЭВМ 1 в первый 6 и второй 7 регистры управления, выходы KOTOpbix соединены с

to

25

входами управления всех элементов устройства.

Все режимы работы устройства наминаются и заканчиваются исходным сос- тоянием устройства-. Исключение составляют режимы: Пуск программы в реальном времени и Принудительный останов.

В исходном состоянии устройства на выходах регистров 6 и 7 управления активный уровень имеет сигналу Ml и Фрагмент. Уровень сигнала, Разр. на выходе первого регистра 6 yпpaвлeн я и сигнала на первом выхо- 15 де второго регистра 7 управления в исходном состоянии может быть произвольным - это определяется последним выполненным режимом устройства, но при включении устройства они устанав-20 ливаются в пассивный уровень. Все остальные вькоды обоих регистров управления имеют в исходном состоянии пассивный уровень. В результате этого в исходном состоянии:

1)мультиплексор 8 соединяет шину 2 адреса с адресным входом блока 22 памяти программ;

2)вход-выход данных блока 22 памяти программ подключен к 1иине 18 данных, которая в свою очередь через первый коммутатор 19 соединена с шиной 3 данных, таким образом блок 22 памяти .программ подклю чен к УЭВМ 1 ;

3)ОМЭ 11 с помощью блока 10 переводится в состояние Останов. При этом ОМЭ 11 через шину 13 данных, а также через свой второй порт передает в регистр 12 отображения - содержимое своего счетчика команд;

А) выход блока 10 подключен к регистру 12 отображения и отображает наличие или отсутствие состояния Останов ОМЭ I1. Таким образом УЭВМ 1 при чтении через первую шину 3 дан- АС ных регистра 12 отображения получает информаиз ю о содержимом счетчика команд ОМЭ и состоянии Останов ОМЭ;

5) буфер 9 программирования от- . . ключает первьш выход блока 4 от шины 13 данных и от второго порта ОНЭ 11.

Устройство имеет два исходньтх состояния, обеспечивак9цих подготовку ОМЭ либо к работе от внутреннего ПЗУ ОЮ И, либо от блока 22 памяти, программ. Это определяется специальными командами оператора в режиме Выбор ис- точника программы ОМЭ. При включении питания устройство,переходит в

30

35

40

50

to

25

15 20 АС.

410708

исходно е состояние, ориентирующее ОМЭ 11 на рабо- у с блоком 22 памяти ,,

программ.

Работа устройства в указанных режимах происходит следуюпщм образом. Сброс ОМЭ.

В этом режиме второй регистр 7 управления выдает активный уровень сигнала СБРОС на вход У4 ОМЭ I1, который осуществляет сброс ОМЭ. При этим внутри ОМЭ 11 происходят необходимы переустановки, в частности обнуля-ет- ся счетчик команд и все порты переводится в отключенное состояние. Этот же сигнал обнуляет триггер в блоке 4., Режим заканчивается снятием сигнала СБРОС и переводом устройства в исход- ное состояние. .

Загрузка программы пользователя в блок-памяти программ.

В этом режиме подготовленный загрузочный модуль программ, пользователя из УЭВМ 1 переписыпается по- , в блок 22 памяти программ. За пись в блок памяти програм 1 осуществляется из ИСХОД1ЮГО состояния устройства с помощью сигна.па Запись в блок памяти программ от У/5ВМ I .

Чтение и модификпция блока памяти программ,

В этом режиме ня дисплей пыподится содержимое ячейки блока 22 памяти программ, адрес которой задан оператором с клавиатуры. Оператор может ввести в ячейку новое содержимое. Чтение и модификация блока памяти программ осуществляется из исходного состояния устройства с помощью сигна лов от УЭВМ 1 Запись в блок памятиi программ и Чтение блока памяти программ.

Выбор источника программы ОМЭ. Сначала второй регистр 7 управления выдает на вход У 4 ОЮ 11 актив- ньй уровень сигнала СБРОС, чем осуществляет сброс ОМЭ. Затем упомянутый регистр устанавливает на входе У1 ОМЭ 11 сигнала Лог. О (для работы ОМЭ I1 от внутреннего ПЗУ) или сигнал Лог. 1 для работы ОМЭ от блока 22 памяти программ или от внешней программной памяти пользователя, подключаемой через буфер 15 пользователя в соответствии с командой оператора. После этого снимается сигнал СБРОС, и устройство переходит в исходное состояние. Установленный при этом уровень сигнала на входе У1 ОМЭ

30

35

40

50

11 определяет в дальнейшем для всех последугапих режимов устройства ис- точник программы для ОМЭ.

Установка и сброс точки останова.

Установка точки дстанова используется для обеспечения возможности останова программы ОМЭ в заданном месте при выполнении Программы поль- зователя в реальном време ни.

При установке точки, останова УЭВМ 1 по шине 3 данных записывает в регистр 5 адреса останова заданный оператором адрес, а первый регистр 6 выдает активный уровень сигнала Разр.. При этом разрешается работа компаратора 39 адреса в блоке 10. Пр сбросе точки останова сигнал Разр, переводится в пассивный уровень, что запрещает работу компара- тора адреса 39 в блоке 10.

Переустановка счетчика команд.

Режим выполняется при работе ОМЭ I от блока 22 памяти программ или от внешней программной памяти пользо вателя. После распознавания команд оператора УЭВМ 1 формирует во вспомо ..гательном блоке 21 памяти код команды безусловного, перехода по указано- му оператором адресу. Для этого сиг- налы Ml и N1, воздействуя на входы управления соответственно блока 22 памяти про грамм и вспомогательного блока 21 памяти, подключают к шине 18 данных вход-выход вспомогательного блока 21 памяти (вместо блока 22 памяти программ). Айрес ячейки вспомогательного блока 21 памяти, содержащей код коматзды безусловного перехода по указанному адресу, заносится в регистр, 30 фрагмента блока А. Затем шина 18 данных подключается кг шине 13 данных через второй коммутатор 20. Далее, второй регистр 7 управления выдает на вход Уб блока А уровень Лог. о сигнала Фрагмент, который через формирователь 37 импульсов обнуляет счетчик 28, Затем второй регистр 7 управления последовательно выдает на вход У5 блока А два импульса Этап, которые переводят счетчик 28 в состояние, обеспечивающее передачу содержимого регистра 30 фрагмента на выход мультиплексора 29. Это достигается тем, что выходы счетчика 28 через 1пифратор 27 воздействуют па входы управления мультиплексора 29. Одновременно со вторым импульсом Этап первый ре

5 0

5 О д с

5

0

гистр 6 управления выдает на вход ОМЭ II сигнал аг, что приводит к пуску ОМЭ 1 1 на один командньЕй цикл и появлению импульсов С1шхроиизации на выходе Cimxp. ОМЭ 11, которые выключают формирователь 31 импульсов в блоке 4 после исполнения одной команды. В результате этого на время одного цсомандного цикла мультиплексор 8 Подключает к адресному входу вспомогательного блока 21 памяти первый выход блока 4, т.е. содержимое регистра 30 фрагмента. Таким образом ОМЭ 11 исполняет команду безусловного перехода по указанному адресу, т.е. перестраивает счетчик команд. Затем устройство переводится в исходное состояние.

Пуск программы в реальном времени.

Пуск программы ОЮ в реальном .времени возможен как с текущего значения счетчика команд, так и с произвольного заданного оператором адреса.

Пуск программы ОМЭ в реальном . . времени с текущего значения счетчика команд осуществим при любом источнике программы ОМЭ и выполняется следующим образом.

Мультиплексор 8 подключает выход регистра 14 адреса к адресному входу блока 22 памяти программ, вход-выход данных которого сигналом Ml подключается к шине 18 данных, которая через второй коммутатор 20 подключается к шине 13 данных. Таким образом блок памяти 22 программ подключен к ОМЭ 11 для работы. Далее первый регистр 6 управления формирует активный уровень сигнала Пуск, который поступает на третий вход управления блока 10. Сигнал Пуск сбрасьгоает триггер 41 в блоке 10 и устанавливает в блоке 10 триггер 42 в активное состояние, не зависящее от наличия сигнала на первом входе управления У1 .блока 10. Тем самым активизируется вход I lar ОМЭ II, в результате чего ОМЭ 11 начинает выполнять програ.мму в реальном времени либо от внутр.еннего ПЗУ, либо . от блока 22 памяти программ, либо от внешней программной памяти пользователя (в зависимости от того, что было выбрано ранее). Выполнение программы будет происходить до выявления точки останова или осуществления оператором принудительного останова.

При работе ОЮ 11 от блока 22 памяти программ KJjK внешней програм10

15

20

мной памяти пользователя в начале каждого кома1щиого цикла содержимое . счетчика команд переписывается- с помощью сигнала на вьсходе Синхр. ОЮ 11 в регистр 1А адреса со второго . порта ОЮ 11 и ШИ1Ш 13 данных. Регистр 14 адреса передает адрес команды на компаратор 39 адреса блока 10 (через второй адресный вход), а-также через мультиплексор 8 на адресный вход блока 22 памяти программ. Код комагуды с выхода блока памяти прог- или внешней программной памяти пользователя передается через шину 3 дакньтх на вход-выход Чина ОЮ 1 под управлением сигнала с выхода чт-гшш команд (НТК) ОМЭ 1 1 (связь ВЫ- хгзда ЧТК к ОЗУ программ на фиг. 1 не

показана).

Выявление точки останова происходит с помощью компаратора 39 адреса в блоке 10. Если точка останова установлена, т.е. сигнал Разр. на входе У5 блока 10 активен, то при -ра-25 Бвнстве текущего адреса команды и адреса останооа (соответственно на втором и первом адресных входах компаратора 39 адраса в блоке 0) компа- ра-тор адреса активным уровнем на своем выходе через элемент ИЛИ 40 в блоке 10 устанавливает в шстивное состояние триггер 41, чем снимает сигнал установки с триггера 42 в блоке- 10. При ЭТОМ сигнал с вьгхода Си1-1хр, ОМЭ 11, поступаю1|дий на первый вход управления блока 10, переводит триггер 42 в пассивное состояние, Пассивный уровезш с выхода триггера 42 блока 1C поступает на вход iHar ОМЗ J и переводит в исходное состояние. Выявление точки останова невозможно при работе ОМЭ 11 от внут рециего ПЗУ, так как в регистр 14 адреса не передается содержимое счет- чика команд ОМЭ.

Пуск программы ОЮ в реальном времени с произвольного заданного оператором адреса возможен когда источ- НИКОМ программы ОМЭ служит либо блок 22 памяти программ, либо внешняя

програт-мная память пользователя, подключаемая через буфер 15 программирования. При этом сначала осуществляется переустановка счетчика команд ОМЭ,

30

35

40

45

50

55

а затем пуск nporpai JMbi в реальном времени с текущего значения счетчика команд. Выполнение программы будет происходить до выявления точки JJCTJ,-

0

5

0

5

0

5

0

5

0

5

нова или осуществления.оператором принудительного останова.

Вьтолнение программы по шагам.

По команде оператора.возможно вьгг полнение одной команды ОЮ с последующим остановом ОМЭ (один гааг) или выполнение нескольких команд с после- остановом ОМЭ (несколько шагов) . Этот режим возможен для любого источника программы ОМЭ. ,

Для выполнения очередной одной команды первый регистр 6 управления вы- импульс Шаг, который переводит триггер 42 блока 0 в активное состояние и через вход Паг ОМЭ 11. осуществляется пуак ОМЭ 11. При этом на выходе Синхр. появляются импуль сы командного цикла, которые через вход У1 блока 10 сбрасывают триггер 42 в блоке 10. Таким образом.происходит выполнение одной команды, после чего ОМЭ 11 возвращается в состояние Останов. .

Еслн задано выполнение нескольких шагов, то УЭВМ 1 выдает заданное количество импульсов 1Чаг через пер- вьш регистр 6 управления. При этом после выполнения очередного шага, что проверяется наличием состояния Останов ОЮ через регистр 12 отображения, УЭВМ 1 выдает очередной сигнал Plar, ждет перехода ОМЭ 11 в состояние Останов и так до вьтол- нения заданного количества шагов. Режим заканчивается переводом устройства в исходное состояние.

При выполнении программы ОМЭ от

блока 22 памяти программ или от внешней программной памяти пользователя . как в реальном времени, так и по шагам триггера 26 блока 4 отражается режим работы внутреннего таймера ОМЭ. Это достигается тем, что дешифратор 17 команд,, тестируя коды команд,.поступающие на шину 13 данных, выделяет команду управления внутренним таймером ОМЭ Старт таймера и Стоп таймера и вырабатывает сигналы Старт и Стоп, пбступаквдие с выходов дешифратора 17 команд соответственно на входы У 3 и У 4 блока А. Эти сигналы, проходя через первый 35 и второй 36 элементы И соответственно, устанавливают ипи сбрасьгеают триггер 26. Сброс триггера 26 возможен также по сигналу Сброс (вход У7 в блоке 4), .осуществляющему сброс ОГО П,

.5

так как при сбросе ОМЭ происходит ос- тамов внутреннего таймера.

При выполнении программы ОМЭ от любого источника программы ОЮ устройство обеспечивает либо работу с реальной.отлаживаемой системой пользователя, п одключаемой через буфер 15 пользователя, либо имитирует работу системы пользователя. 10

Для имитации системы пользователя предложенное устройство содержит блок 16 памяти данных, а также первый 23 и второй 24 элементы ИЛИ. Блок 16 памяти данных служит щи имитации рабо- ты ОМЭ 11 с внешними относительно ОМЭ ячейками данных пользователя или устройствами ввода-Вывода пользователя. На вход блока 16 Памяти данных поступает адрес внешней ячейки данных с 20 регистра 14 адреса, а его вход-выход .подключается к шине 13 данных.

Первый элемент ИЛИ 23 передает на первый вход прерьтания П1 ОЮ 11 соответствующий сигнал от системы поль- 25 зователя или имитирующий сигнал прерывания с пятого выхода второго ре- гистра 7 управле1Шя. Второй элемент ИЛИ 24 передает на второй вход прерывания П2 ОНЭ 11 соответствующий сиг зо нал от системы пользователя или имитирующий сигнал прерьшания с выхода второго регистра 7 управления.

Принудительньй останов.

Этот режим позволяет осуществить останов выполнения программы ОМЭ при работе ОМЭ в реальном времени от лю- бого источника программы.

Для останова ОМЭ первый регис тр 6 управления формирует импульс. Оста- .jg нов, которьй, поступая на вход У2 блока 10, устанавливает в активное состояние триггер 41, чем снимает сигнал установки триггера 42. При этом сигнал с выхода Синхр ОЮ 11, Дд .поступающий на вход У1 блока 10, переводит триггер 42 в пассивное состояние. Пассивный уровень с выхода триггера 42 поступает на вход П1аг ОМЭ 11 и переводит ОМЭ в сЛэстояние Останов, После этого устройство переводится в исходное состояние.

Чтение и модификация содержимого внутренних ячеек ОМЭ.

Режим выполняется из исходного , со стояния, соответствуняцего работе ОМЭ от блока 22 памяти программ или .от внешней программной памяти пользо- . Чтение или модификация содер35

50

55

5

0

0

5 о

jg Дд

5

50

55

жимого внутренней ячейки ОМЭ достигается тем, что ОМЭ I1 принудительно переключается на выполнение специального программного фрагмента отладки, записанного во вспомогательном блоке 21 памяти. HasHa ieime фрагмента отладки состоит в считывании или записи интересуемой ячейки ОЮ 11. Так как обращение к внутренним ячейкам ОМЭ возможно только через аккумулятор или регистры общего назначения, то это приводит к потере действительной информации пр ограммы пользователя. Поэтому фрагмент отладки должен Также содержать команды дпя сохранения и последующего .восстановления действительной информации. Кроме того, фрагмент отладки должен содержать команду возврата в программу пользователя. После распознавания команды оператора УЭВМ 1 запоминает адрес текущей команды программы пользователя. Далее для перехода к выполнению фраг , мента отладки УЭВМ 1 формирует во вспомогательном блоке 21 памяти код команды безусловного перехода на Фрагмент отладки, а адрес этой команды записывает в регистр 30 фрагмента блока 4. Затем УЭВМ I формирует во вспомогательном блоке 21 памяти собственно фрагмент отладки. Кроме того, для обеспечения правильной работы внутреннего таймера ОМЭ 11 во вспомогательном блоке 21 памяти формируются: кОд команды Старт таймера (по адресу, хранящег уся в первом регистре 31 константы); код командь Стоп- таймера (по адресу, хранящемуся во втором регистре 32 константы)};И код команды Нет операции (по адресу, хранящемуся в третьем регистре 33 константы).

Затем УЭВМ 1 подключает ОЮ П к вспомогательному блоку 21 памяти, для чего мультиплексор 8 передает на адресньй вход вспомогательного блока 21 памяти вход регистра 14, а вход- выход данных вспомогательного блока 2 памяти через шину 18. данных и второй коммутатор 20 подключается к шине 13 данных. Далее второй регистр 7 управления вьщает на вход У6 блока 4 уровень Лог, О, сигнала Фрагмент, который, во-первых, через формирователь 37 импульсов обнуляет счетчик 28, Га, во-вторых, через первый 35 И, второй 36 элемент И запре- щает изменение состояния триггера 26,t

отражающего работу внутреннего таймера ОМЭ II. Затем второй регистр 7 управления выдаёт на вход У5 блока 4 импульс Этап, который увеличивает содержимое счетчика 28 и запускает формирователь ЗА импульсов, выход которого через элемент ИЛИ 38 передается на второй выход блока А. При этом блок А выдает на первый выход либо содержимое третьего регистра 33.константы (если триггер 26 сброшен, т.е. внутренний таймер ОМЭ отключен), либо содержимое второго регистра 32 константы (если триггер 26 установлен, . т.е. пущен внутренний таймер ОМЭ), что определяется содержимым, первого и второго вьгходов дешифратора 27, управляющих работой второго мультиплексора 29. Одновременно с импульсом Этап первый регистр 6 управления 6 посылает сигнал на четвертый вход управления блока 10, что приво- Д1-ГГ к пуску ОМЭ 11 на один командный цикл и появлению импульсов синхрони- зации на выходе Синх. ОМЭ II, которые выключают форм}фователь ЗА импульсов в блоке А после исполнения одной команды. В результате, этого на время одного командного цикла муль-;; типлексор. 8 подключает к адресному входу вспомогательного блока 21 памяти первый выход блока А.

Таким образом, Ьервый импульс Этап вызывает выполнение одной команды ОМЭ: Стоп таймера или Нет операции. Это подготовительный этап перед отработкой фрагмента ртладки, позволяющий сохранить неизменным содержимое внутреннего таймера ОМЭ. Затем первый 6 и второй 7 регистры уп- равления еще раз одновременно формируют импульс Этап и сигнал Шаг, в результат чего содержимое счетчи- ка 28 в блоке А увеличивается-на единицу, и в течение одного командного цикла на адресный вход вспомогательного блока 21 памяти передается содержимое регистра 30 фрагмента,.в котором хранится адрес команды безус- лонного перехода на начало фрагмента отладки. Таким образом, следствием второго импульса Этап является переустановка счетчика команд ОМЭ на начало фрагмента отладки. .

Затем УЭВМ 1 путем выдачи последовательности импульсов Шаг осуществляет выполнение фpaгмeнVa отладки по

« 0 0 5 О

- .

5

0

0

шагам. При этом устройство работает в режиме, аналогичном режиму Вьтол- нение программы по шагам, с той лишь разницей, что в качестве программной памяти для ОМЭ 11 используется не .-блок 22 памяти йрограмм, а вспомогательный блок 21 памяти. При отработке фрагмента отладки первый регистр 6 управления отключает шину 13 данных от блока 16 памяти и от буфера 15 : пользователя. Это позволяет передавать содержимое внутренних ячеек ОМЭ П в регистр 12 отображения без искажения ячеек блока.16 памяти данных или устройств ввода-вывода пользователя. При выполнении команд фрагмента отладки ОЮ 11 сначала, передает в регистр 12 отображения данные, необходимые дпя сохранения. Они в свою очередь считываются в УЭВМ 1 и запо- минлются во вспомогательном блоке 21 памяти. Затем из ОМЭ 11 в регистр 12 отображения передается содержимое и.с- комых ячеек, которое поступает в . УЭВМ I (так осуществляется чтение содержимого .внутренних ячеек ОМЭ). Дпя модификации содержимого внутренних ячеек.ОМЭ П в самом фрагменте отладки формируются команды записи необходимых данных в нужные ячейки. Далее ОМЭ I1 выполняет команды по восста- новлен) сохраненных данных. Последней командой фрагмента отладки является безусловньй переход, перестраи- ; ааквдий счетчик команд ОЮ 11 в значение, на единицу меньше адреса текущей команды программы пользователя.

Далее одновременно вьздаютс-я третий импульс Этап и сигнал Шаг. При этом за счет перестройки счетчика 28 в блоке Айв зависимости от исходного состояния внутреннего таймера ОМЭ, которое отражается в триггере 26 бдрка А, будет вьтолнена или команда Старт таймера, или команда Нет операции. Это заключительный этап режима, которьй возвращает внутренний таймер и счетчик команд ОМЭ в исходное состояние.

После этого сигнал Фрагмент переводится в состояние Лог., что открывает возможность триггеру 26 в блоке А следить за состоянием внутреннего таймера ОМЭ при работе от реальной программы пользователя, и одновреме1шо подключает шину 13 данных к блоку 16 памяти данных и к буферу 15 пользователя. Режим заканчивается переводом устройства в исходное состояние.

Предложенная организация режима , Чтение и модификация содержимого внутренних ячеек ОМЭ за счет применения описанного блока 4 формирования адреса и введения вспомогательного блока 21 памяти позволяет исклй- Ю чить возможность искажения достоверной работы внутреннего таймера ОЮ, а также позволяет снять ограничение на использование полного адресного пространства ОМЭ для программ поль- |5 зователя, так как программа пользователя помещается в блоке 22 памяти программ, а все необходимые команды для нужд отладки (фрагмент отладки

переносятся во.внутреннее ПЗУ ОМЭ 11 Это происходит следующим образом.

Второй регистр 7 управления вьща- ет на вход У6 блока 4 уровень Лог. О сигнала фрагмент, который через формирователь 37 импульсов обнуляет счетчик 28 в блоке 4. Далее второй регистр 7 управления последовательно выдает два импульса Этап, которые переводят счетчик 28 в состояние, обеспечивающее передачу на мультиплексора 29 содержимого регистра 30 фрагмента. Это достигается тем что выходы счетчика 28 через шифоа- / тор 27 воздействуют на входы управления мультиплексора 29. Затем второй регистр 7 управления выдает сигнал N4, который через элемент ИПИ 38

Старт таймера и т.п.) располагаются 20 устанавливает второй выход блока 4 в

переносятся во.внутреннее ПЗУ ОМЭ 11. Это происходит следующим образом.

Второй регистр 7 управления вьща- ет на вход У6 блока 4 уровень Лог. О сигнала фрагмент, который через формирователь 37 импульсов обнуляет счетчик 28 в блоке 4. Далее второй регистр 7 управления последовательно выдает два импульса Этап, которые переводят счетчик 28 в состояние, обеспечивающее передачу на мультиплексора 29 содержимого регистра 30 фрагмента. Это достигается тем что выходы счетчика 28 через шифоа- / тор 27 воздействуют на входы управления мультиплексора 29. Затем второй регистр 7 управления выдает сигнал N4, который через элемент ИПИ 38

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1984 |

|

SU1238086A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

Изобретение относится к вычислительной технике и может быть исполь- зова1То для автоматизации отладки ., программ в реальном м штабе времени для специализированных программных устройств на базе однокристальной микроэвм (ОЮ), для записи отлажен- ных программ пользователя во внутреннее постоянное запоминакмее устройство (ПЗУ) ОМЗ и для отладки аппаратной част 1 программш.-к устроПств на базе . ОМЭ. Изобретение позволяет повысить. производительность процесса отладки за счет предоставления лользоватеяю полного адресного пространства для размещения программ, обеспечения в пошаговом режиме функций таймера и прерываний, а также за счет реализации возможностей записи и контроля информации во внутре}и1бм ПЗУ. Устройство для отладки микроЗВМ содержит блок формирования адреса, регистр адреса останова, два регистра управления, мультиплексор, блок ключей, блок сравнения адреса, эмулирую;- щуто микроЗВМ, регистр отображения, регистр адреса, блок памяти данных, дешифратор команд, два коммутатора, .вспомогательньй блок памяти, блок памяти программ, два элемента ИЛИ. Устройство имеет входы и выходы для ;подклгочен1« к управляющей ЗВМ и имеет средства дпя подключения к отла- - живаемой микроЗВМ. 2 з.п. ф-лы,3 ип., 1 табл. (Л с 141 О

во вспомогательном блоке 21 памяти.

Обеспечение прерывания программы ОКЗ от внешнего события и внутреннего счетчика событий.

Прерывание программы ОМЭ от внешнего события и внутреннего счетчика события ОМЭ обеспечивается при выполнении программы ОМЭ как в реальном времени, так и по шагам. Это достигается тем,, что первый 23 и второй 24 зо раммирования внутреннего ПЗУ,

элементы ИЛИ передаЕот соответственно на первый П1 и второй П2 входы прерывания ОМЭ 1 1 или имитируннцие сигналы прерывания из устройства -{с пятого и шестого выходов второго регистра 7 управления), или сигналы прерывания от системы пользователя.

Обеспечение прерьгоания программы ОЮ от внутреннего таймера.

Прерьшание программы ОМЭ от внутреннего таймера обеспечивается при выполнении программы ОМЭ как в реальном времени, так и по шагам. Это достигается тем, что при работе устройства в любом режиме (в частности, при чтении и модификации содержимого внутренних ячеек ОМЭ) с помощью блока 4 обеспечивается достоверная работа внутреннего таймера, т.е. осуществляется остановка «таймера при выполнении ОМЭ 11 служебных команд, связанных с отладочными процедурами (например, выполнение команд фрагмента отладки).

Программирование внутреннего ПЗУ ОЮ.

При программировании внутреннего ПЗУ ОМЭ 11 отлаженной программ, хранящейся в блоке 22 памяти программ.

35

40

45

50

55

чего на вход У4 ОМЭ 11 выдает нал Сброс, а затем на вход 1I вьщает сигнал напряжением После этого второй регистр 7 ния вьщаег сигнал N3 и подклю самым через буфер 9 программи первый выход блока 4 (т.е. со мое регистра 30 фрагмента) к данных и входу-выходу 1Чина а также к второму порту ОЮ 1 тем УЭВМ 1 заносит в регистр та адреса текущей программирую ячейки, который записывается ОМЭ 11 снятием сигнала Сброс лее снимается сигнал N3,отклю связь буфера 9 программировани входом-выхедом 1Чина и вторым том ОМЭ 11.

Следующим этапом является пись содержимого ячейки блока мяти программ (адрес которой регистре 30 фрагмента) в соотв вукячую ячейку внутреннего ПЗУ Для этого второй коммутатор 20 ключает шину 18 данных к шине ных и осуществляет тем самым .входа-выхода данных блока 22 п программ с входом-выходом Шин П. Далее сигналы с второго и

а.ктивное состояние, в результате чего на выход мультиплексора 8.передается содержимое регистра 30 фрагмента блока 4. Таким образом адресация блока 22 памяти программ осуществляется через регистр 30 фрагмента блока 4.

Далее второй регистр 7 управления переводит 1 в состояние прого раммирования внутреннего ПЗУ,

5

0

5

0

5

для

чего на вход У4 ОМЭ 11 выдает сигнал Сброс, а затем на вход У1 ОМЭ 1I вьщает сигнал напряжением +25 В. После этого второй регистр 7 управления вьщаег сигнал N3 и подключает тем самым через буфер 9 программирования первый выход блока 4 (т.е. содержимое регистра 30 фрагмента) к шине 13 данных и входу-выходу 1Чина ОЮ П j а также к второму порту ОЮ 11 . За- . тем УЭВМ 1 заносит в регистр фрагмента адреса текущей программирующей ячейки, который записывается внутрь ОМЭ 11 снятием сигнала Сброс. Далее снимается сигнал N3,отключающий связь буфера 9 программирования со входом-выхедом 1Чина и вторым портом ОМЭ 11.

Следующим этапом является перезапись содержимого ячейки блока 22 памяти программ (адрес которой задан в регистре 30 фрагмента) в соответст- вукячую ячейку внутреннего ПЗУ ОМЭ 11. Для этого второй коммутатор 20 подключает шину 18 данных к шине I3 данных и осуществляет тем самым связь .входа-выхода данных блока 22 памяти программ с входом-выходом Шина ОМЭ П. Далее сигналы с второго и третьего выходов второго регистра 7 управ-4. ления осуществляют запись вводимого ; кода во внутреннее ПЗУ ОМЭ 11. Для записи новой ячейки сигналом N3 снова роЭВМ, причем вход-выход данных устройства для подключения к двунапраарамм, первый и .второй коммутаторы, дешифратор команд, регистр адреса, блок памяти данных и эмулирующую Микподключается буфер 9 программирования, УЭВМ 1 заносит в.регистр 30 фрагмента новый адрес, и процесс повторяется. ,

Тестирование внутреннего ПЗУ ОМЭ.

В этом режиме содержимое внутреннего ПЗУ ОМЭ 11 переносится во вспомогательный блок 21 памяти. В дальнейшем эта информация может быть либо

ленной шине данных управлякщей ЭВМ подключен к информационным входам регистра адреса останова и первого 10 регистра управления и К первому информационному входу-выходу первого коммутатора, т формацион1п й вход-выход блока памяти программ соединен с вторым информационным входом-выходом

вьгеедена на дисплей, либо пройти по- 5 . кoм fyтaтopa и с первым ин30

байтное сравнение с эталонной программой, расположенной в блоке 22 памяти программ. Последовательность работы устройства в этом режиме следующая .-20

Первый б и второй 7 регистры управления с помощью сигналов N1 и Ml подключают к шине 8 данных вспомога- тельньй блок 21 памяти вместо блока 22 памяти программ..Далее аналогично 25 режиму - Программирование внутреннего ПЗУ ОНЭ обеспечивается передача на выход мультиплексора 8 содержимого регистра 30 фрагмента блока 4 и запись адреса текущей ячейки внутрь ОМЭ 1 1 . Поел-е этого второй регистр 7 управления, воздействуя на входы У2 и УЗ ОЮ 11, обеспечивает передачу содержимого текущей ячейки внутреннего ПЗУ из ОМЭ I1 через вход-выход Шина ОМЭ 11 по шине 13 данных через второй коммутатор 20 и шину 18 данных во вспомогательньп блок 2 памяти. .

Далее УЭВМ 1 заносит в регистр 30 фрагмента блок 4 адрес следующей счи- тывак)щей ячейки и процесс .повторяется снова. После переноса всего сбдержимого внутреннего ПЗУ 11 во вспомогательный блок 21 памяти УЭВМ 1 в

зависимости от крма1гды оператора осуществляет либо побайтное сравнение содержимого вспомагательного блока

21 памяти с эталонной программой, расположенной в блоке 22 памяти программ, либо индикацию на дисплее за- данных ячеек.

Формула и 3 о б р е т е н и я

формационным входом-выходом второго коммутатора, второй информационный вход-выход которого соединен с инфо мационныьС входом дешифратора команд и подключен к двунаправленной данных эмулирующей 1 1кроЭВМ, двунаправленная шипа данных эмулирующей. микроэвм подключена к 1П{формационно му входу-выходу блока памяти -данных к первому информационному входу регистра адреса и к входу-выходу данных устройства для подключения к дв направленной шине -адреса1, от лаживаемой микроЭВМ, первая и этора группы информационных входов-выходо эмз лн рующей №1кроЭВМ подключены соответственно к первой и второй г руп пам информационных входов-выходов устройства для подключения к дауна- правленпой шине данньтх адреса отла г 35 живаемой миКроЭВМ, выходы чтения и записи эмулирующей микроЭВМ соедине ны с входами соответственно чтения и записи блока памяти дашшгх и прд- ключены к выходам соответственно чтения и записи.устройства для подключения к двунаправленной шине уп- равлен 1я отлаживаемой микроЭВМ,, выход чтения команд эмулирующей микро- ЭВМ соединен с первым управляющим входом второго коммутатора и подключен к выходу чтения команд устройства для подключения к двунаправленной шине управления отлаживаемой микро- ЭВМ; выход синхронизации змулируюп й ммкроЭВМ соединен с-входом записи ре гистра адреса, с установочным входом блока сравнения адреса и подключен к выходу синхронизации устройства для подключения к Двунаправленной шине управления .отлаживаемой микроЭВМ, вы ходы первогоi в.торого, третьего и четвертого разрядов первого регистра управления соединены с входами соот40

45

роЭВМ, причем вход-выход данных устройства для подключения к двунапраарамм, первый и .второй коммутаторы, дешифратор команд, регистр адреса, блок памяти данных и эмулирующую Микленной шине данных управлякщей ЭВМ подключен к информационным входам регистра адреса останова и первого регистра управления и К первому информационному входу-выходу первого коммутатора, т формацион1п й вход-выход блока памяти программ соединен с вторым информационным входом-выходом

30

20

25

5

формационным входом-выходом второго коммутатора, второй информационный вход-выход которого соединен с инфор мационныьС входом дешифратора команд и подключен к двунаправленной . данных эмулирующей 1 1кроЭВМ, двунаправленная шипа данных эмулирующей. микроэвм подключена к 1П{формационног му входу-выходу блока памяти -данных, к первому информационному входу ре. гистра адреса и к входу-выходу данных устройства для подключения к двунаправленной шине -адреса1, отлаживаемой микроЭВМ, первая и эторая группы информационных входов-выходов эмз лн рующей №1кроЭВМ подключены соответственно к первой и второй г руп- пам информационных входов-выходов устройства для подключения к дауна- правленпой шине данньтх адреса отла г 5 живаемой миКроЭВМ, выходы чтения и записи эмулирующей микроЭВМ соединены с входами соответственно чтения и записи блока памяти дашшгх и прд- ключены к выходам соответственно чтения и записи.устройства для подключения к двунаправленной шине уп- равлен 1я отлаживаемой микроЭВМ,, выход чтения команд эмулирующей микро- ЭВМ соединен с первым управляющим входом второго коммутатора и подключен к выходу чтения команд устройст ва для подключения к двунаправленной шине управления отлаживаемой микро- ЭВМ; выход синхронизации змулируюп й ммкроЭВМ соединен с-входом записи регистра адреса, с установочным входом блока сравнения адреса и подключен к выходу синхронизации устройства для подключения к Двунаправленной шине : управления .отлаживаемой микроЭВМ, выходы первогоi в.торого, третьего и четвертого разрядов первого регистра управления соединены с входами соот0

5

17

зации н разрешения блока сравнения адреса, выход пятого разряда первого регистра управления соединен с входом разрешения блока памяти программ, входы записи первого регистра управ- ления и регистра адреса останова под- ключены соответственно к первому и второму входам записи устройства для подключения к вьпсодйой шине управления управляющей ЭВМ, выход регистра адреса останова соединен с первь1М информационным входом блока сравнения адреса, выход регистра адреса соединен с адресным входом блока памяти данных и с вторым информационньм входом блока сравнения адреса, выход которого соединен с входом Шаг эмупирующей микроэвм, вторая группа ин- формационных входов-вьтодов эмулирующей микроэвм образует второй информационный вход регистра адреса, вход записи блока памяти программ и первый управляющий вход первого крммута- тора подключены к третьему входу записи устройства для подключения к выходной шине управления управляющей ЭВМ, второй управляющий вход первого коммутатора подключен к четвертому входу записи устройства для подключения к вькодной шине управления -управляющей ЭВМ, отличающееся тем, что, с целью повьшения производительности нроцесса отладки, оно содержит второй регистр управления, первый и второй элементы ИЛИ, регистр отображения, блок ключей, вспомога- тальньй блок памяти, мультиплексор и блок юрнирования адреса, информа-

ционный вход .второго регистра управления и выход регистра отображения подключен к входу-выходу данных устройства для подключения к двунаправленной шине данных управляющей ЭВМ, выход синхронизаияи эмулирующей мик- роЭВМ соединен с первым входом синхронизации блока формирования адреса, выход блока сравнения адреса соединен с вторым входом синхронизации блока формирования адреса, входы пуска и . останова которого соединены соответственно с первым и вторым выходом дешифратора команд, первый выход блока формирования адреса соединен с первым информационным входом мультиплек- сора и с информационным входом блока ключей, первый и второй выходы которого подключены соответственно к дву

10

15

20 25зоi45

55 1070818

направленной шине данных эмулирующей микроэвм и к второй группе информационных входов-выходов эмулирующей микроэвм, второй выход Ълока формирования адреса соединен с первым управляющим входом мультиплексора, второй и третий информационные входы которого соединены с адресным входом устройства дпя подключения к выходной шине адреса управляющей ЭВМ и с выходом регистра адреса, выход мультиплексора соединен с адресными вхо- дами блока памяти программ и вс.помо- гательного блока памяти, информационный вход-выход которого соединен С информационным входом-выходом блока памяти программ, вторым информационным входом-выходом первого KONO-syTaTO- pa и первым информационным входом- выходом второго коммутатора, первый вход записи вспомогателького блока памяти подключен к третьему входу. записи устройства для подключения к выходной шине управления управляющей ЭВМ, первый ш1формационньй вход регистра отображения подкл очен к второй группе информационных входов-вы ходов эмулирующей микроЭВМ, второй и третий информационные входы регистра отображения соединены соответственно с двунаправленной шиной данных эмулирующей микроэвм и с выходом блока сравнения адреса, выход записи эмулирующей микроэвм соединен с входом записи регистра отображения, вход чтения которого подключен к входу чтения устройства для подключения к выходной шине управления управляющей ЭВМ, разряд выхода второго регистра управлен11Я соединен с входом выбора источника программ эмулирующей микроэвм, второй разряд выхода второго {регистра управленг1Я соединен с первым входом управления вводом вы-- водом .эмулирутощей микроЭВМ и t вторьп 1 управляющим входом второго та тора, третий разряд выхода второго регистра управления соединен с вторым входом управления-вводом-выводом эму- лирзпощей микроэвм, с третьим управ-/ ляЮщим входом второго коммутатора и с вторым входом записи вспомогательного блока памяти, четвертый разряд выхода второго регистра управления соединен с входами сбро.са эмулирутощей. микроэвм и блока формирования адреса, С-,пятого по двенадцатый разряды выхода второго регистра управле35

50

ння соединены соответственно с первым входом первого элемента ИЛИ, с первым входом второго элемента ИЛИ, с входом разрешения вспомогательного блока памяти, с вторым управляющим . входом мультиплексора, с входом признака Этап блока формирования адреса, с входом приэнака Фрагмент блока формирования ад.реса, с управляю- щим входом блока ключей и с разрешающим входом блока формирования адреса, вторые входы первого и второго элементов ИЛИ подключены соответственно к первому и второму входам прерывания устройства дпя подключени к двунаправленной шине управления отлаживаемой микроэвм, выходы первого и второго элементов ИЛИ соединены соответственно с первым и вторым вхо дами прерывания эмулирующей микро- ЭВМ, вход записи второго регистра управления соединен с пятым входом записи устройства для подключения к выходной шине управления управляю- щей ЭВМ.

-

тем, что блок форми3. Устройство по п.1, о т л и

чающееся рования адреса.содержит первый и.второй элементы И, триггер, счетчик, первый и второй формирователи импульсов, элемент ИШТ, шифратор, регистр фрагмента, первый, второй и третий регистры константы и мультиплексор, выход которого является пер

вым выходом блока, первый, второй, третий и четвертый информационные i входы мультиплексора соединены с выходами соответственно регистра фра г- мента, первого, второго и третьего регистров константы, информационный вход регистра фрагмента является ин- формационньм входом блока, первый вход первого элемента И, первый и второй входы второго- элемента И являются соответственно входами-пуска, останова и сброса блока, выходы первого и второго элементов И соединены соответственно с С и R-входами триггера, выход которого.соединен с.первым входом шифратора, второй и третий входы которого соединены соответственно с первым и вторым выходами счетчика, вход сброса которого соединен с выходом первого формирователя импульсов, счетный вход счетчика и первый вход второго форьшрова- теля импульсов подключены к входу признака Этап блока, вход первого формирователя импульсов, второй вход первого элемента И и третий вход второго элемента И подключены к входу признака Фрагмент блока, второй и третий входы второго формирователя импульсов являются первым и вторым входами синхронизации блока, вход разрешения блока подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом второго фо.р- мирователя импульсов, выход элемен- та ИЛИ является вторым выходом блока первый и второй выходы шифратора соединены соответственно с первым и вторым управляющими входами мультиплексора.

Останов

У2

f7ycfi

УЗ

aff

У4

Разр

У5

Синжр

У/

фиг. 2

(Ь

4f/

2

| Wybranp | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

Авторы

Даты

1990-09-15—Публикация

1985-11-04—Подача