0 Ј

О 1

оо

оо

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| ВЫХОДНОЙ КАСКАД ДЛЯ КМОП МИКРОСХЕМ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2014 |

|

RU2560822C1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

Изобретение относится к цифровой технике и может быть использовано в микросхемах программируемой логики, динамически реконфигурируемых БИС, микропроцессорах и прочих устройствах обработки дискретной информации с использованием оперативного запоминающего устройства (ОЗУ) в качестве управляющей памяти. Цель изобретения - повышение быстродействия ячейки памяти. Поставленная цель достигается за счет введения третьего ключевого элемента 10 на р-каналь- ном МОП. При этом ячейка памяти устойчиво функционирует пои записи как Лог. О, так и Лог, 1, не требуя понижения напряжения питания ячейки до какого-то промежуточного значения, т.е. исключаются по сравнению с прототипом временные потери на переход напряжения питания от одного значения к другому, и наоборот. Перезаряд точки соединения стоковых областей элементов 3, 4 схемы лог. О к Лог, 1 происходит быстрее вследствие отрыва элемента 3 от потенциала шины 8 ячейки, что, в свою очередь, приводит к уменьшению размеров элемента 5 до размеров элементов 3, 4 и, как следствие, ведет к уменьшению площади, занимаемой ячейкой. 1 ил. §

Изобретение относится к цифровой технике и может быть использовано в микросхемах программируемой логики, динамически реконфигурируемых БИС, микропроцессорах и прочих устройствах обработки дискретной информации с использованием оперативного запоминающего устройства (ОЗУ) в качестве управляющей памяти.

Цель изобретения - повышение быстродействия ячейки памяти.

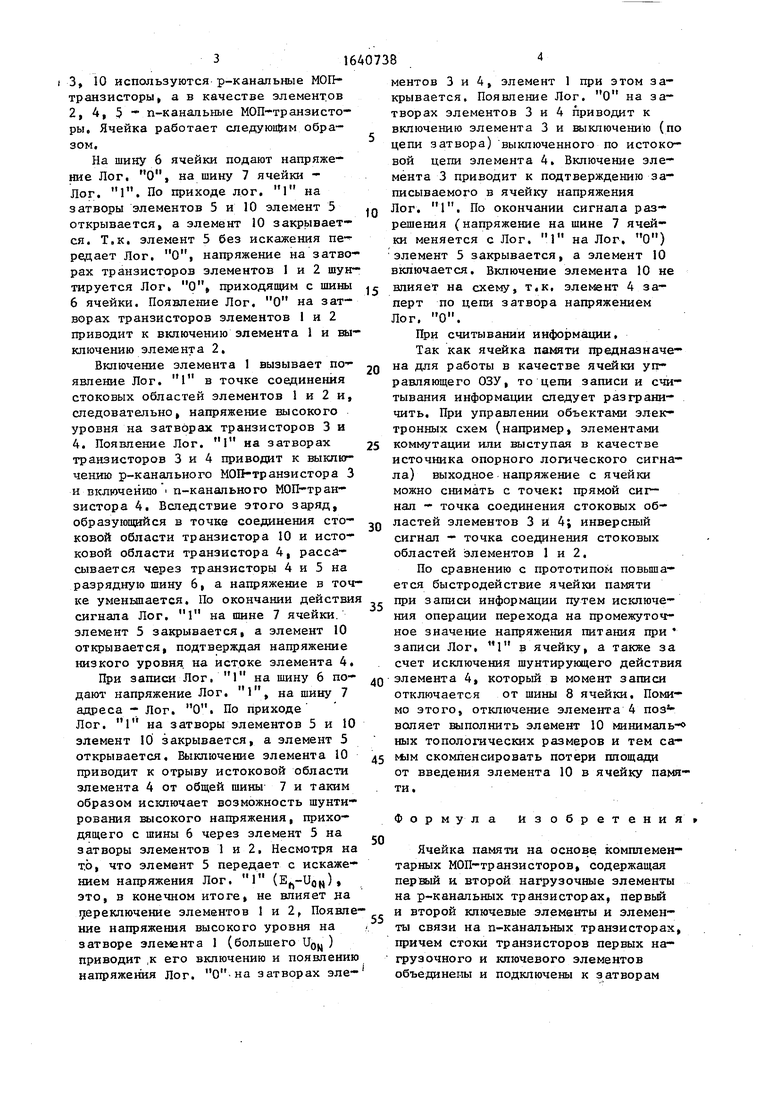

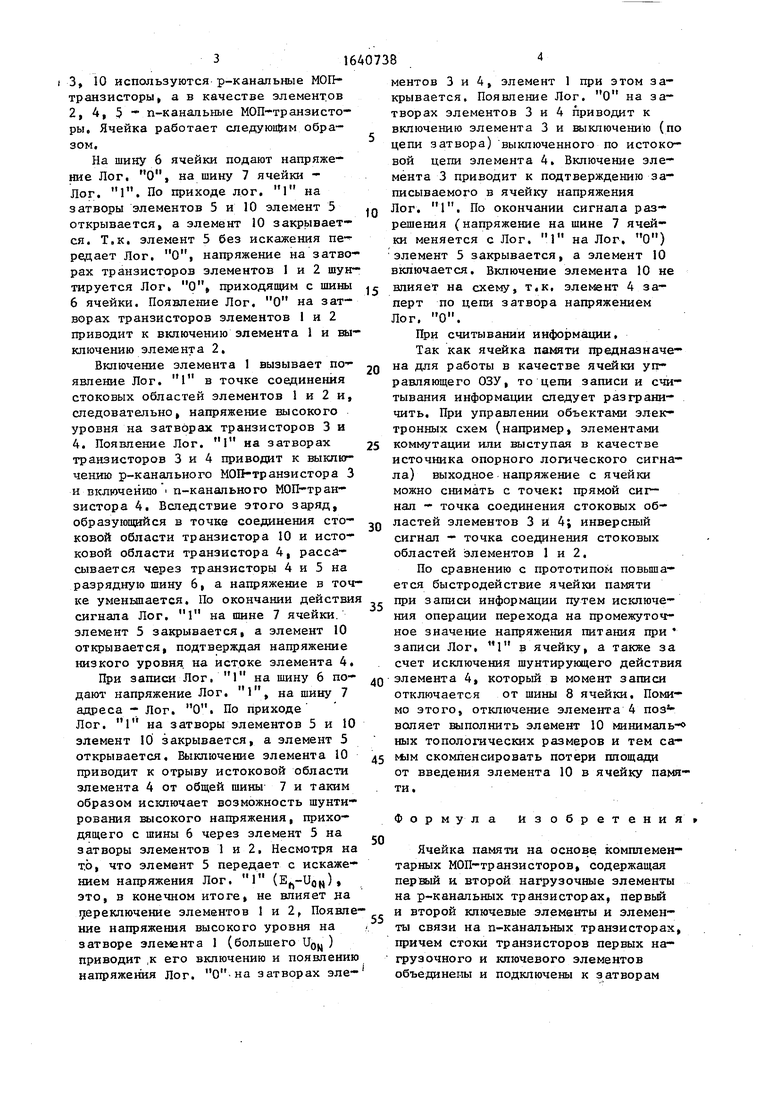

На чертеже приведена схема ячейки памяти.

Ячейка содержит вторые нагрузочный и ключевой элементы 1, 2, первые нагрузочный и ключевой элементы 3, 4, элемент 5 связи, разрядную и адресную шины 6, 7, шину 8 нулевого потенциала и шину 9 питания, третий ключевой элемент 10 ячейки. Ячейка памяти выполнена на основе комплементарных. транзисторов, В качестве элементов 1.

10

20

25

31640738

3, 10 используются р-канальные МОП- транзисторы, а в качестве элементов 2, 4, 5 ° n-канальные МОП-транзисторы. Ячейка работает следующим образом.

На шину 6 ячейки подают напряжение Лог, О, на шину 7 ячейки - Лог. 1. По приходе лог. 1 на затворы элементов 5 и 10 элемент 5 открывается, а элемент 10 закрывается. Т.к. элемент 5 без искажения передает Лог. О, напряжение на затворах транзисторов элементов 1 и 2 шунтируется Лог О, приходящим с шины с 6 ячейки. Появление Лог. О на затворах транзисторов элементов 1 и 2 приводит к включению элемента 1 и выключению элемента 2,

Включение элемента 1 вызывает появление Лог. 1 в точке соединения стоковых областей элементов 1 и 2 и, следовательно, напряжение высокого уровня на затворах транзисторов 3 и 4. Появление Лог. I на затворах транзисторов 3 и 4 приводит к выключению р-канального MOR-транзистора З и включению п-канапьного МОП-транзистора 4. Вследствие этого заряд, образующийся в точке соединения стоковой области транзистора 10 и исто- ковой области транзистора 4, рассасывается через транзисторы 4 и 5 на разрядную шину 6, а напряжение в точке уменьшается. По окончании действия сигнала Лог. I на шине 7 ячейки, элемент 5 закрывается, а элемент 10 открывается, подтверждая напряжение низкого уровня на истоке элемента 4. При записи Лог, 1 на шину 6 подают напряжение Лог. 1, на шину 7 адреса - Лог. О. По приходе Лог. 1 на затворы элементов 5 и 10 элемент 10 закрывается, а элемент 5 открывается. Выключение элемента 10 приводит к отрыву истоковой области элемента 4 от общей шины 7 и таким образом исключает возможность шунтирования высокого напряжения, приходящего с шины 6 через элемент 5 на затворы элементов 1 и 2, Несмотря на то, что элемент 5 передает с искажением напряжения Лог. 1 (Eh-UON),

30

35

40

45

т в

50

это, в конечном итоге, не влияет да

переключение элементов 1 и 2, Появле- и второй ключевые элементы и элеменние напряжения высокого уровня на затворе элемента 1 (большего UOH ) приводит ,к его включению и появлению напряжения Лог. затворах эле-1

ты связи на п-канальных транзисторах, причем стоки транзисторов первых нагрузочного и ключевого элементов объединены и подключены к затворам

0

0

5

с

30

35

40

45

ментов 3 и 4, элемент 1 при этом закрывается. Появление Лог. О на затворах элементов 3 и 4 приводит к включению элемента 3 и выключению (по цепи затвора) выключенного по истоко- вой цепи элемента 4. Включение элемента 3 приводит к подтверждению записываемого в ячейку напряжения Лог. 1. По окончании сигнала разрешения (напряжение на шине 7 ячейки меняется с Лог. 1 на Лог, О) элемент 5 закрывается, а элемент 10 включается. Включение элемента 10 не влияет на схему, т.к. элемент 4 заперт по цепи затвора напряжением Лог. О.

При считывании информации, Так как ячейка памяти предназначена для работы в качестве ячейки управляющего ОЗУ, то цепи записи и считывания информации следует разграничить. При управлении объектами электронных схем (например, элементами коммутации или выступая в качестве источника опорного логического сигнала) выходное напряжение с ячейки можно снимать с точек: прямой сигнал - точка соединения стоковых областей элементов 3 и 4; инверсный сигнал - точка соединения стоковых областей элементов 1 и 2,

По сравнению с прототипом повышается быстродействие ячейки памяти при записи информации путем исключения операции перехода на промежуточное значение напряжения питания при записи Лог, 1 в ячейку, а также за счет исключения шунтирующего действия элемента 4, который в момент записи отключается от шины 8 ячейки. Помимо этого, отключение элемента 4 поз воляет выполнить элемент 10 минималь-о ных топологических размеров и тем самым скомпенсировать потери площади от введения элемента 10 в ячейку памяти.

Формула изобретения

Ячейка памяти на основе комплементарных МОП-транзисторов, содержащая первый и, второй нагрузочные элементы на р-канальных транзисторах, первый

ты связи на п-канальных транзисторах, причем стоки транзисторов первых нагрузочного и ключевого элементов объединены и подключены к затворам

транзисторов вторых нагрузочного и ключевого элементов и стоку транзистора элемента связи, исток и затвор которого подключены соответственно к разрядной и адресной шинам ячейки, истоки транзисторов нагрузочных элементов подключены к шине питания ячейки, исток транзистора второго ключевого элемента подключен к шине нулевого потенциала ячейки, отличающая с я тем, что с целью повышения быстродействия, в нее введен третий ключевой элемент на р-канапь- ном транзисторе, затвор и исток которого подключены соответственно к разрядной шине и шине нулевого потенциала, а сток подключен к истоку транзис- тора первого ключевого элемента.

| Ячейка памяти | 1987 |

|

SU1444888A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Алексеенко А.Г | |||

| и Шагурин и,И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с | |||

| Синхронизирующее устройство для аппарата, служащего для передачи изображений на расстояние | 1920 |

|

SU225A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1991-04-07—Публикация

1989-03-30—Подача