Изобретение относится к вычислительной технике и может быть использовано при построении средств автоматики, функциональных узлов систем управления и др.

Известны мажоритарные модули (см., например, патент РФ 2700552, кл. H03K19/23, 2019 г.), которые содержат элементы 2И, элементы 2ИЛИ и реализуют мажоритарную функцию семи аргументов – входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных мажоритарных модулей, относятся большие аппаратурные затраты, обусловленные тем, что, в частности, упомянутый аналог содержит двенадцать элементов 2И и двенадцать элементов 2ИЛИ.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип мажоритарный модуль (патент РФ 2764709, кл. G06F7/57, 2022 г.), который содержит десять элементов 2И, десять элементов 2ИЛИ и реализует мажоритарную функцию семи аргументов – входных двоичных сигналов.

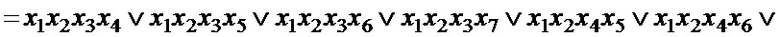

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится низкое быстродействие, обусловленное тем, что максимальное время задержки распространения сигнала в прототипе определяется выражением  , где

, где  есть длительность задержки, вносимой логическим элементом.

есть длительность задержки, вносимой логическим элементом.

Техническим результатом изобретения является повышение быстродействия при сохранении аппаратурного состава прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в мажоритарном модуле, содержащем десять элементов 2И и десять элементов 2ИЛИ, первый, второй входы k-го ( ), первый вход m-го (

), первый вход m-го ( ) и выход восьмого элементов 2ИЛИ соединены соответственно с первым, вторым входами k-го, первым входом m-го элементов 2И и выходом мажоритарного модуля, четвертый, пятый входы которого подключены соответственно к первому, второму входам второго элемента 2ИЛИ, особенность заключается в том, что вторые входы k-го, девятого элементов 2ИЛИ и первые входы десятых элементов 2И, 2ИЛИ соединены соответственно с вторыми входами k-го, девятого элементов 2И и выходами девятых элементов 2ИЛИ, 2И, вторые входы шестых элементов 2И, 2ИЛИ и первый, второй входы пятого элемента 2ИЛИ подключены соответственно к первым входам девятых элементов 2ИЛИ, 2И и выходам десятых элементов 2И, 2ИЛИ, первый вход шестого, выход второго элементов 2И и второй вход десятого элемента 2ИЛИ соединены соответственно с вторым входом девятого, первым входом четвертого и выходом третьего элементов 2И, первый, второй входы (

) и выход восьмого элементов 2ИЛИ соединены соответственно с первым, вторым входами k-го, первым входом m-го элементов 2И и выходом мажоритарного модуля, четвертый, пятый входы которого подключены соответственно к первому, второму входам второго элемента 2ИЛИ, особенность заключается в том, что вторые входы k-го, девятого элементов 2ИЛИ и первые входы десятых элементов 2И, 2ИЛИ соединены соответственно с вторыми входами k-го, девятого элементов 2И и выходами девятых элементов 2ИЛИ, 2И, вторые входы шестых элементов 2И, 2ИЛИ и первый, второй входы пятого элемента 2ИЛИ подключены соответственно к первым входам девятых элементов 2ИЛИ, 2И и выходам десятых элементов 2И, 2ИЛИ, первый вход шестого, выход второго элементов 2И и второй вход десятого элемента 2ИЛИ соединены соответственно с вторым входом девятого, первым входом четвертого и выходом третьего элементов 2И, первый, второй входы ( )-го и второй вход шестого элементов 2И подключены соответственно к выходам (

)-го и второй вход шестого элементов 2И подключены соответственно к выходам ( )-го, m-го и выходу первого элементов 2ИЛИ, первый, второй входы (

)-го, m-го и выходу первого элементов 2ИЛИ, первый, второй входы ( )-го и первый, второй входы шестого элементов 2ИЛИ соединены соответственно с выходами (

)-го и первый, второй входы шестого элементов 2ИЛИ соединены соответственно с выходами ( )-го, m-го и выходами шестого, первого элементов 2И, а вторые входы четвертого, десятого и первый вход шестого элементов 2И подключены соответственно к выходам третьего, второго элементов 2ИЛИ и первому входу мажоритарного модуля, второй, третий и шестой, седьмой входы которого соединены соответственно с первым, вторым входами первого и первым, вторым входами третьего элементов 2ИЛИ.

)-го, m-го и выходами шестого, первого элементов 2И, а вторые входы четвертого, десятого и первый вход шестого элементов 2И подключены соответственно к выходам третьего, второго элементов 2ИЛИ и первому входу мажоритарного модуля, второй, третий и шестой, седьмой входы которого соединены соответственно с первым, вторым входами первого и первым, вторым входами третьего элементов 2ИЛИ.

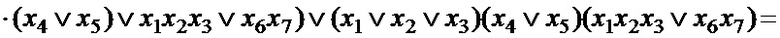

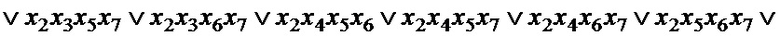

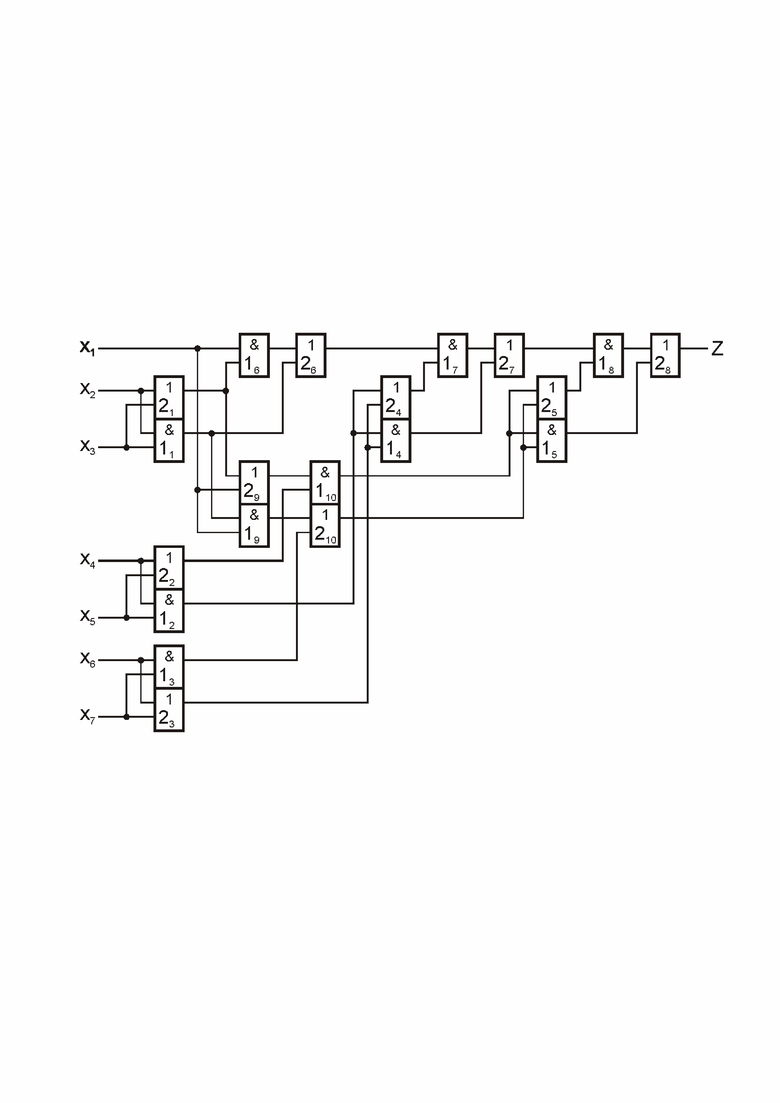

На чертеже представлена схема предлагаемого мажоритарного модуля.

Мажоритарный модуль содержит элементы 2И 11,…, 110 и элементы 2ИЛИ 21,…,210, причем первый, второй входы элемента 2i ( ), второй вход элемента 29 и первые входы элементов 110, 210 соединены соответственно с первым, вторым входами элемента 1i, вторым входом элемента 19 и выходами элементов 29, 19, вторые входы элементов 16, 26 и первый, второй входы элемента 25 подключены соответственно к первым входам элементов 29, 19 и выходам элементов 110, 210, первый вход элемента 16, выход элемента 12 и второй вход элемента 210 соединены соответственно с вторым входом элемента 19, первым входом элемента 14 и выходом элемента 13, первый, второй входы элемента 1j (

), второй вход элемента 29 и первые входы элементов 110, 210 соединены соответственно с первым, вторым входами элемента 1i, вторым входом элемента 19 и выходами элементов 29, 19, вторые входы элементов 16, 26 и первый, второй входы элемента 25 подключены соответственно к первым входам элементов 29, 19 и выходам элементов 110, 210, первый вход элемента 16, выход элемента 12 и второй вход элемента 210 соединены соответственно с вторым входом элемента 19, первым входом элемента 14 и выходом элемента 13, первый, второй входы элемента 1j ( ) и второй вход элемента 16 подключены соответственно к выходам элементов 2j–1, 2j–3 и выходу элемента 21, первый, второй входы элемента 2j и первый, второй входы элемента 26 соединены соответственно с выходами элементов 1j, 1j–3 и выходами элементов 16, 11, вторые входы элементов 14, 110, первый вход элемента 16 и выход элемента 28 подключены соответственно к выходам элементов 23, 22, первому входу и выходу мажоритарного модуля, (

) и второй вход элемента 16 подключены соответственно к выходам элементов 2j–1, 2j–3 и выходу элемента 21, первый, второй входы элемента 2j и первый, второй входы элемента 26 соединены соответственно с выходами элементов 1j, 1j–3 и выходами элементов 16, 11, вторые входы элементов 14, 110, первый вход элемента 16 и выход элемента 28 подключены соответственно к выходам элементов 23, 22, первому входу и выходу мажоритарного модуля, ( )-й (

)-й ( ), (

), ( )-й входы которого соединены соответственно с первым, вторым входами элемента 2k.

)-й входы которого соединены соответственно с первым, вторым входами элемента 2k.

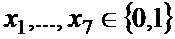

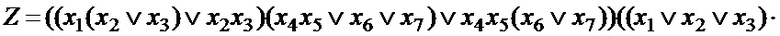

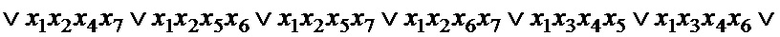

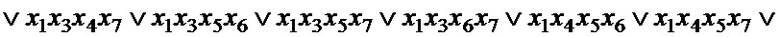

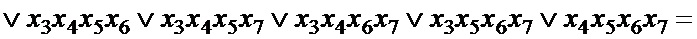

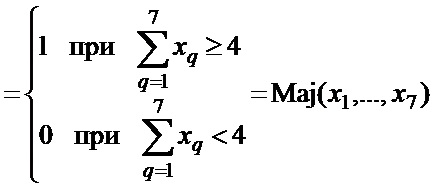

Работа предлагаемого мажоритарного модуля осуществляется следующим образом. На его первый, …, седьмой входы подаются соответственно двоичные сигналы  . На выходе предлагаемого модуля получим

. На выходе предлагаемого модуля получим

,

,

где ∙,  и

и  есть соответственно символы операций И, ИЛИ и мажоритарная функция семи аргументов

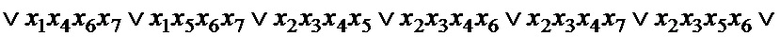

есть соответственно символы операций И, ИЛИ и мажоритарная функция семи аргументов  . При этом максимальное время задержки распространения сигнала в предлагаемом модуле определяется выражением

. При этом максимальное время задержки распространения сигнала в предлагаемом модуле определяется выражением  (

( – длительность задержки, вносимой логическим элементом).

– длительность задержки, вносимой логическим элементом).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый мажоритарный модуль реализует мажоритарную функцию семи аргументов – входных двоичных сигналов, имеет аппаратурный состав прототипа и обладает более высоким по сравнению с прототипом быстродействием.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2764709C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2700552C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2775589C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2776923C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2789750C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2762545C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2019 |

|

RU2710877C1 |

| МАЖОРИТАЛЬНЫЙ МОДУЛЬ | 2021 |

|

RU2778677C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2016 |

|

RU2629451C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2812683C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении средств автоматики, функциональных узлов систем управления. Техническим результатом изобретения является повышение быстродействия мажоритарного модуля. Технический результат заявленного решения достигается тем, что в нем предусмотрены десять элементов 2И и десять элементов 2ИЛИ, а также наличием определенных связей между указанными элементами. 1 ил.

Мажоритарный модуль, содержащий десять элементов 2И и десять элементов 2ИЛИ, причем первый, второй входы k-го ( ), первый вход m-го (

), первый вход m-го ( ) и выход восьмого элементов 2ИЛИ соединены соответственно с первым, вторым входами k-го, первым входом m-го элементов 2И и выходом мажоритарного модуля, четвертый, пятый входы которого подключены соответственно к первому, второму входам второго элемента 2ИЛИ, отличающийся тем, что вторые входы k-го, девятого элементов 2ИЛИ и первые входы десятых элементов 2И, 2ИЛИ соединены соответственно с вторыми входами k-го, девятого элементов 2И и выходами девятых элементов 2ИЛИ, 2И, вторые входы шестых элементов 2И, 2ИЛИ и первый, второй входы пятого элемента 2ИЛИ подключены соответственно к первым входам девятых элементов 2ИЛИ, 2И и выходам десятых элементов 2И, 2ИЛИ, первый вход шестого, выход второго элементов 2И и второй вход десятого элемента 2ИЛИ соединены соответственно с вторым входом девятого, первым входом четвертого и выходом третьего элементов 2И, первый, второй входы (

) и выход восьмого элементов 2ИЛИ соединены соответственно с первым, вторым входами k-го, первым входом m-го элементов 2И и выходом мажоритарного модуля, четвертый, пятый входы которого подключены соответственно к первому, второму входам второго элемента 2ИЛИ, отличающийся тем, что вторые входы k-го, девятого элементов 2ИЛИ и первые входы десятых элементов 2И, 2ИЛИ соединены соответственно с вторыми входами k-го, девятого элементов 2И и выходами девятых элементов 2ИЛИ, 2И, вторые входы шестых элементов 2И, 2ИЛИ и первый, второй входы пятого элемента 2ИЛИ подключены соответственно к первым входам девятых элементов 2ИЛИ, 2И и выходам десятых элементов 2И, 2ИЛИ, первый вход шестого, выход второго элементов 2И и второй вход десятого элемента 2ИЛИ соединены соответственно с вторым входом девятого, первым входом четвертого и выходом третьего элементов 2И, первый, второй входы ( )-го и второй вход шестого элементов 2И подключены соответственно к выходам (

)-го и второй вход шестого элементов 2И подключены соответственно к выходам ( )-го, m-го и выходу первого элементов 2ИЛИ, первый, второй входы (

)-го, m-го и выходу первого элементов 2ИЛИ, первый, второй входы ( )-го и первый, второй входы шестого элементов 2ИЛИ соединены соответственно с выходами (

)-го и первый, второй входы шестого элементов 2ИЛИ соединены соответственно с выходами ( )-го, m-го и выходами шестого, первого элементов 2И, а вторые входы четвертого, десятого и первый вход шестого элементов 2И подключены соответственно к выходам третьего, второго элементов 2ИЛИ и первому входу мажоритарного модуля, второй, третий и шестой, седьмой входы которого соединены соответственно с первым, вторым входами первого и первым, вторым входами третьего элементов 2ИЛИ.

)-го, m-го и выходами шестого, первого элементов 2И, а вторые входы четвертого, десятого и первый вход шестого элементов 2И подключены соответственно к выходам третьего, второго элементов 2ИЛИ и первому входу мажоритарного модуля, второй, третий и шестой, седьмой входы которого соединены соответственно с первым, вторым входами первого и первым, вторым входами третьего элементов 2ИЛИ.

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2758186C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2757817C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2018 |

|

RU2701464C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2762620C1 |

| US 6868536 B2, 15.03.2005. | |||

Авторы

Даты

2023-03-09—Публикация

2022-03-18—Подача