Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора или универсального логического модуля.

Известен восьмиканальный мультиплексор, содержащий три элемента НЕ, четыре элемента 2-2ИЛИ--4И-НЕ и элемент .

Недостатком мультиплексора являются ограниченные функциональные возможности.

Наиболее близким по функциональным возможностям и конструкции техническим решением к заявляемому является шестнадцатиканальный мультиплексор, содержащий четыре элемента НЕ, шестнадцать элементов И и элемент ИЛИ 2,

Недостатком известного мультиплексора является высокая конструктивная сложность.

Цель изобретения - упрощение конструкции мультиплексора.

Поставленная цель достигается тем, что в мультиплексор, содержащий четыре элемента НЕ, шестнадцать информационных шин и четыре адресные шины, i-я (,2,3,4) из которых соединена с входом 1-го элемента НЕ, введены элемент 4-4ИЛИ-4И-НЕ и восемь элементов 2-2И-ЗИЛИ-НЕ, j-й (,2) вход k-ro ,2,..,,8) из которых соединен с {2k+j-2)-й информационной шиной мультиплексора, а выход соединен с k-м входом элемента 4-4ИЛИ-4И-НЕ, выход которого соединен с выходной шиной мультиплексора, а девятый и десять / входы соединены соответственно с входами первого и второго элементов НЕ, одиннадцатый и двенадцатый входы соединены соответственно с входом первого элемента НЕ и выходом второго элемента НЕ, тринадцатый и четырнадцатый входы соединены соответственно с выходом первого элемента НЕ и входом второго элемента НЕ, пятнадцатый и шестнадцатый входы соединены соответственно с выходами первого и второго элементов НЕ, третий вход {2i-1)-ro элемента ,2-2И-ЗИЛИНЕ соеди-нен с входом третьего элемента НЕ, выход которого соединен с третьим входом 2i-ro элемента 2-2И-ЗИЛИ-НЕ, четвертый вход k-ro элемента 2-2И-ЗИЛИ-НЕ соединен с выходом четвертого элемента НЕ, вход которого соединен с пятым входом k-ro элемента 2-2И-ЗИЛИ-НЕ, причем элемент НЕ содержит два МОП-транзистора, затвор первого из которых соединен с входной шиной элемента, первая шина П1:тания которого соединена с истоком первого транзистора, сток которого соединен с выходной шиной элемента и истоком второго

транзистора, сток которого соединен с затвором и второй шиной питания, элемент 2-2И-ЗИЛИ-НЕ содержит шесть .МОП-транзисторов, затвор р-го (,2,3) из которых

соединен с р-й входной шиной элемента. 0+3)-я входная шина которого соединена с затвором (+3)-го транзистора, исток которого соединен с истоком третьего транзистора и первой шиной питания, сток соединен с

0 истоком j-ro транзистора, сток которого соединен с выходной шиной элемента, стоком третьего транзистора и истоком шестого транзистора, сток которого соединен с затвором и второй шиной питания, элемент

5 4-4ИЛИ-4И-НЕ содержит семнадцать МОПтранзисторов, затпор г-го(.216) из которых соединен с г-й входной ииной элемента, выходная шина которого соединена с истоком семнадцатого транзистора и

0 стоками j-ro и 0+8)-го транзисторов, истоки которых соединены со стоками (j+2)-ro и 0+iO)-fo транзисторов, истоки которых соединены со стоками ()-гo и Q+12)-ro транзисторов, истоки которых соединены со

5 стоками ()-го и 0+14)-го транзисторов, истоки которых соединены с первой шиной питания, вторая шина питания соединена с затвором и стоком семнадцатого транзистора.

0Мультиплексор с о д е р ж и т ч е т ы р е

элемента НЕ, элемент 4 - 4 И Л И - 4 И НЕ, восемь элементов 2 - 2 И - 3 И Л И НЕ. шестнадцать информационны х LU и н и ч е т ь р е а д р е с i ы е шины, i-я

5 (,2,3,4) из которых соединена с входом i-ro элемента НЕ. Причем, j-й, (.2} вхЬд k-ro (k-1,28) элемента 2-2И-ЗИЛИ-НЕ соединен с ()-й информационной 1ииной мультиплексора, а выход соединен с k-м входом элемента 4-4ИЛИ-4И-НЕ, выход которого соединен с выходной шиной мультиплексора. Девятый и десятый входы элемента 4-4ИЛИ-4И-НЕ соединены соответственно с входами первого и второго эле5 ментоп i-IE, а одиннадцатый и двенадцатый входы соединены соответственно с входом первого элемента НЕ и выходом второго элемента НЕ. Далее, тринадцатый и четырнадцатый входы элемента 4-4ИЛИ-4И-.НЕ

0 соединены соответственно с выходом первого элемента НЕ и входом второго элемента НЕ, а пятнадцатый и, шестнадцатый входы соединены соответственно с выходами первого и второго элементов НЕ. Третий

5 вход(21-1)-го элемента 2-2И-ЗИЛИ-НЕ соединен с входом третьего элемента НЕ, выход которого соединен с трегьим входом 2i-ro элемента 2-2И-ЗИЛИ-НЕ. Четвертый гвход k-ro .элемента 2-2И-ЗИЛИ-НЕ соединен с )ыходом четвертого элемента НЕ. вход

которого соединен с пятым входом k-ro элемента 2-2И-ЗИЛИ-НЕ.

Использование идентичных или сходных конструктивных признаков и связей между ними в источниках информации не обнаружено.

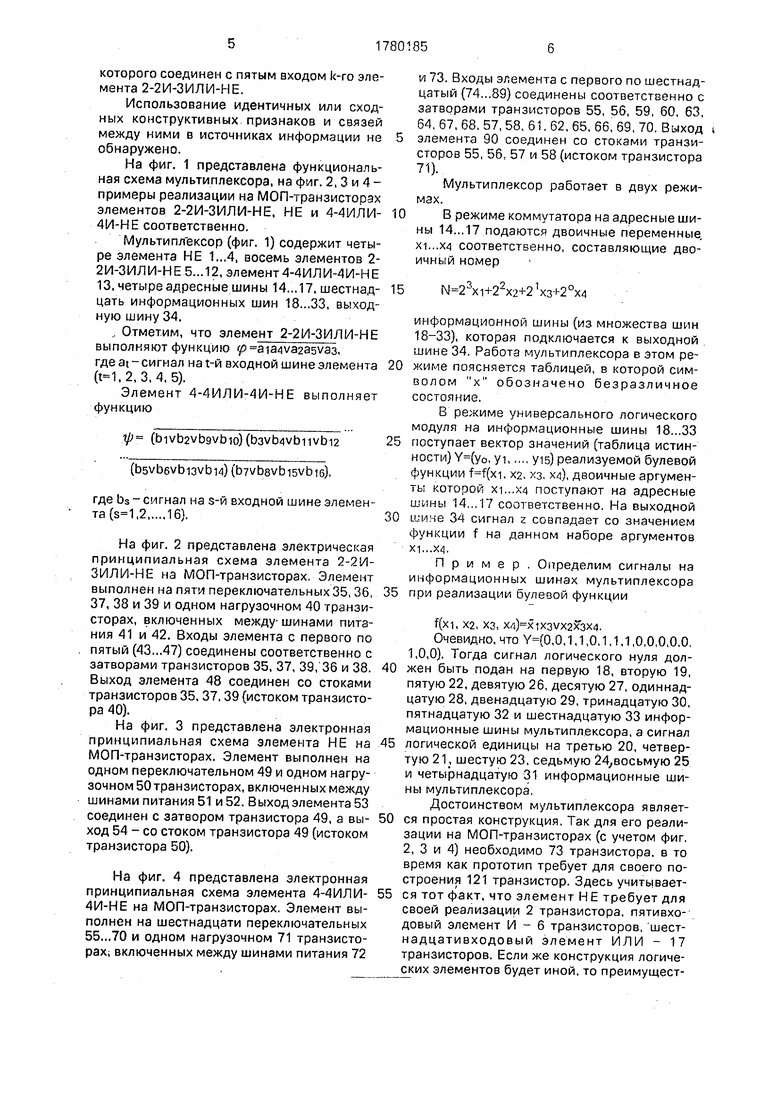

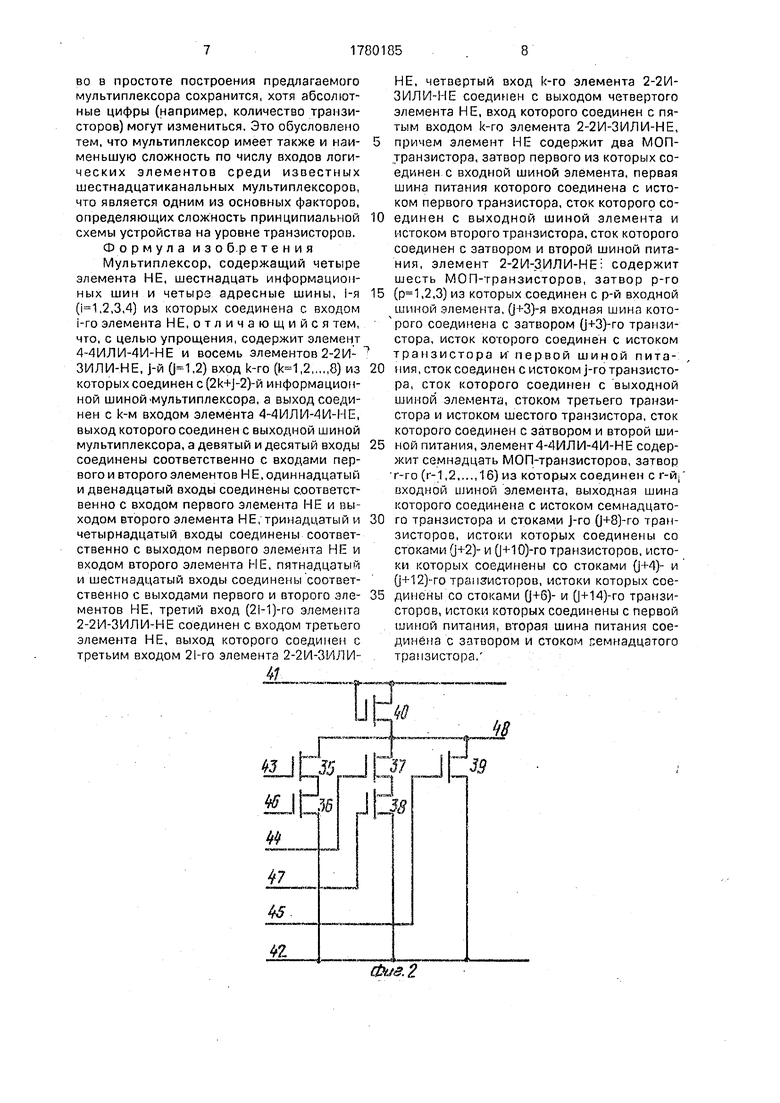

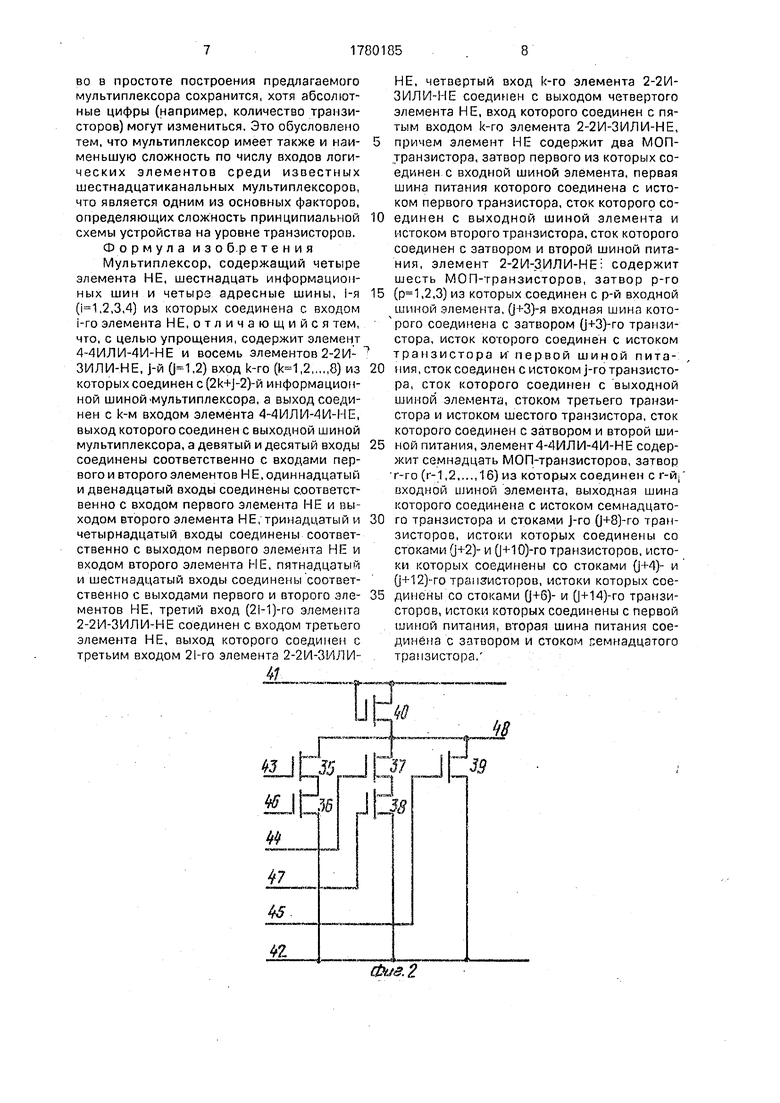

На фиг, 1 представлена функциональная схема мультиплексора, на фиг. 2,3 и 4 примеры реализации на МОП-транзисторэх элементов 2-21/1-ЗИЛИ-НЕ. НЕ и 4-4ИЛИ4И-НЕ соответственно.

Мультиплексор (фиг. 1) содержит четыре элемента НЕ 1,..4, восемь элементов 22И-ЗИЛИ-НЕ5...12, элемент4-4ИЛИ-4И-НЕ 13, четыре адресные шины 14.,.17, шестнадцать информационных шин 18..,33, выходную шину 34.

,. Отметим, что элемент 2-2И-ЗИЛИ-НЕ выполняют функцию 99 aia4va2a5va3, где at - сигнал на t-й входной шине элемента (,2,3,4,5).

Элемент 4-4ИЛИ-4И-НЕ выполняет функцию

(bivb2Vb9Vbio)(b3Vb4Vbiivbi2

(b5Vb6Vbl3Vbl4) (b7Vb8Vbt5Vbl5),

где bs-сигнал на s-й входной шине элемента (,216).

На фиг. 2 представлена электрическая принципиальная схема элемента 2-2ИЗИЛИ-НЕ на МОП-транзисторах, Элемент выполнен на пяти переключательных 35, 36, 37, 38 и 39 и одном нагрузочном 40 транзисторах, включенных между шинами питания 41 и 42. Входы элемента с первого по пятый (43...47) соединены соответственно с затворами транзисторов 35, 37, 39,36 и 38. Выход элемента 48 соединен со стоками транзисторов 35, 37, 39 (истоком транзистора 40).

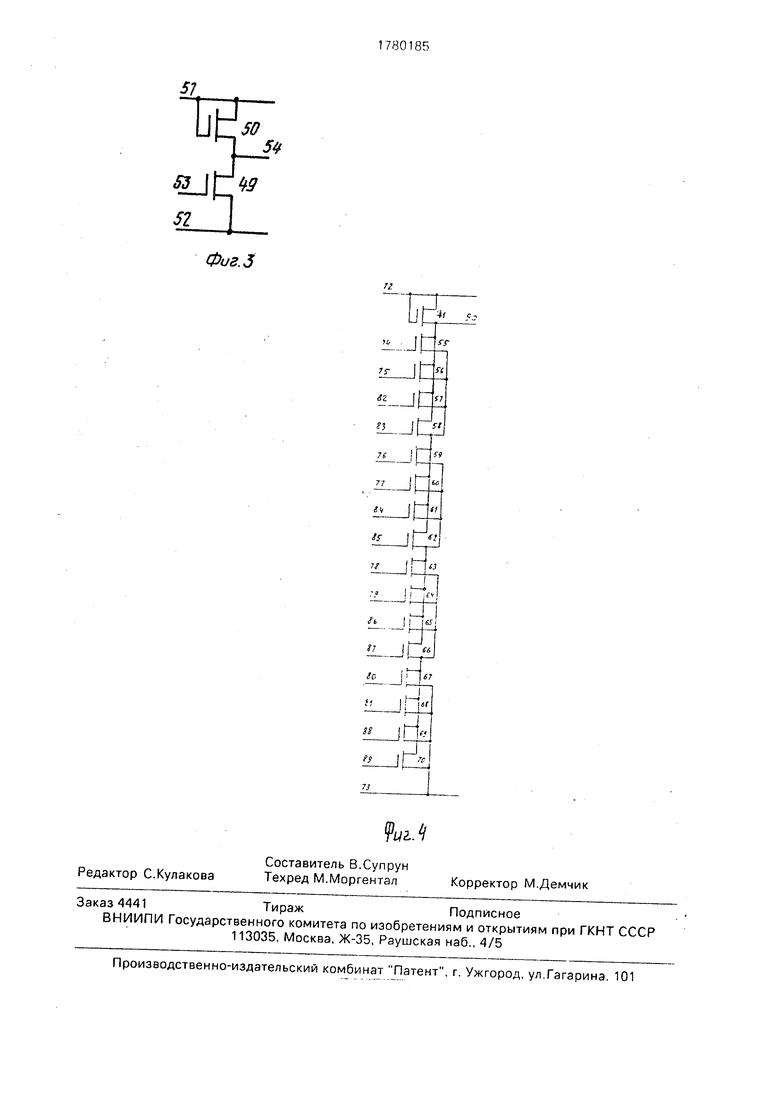

На фиг. 3 представлена электронная принципиальная схема элемента НЕ на МОП-транзисторах. Элемент выполнен на одном переключательном 49 и одном нагрузочном 50транзисторах, включенных между шинами питания 51 и 52. Выход элемента 53 соединен с затвором транзистора 49, а выход 54 - со стоком транзистора 49 (истоком транзистора 50).

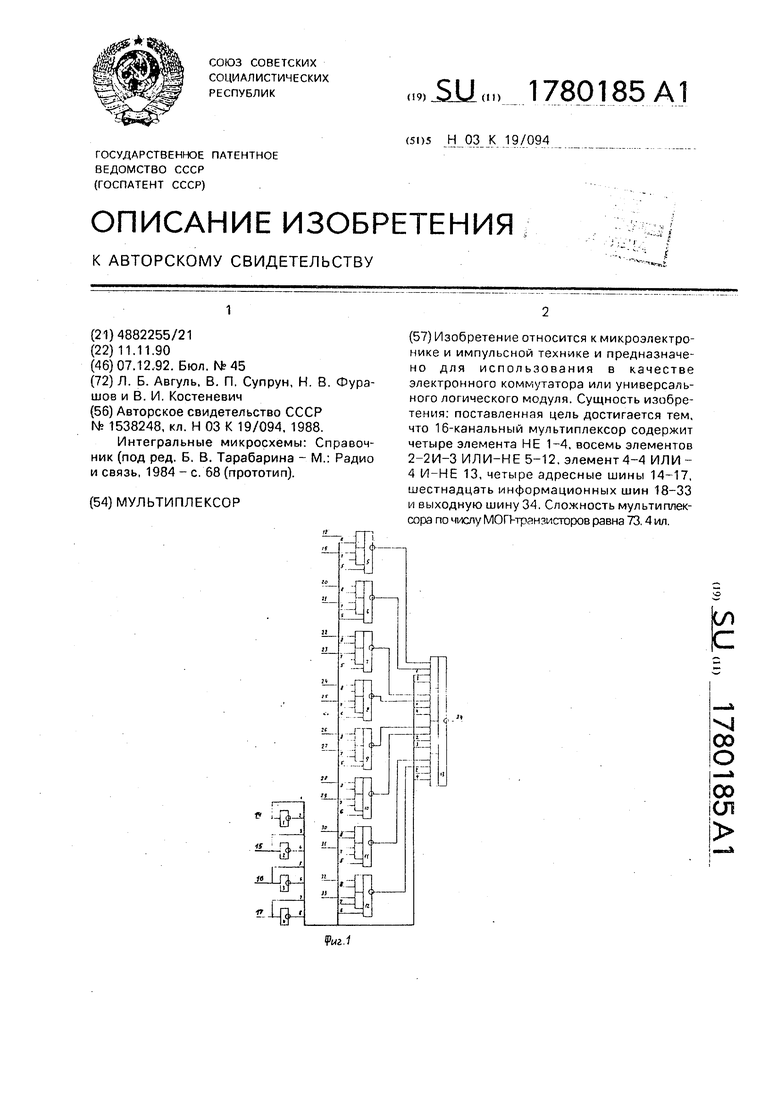

На фиг. 4 представлена электронная принципиальная схема элемента 4-4ИЛИ4И-НЕ на МОП-транзисторах, Элемент выполнен на шестнадцати переключательных 55...70 и одном нагрузочном 71 транзисторах; включенных между шинами питания 72

и 73. Входы элемента с первого по шестнадцатый (74,..89) соединены соответственно с затворами транзисторов 55, 56, 59, 60, 63, 64, 67, 68, 57, 58, 61, 62, 65, 66, 69, 70. Выход t

5 элемента 90 соединен со стоками транзисторов 55, 56. 57 и 58 (истоком транзистора 71).

Мультиплексор работает в двух режимах.

0В режиме коммутатора на адресные шины 14..,17 подаются двоичные переменные, Х1.,,Х4 соответственно, составляющие двоичный номер

хз+2°Х4

информационной шины (из множества шин 18-33), которая подключается к выходной шине 34, Работа мультиплексора в этом режиме поясняется таблицей, в которой символом х обозначено безразличное состояние.

В режиме универсального логического модуля на информационные шины 18,.,33

5 поступает вектор значений (таблица истинности) У(УО, У1yis) реализуемой булевой

функции (xi. Х2. хз, ), двоичные аргументы которой Х1,.,Х4 поступают на адресные шины 14,,,17 соотЕзетственно, На выходной

0 шине 34 сигнал г совпадает со значением функции f на данном наборе аргументов

Х1,,.Х4,

Пример, Определим сигналы на информационных шинах мультиплексора 5 при реализации булевой функции

f(xi, Х2, хз, X4)X1X3VX2X3X4,

Очевидно, что Y(0,0,1,1,0,1,1,1,0,0,0,0,0, 1,0,0). Тогда сигнал логического нуля должен быть подан на первую 18, вторую 19, пятую 22, девятую 26, десятую 27, одиннадцатую 28, двенадцатую 29, тринадцатую 30, пятнадцатую 32 и шестнадцатую 33 информационные шины мультиплексора, а сигнал

5 логической единицы на третью 20, четвертую 21, шестую 23, седьмую 24 восьмую 25 и четырнадцатую 31 информационные шины мультиплексора.

Достоинством мультиплексора является простая конструкция. Так для его реализации на МОП-транзисторах (с учетом фиг, 2, 3 и 4) необходимо 73 транзистора, в то время как прототип требует для своего построения 121 транзистор. Здесь учитывается тот факт, что элемент НЕ требует для своей реализации 2 транзистора, пятивходовый элемент И - 6 транзисторов, шестнадцативходовый элемент ИЛИ - 17 транзисторов. Если же конструкция логических элементов будет иной, то преимущество в простоте построения предлагаемого мультиплексора сохранится, хотя абсолютные цифры (например, количество транзисторов) могут измениться. Это обусловлено тем. что мультиплексор имеет также и наименьшую сложность по числу входов логических элементов среди известных шестнадцатиканальных мультиплексоров, что является одним из основных факторов, определяющих сложность принципиальной схемы устройства на уровне транзисторов. Формула и 3 о б.р е т е н и я Мультиплексор, содержащий четыре элемента НЕ. шестнадцать информационных шин и четыре адресные шины. 1-я (,2.3.4) из которых соединена с входом 1-го элемента НЕ. отличающийся тем, что. с целью упрощения, содержит элемент 4-4ИЛИ-4И-НЕ и восемь элементов 2-2ИЗИЛИ-НЕ. Н ,2) вход k-ro (,28) из

которых соединен с (2k+J-2)-й информационной шинойМультиплексора, а выход соединен с k-M входом элемента 4-4ИЛИ-4И-НЕ. выход которого соединен с выходной шиной мультиплексора, а девятый и десятый входы соединены соответственно с входами первого и второго элементов НЕ. одиннадцатый и двенадцатый входы соединены соответственно с входом первого элемента НЕ и выходом второго элемента НЕ, тринадцатый и четырнадцатый входы соединены соответственно с выходом первого элемента НЕ и входом второго элемента НЕ. пятнадцатый и шестнадцатый входы соединены соответственно с выходами первого и второго элементов НЕ, третий вход (21-1)-го элемента 2-2И-ЗИЛИ-НЕ соединен с входом третьего элемента НЕ. выход которого соединен с третьим входом 21-го элемента 2-2И-ЗИЛИMJ& itPrJ&

НЕ. четвертый вход k-ro элемента 2-2ИЗИЛИ-НЕ соединен с выходом четвертого элемента НЕ, вход которого соединен с пятым входом k-ro элемента 2-2И-ЗИЛИ-НЕ.

причем элемент НЕ содержит два МОПтранзистора, затвор первого из которых соединен с входной шиной элемента, первая шина питания которого соединена с истоком первого транзистора, сток которого соединен с выходной шиной элемента и истоком второго транзистора, сток которого соединен с затвором и второй шиной питания, элемент 2-2И-ЗИЛИ-НЕ: содержит шесть МОП-транзисторов, затвор р-го

(.2.3) иэ которых соединен с р-й входной шиной элемента. )-я входная шина котоpoio соединена с затвором 0+3)-го транзистора, исток которого соединен с истоком транзистора и первой шиной питаПИЯ, сток соединен с истоком j-ro транзистора, сток которого соединен с выходной шиной элемента, стоком третьего транзистора и истоком шестого транзистора, сток которого соединен с затвором и второй шиной питания. элемент4-4ИЛИ-4И-НЕ содержит семнадцать МОП-транзисторов, затвор т-го (г-1,2.....16) из которых соединен с г-й| входной шиной элемента, выходная шина которого соединена с истоком семнадцатого транзистора и стоками j-ro 0+8)-го транзисторов, истоки которых соединены со стоками 0+2)- и 0+10)-го транзисторов, истоки которых соединены со стоками (j+4)- и fj+12)-To транзисторов, истоки которых соединены со стоками О+б)- и (|+14)-го транзисторов, истоки которых соединены с первой шиной питания, вторая шина питания соединбна с затвором и стоком семнадцатого транзистора/

±

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ | 1991 |

|

SU1811002A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Многовходовый логический модуль | 1990 |

|

SU1793547A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Устройство для сравнения двух @ -разрядных двоичных чисел | 1989 |

|

SU1640684A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора или универсального логического модуля. Сущность изобретения: поставленная цель достигается тем, что 16-канальный мультиплексор содержит четыре элемента НЕ 1-4, восемь элементов 2-2И-3 ИЛИ-НЕ 5-12. элемент4-4 ИЛИ- 4 И-НЕ 13, четыре адресные шины 14-17, шестнадцать информационных шин 18-33 и выходную шину 34. Сложность мультиплексора по числу МОП-транзистаров равна 73.4 ил.слс^00оCDjcjn>&

Фи8.2

Ii -:Jtic

SI

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Б | |||

| В | |||

| Тарабарина - М.: Радио и связь, 1984 - с | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

Авторы

Даты

1992-12-07—Публикация

1990-11-11—Подача