Изобретение относится к области радиоэлектроники и может быть использовано в качестве входного каскада быстродействующих арсенид-галлиевых операционных усилителей.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) с входным дифференциальным каскадом на полевых и биполярных транзисторах, выполненные на основе архитектуры так называемого «перегнутого каскода» [1-45]. Их основные достоинства - расширенный частотный диапазон, а также эффективное использование напряжения питания.

В настоящее время в российской и зарубежной микроэлектронике уделяется повышенное внимание арсенид-галлиевым микросхемам [46]. Данное направление создания электронной компонентной базы относится к числу наиболее перспективных в задачах космического приборостроения. Однако, особенности арсенид-галлиевых технологических процессов накладывают существенные ограничения на типы реализуемых транзисторов и их характеристики [47,48]. Так, например, арсенид-галлиевый технологический процесс, освоенный Минским научно-исследовательским институтом радиоматериалов (https://mniirm.by/), ориентирован на изготовление аналоговых схем, содержащих только полевые GaAs транзисторы с управляющим p-n переходом (n-канал) и биполярные GaAs p-n-p транзисторы. Применение других полупроводниковых приборов не допускается. Это накладывает существенные ограничения на схемотехнику аналоговых устройств, ориентированных на данный технологический процесс.

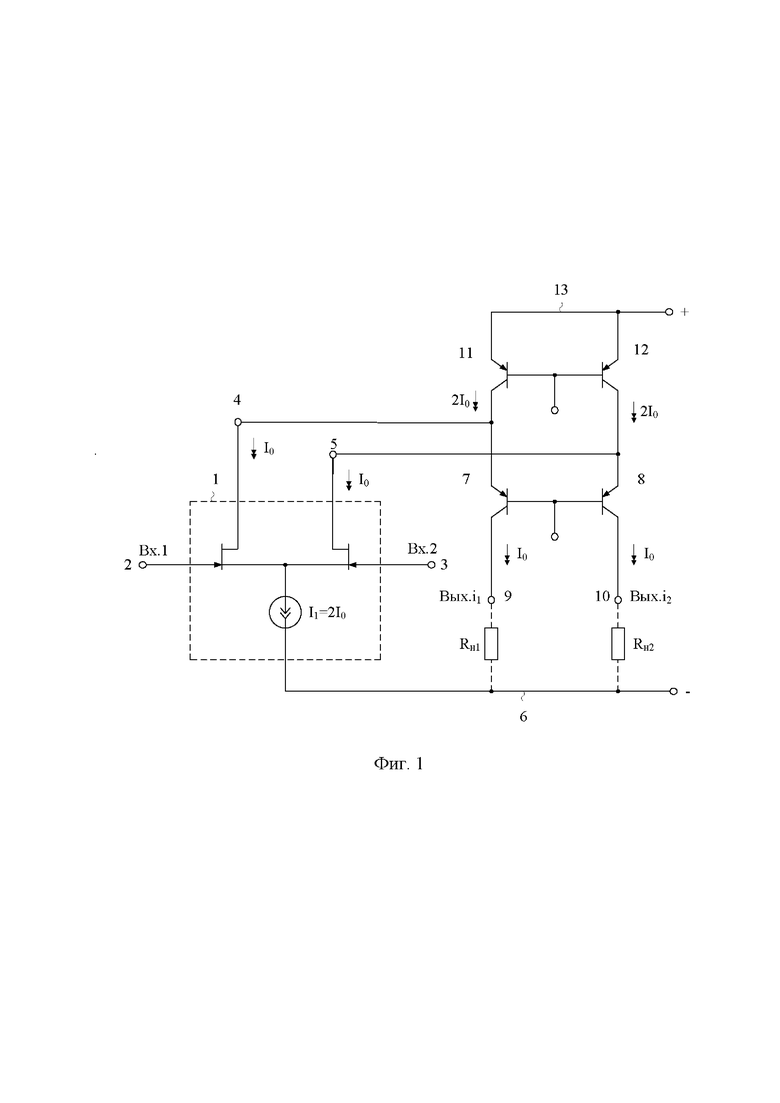

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад по патенту US 6.529.076, 2003 г. Он содержит (фиг. 1) входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также с первым 4 и вторым 5 токовыми выходами, первую 6 шину источника питания, первый 7 и второй 8 выходные биполярные p-n-p транзисторы, коллекторы которых связаны с соответствующими первым 9 и вторым 10 токовыми выходами устройства, согласованными с первой 6 шиной источника питания, первый 11 и второй 12 токостабилизирующие биполярные p-n-p транзисторы с объединенными базами, эмиттеры которых соединены со второй 13 шиной источника питания, коллектор первого 11 токостабилизирующего биполярного p-n-p транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1, коллектор второго 12 токостабилизирующего биполярного p-n-p транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1.

Существенный недостаток дифференциального каскада - прототипа (фиг. 1) состоит в том, что при его реализации на JFET GaAs полевых транзисторах с n-каналом и p-n-p GaAs биполярных транзисторах, он не работает в режиме класса АВ. Это не позволяет выполнять на его основе схемы быстродействующих операционных усилителей, в которых эффект повышения SR достигается за счет применения ДК класса АВ.

Основная задача предполагаемого изобретения состоит в создании входного дифференциального каскада ОУ, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим p-n переходом и биполярных GaAs p-n-p транзисторах, который обеспечивает по токовым выходам режим класса АВ, когда максимальные выходные токи ДК Iвых.max существенно превышают их статические значения Iвых.0. Это ускоряет процесс перезарядки емкости корректирующего конденсатора ОУ и повышает быстродействие ОУ в режиме большого сигнала.

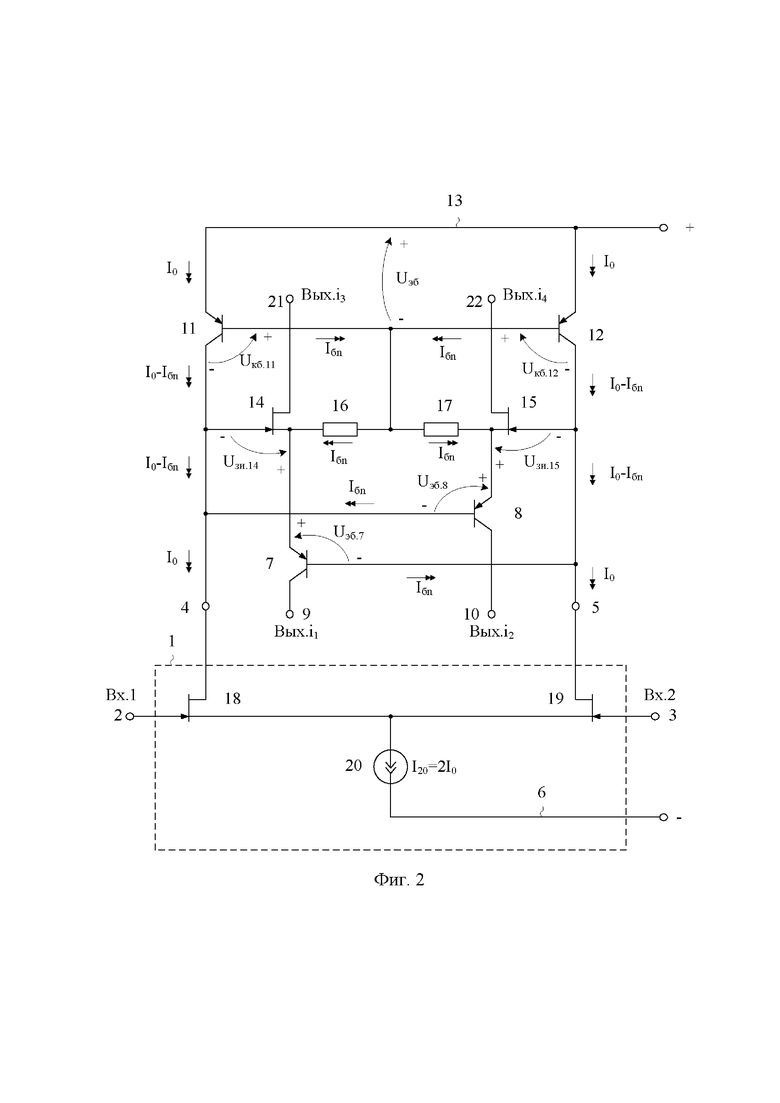

Поставленная задача достигается тем, что в дифференциальном каскаде фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также с первым 4 и вторым 5 токовыми выходами, первую 6 шину источника питания, первый 7 и второй 8 выходные биполярные p-n-p транзисторы, коллекторы которых связаны с соответствующими первым 9 и вторым 10 токовыми выходами устройства, согласованными с первой 6 шиной источника питания, первый 11 и второй 12 токостабилизирующие биполярные p-n-p транзисторы с объединенными базами, эмиттеры которых соединены со второй 13 шиной источника питания, коллектор первого 11 токостабилизирующего биполярного p-n-p транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1, коллектор второго 12 токостабилизирующего биполярного p-n-p транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1, предусмотрены новые элементы и связи - в схему введены первый 14 и второй 15 дополнительные полевые транзисторы с управляющим p-n переходом и n-каналом, стоки которых согласованы со второй 13 шиной источника питания, между их истоками включены два последовательно соединенных дополнительных резистора 16 и 17, общий узел которых подключен к объединенным базам первого 11 и второго 12 токостабилизирующих биполярных p-n-p транзисторов, затвор первого 14 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом соединен с коллектором первого 11 токостабилизирующего биполярного p-n-p транзистора и базой второго 8 выходного биполярного p-n-p транзистора, затвор второго 15 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом соединен с коллектором второго 12 токостабилизирующего биполярного p-n-p транзистора и базой первого 7 выходного биполярного p-n-p транзистора, эмиттер первого 7 выходного биполярного p-n-p транзистора соединен с истоком первого 14 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом, а эмиттер второго 8 выходного биполярного p-n-p транзистора соединен с истоком второго 15 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом.

На чертеже фиг. 1 приведена схема входного дифференциального каскада - прототипа по патенту US 6.529.076, 2003 г.

На чертеже фиг. 2 показана схема заявляемого дифференциального каскада класса АВ в соответствии с п. 1, п. 2 и п. 3 формулы изобретения.

На чертеже фиг. 3 приведен пример включения заявляемого ДК в структуре быстродействующего ОУ.

На чертеже фиг. 4 представлен статический режим ДК фиг. 2 на GaAs JFET и BJT транзисторах Минского НИИ радиоматериалов в среде LTSpice при 27°С, источнике опорного тока I1=200мкА, резисторах R1=R2=20кОм, Rn1=Rn2=1Ом, напряжениях питания V1=V2=±5В.

На чертеже фиг. 5 показана зависимость выходных токов ДК фиг. 4 от входного дифференциального напряжения в диапазоне от -600мВ до 600мВ.

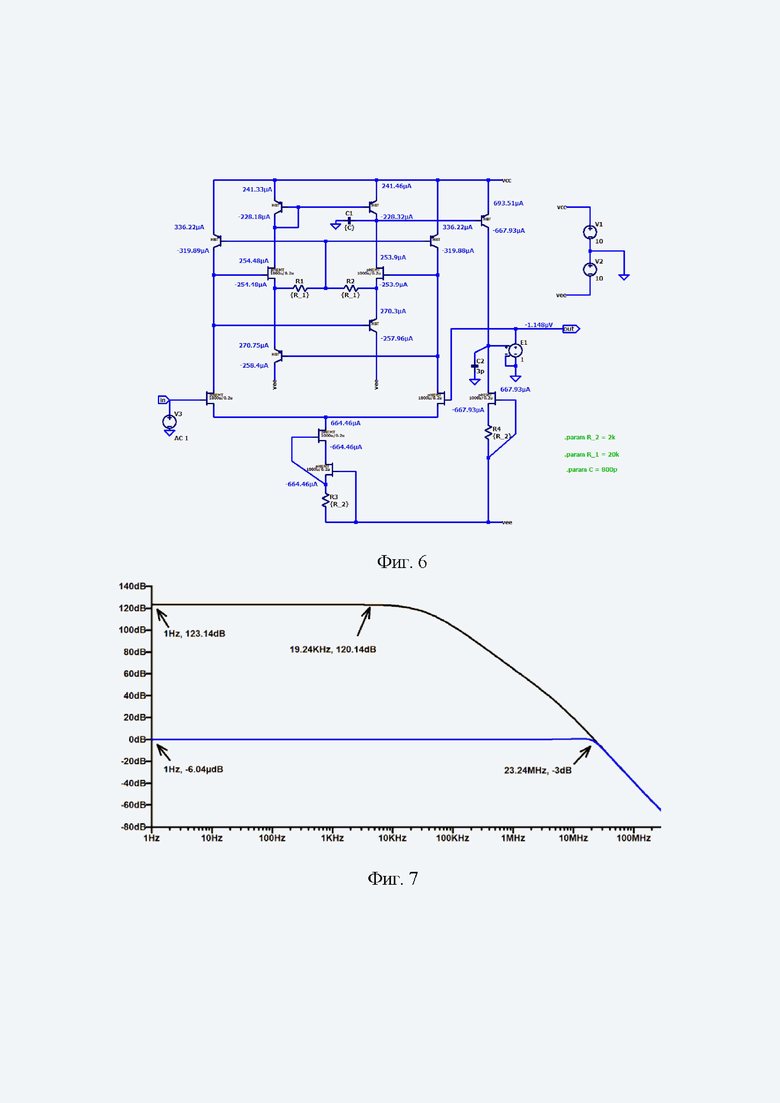

На чертеже фиг. 6 приведен статический режим предлагаемого входного дифференциального каскада класса АВ в структуре бвыстродействующего операционного усилителя на GaAs транзисторах при R1÷R2 = 20 кОм, R3÷R4 = 2 кОм, C1=5 нФ, C2 = 8 пФ, vcc= +10 В, vee = -10 В.

На чертеже фиг. 7 представлены результаты моделирования амплитудно-частотной характеристики коэффициента усиления ОУ фиг. 6 в среде LTspice на моделях GaAs транзисторов Минского НИИ радиоматериалов.

Арсенид-галлиевый входной дифференциальный каскад класса АВ быстродействующего операционного усилителя фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также с первым 4 и вторым 5 токовыми выходами, первую 6 шину источника питания, первый 7 и второй 8 выходные биполярные p-n-p транзисторы, коллекторы которых связаны с соответствующими первым 9 и вторым 10 токовыми выходами устройства, согласованными с первой 6 шиной источника питания, первый 11 и второй 12 токостабилизирующие биполярные p-n-p транзисторы с объединенными базами, эмиттеры которых соединены со второй 13 шиной источника питания, коллектор первого 11 токостабилизирующего биполярного p-n-p транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1, коллектор второго 12 токостабилизирующего биполярного p-n-p транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1. В схему введены первый 14 и второй 15 дополнительные полевые транзисторы с управляющим p-n переходом и n-каналом, стоки которых согласованы со второй 13 шиной источника питания, между их истоками включены два последовательно соединенных дополнительных резистора 16 и 17, общий узел которых подключен к объединенным базам первого 11 и второго 12 токостабилизирующих биполярных p-n-p транзисторов, затвор первого 14 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом соединен с коллектором первого 11 токостабилизирующего биполярного p-n-p транзистора и базой второго 8 выходного биполярного p-n-p транзистора, затвор второго 15 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом соединен с коллектором второго 12 токостабилизирующего биполярного p-n-p транзистора и базой первого 7 выходного биполярного p-n-p транзистора, эмиттер первого 7 выходного биполярного p-n-p транзистора соединен с истоком первого 14 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом, а эмиттер второго 8 выходного биполярного p-n-p транзистора соединен с истоком второго 15 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, входной дифференциальный каскад 1 выполнен на основе первого 18 и второго 19 входных полевых транзисторах с управляющим p-n переходом и n-каналом, объединенные истоки которых связаны с первой 6 шиной источника питания через источник опорного тока 20.

Кроме этого, на чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, сток первого 14 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом соединен с первым 21 дополнительным токовым выходом устройства, а сток второго 15 дополнительного полевого транзистора с управляющим p-n переходом и n-каналом соединен со вторым 22 дополнительным токовым выходом устройства.

Проходная характеристика предлагаемого ДК фиг. 4, представленная на графиках фиг. 5, показывает, что рассматриваемая схема работает в режиме класса АВ - ее максимальным выходной ток Iвых.max значительно превышает статические выходные токи Iвых.0, причем отношение

где Iвых.max = 2,8 мА, Iвых.0 = 30 мкА.

Таким образом, предлагаемый входной GaAs ДК, схемотехника которого адаптирована на применение в широком диапазоне температур и воздействия проникающей радиации [46], имеет существенные достоинства в сравнении с известным вариантом построения ДК фиг. 1 при его реализации в рамках рассматриваемого арсенид-галлиевого технологического процесса, обеспечивающего создание только полевых транзисторов с управляющим p-n переходом и биполярных p-n-p транзисторов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2321159, 2008 г., fig. 3, fig. 5

2. Патент US 5.153.529, 1992 г., fig. 1

3. Патент US 5.327.100, 1994 г., fig. 1

4. Патент US 6.529.076, 2003 г., fig. 1

5. Патент US 5.805.021, 1998 г., fig. 1

6. Патент US 5.140.280, 1992 г., fig. 1

7. Патент US 3.644.838, 1972 г.

8. Патент US 6.018.268, 2000 г., fig. 1

9. Патент US 7.714.656, 2010 г., fig. 3

10. Патент US 6.717.474, 2004 г.

11. Патент США № 5.422.600, фиг. 2

12. Патент США № 4.406.990, фиг. 4

13. Патент США № 5.952.882, 1999 г.

14. Патент США № 4.723.111, 1988 г.

15. Патент США № 4.293.824, 1981 г.

16. Патент США № 5.323.121, 1994 г.

17. Патент США № 5.420.540, fig. 1, 1995 г.

18. Патент RU № 2354041 C1, 2009 г.

19. Патентная заявка США № 2003/0201828, fig. 1, fig. 2, 2003 г.

20. Патент США № 6.825.721, fig. 1, fig. 2, 2004 г.

21. Патент США № 6.542.030, fig. 1, 2003 г.

22. Патент US 6.456.162, fig. 2, 2002 г.

23. Патент US 6.501.333, 2002 г.

24. Патент US 6.717.466, 2004 г.

25. Патентная заявка US № 2002/0196079, fig. 1, 2002 г.

26. Патент US № 4.600.893, fig. 7, 1986 г.

27. Патент US № 4.004.245, 1977 г.

28. Патент US № 7.411.451, fig. 5, 2008 г.

29. Патент US № 6.788.143, 2004 г.

30. Патент US 4.387.309, 1983 г.

31. Патент US 4.390.850, 1983 г.

32. Патент US 5.963.085, 1999 г.

33. Патент US 4.783.637, 1988 г.

34. Патент GB 2.035.003, fig. 2, 1980 г.

35. Патент US 7.215.200, fig. 6, 2007 г.

36. Патент US 6.393.495, 2002 г.

37. Патент US 6.628.168, fig. 2, 2003 г. (в ОУ)

38. Патент US 8.604.878, fig. 2, 2013 г. (в ОУ)

39. Патент US 7.453.319, fig. 1, 2008 г.

40. Патент EP 0632581, fig. 1, fig. 3, 1995 г.

41. Заявка на патент US 2009/0079503, fig. 1а, 2009 г.

42. Патент US 5.376.899, fig. 1, 1994 г.

43. Заявка на патент US 2008/0129383, fig. 1, 2008 г.

44. Патент US 5.424.681, fig. 1, 1995 г.

45. Патент US 5.475.339, 1995 г.

46. Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. Арсенид-галлиевый аналоговый базовый кристалл // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2021. Выпуск 2. С. 47-54. doi:10.31114/2078-7707-2021-2-47-54

47. W. Liu, D. Hill, D. Costa and J. S. Harris, "High-performance microwave AlGaAs-InGaAs Pnp HBT with high-DC current gain," in IEEE Microwave and Guided Wave Letters, vol. 2, no. 8, pp. 331-333, Aug. 1992, doi: 10.1109/75.153604.

48. K. W. Kobayashi, D. K. Umemoto, J. R. Velebir, D. C. Streit and A. K. Oki, "Integrated complementary HBT microwave push-pull and Darlington amplifiers with PNP active loads," GaAs IC Symposium Technical Digest 1992, 1992, pp. 313-316, doi: 10.1109/GAAS.1992.247281.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

Изобретение относится к области радиоэлектроники и может быть использовано в качестве входного каскада быстродействующих арсенид-галлиевых операционных усилителей. Технический результат: создание входного дифференциального каскада ОУ, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим p-n-переходом и биполярных GaAs p-n-p-транзисторах, который обеспечивает по токовым выходам режим класса АВ, когда максимальные выходные токи ДК Iвых.max существенно превышают их статические значения Iвых.0. Это ускоряет процесс перезарядки емкости корректирующего конденсатора ОУ и повышает быстродействие ОУ в режиме большого сигнала. Арсенид-галлиевый входной дифференциальный каскад класса АВ быстродействующего операционного усилителя содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) входами, а также с первым (4) и вторым (5) токовыми выходами, первую (6) шину источника питания, первый (7) и второй (8) выходные биполярные p-n-p-транзисторы, коллекторы которых связаны с соответствующими первым (9) и вторым (10) токовыми выходами устройства, согласованными с первой (6) шиной источника питания, первый (11) и второй (12) токостабилизирующие биполярные p-n-p-транзисторы с объединенными базами, эмиттеры которых соединены со второй (13) шиной источника питания, коллектор первого (11) токостабилизирующего биполярного p-n-p-транзистора соединен с первым (4) токовым выходом входного дифференциального каскада (1), коллектор второго (12) токостабилизирующего биполярного p-n-p-транзистора связан со вторым (5) токовым выходом входного дифференциального каскада (1). В схему введены первый (14) и второй (15) дополнительные полевые транзисторы с управляющим p-n-переходом и n-каналом, стоки которых согласованы со второй (13) шиной источника питания, между их истоками включены два последовательно соединенных дополнительных резистора (16) и (17), общий узел которых подключен к объединенным базам первого (11) и второго (12) токостабилизирующих биполярных p-n-p-транзисторов, затвор первого (14) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом соединен с коллектором первого (11) токостабилизирующего биполярного p-n-p-транзистора и базой второго (8) выходного биполярного p-n-p-транзистора, затвор второго (15) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом соединен с коллектором второго (12) токостабилизирующего биполярного p-n-p-транзистора и базой первого (7) выходного биполярного p-n-p-транзистора, эмиттер первого (7) выходного биполярного p-n-p-транзистора соединен с истоком первого (14) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом, а эмиттер второго (8) выходного биполярного p-n-p-транзистора соединен с истоком второго (15) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом. 2 з.п. ф-лы, 7 ил.

1. Арсенид-галлиевый входной дифференциальный каскад класса АВ быстродействующего операционного усилителя, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) входами, а также с первым (4) и вторым (5) токовыми выходами, первую (6) шину источника питания, первый (7) и второй (8) выходные биполярные p-n-p-транзисторы, коллекторы которых связаны с соответствующими первым (9) и вторым (10) токовыми выходами устройства, согласованными с первой (6) шиной источника питания, первый (11) и второй (12) токостабилизирующие биполярные p-n-p-транзисторы с объединенными базами, эмиттеры которых соединены со второй (13) шиной источника питания, коллектор первого (11) токостабилизирующего биполярного p-n-p-транзистора соединен с первым (4) токовым выходом входного дифференциального каскада (1), коллектор второго (12) токостабилизирующего биполярного p-n-p-транзистора связан со вторым (5) токовым выходом входного дифференциального каскада (1), отличающийся тем, что в схему введены первый (14) и второй (15) дополнительные полевые транзисторы с управляющим p-n-переходом и n-каналом, стоки которых согласованы со второй (13) шиной источника питания, между их истоками включены два последовательно соединенных дополнительных резистора (16) и (17), общий узел которых подключен к объединенным базам первого (11) и второго (12) токостабилизирующих биполярных p-n-p-транзисторов, затвор первого (14) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом соединен с коллектором первого (11) токостабилизирующего биполярного p-n-p-транзистора и базой второго (8) выходного биполярного p-n-p-транзистора, затвор второго (15) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом соединен с коллектором второго (12) токостабилизирующего биполярного p-n-p-транзистора и базой первого (7) выходного биполярного p-n-p-транзистора, эмиттер первого (7) выходного биполярного p-n-p-транзистора соединен с истоком первого (14) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом, а эмиттер второго (8) выходного биполярного p-n-p-транзистора соединен с истоком второго (15) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом.

2. Арсенид-галлиевый входной дифференциальный каскад класса АВ быстродействующего операционного усилителя по п.1, отличающийся тем, что входной дифференциальный каскад (1) выполнен на основе первого (18) и второго (19) входных полевых транзисторах с управляющим p-n-переходом и n-каналом, объединенные истоки которых связаны с первой (6) шиной источника питания через источник опорного тока (20).

3. Арсенид-галлиевый входной дифференциальный каскад класса АВ быстродействующего операционного усилителя по п.1, отличающийся тем, что сток первого (14) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом соединен с первым (21) дополнительным токовым выходом, а сток второго (15) дополнительного полевого транзистора с управляющим p-n-переходом и n-каналом соединен со вторым (22) дополнительным токовым выходом.

| US 5153529 A1, 06.10.1992 | |||

| US 6529076 B2, 04.03.2003 | |||

| US 5327100 A1, 05.07.1994 | |||

| US 5805021 A1, 08.09.1998 | |||

| Дифференциальный усилитель | 1983 |

|

SU1166271A1 |

Авторы

Даты

2022-12-26—Публикация

2022-04-05—Подача