Изобретение относится к автоматике и вычислительной техники и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности.

Известен способ мажоритирования в вычислительной системе [1]. Согласно известному способу мажоритирования в вычислительной системе формируют отказоустойчивую вычислительную систему, содержащую группу центральных процессоров, выходная информация с выходов которых мажоритируется одним из способов: 2 из 3, 3 и более из 5, 4 и более из 7 или 5 и более из 9 и т.д. Выбор варианта мажоритирования и переход с одного варианта в системе осуществляется программно.

Недостатком данного способа является необходимость во временной избыточности на анализ и поиск неисправного канала, а также на программный переход на нижний вариант мажоритирования.

Наиболее близким к предложенному решению является способ мажоритирования в вычислительной системе [1], в соответствии с которым в вычислительной системе формируют отказоустойчивую вычислительную систему, содержащую группу центральных процессоров, выходная информация с выходов которых мажоритируется одним из способов: 2 из 3, 3 и более из 5, 4 и более из 7 или 5 и более из 9 и т.д.

Известным способом мажоритирования в вычислительной системе формируют отказоустойчивую вычислительную систему, содержащую группу центральных процессоров, выходная информация с выходов которых мажоритируется одним из способов: 2 из 3, 3 и более из 5, 4 и более из 7 или 5 и более из 9 и т.д.

Технический результат предлагаемого изобретения - способ адаптивного мажоритирования элементов «п и более из (2n-1)», где n=1,2, 3 и т.д.

Технический результат достигается тем, что в способе при котором адаптивное мажоритирование в системе выполняют путем суммирования всех (2n-1) мажоритируемых двоичных сигналов. Результат суммирования всех (2n-1) мажоритируемых двоичных сигналов сравнивается со значением п, после чего за значение результата мажоритирования принимается результат сравнения выхода сумматора со значением п.

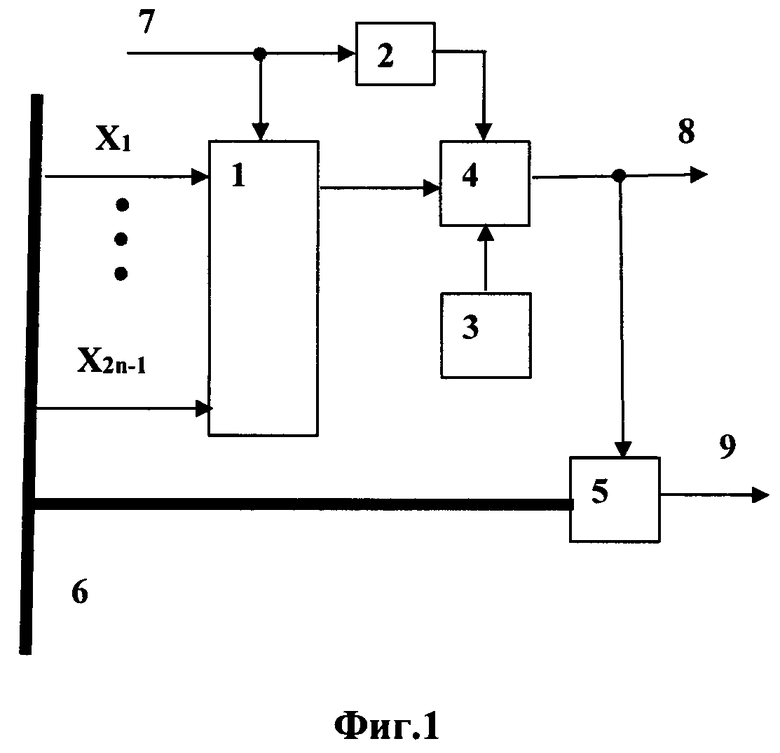

На чертеже представлена блок-схема (см. Фиг. 1) мажоритируемых (2n-1) двоичных сигналов. На чертеже представлены:

1) сумматор комбинационного типа (1);

2) элемент задержки (2);

3) регистр для хранения числа n (3);

4) схема сравнения (4);

5) блок анализа неисправных каналов (5);

6) входы мажоритируемых (2n-1) двоичных сигналов (6);

7) вход тактирующего сигнала (7);

8) выходной мажоритируемый двоичный сигнал (8);

9) номера неисправных каналов (9).

Мажоритируемые сигналы Xi (i=1,2,…(2n-1)) поступают на входы сумматора 1, где по тактирующему сигналу с входа 7 происходит их сложение. Результат с выхода сумматора 1 поступает на первый вход схемы сравнения 4, на второй вход которой поступает код числа п с выхода регистра 3. Элемент 2 задерживает тактирующий сигнал на время надежного срабатывания сумматора 1. Результат мажоритирования будет равен 1, если значение кода на выходе сумматора будет больше или равно числа n, и 0 - в противном случае. Кроме того, сигнал с выхода схемы сравнения 4 поступает на блок 5 анализа неисправных каналов.

Способ включает следующие операции:

1. Адаптивное мажоритирование в системе выполняют путем суммирования всех (2n-1) мажоритируемых двоичных сигналов.

2. Результат суммирования всех (2n-1) мажоритируемых двоичных сигналов сравнивается со значением n.

3. За значение результата мажоритирования принимается результат сравнения выхода сумматора со значением п.

Способ адаптивного мажоритирования в системе позволяет осуществить непрерывный контроль работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности.

Таким образом данный способ адаптивного мажоритирования в системе выполняют путем суммирования любых всех (2n-1) мажоритируемых двоичных сигналов, при этом за значение результата мажоритирования принимают результат сравнения выхода сумматора со значением числа п.

1. RU №2716061, кл. G06F 7/57, H03K 19/23, 2019.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов | 2024 |

|

RU2835006C1 |

| Способ мажоритирования сигналов "2 из 3" | 2022 |

|

RU2789213C1 |

| Адаптивный мажоритарный блок элементов "n и более из (2n-1)" | 2023 |

|

RU2818031C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| СПОСОБ ОБЕСПЕЧЕНИЯ СБОЕ- И ОТКАЗОУСТОЙЧИВОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, ОСНОВАННЫЙ НА РЕПЛИКАЦИИ ЗАДАЧ, ВОЗМОЖНОСТИ САМОРЕКОНФИГУРАЦИИ И САМОУПРАВЛЕНИИ ДЕГРАДАЦИЕЙ | 2013 |

|

RU2559767C2 |

| Устройство мажоритирования с заменой | 2020 |

|

RU2726646C1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для коррекции изображений объектов | 1989 |

|

SU1755305A2 |

| Система надежного облачного хранения с регулируемой избыточностью данных | 2021 |

|

RU2782681C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

Настоящее техническое решение относится к области вычислительной техники. Технический результат заключается в устранении временной избыточности на анализ и поиск неисправного канала, а также на программный переход на нижний вариант мажоритирования за счёт адаптивного мажоритирования элементов «n и более из (2n-1)». Технический результат достигается за счёт способа адаптивного мажоритирования элементов, заключающегося в том, что в системе формируют отказоустойчивую вычислительную систему, содержащую группу центральных процессоров, выходная информация с выходов которых мажоритируется одним из способов: 2 из 3, 3 и более из 5, 4 и более из 7 или 5 и более из 9 и т.д., а адаптивное мажоритирование в системе выполняют путем суммирования всех (2n-1) мажоритируемых двоичных сигналов; результат суммирования всех (2n-1) мажоритируемых двоичных сигналов сравнивается со значением n; после чего за значение результата мажоритирования принимается результат сравнения выхода сумматора со значением n. 1 ил.

Способ адаптивного мажоритирования элементов, заключающийся в том, что в системе формируют отказоустойчивую вычислительную систему, содержащую группу центральных процессоров, выходная информация с выходов которых мажоритируется одним из способов: 2 из 3, 3 и более из 5, 4 и более из 7 или 5 и более из 9 и т.д., отличающийся тем, что адаптивное мажоритирование в системе выполняют путем суммирования всех (2n-1) мажоритируемых двоичных сигналов; результат суммирования всех (2n-1) мажоритируемых двоичных сигналов сравнивается со значением n; после чего за значение результата мажоритирования принимается результат сравнения выхода сумматора со значением n.

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "5 И БОЛЕЕ ИЗ 9" | 2016 |

|

RU2665226C2 |

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "7 И БОЛЕЕ ИЗ 13" | 2016 |

|

RU2628222C2 |

| Устройство мажоритирования с заменой | 2020 |

|

RU2726646C1 |

| Мажоритарный блок элементов "два из трех" | 2019 |

|

RU2711726C1 |

| US 10229016 B2, 12.03.2019. | |||

Авторы

Даты

2022-12-05—Публикация

2022-01-17—Подача