Изобретение относится к области радиотехники и связи и может быть использовано в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компенсационных стабилизаторах напряжения, компараторах и т.п.

Известны схемы относительно нового подкласса дифференциальных каскадов (ДК) класса АВ с резистивной отрицательной обратной связью по синфазному сигналу [1-18], в т.ч. на биполярных и CMOS полевых транзисторах, которые стали основой многих серийных аналоговых микросхем с повышенной максимальной скоростью нарастания выходного напряжения.

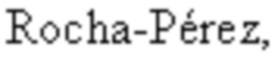

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад по патенту US 5.376.897, fig. 3, 1994 г. Он содержит входной параллельно-балансный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первую 6 шину источника питания, первый 7 и второй 8 вспомогательные транзисторы с объединенными базами, эмиттеры которых связаны со второй 9 шиной источника питания, первый 10 и второй 11 выходные транзисторы, причем коллектор первого 10 выходного транзистора связан с первым 12 токовым выходом устройства, а коллектор второго 11 выходного транзистора соединен со вторым 13 токовым выходом устройства, эмиттеры первого 10 и второго 11 выходных транзисторов связаны со второй 9 шиной источника питания, база первого 10 выходного транзистора соединена с коллектором первого 7 вспомогательного транзистора, база второго 11 выходного транзистора соединена с коллектором второго 8 вспомогательного транзистора, между базами первого 10 и второго 11 выходных транзисторов включены последовательно соединенные первый 14 и второй 15 вспомогательные резисторы, общий узел которых связан с объединенными базами первого 7 и второго 8 вспомогательных транзисторов, причем первая (6) шина источника питания связана с общей эмиттерной цепью входного параллельно-балансного каскада (1).

Существенный недостаток известного ДК (фиг.1) состоит в том, что при микроамперных статических токах коллектора входных транзисторов 16 и 17 его выходные статические токи по первому 12 и второму 13 токовым выходам (Iвых.1, Iвых.2) всегда имеют относительно большие значения, что оказывает отрицательное влияние на общее токопотребление устройства. Этот неустранимый в данном классе ДК эффект связан с особенностями цепей установления статического режима ДК фиг. 1 и обусловлен существенным влиянием на работу схемы коэффициента усиления по току базы (β) применяемых первого 7 и второго 8 вспомогательных транзисторов.

Основная задача предлагаемого изобретения состоит в обеспечении работы ДК в режиме класса АВ при повышенных отношениях его максимальных выходных токов Iвых.max на первом 12 и втором 13 токовых выходах к статическим значениям его выходных токов Iвых.0, которые определяются при нулевом входном напряжении ДК.

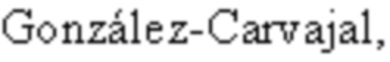

Решение поставленной задачи достигается тем, что в дифференциальном каскаде фиг. 1, содержащем входной параллельно-балансный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первую 6 шину источника питания, первый 7 и второй 8 вспомогательные транзисторы с объединенными базами, эмиттеры которых связаны со второй 9 шиной источника питания, первый 10 и второй 11 выходные транзисторы, причем коллектор первого 10 выходного транзистора связан с первым 12 токовым выходом устройства, а коллектор второго 11 выходного транзистора соединен со вторым 13 токовым выходом устройства, эмиттеры первого 10 и второго 11 выходных транзисторов связаны со второй 9 шиной источника питания, база первого 10 выходного транзистора соединена с коллектором первого 7 вспомогательного транзистора, база второго 11 выходного транзистора соединена с коллектором второго 8 вспомогательного транзистора, между базами первого 10 и второго 11 выходных транзисторов включены последовательно соединенные первый 14 и второй 15 вспомогательные резисторы, общий узел которых связан с объединенными базами первого 7 и второго 8 вспомогательных транзисторов, причем первая (6) шина источника питания связана с общей эмиттерной цепью входного параллельно-балансного каскада (1), предусмотрены новые элементы и связи - в схему введены первый 19 и второй 20 дополнительные транзисторы, базы которых объединены и подключены к объединенным базам первого 7 и второго 8 вспомогательных транзисторов, коллектор первого 19 дополнительного транзистора соединен с базой первого 10 выходного транзистора, коллектор второго 20 дополнительного транзистора соединен с базой второго 11 выходного транзистора, эмиттер первого 19 дополнительного транзистора соединен с первым 4 токовым выходом входного параллельно-балансного каскада 1, а эмиттер второго 20 дополнительного транзистора соединен со вторым 5 токовым выходом входного параллельно-балансного каскада 1.

На чертеже фиг. 1 представлена схема ДК-прототипа по патенту US 5.376.897, fig. 3, 1994 г.

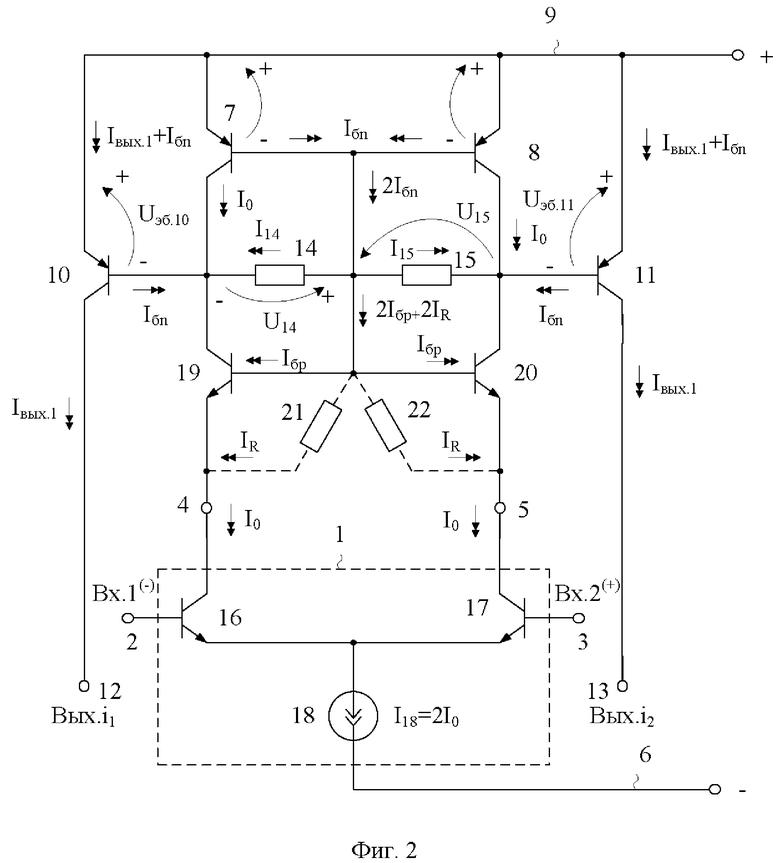

На чертеже фиг. 2 приведена схема заявляемого входного дифференциального каскада класса АВ в соответствии с п. 1 и п. 2 формулы изобретения.

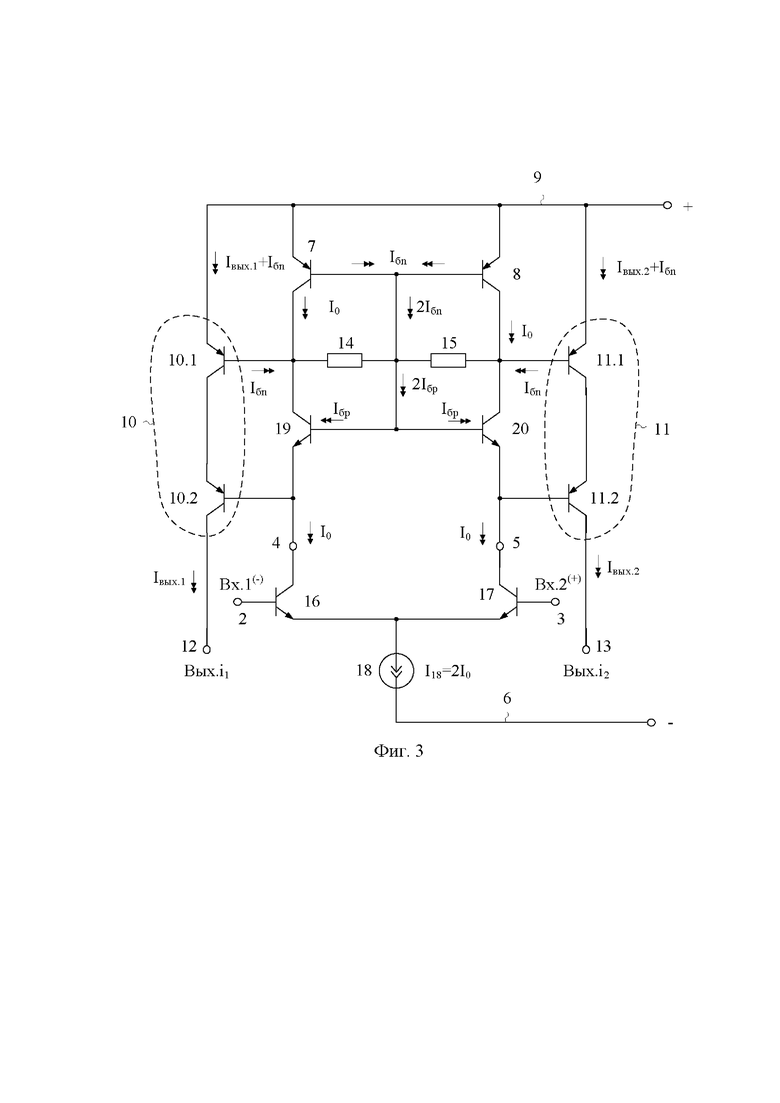

На чертеже фиг. 3 показана схема заявляемого входного дифференциального каскада класса АВ в соответствии с п. 3 формулы изобретения.

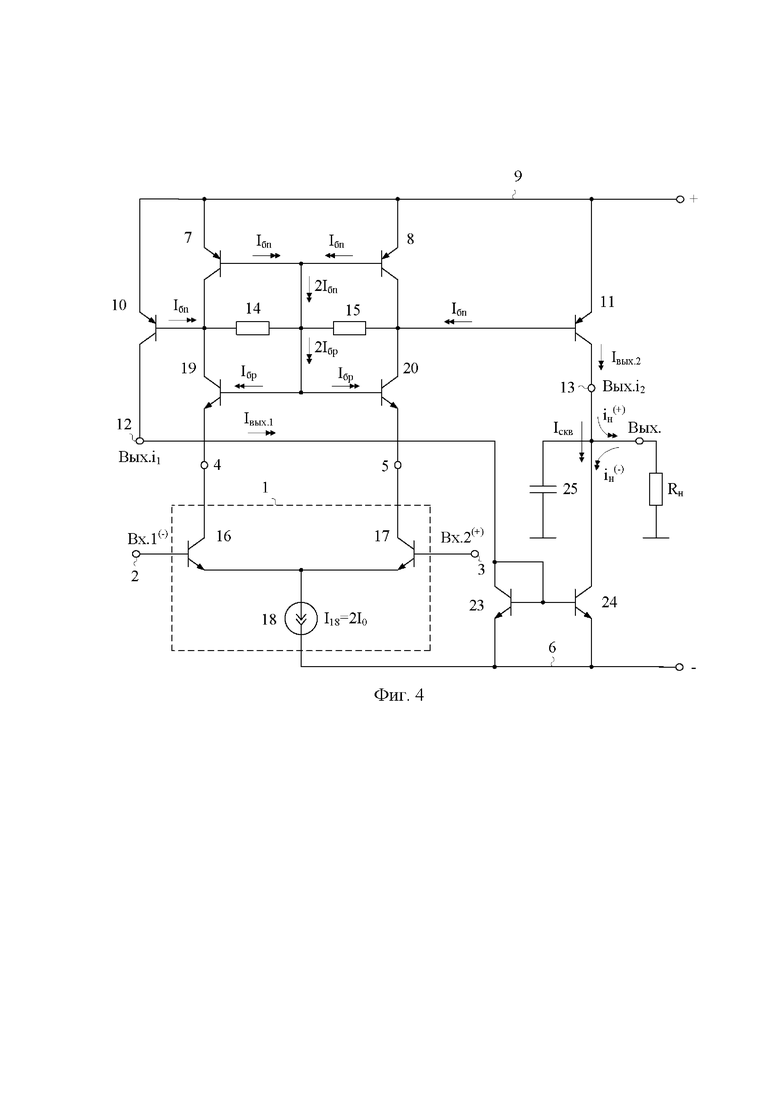

На чертеже фиг. 4 представлен пример включения заявляемого входного ДК фиг. 2 в схеме ОУ с малым токопотреблением в статическом режиме.

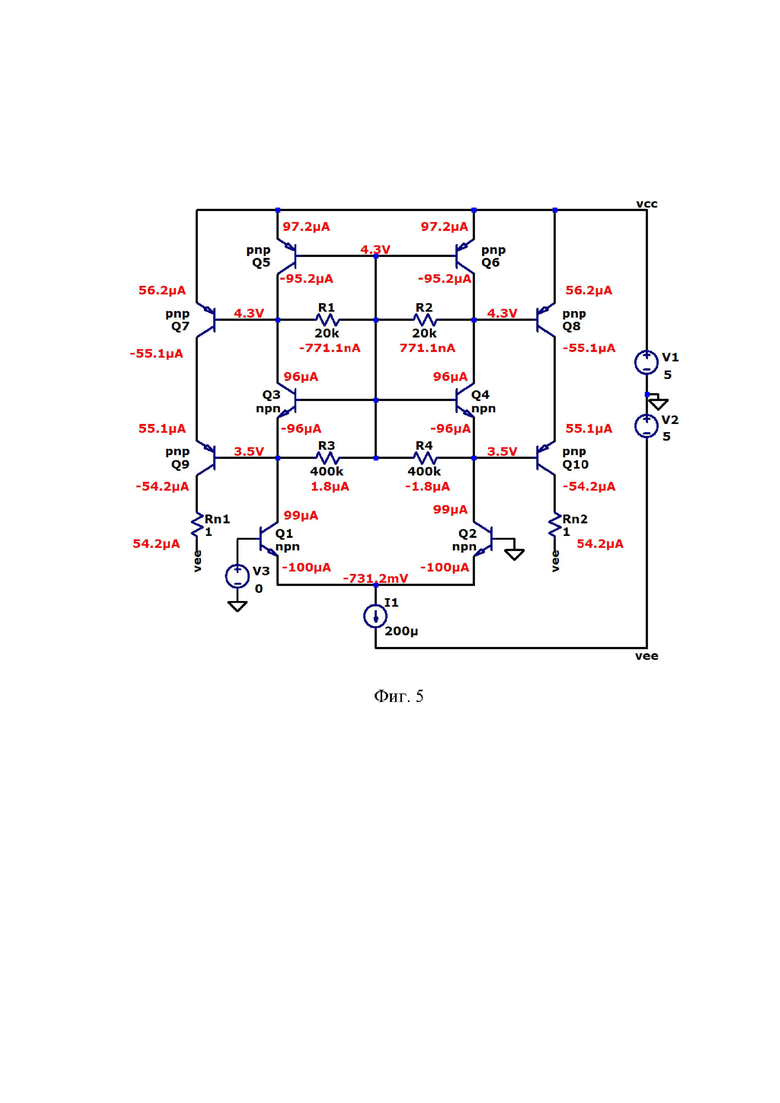

На чертеже фиг. 5 показан статический режим схемы ДК фиг. 2 в среде LTSpice на BiJT транзисторах АО «Интеграл» (г. Минск) при 27°С, источнике опорного тока I1=200мкА, резисторах R1=R2=20кОм, R3=R4=400кОм, напряжениях питания V1=V2=±5В.

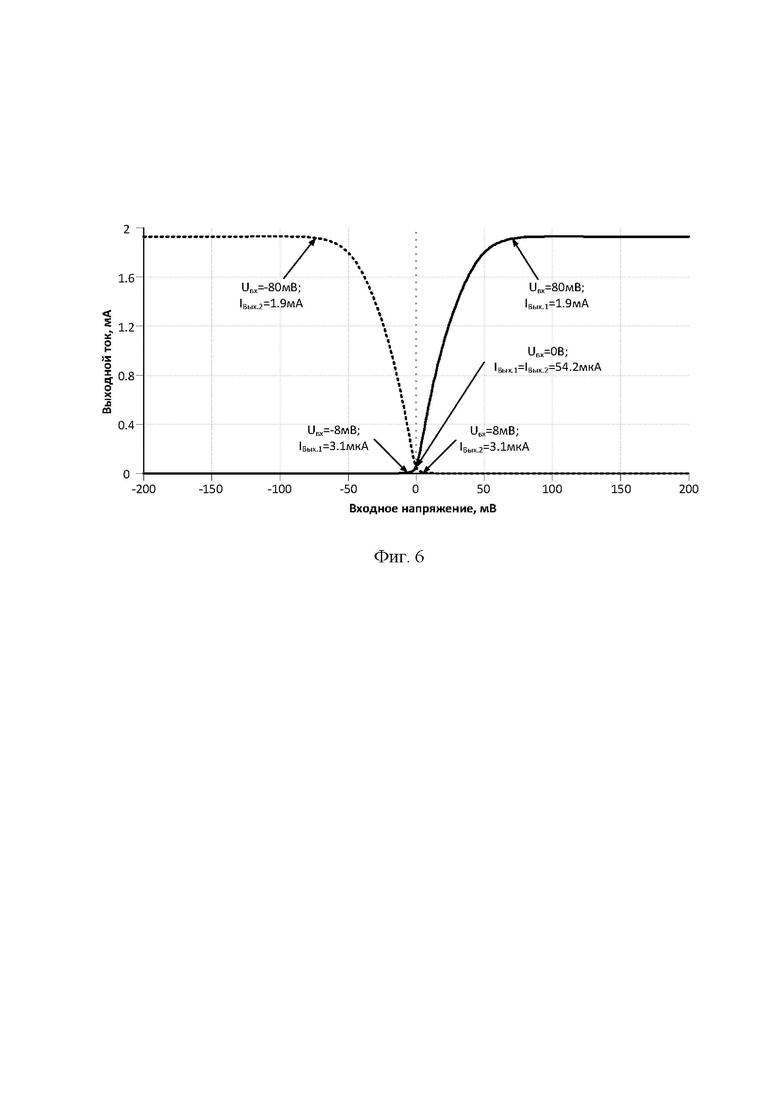

На чертеже фиг. 6 приведена зависимость выходных токов (Iвых.1, Iвых.2) ДК фиг. 5 от входного дифференциального напряжения.

Входной дифференциальный каскад класса АВ быстродействующего операционного усилителя фиг. 2 содержит входной параллельно-балансный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первую 6 шину источника питания, первый 7 и второй 8 вспомогательные транзисторы с объединенными базами, эмиттеры которых связаны со второй 9 шиной источника питания, первый 10 и второй 11 выходные транзисторы, причем коллектор первого 10 выходного транзистора связан с первым 12 токовым выходом устройства, а коллектор второго 11 выходного транзистора соединен со вторым 13 токовым выходом устройства, эмиттеры первого 10 и второго 11 выходных транзисторов связаны со второй 9 шиной источника питания, база первого 10 выходного транзистора соединена с коллектором первого 7 вспомогательного транзистора, база второго 11 выходного транзистора соединена с коллектором второго 8 вспомогательного транзистора, между базами первого 10 и второго 11 выходных транзисторов включены последовательно соединенные первый 14 и второй 15 вспомогательные резисторы, общий узел которых связан с объединенными базами первого 7 и второго 8 вспомогательных транзисторов, причем первая (6) шина источника питания связана с общей эмиттерной цепью входного параллельно-балансного каскада (1). В схему введены первый 19 и второй 20 дополнительные транзисторы, базы которых объединены и подключены к объединенным базам первого 7 и второго 8 вспомогательных транзисторов, коллектор первого 19 дополнительного транзистора соединен с базой первого 10 выходного транзистора, коллектор второго 20 дополнительного транзистора соединен с базой второго 11 выходного транзистора, эмиттер первого 19 дополнительного транзистора соединен с первым 4 токовым выходом входного параллельно-балансного каскада 1, а эмиттер второго 20 дополнительного транзистора соединен со вторым 5 токовым выходом входного параллельно-балансного каскада 1.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, между эмиттером и базой первого 19, а также между эмиттером и базой второго 20 дополнительных транзисторов включены соответствующие первый 21 и второй 22 согласующие резисторы.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, первый 10 и второй 11 выходные транзисторы выполнены как соответствующие каскодные составные транзисторы (10.1, 10.2 и 11.1, 11.2), причем база выходного транзистора 10.2 первого каскодного составного транзистора 10 подключена к эмиттеру первого 19 дополнительного транзистора, а база выходного транзистора 11.2 второго каскодного составного транзистора 11 подключена к эмиттеру второго 20 дополнительного транзистора.

На чертежах фиг. 2, фиг. 3, фиг. 4 входной параллельно-балансный каскад 1 выполнен на входных транзисторах 16, 17, общая эмиттерная цепь которых связана с первой 6 шиной источника питания через вспомогательный источник опорного тока 18.

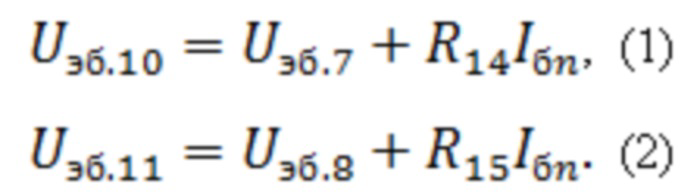

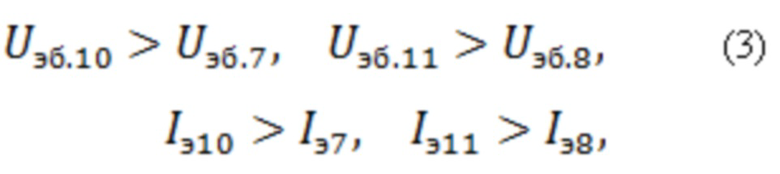

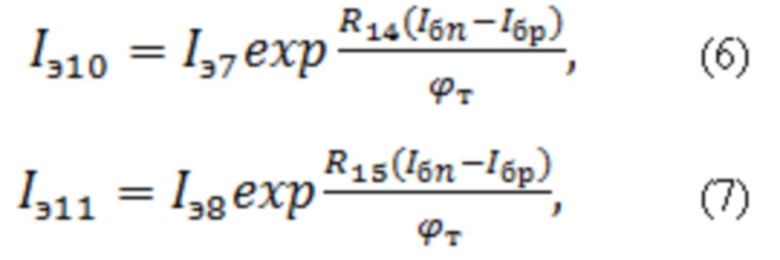

Рассмотрим вначале работу ДК-прототипа фиг. 1, в котором напряжением эмиттер-база транзисторов 7, 8, 10 и 11 связаны уравнениями Кирхгофа:

где Iбn - ток базы первого 7 и второго 8 p-n-p вспомогательных транзисторов, R14=R15 - сопротивления первого 14 и второго 15 вспомогательных резисторов.

Для повышения коэффициента усиления ДК по напряжению приходится выбирать относительно большими сопротивления первого 14 и второго 15 вспомогательных резисторов, что приводит, судя по уравнениям (1) и (2), к неравенствам

где Iэij - токи эмиттеров соответствующих транзисторов.

То есть выходные токи ДК Iвых.1=Iэ10 и Iвых.2=Iэ11 всегда больше, чем токи Iэ7≈I0 и Iэ8≈I0.

Для количественных оценок неравенств (3) экспоненциальные вольт-амперные характеристики эмиттерно-базового перехода биполярных транзисторов 10 и 7 аппроксимируем следующими известными уравнениями:

где Uxx, Ixx - характеристические параметры первого 10 выходного и первого 7 вспомогательного транзисторов, ϕт =26 мВ - температурный потенциал.

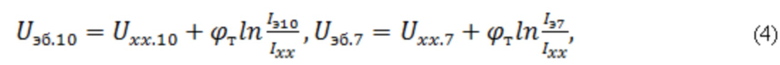

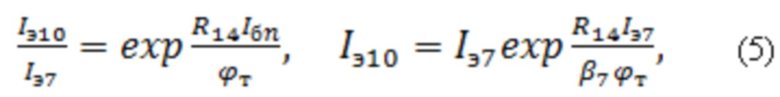

Поэтому из уравнений (1) и (2) можно получить

где β7 - статический коэффициент усиления по току базы p-n-p первого 7 и второго 8 вспомогательных транзисторов.

Таким образом, как следует из (5), статические коллекторные токи первого 10 и второго 11 выходных транзисторов в ДК-прототипе имеют экспоненциальную зависимость от тока эмиттера транзистора 7 (8) и сопротивления резистора 14 (15). Это является существенным недостатком известной схемы, т.к. здесь выходные статические токи ДК существенно (в десятки раз) превышают статические токи входных транзисторов 16 и 17.

Рассмотрим далее работу ДК фиг. 2.

С учетом формул (4) и (5) можно показать, что в заявляемой схеме токи эмиттера (коллектора) первого 10 и второго 11 выходных транзисторов связаны с сопротивлениями первого 14 и второго 15 вспомогательных резисторов следующими уравнениями

где R14, R15 - сопротивления первого 14 и второго 15 вспомогательных резисторов, Iбр - ток базы первого 19 и второго 20 дополнительных транзисторов.

Из уравнений (6) и (7) следует, что при равенстве Iбn=Iбp выходные статические токи ДК фиг. 2 равны статическим токам первого 7 и второго 8 вспомогательных транзисторов: Iэ10≈Iэ7, Iэ11≈Iэ8. Это является важным свойством предлагаемого устройства. Причем данный режим обеспечивается также при идентичных температурных и радиационных изменениях Iбn и Iбp.

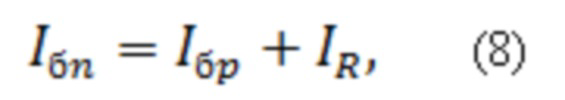

В тех случаях, когда условия Iбn=Iбp не выполняются, а ток Iбp<Iбn, в схеме фиг. 3, в соответствии с п. 2 формулы изобретения, вводятся первый 21 и второй 22 согласующие резисторы. В этом случае условия компенсации влияния токов базы на статический режим первого 10 и второго 11 выходных транзисторов могут быть записаны в виде

где IR - ток через первый 21 и второй 22 согласующие резисторы.

Для уменьшения влияния напряжения на второй 9 и первой 6 шинах питания на выходные статические токи ДК, в соответствии с п. 3 формулы изобретения, предусмотрено применение в качестве первого 10 и второго 11 выходных транзисторов их каскодных структур 10.1, 10.2 и 11.1, 11.2. При этом одновременно минимизируется влияние на статический режим первого 10 и второго 11 выходных транзисторов эффекта Эрли (модуляция базы), что также способствует повышению выходного сопротивления ДК по первому 12 и второму 13 токовым выходам и, как следствие, повышению предельных значений коэффициента усиления по напряжению.

Таким образом, ДК фиг. 2 (фиг. 3), в отличие от ДК-прототипа фиг. 1, работает в режиме класса АВ, когда его максимальные выходные токи Iвых.max значительно превышают выходные токи ДК в статическом режиме (Iвых.0). Увеличение Iвых.max, несмотря на нелинейность проходной характеристики, увеличивает скорость перезаряда корректирующего конденсатора ОУ, что позволяет повысить SR операционных усилителей на основе заявляемого ДК.

Существенная особенность предлагаемого ДК состоит в том, что он работает в режиме класса AB (фиг. 6) при более высоком отношении Iвых.max/Iвых.0, чем схема ДК-прототипа. Действительно, как следует из графиков фиг. 6, при нулевом входном сигнале выходные статические токи ДК в 40 раз меньше, чем его максимальные выходные токи при большом входном сигнале. Это позволяет получить в ОУ фиг. 4 на основе предлагаемого ДК более высокие (в 40 раз) значения максимальной скорости нарастания выходного напряжения при малых сквозных статических токах (Iскв≈Iвых.0).

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с известным схемотехническим решением ДК, что позволяет рекомендовать его для практического использования в быстродействующих ОУ с малым статическим током.

Библиографический список

1. Kannan, R. K. Guntreddi, K. Reddy, ''Transfer-function control in an active filter'' Patent appl. US 20110012678A1, Jan. 20, 2011, fig. 4c

2. T. Tanaka, M. Kubo, ''Differential current amplifier circuit''. US Patent 5132640, July 21, 1992, fig. 1.

3. Chamas, ''Baseband filters and interfaces between a digital-to-analog converter and a baseband filter, '' Patent appl. US 9647639B1, May 9, 2017, fig. 14

4. Yoshino Hiroshi, Matsuo Sakiko, “Differential amplifier circuit providing high gain output at low power supply voltage”, Patent US 5376897, December 27, 1994, fig. 3.

5. Katakura Masayuki, “Cross coupled symmetrical current source unit”, Patent US 5446409, August 29, 1995, fig. 9.

6. А. Paul, J. Ramirez-Angulo, A. D. Sánchez, A. J. López-Martín, R. G. Carvajal and F. X. Li, "Super-Gain-Boosted AB-AB Fully Differential Miller Op-Amp With 156dB Open-Loop Gain and 174MV/V MHZ pF/μW Figure of Merit in 130nm CMOS Technology," in IEEE Access, vol. 9, pp. 57603-57617, 2021. DOI: 10.1109/ACCESS.2021.3072595

7. Paul, J. Ramirez-Angulo, A. J. Löpez-Mart, R. G. Carvajal, and J. M. Rocha-Pdrez, “Pseudo-three-stage Miller op-amp with enhanced small-signal and large-signal performance,” IEEE Trans. Very Dirge Scale Integr (VLSI) Syst., vol. 27, no. 10, pp. 2249-2259, Oct. 2019.

8. J. Ramirez-Angulo and M. Holmes, “Simple technique using local CMFB to enhance slew rate and bandwidth of one-stage CMOS op-amps,” Electron. Dtt., vol. 38, no. 23, pp. 1409-1411, Nov. 2002.

9. M. H. Naderi, S. Prakash and J. Silva-Martinez, "Operational Transconductance Amplifier With Class-B Slew-Rate Boosting for Fast High-Performance Switched-Capacitor Circuits," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 11, pp. 3769-3779, Nov. 2018. doi: 10.1109/TCSI.2018.2852273

10. S. Kumar, R. Goroju, D. K. Bhat, K. S. Rakshitdatta and N. Krishnapura, "Design Considerations for Low-Distortion Filter and Oscillator ICs for Testing High-Resolution ADCs," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 9, pp. 3393-3401, Sept. 2019. doi: 10.1109/TCSI.2019.2926927

11. Martínez-Nieto J. A. et al. High-Linearity Self-Biased CMOS Current Buffer //Electronics. - 2018. - vol. 7. - no. 12. - pp. 423. doi: 10.3390/electronics7120423

12. Das D. M. et al. ''A novel low-noise fully differential CMOS instrumentation amplifier with 1.88 noise efficiency factor for biomedical and sensor applications, '' Microelectronics Journal. - 2016. - vol. 53. - pp. 35-44. doi: 10.1016/j.mejo.2016.04.008

13. Cellucci D. et al. ''0.6-V CMOS cascode OTA with complementary gate-driven gain-boosting and forward body bias,'' International Journal of Circuit Theory and Applications. - 2020. - Т. 48. - №. 1. - С. 15-27. DOI: 10.1002/cta.2703

14. Shad E. H. T., Molinas M., Ytterdal T. ''A fully differential capacitively-coupled high CMRR low-power chopper amplifier for EEG dry electrodes, '' Analog Integrated Circuits and Signal Processing. - 2020. - vol. 102. - no. 2. - pp. 353-362. doi: 10.1007/s10470-019-01577-w

15. Y. Zheng, J. Lan, F. Ye and J. Ren, "A 12-bit 100MS/s SAR ADC With Equivalent Split-Capacitor and LSB-Averaging in 14-nm CMOS FinFET," in IEEE Access, vol. 9, pp. 169107-169121, 2021. doi: 10.1109/ACCESS.2021.3135042

16. Paul, J.  A. J.

A. J.  R. G. Carvajal and J. M.

R. G. Carvajal and J. M.  "Pseudo-Three-Stage Miller Op-Amp With Enhanced Small-Signal and Large-Signal Performance," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 10, pp. 2246-2259, Oct. 2019. doi: 10.1109/TVLSI.2019.2918235

"Pseudo-Three-Stage Miller Op-Amp With Enhanced Small-Signal and Large-Signal Performance," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 10, pp. 2246-2259, Oct. 2019. doi: 10.1109/TVLSI.2019.2918235

17. Vafaei M. et al. ''A low power and ultra-high input impedance analog front end based on fully differential difference inverter-based amplifier for biomedical applications, '' AEU-International Journal of Electronics and Communications. - 2021. - vol. 142. - pp. 154005. doi: 10.1016/j.aeue.2021.154005

18. S. Pourashraf, J. Ramirez-Angulo, A. J. Lopez-Martin and R.  "A Highly Efficient Composite Class-AB-AB Miller Op-Amp With High Gain and Stable From 15 pF Up To Very Large Capacitive Loads," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 10, pp. 2061-2072, Oct. 2018. doi: 10.1109/TVLSI.2018.2830365

"A Highly Efficient Composite Class-AB-AB Miller Op-Amp With High Gain and Stable From 15 pF Up To Very Large Capacitive Loads," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 10, pp. 2061-2072, Oct. 2018. doi: 10.1109/TVLSI.2018.2830365

| название | год | авторы | номер документа |

|---|---|---|---|

| ВХОДНОЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С РЕЗИСТИВНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2022 |

|

RU2784382C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| МНОГОКАНАЛЬНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2626667C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД С ПОВЫШЕННЫМ УСИЛЕНИЕМ ПО НАПРЯЖЕНИЮ | 2011 |

|

RU2461957C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2412528C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ "НАПРЯЖЕНИЕ-ТОК" С ШИРОКИМ ДИАПАЗОНОМ ЛИНЕЙНОЙ РАБОТЫ | 2017 |

|

RU2658818C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в структуре аналоговых микросхем различного функционального назначения, например операционных усилителях (ОУ), компенсационных стабилизаторах напряжения, компараторах и т.п. Техническим результатом изобретения является обеспечение работы дифференциального каскада (ДК) в режиме класса АВ при повышенных отношениях его максимальных выходных токов Iвых.max на первом 12 и втором 13 токовых выходах к статическим значениям его выходных токов Iвых.0, которые определяются при нулевом входном напряжении ДК. Входной дифференциальный каскад класса АВ быстродействующего операционного усилителя дополнительно содержит первый (19) и второй (20) дополнительные транзисторы. Базы первого (19) и второго (20) дополнительных транзисторов объединены и подключены к объединенным базам первого (7) и второго (8) вспомогательных транзисторов. Коллектор первого (19) дополнительного транзистора соединен с базой первого (10) выходного транзистора. Коллектор второго (20) дополнительного транзистора соединен с базой второго (11) выходного транзистора. Эмиттер первого (19) дополнительного транзистора соединен с первым (4) токовым выходом входного параллельно-балансного каскада (1). Эмиттер второго (20) дополнительного транзистора соединен со вторым (5) токовым выходом входного параллельно-балансного каскада (1). 2 з.п. ф-лы, 6 ил.

1. Входной дифференциальный каскад класса АВ быстродействующего операционного усилителя, содержащий входной параллельно-балансный каскад (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, первую (6) шину источника питания, первый (7) и второй (8) вспомогательные транзисторы с объединенными базами, эмиттеры которых связаны со второй (9) шиной источника питания, первый (10) и второй (11) выходные транзисторы, причем коллектор первого (10) выходного транзистора связан с первым (12) токовым выходом устройства, а коллектор второго (11) выходного транзистора соединен со вторым (13) токовым выходом устройства, эмиттеры первого (10) и второго (11) выходных транзисторов связаны со второй (9) шиной источника питания, база первого (10) выходного транзистора соединена с коллектором первого (7) вспомогательного транзистора, база второго (11) выходного транзистора соединена с коллектором второго (8) вспомогательного транзистора, между базами первого (10) и второго (11) выходных транзисторов включены последовательно соединенные первый (14) и второй (15) вспомогательные резисторы, общий узел которых связан с объединенными базами первого (7) и второго (8) вспомогательных транзисторов, причем первая (6) шина источника питания связана с общей эмиттерной цепью входного параллельно-балансного каскада (1), отличающийся тем, что в схему введены первый (19) и второй (20) дополнительные транзисторы, базы которых объединены и подключены к объединенным базам первого (7) и второго (8) вспомогательных транзисторов, коллектор первого (19) дополнительного транзистора соединен с базой первого (10) выходного транзистора, коллектор второго (20) дополнительного транзистора соединен с базой второго (11) выходного транзистора, эмиттер первого (19) дополнительного транзистора соединен с первым (4) токовым выходом входного параллельно-балансного каскада (1), а эмиттер второго (20) дополнительного транзистора соединен со вторым (5) токовым выходом входного параллельно-балансного каскада (1).

2. Входной дифференциальный каскад класса АВ быстродействующего операционного усилителя по п. 1, отличающийся тем, что между эмиттером и базой первого (19), а также между эмиттером и базой второго (20) дополнительных транзисторов включены соответствующие первый (21) и второй (22) согласующие резисторы.

3. Входной дифференциальный каскад класса АВ быстродействующего операционного усилителя по п. 1, отличающийся тем, что первый (10) и второй (11) выходные транзисторы выполнены как соответствующие каскодные составные транзисторы (10.1, 10.2 и 11.1, 11.2), причем база выходного транзистора (10.2) первого каскодного составного транзистора (10) подключена к эмиттеру первого (19) дополнительного транзистора, а база выходного транзистора (11.2) второго каскодного составного транзистора (11) подключена к эмиттеру второго (20) дополнительного транзистора.

| US 5376897 A, 27.12.1994 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| МНОГОКАНАЛЬНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2626667C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2007 |

|

RU2331970C1 |

| УСИЛИТЕЛЬ МОЩНОСТИ И СПОСОБ, РЕАЛИЗОВАННЫЙ В НЕМ | 1998 |

|

RU2168262C1 |

| US 5132640 A, 21.07.1992 | |||

| US 5293136 A, 08.03.1994 | |||

| US 2006220741 A1, 05.10.2006 | |||

| ZHENG Y., LAN J., YE F., REN J | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

2022-12-21—Публикация

2022-04-04—Подача