Изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых интерфейсах, например, драйверах АЦП на основе быстродействующих операционных усилителей (ОУ).

Максимальная скорость нарастания выходного напряжения (SR) современных операционных усилителей с однополюсной частотной коррекцией в значительной степени определяется максимальным выходным током Iвых.max входного каскада, который перезаряжает корректирующий конденсатор ОУ (Cк):

В современной микроэлектронике широкое распространение получили входные дифференциальные каскады (ДК) класса АВ с резистивной отрицательной обратной связью по синфазному сигналу [1-22], повышающие SR. Данное схемотехническое решение относится к числу базовых основ современной быстродействующей аналоговой микросхемотехники [8-22].

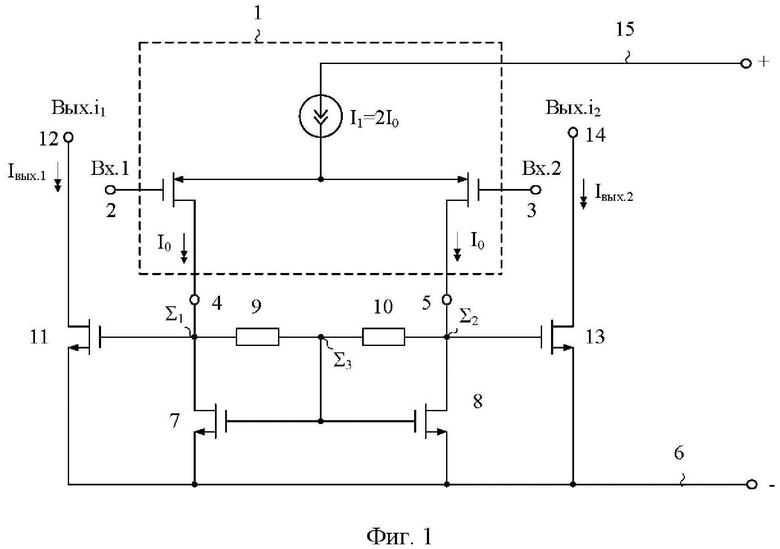

Ближайшим прототипом (фиг. 1) заявляемого устройства является КМОП входной ДК по патентной заявке US 2011/0012678, fig. 4, 2011 г. Он содержит (фиг. 1) входной параллельно-балансный усилитель 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, которые согласованы с первой 6 шиной источника питания, первый 7 и второй 8 согласующие транзисторы, затворы которых объединены, а истоки соединены с первой 6 шиной источника питания, первый 9 и второй 10 последовательно соединенные согласующие резисторы, включенные между первым 4 токовым выходом входного параллельно-балансного усилителя 1, связанным со стоком первого 7 согласующего транзистора и вторым 5 токовым выходом входного параллельно-балансного усилителя 1, соединенным со стоком второго 8 согласующего транзистора, причем общий узел последовательно соединенных первого 9 и второго 10 согласующих резисторов соединен с затворами первого 7 и второго 8 согласующих транзисторов, первый 11 выходной транзистор, сток которого связан с первым 12 токовым выходом устройства, затвор - соединен со стоком первого 7 согласующего транзистора, а исток подключен к первой 6 шине источника питания, второй 13 выходной транзистор, сток которого связан со вторым 14 токовым выходом устройства, затвор подключен к стоку второго 8 согласующего транзистора, а исток соединен с первой 6 шиной источника питания, причем первый 12 и второй 14 токовые выходы устройства согласованы со второй 15 шиной источника питания.

Существенный недостаток известного входного ДК класса АВ (фиг. 1) состоит в том, что его выходные статические токи Iвых.0 имеют (при Uвх=0) сравнительно большое значение. Данный вывод следует из результатов компьютерного моделирования ДК фиг. 1, представленных на чертеже фиг. 5. Здесь выходной статический ток Iвых.0 ДК принимает большое значение. Это отрицательно сказывается на статическом токопотреблении быстродействующего ОУ с рассматриваемым входным ДК.

Основная задача предлагаемого изобретения состоит в создании входного ДК, у которого коэффициент эффективности по току, определяемый как отношение Ni = Iвых.max / Iвых.0 , существенно лучше (Ni >>1), чем в ДК-прототипе. Как следствие, это повышает максимальную скорость нарастания выходного напряжения ОУ на основе ДК при малом статическом токе, потребляемом ОУ от источника питания.

Поставленная задача достигается тем, что во входном каскаде операционного усилителя фиг.1, содержащем входной параллельно-балансный усилитель 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, которые согласованы с первой 6 шиной источника питания, первый 7 и второй 8 согласующие транзисторы, затворы которых объединены, а истоки соединены с первой 6 шиной источника питания, первый 9 и второй 10 последовательно соединенные согласующие резисторы, включенные между первым 4 токовым выходом входного параллельно-балансного усилителя 1, связанным со стоком первого 7 согласующего транзистора и вторым 5 токовым выходом входного параллельно-балансного усилителя 1, соединенным со стоком второго 8 согласующего транзистора, причем общий узел последовательно соединенных первого 9 и второго 10 согласующих резисторов соединен с затворами первого 7 и второго 8 согласующих транзисторов, первый 11 выходной транзистор, сток которого связан с первым 12 токовым выходом устройства, затвор - соединен со стоком первого 7 согласующего транзистора, а исток подключен к первой 6 шине источника питания, второй 13 выходной транзистор, сток которого связан со вторым 14 токовым выходом устройства, затвор подключен к стоку второго 8 согласующего транзистора, а исток соединен с первой 6 шиной источника питания, причем первый 12 и второй 14 токовые выходы устройства согласованы со второй 15 шиной источника питания, предусмотрены новые элементы и связи - затворы первого 7 и второго 8 согласующих транзисторов соединены с выходом 16 дополнительного источника компенсирующего тока 17, содержащего входы положительного 18, отрицательного 19 и общего 20 электропитания, которые связаны с соответствующими второй 15 и первой 6 шинами источников питания, а также общей шиной 21 источников питания.

На чертеже фиг. 1 показана схема входного ДК класса АВ - прототипа при его выполнении на КМОП транзисторах.

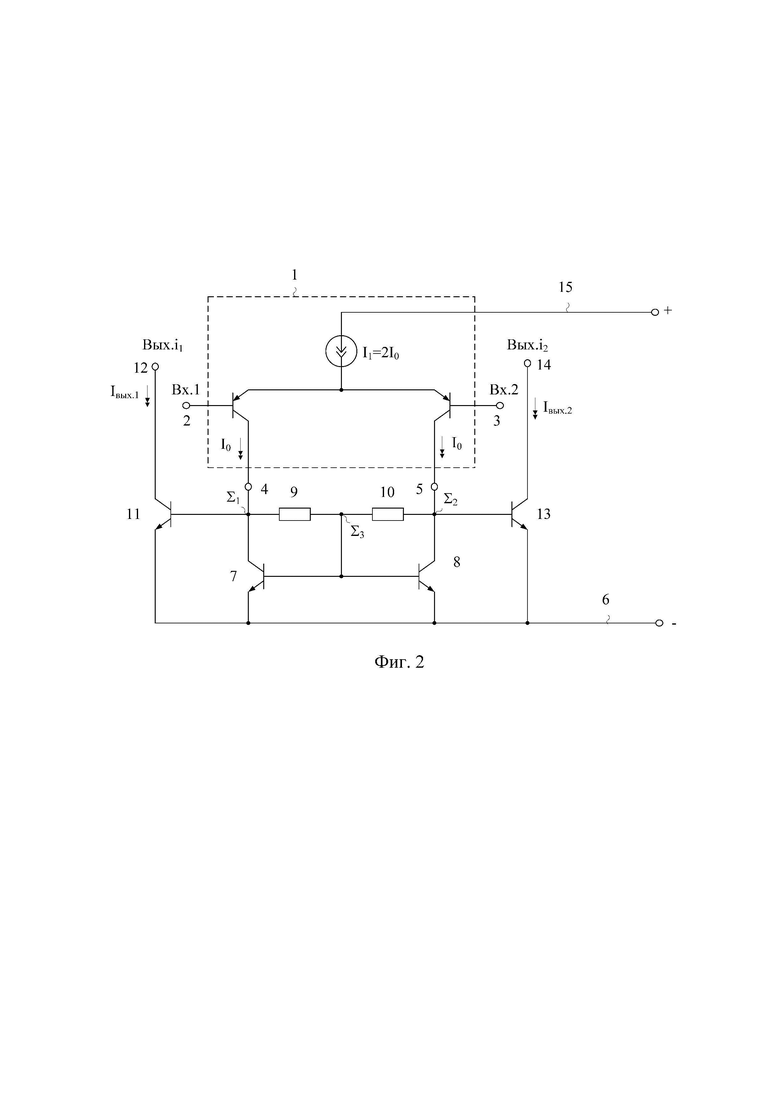

На чертеже фиг. 2 в качестве примера приведена схема входного каскада класса АВ фиг. 1 при его реализации на другой элементной базе - биполярных транзисторах (патенты US 5.376.897, fig.3, US 5.446.409, fig. 9, US 5.132.640), у которых направления статических токов выводов и напряжения между выводами совпадают с аналогичными координатами КМОП транзисторов [23]. То есть предлагаемое схемотехническое решение может быть выполнено не только на КМОП транзисторах, но и по другим перспективным технологическим процессам (TFT, SiGe, GaAs, GaN, SiC и др.).

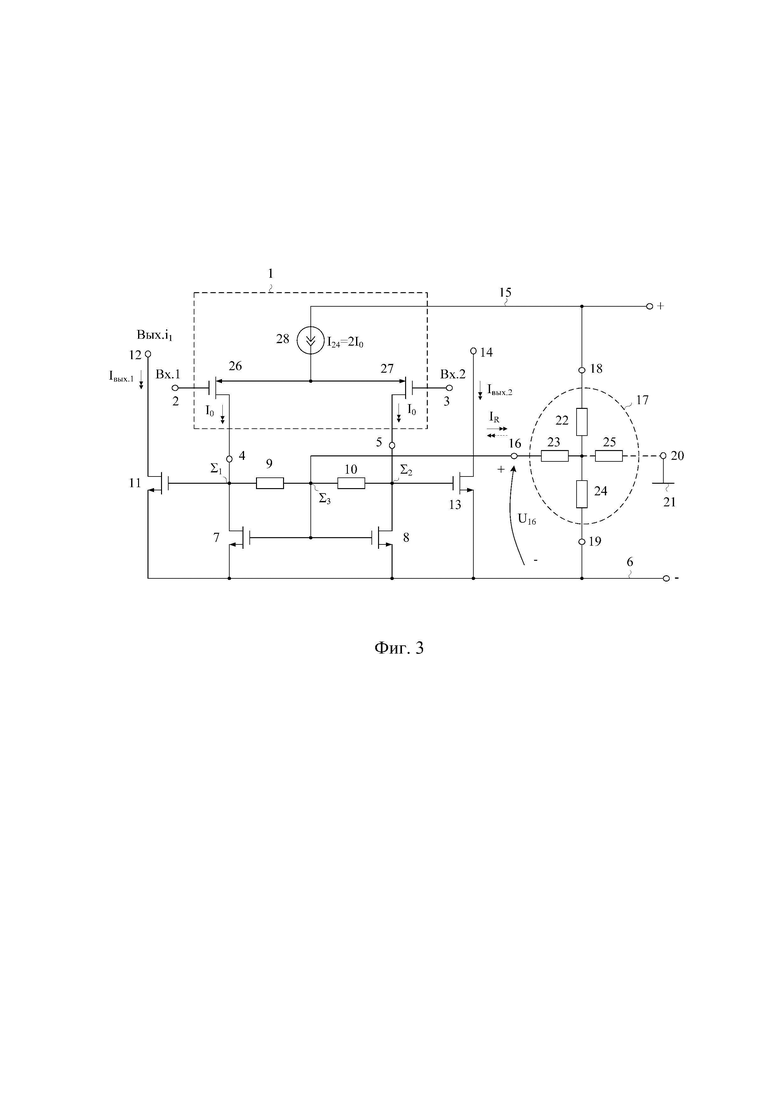

На чертеже фиг. 3 приведена схема заявляемого входного ДК класса АВ для случая его реализации на КМОП транзисторах в соответствии с п. 1, п. 2, п.3, п.4 формулы изобретения.

На чертеже фиг. 4 в качестве примера показана схема заявляемого входного ДК класса АВ для случая его реализации на биполярных транзисторах.

На чертеже фиг. 5 приведена cхема входного каскада - прототипа фиг. 1 и ее статический режим в среде Cadence OrCAD 16.6 на моделях транзисторов TSMС 0.35um.

На чертеже фиг. 6 представлен статический режим схемы ДК фиг. 3 в среде Cadence OrCAD 16.6 на моделях транзисторов TSMС 0.35um.

На чертеже фиг. 7 показана зависимость выходного тока ДК фиг. 6 Iвых (IRload1 и IRload2) от входного напряжения V3 при I2=435мкА, R3=1кОм в укрупненном масштабе.

На чертеже фиг. 8 представлен статический режим схемы ОУ с предлагаемым входным каскадом фиг. 3 в среде Cadence OrCAD 16.6 на моделях транзисторов TSMС 0.35um при I2=435мкА и R3=1кОм.

Входной каскад класса АВ быстродействующего операционного усилителя с резистивной отрицательной обратной связью по синфазному сигналу фиг. 2 содержит входной параллельно-балансный усилитель 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, которые согласованы с первой 6 шиной источника питания, первый 7 и второй 8 согласующие транзисторы, затворы которых объединены, а истоки соединены с первой 6 шиной источника питания, первый 9 и второй 10 последовательно соединенные согласующие резисторы, включенные между первым 4 токовым выходом входного параллельно-балансного усилителя 1, связанным со стоком первого 7 согласующего транзистора и вторым 5 токовым выходом входного параллельно-балансного усилителя 1, соединенным со стоком второго 8 согласующего транзистора, причем общий узел последовательно соединенных первого 9 и второго 10 согласующих резисторов соединен с затворами первого 7 и второго 8 согласующих транзисторов, первый 11 выходной транзистор, сток которого связан с первым 12 токовым выходом устройства, затвор - соединен со стоком первого 7 согласующего транзистора, а исток подключен к первой 6 шине источника питания, второй 13 выходной транзистор, сток которого связан со вторым 14 токовым выходом устройства, затвор подключен к стоку второго 8 согласующего транзистора, а исток соединен с первой 6 шиной источника питания, причем первый 12 и второй 14 токовые выходы устройства согласованы со второй 15 шиной источника питания. Затворы первого 7 и второго 8 согласующих транзисторов соединены с выходом 16 дополнительного источника компенсирующего тока 17, содержащего входы положительного 18, отрицательного 19 и общего 20 электропитания, которые связаны с соответствующими второй 15 и первой 6 шинами источников питания, а также общей шиной 21 источников питания.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, дополнительный источник компенсирующего тока 17 содержит первый 22, второй 23 и третий 24 двухполюсники, причем первый 22 и третий 24 двухполюсники включены последовательно между входами положительного 18 и отрицательного 19 электропитания дополнительного источника компенсирующего тока 17, а второй 23 двухполюсник включен между выходом 16 дополнительного источника компенсирующего тока 17 и общим узлом последовательно соединенных первого 22 и третьего 24 двухполюсников.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, общий узел первого 22 и третьего 24 двухполюсников в структуре дополнительного источника компенсирующего тока 17 связан с общей шиной 21источников питания через четвертый 25 двухполюсник.

На чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, входной параллельно-балансный усилитель 1 выполнен на первом 26 и втором 27 входных полевых транзисторах, общая истоковая цепь которых связана со второй 15 шиной источника питания через токостабилизирующий двухполюсник 28.

На чертеже фиг. 4 приведен пример применения заявляемого устройства при его реализации на другой элементной базе. Здесь вместо упомянутых в п.1 и п.4 всех полевых транзисторов используются соответствующие биполярные транзисторы, причем коллектор каждого биполярного транзистора соответствует по схеме включения стоку, база - затвору, а эмиттер - истоку полевого транзистора [23].

Рассмотрим вначале недостатки ДК-прототипа фиг. 1. Первый 11 и второй 13 выходные транзисторы в схеме фиг. 1 работают при напряжениях между затвором и стоком, близких к напряжению на второй 15 шине источника питания. За счет эффекта модуляции длины канала напряжение между истоком и затвором этих транзисторов оказываются меньше чем напряжение между затвором и истоком первого 7 и второго 8 согласующих транзисторов. Как следствие, выходные статические токи ДК фиг. 1 значительно превышают статические токи стока первого 7 и второго 8 согласующих транзисторов. Таким образом, классическая схема входного каскада класса АВ характеризуется сравнительно малым отношением токов Iвых.max/Iвых.0, что не позволяет реализовывать на его основе микромощные быстродействующие ОУ.

В заявляемом устройстве фиг. 3 этот недостаток устранен - статический ток ДК по первому 12 и второму 14 токовым выходам составляет 256 мкА. Как следствие, предлагаемый ДК имеет повышенное отношение токов

Ni=Iвых.max/Iвых.0>>100,

где Iвых.max - максимальные значения выходных токов ДК.

Это значительно больше, чем Ni в схеме ДК-прототипа.

Предлагаемое схемотехническое решение актуально не только для КМОП аналоговых устройств, но и для микросхем на основе биполярных транзисторов (фиг. 4), в которых за счет введения новых связей также обеспечивается уменьшение статического тока, потребляемого от источника питания.

Первый 22, второй 23, третий 24 и четвертый 25 двухполюсники в схеме дополнительного источника компенсирующего тока 17 (фиг. 3, фиг. 4) могут выполняться как на резисторах, так и на вспомогательных источниках опорного тока, а также p-n переходах, реализуемых на КМОП или BJT транзисторах.

Таким образом,

- дифференциальный каскад фиг. 3 работает в режиме класса «АВ» с малым статическим токопотреблением, причем его максимальный выходной ток существенно превышает выходной статический ток ДК Iвых.0=256 мкА. В конечном итоге это способствует существенному повышению максимальной скорости нарастания выходного напряжения микромощного ОУ с предлагаемым ДК (фиг. 8);

- рассмотренное схемотехническое решение имеет существенные преимущества в сравнении с ДК-прототипом и перспективно для использования не только в ОУ, но и в компенсационных стабилизаторах напряжения, которые должны обеспечивать повышенные токи в нагрузке при малом собственном токопотреблении в статическом режиме;

- за счет введения новых элементов и связей между ними в предлагаемом ДК решается проблема энергоэффективности достаточно обширного класса аналоговых микросхем [1-22], который является одним из «кирпичиков» современной быстродействующей микроэлектроники.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. A. Kannan, R. K. Guntreddi, K. Reddy, ''Transfer-function control in an active filter'' Patent appl. US 20110012678A1, Jan. 20, 2011

2. T. Tanaka, M. Kubo, ''Differential current amplifier circuit'' US Patent 5132640, July 21, 1992.

3. I. Chamas, ''Baseband filters and interfaces between a digital-to-analog converter and a baseband filter, '' Patent appl. US 9647639B1, May 9, 2017

4. Katakura Masayuki, “Cross coupled symmetrical current source unit”, Pat. US 5446409, August 29, 1995, fig. 9

5. Yamamoto; Takeshi, “Differential amplifier and filter circuit using the same”, Pat. US 6552611, April 22, 2003, fig. 10

6. Taylor; Clive Roland, “High frequency differential amplifier”, Pat. US 6624697 B2, September 23, 2003, fig. 1

7. Yoshino Hiroshi, Matsuo Sakiko, ”Differential amplifier circuit providing high gain output at low power supply voltage”, Pat. US 5376897, December 27, 1994, fig. 3

8. А. Paul, J. Ramirez-Angulo, A. D. Sánchez, A. J. López-Martín, R. G. Carvajal and F. X. Li, "Super-Gain-Boosted AB-AB Fully Differential Miller Op-Amp With 156dB Open-Loop Gain and 174MV/V MHZ pF/μW Figure of Merit in 130nm CMOS Technology," in IEEE Access, vol. 9, pp. 57603-57617, 2021. DOI: 10.1109/ACCESS.2021.3072595

9. A. Paul, J. Ramirez-Angulo, A. J. Löpez-Mart, R. G. Carvajal, and J. M. Rocha-Pdrez, “Pseudo-three-stage Miller op-amp with enhanced small-signal and large-signal performance,” IEEE Trans. Very Dirge Scale Integr (VLSI) Syst., vol. 27, no. 10, pp. 2249-2259, Oct. 2019.

10. J. Ramirez-Angulo and M. Holmes, “Simple technique using local CMFB to enhance slew rate and bandwidth of one-stage CMOS op-amps,” Electron. Dtt., vol. 38, no. 23, pp. 1409-1411, Nov. 2002.

11. M. H. Naderi, S. Prakash and J. Silva-Martinez, "Operational Transconductance Amplifier With Class-B Slew-Rate Boosting for Fast High-Performance Switched-Capacitor Circuits," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 11, pp. 3769-3779, Nov. 2018. doi: 10.1109/TCSI.2018.2852273

12. S. Kumar, R. Goroju, D. K. Bhat, K. S. Rakshitdatta and N. Krishnapura, "Design Considerations for Low-Distortion Filter and Oscillator ICs for Testing High-Resolution ADCs," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 9, pp. 3393-3401, Sept. 2019. doi: 10.1109/TCSI.2019.2926927

13. Martínez-Nieto J. A. et al. High-Linearity Self-Biased CMOS Current Buffer //Electronics. - 2018. - vol. 7. - no. 12. - pp. 423. doi: 10.3390/electronics7120423

14. Das D. M. et al. ''A novel low-noise fully differential CMOS instrumentation amplifier with 1.88 noise efficiency factor for biomedical and sensor applications, '' Microelectronics Journal. - 2016. - vol. 53. - pp. 35-44. doi: 10.1016/j.mejo.2016.04.008

15. Cellucci D. et al. ''0.6-V CMOS cascode OTA with complementary gate-driven gain-boosting and forward body bias,'' International Journal of Circuit Theory and Applications. - 2020. - Т. 48. - №. 1. - С. 15-27. DOI: 10.1002/cta.2703

16. Shad E. H. T., Molinas M., Ytterdal T. ''A fully differential capacitively-coupled high CMRR low-power chopper amplifier for EEG dry electrodes, '' Analog Integrated Circuits and Signal Processing. - 2020. - vol. 102. - no. 2. - pp. 353-362. doi: 10.1007/s10470-019-01577-w

17. Y. Zheng, J. Lan, F. Ye and J. Ren, "A 12-bit 100MS/s SAR ADC With Equivalent Split-Capacitor and LSB-Averaging in 14-nm CMOS FinFET," in IEEE Access, vol. 9, pp. 169107-169121, 2021. doi: 10.1109/ACCESS.2021.3135042

18. A. Paul, J. Ramírez-Angulo, A. J. López-Martín, R. G. Carvajal and J. M. Rocha-Pérez, "Pseudo-Three-Stage Miller Op-Amp With Enhanced Small-Signal and Large-Signal Performance," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 10, pp. 2246-2259, Oct. 2019. doi: 10.1109/TVLSI.2019.2918235

19. Vafaei M. et al. ''A low power and ultra-high input impedance analog front end based on fully differential difference inverter-based amplifier for biomedical applications, '' AEU-International Journal of Electronics and Communications. - 2021. - vol. 142. - pp. 154005. doi: 10.1016/j.aeue.2021.154005

20. S. Pourashraf, J. Ramirez-Angulo, A. J. Lopez-Martin and R. González-Carvajal, "A Highly Efficient Composite Class-AB-AB Miller Op-Amp With High Gain and Stable From 15 pF Up To Very Large Capacitive Loads," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 10, pp. 2061-2072, Oct. 2018. doi: 10.1109/TVLSI.2018.2830365

21. E. Cabrera-Bernal, S. Pennisi, A. D. Grasso, A. Torralba and R. G. Carvajal, "0.7-V Three-Stage Class-AB CMOS Operational Transconductance Amplifier," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 63, no. 11, pp. 1807-1815, Nov. 2016, doi: 10.1109/TCSI.2016.2597440.

22. M. P. Garde, A. Lopez-Martin, R. G. Carvajal and J. Ramírez-Angulo, "Super Class-AB Recycling Folded Cascode OTA," in IEEE Journal of Solid-State Circuits, vol. 53, no. 9, pp. 2614-2623, Sept. 2018, doi: 10.1109/JSSC.2018.2844371, fig. 1c

23. П.Хоровиц, У. Хилл. Искусство схемотехники / пер. с англ.; издание седьмое. - М: Бином, 2014. - С. 122, раздел 3.01.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2720555C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786507C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ УРОВНЕМ СИСТЕМАТИЧЕСКОЙ СОСТАВЛЯЮЩЕЙ НАПРЯЖЕНИЯ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2780221C1 |

| МНОГОКАНАЛЬНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2626667C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания | 2024 |

|

RU2822991C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2624585C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых интерфейсах, например драйверах АЦП на основе быстродействующих операционных усилителей (ОУ). Технический результат заключается в повышении максимальной скорости нарастания выходного напряжения ОУ при малом статическом токе, потребляемом ОУ от источника питания. Входной каскад класса АВ быстродействующего операционного усилителя с резистивной отрицательной обратной связью по синфазному сигналу содержит входной параллельно-балансный усилитель (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, которые согласованы с первой (6) шиной источника питания, первый (7) и второй (8) согласующие транзисторы, первый (9) и второй (10) последовательно соединенные согласующие резисторы, первый (11) выходной транзистор, сток которого связан с первым (12) токовым выходом устройства, затвор соединен со стоком первого (7) согласующего транзистора, а исток подключен к первой (6) шине источника питания, второй (13) выходной транзистор, сток которого связан со вторым (14) токовым выходом устройства, затвор подключен к стоку второго (8) согласующего транзистора, а исток соединен с первой (6) шиной источника питания, причем первый (12) и второй (14) токовые выходы устройства согласованы со второй (15) шиной источника питания. Затворы первого (7) и второго (8) согласующих транзисторов соединены с выходом (16) дополнительного источника компенсирующего тока (17), содержащего входы положительного (18), отрицательного (19) и общего (20) электропитания, которые связаны с соответствующими второй (15) и первой (6) шинами источников питания, а также общей шиной (21) источников питания. 3 з.п. ф-лы, 8 ил.

1. Входной каскад класса АВ быстродействующего операционного усилителя с резистивной отрицательной обратной связью по синфазному сигналу, содержащий входной параллельно-балансный усилитель (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, которые согласованы с первой (6) шиной источника питания, первый (7) и второй (8) согласующие транзисторы, затворы которых объединены, а истоки соединены с первой (6) шиной источника питания, первый (9) и второй (10) последовательно соединенные согласующие резисторы, включенные между первым (4) токовым выходом входного параллельно-балансного усилителя (1), связанным со стоком первого (7) согласующего транзистора, и вторым (5) токовым выходом входного параллельно-балансного усилителя (1), соединенным со стоком второго (8) согласующего транзистора, причем общий узел последовательно соединенных первого (9) и второго (10) согласующих резисторов соединен с затворами первого (7) и второго (8) согласующих транзисторов, первый (11) выходной транзистор, сток которого связан с первым (12) токовым выходом устройства, затвор соединен со стоком первого (7) согласующего транзистора, а исток подключен к первой (6) шине источника питания, второй (13) выходной транзистор, сток которого связан со вторым (14) токовым выходом устройства, затвор подключен к стоку второго (8) согласующего транзистора, а исток соединен с первой (6) шиной источника питания, причем первый (12) и второй (14) токовые выходы устройства согласованы со второй (15) шиной источника питания, отличающийся тем, что затворы первого (7) и второго (8) согласующих транзисторов соединены с выходом (16) дополнительного источника компенсирующего тока (17), содержащего входы положительного (18), отрицательного (19) и общего (20) электропитания, которые связаны с соответствующими второй (15) и первой (6) шинами источников питания, а также общей шиной (21) источников питания.

2. Входной каскад класса АВ быстродействующего операционного усилителя с резистивной отрицательной обратной связью по синфазному сигналу по п.1, отличающийся тем, что дополнительный источник компенсирующего тока (17) содержит первый (22), второй (23) и третий (24) двухполюсники, причем первый (22) и третий (24) двухполюсники включены последовательно между входами положительного (18) и отрицательного (19) электропитания дополнительного источника компенсирующего тока (17), а второй (23) двухполюсник включен между выходом (16) дополнительного источника компенсирующего тока (17) и общим узлом последовательно соединенных первого (22) и третьего (24) двухполюсников.

3. Входной каскад класса АВ быстродействующего операционного усилителя с резистивной отрицательной обратной связью по синфазному сигналу по п.2, отличающийся тем, что общий узел первого (22) и третьего (24) двухполюсников в структуре дополнительного источника компенсирующего тока (17) связан с общей шиной (21) источников питания через четвертый (25) двухполюсник.

4. Входной каскад класса АВ быстродействующего операционного усилителя с резистивной отрицательной обратной связью по синфазному сигналу по п.1, отличающийся тем, что входной параллельно-балансный усилитель (1) выполнен на первом (26) и втором (27) входных полевых транзисторах, общая истоковая цепь которых связана со второй (15) шиной источника питания через токостабилизирующий двухполюсник (28).

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2659476C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2006 |

|

RU2321160C1 |

| КОМПЛЕМЕНТАРНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2510570C1 |

Авторы

Даты

2022-11-24—Публикация

2022-04-01—Подача