Изобретение относится к автоматическим регуляторам, реализующим пропорционально-интегрально-дифференциальный закон регулирования, и может быть использовано для регулирования любых технологических объектов, имеющих дрейф параметров и подверженных неконтролируемым возмущениям.

Известен пропорционально-интегрально-дифференциальный регулятор, содержащий блок сравнения, блок задания объекта регулирования, блоки умножения, пропорциональные блоки, ограничители, сумматоры, блок определения модуля, нелинейный блок с зоной нечувствительности, дифференциатор, ключ, интегратор, элемент ИЛИ (№ 2234116, G05B 11/36, опубл 10.08.2004, бюл. № 22).

Недостатком данного ПИД-регулятора является сложность конструкции и недостаточная скорость и точность регулирования технологических процессов.

Известен также ПИД-регулятор, содержащий интегратор, дифференциатор, три сумматора, нелинейный ограничитель, два релейных элемента, переключатель параметров, три элемента ИЛИ и делитель (№2156992, G05B 11/36, опубл 27.09.2000, бюл. № 27).

Недостатком данного регулятора является невысокое качество регулирования и ограниченная область устойчивости при дрейфе параметров объекта с запаздыванием и действии на входе системы возмущений. Известный регулятор ориентирован на защиту выходного сигнала от насыщений за счет ухудшения скорости регулирования.

Основной задачей изобретения является повышение качества регулирования.

Технический результат - расширение границы устойчивости и функциональных возможностей регулятора.

Указанный технический результат достигается пропорционально-интегрально-дифференциальным регулятором, включающим, по меньшей мере, два последовательно установленных сумматора отклонений, каждый из которых состоит из последовательно соединенных между собой ограничителя входного сигнала, блока умножения, ограничителя выходного сигнала, и сумматора, при этом ограничитель входного сигнала выполнен с возможностью задания диапазона работы сумматора отклонений, блок умножения выполнен с возможностью вычисления дополнительного управляющего воздействия на исполнительный механизм, ограничитель выходного сигнала выполнен с возможностью предотвращения избыточного выходного сигнала, а сумматор выполнен с возможностью суммирования выходного сигнала сумматора отклонения предыдущего диапазона работы с выходным сигналом от ограничителя выходного сигнала сумматора отклонения рабочего диапазона.

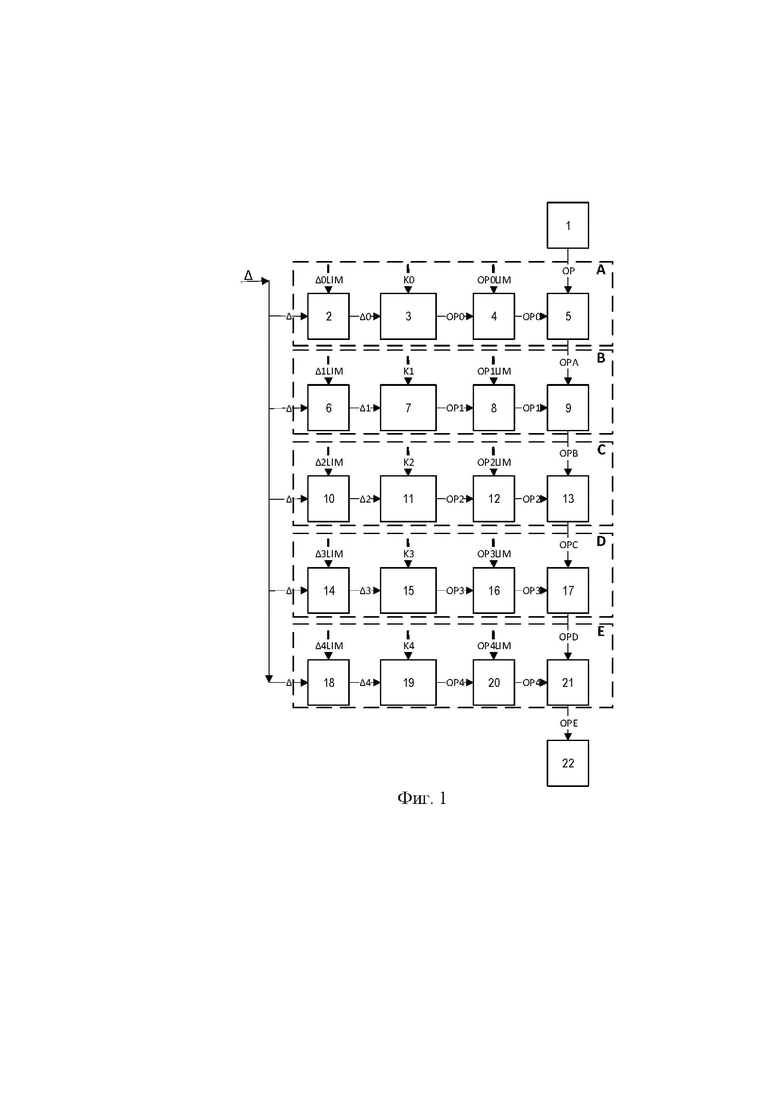

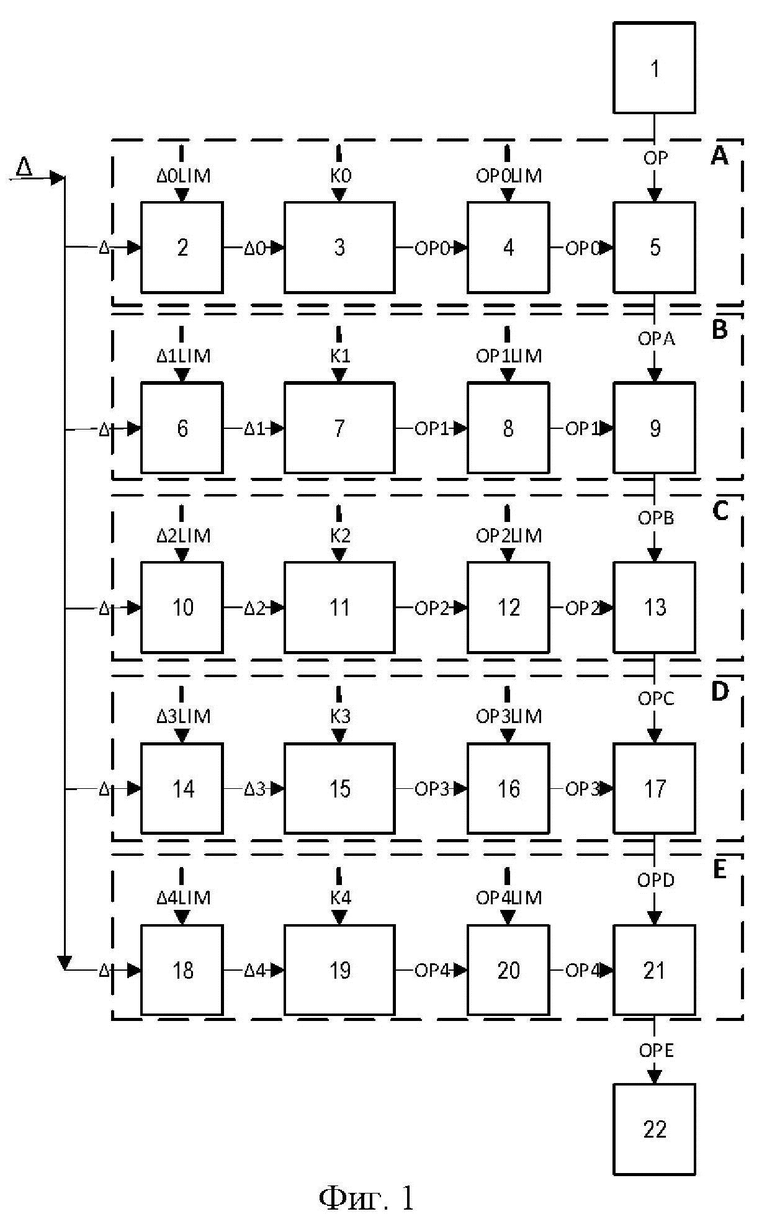

На фиг. 1 показана структурная схема ПИД-регулятора с сумматорами отклонений.

Устройство содержит стандартный ПИД-регулятор 1 и, в зависимости от сложности технологического процесса, последовательно установленные сумматоры отклонений А, В, С, D, Е, при этом для осуществления изобретения их может быть установлено по меньшей мере два. Каждый из сумматоров отклонений А, В, С, D, Е состоит из последовательно соединенных между собой ограничителя входного сигнала 2, 6, 10, 14, 18 соответственно, с помощью которого задается диапазон работы сумматора отклонения, блока умножения 3, 7, 11, 15, 19 соответственно, с помощью которого производится вычисление управляющего воздействия, ограничителя выходного сигнала 4, 8, 12, 16, 20 соответственно, предназначенного для предотвращения избыточного выходного сигнала, и сумматора 5, 9, 13, 17, 21 соответственно, с помощью которого осуществляется суммирование выходного сигнала предыдущего сумматора с выходным сигналом из ограничителя выходного сигнала сумматора отклонения рабочего диапазона. Сумматор отклонения A является нулевым сумматором и предназначен для упреждающего воздействия на регулирующий орган при изменении знака рассогласования Δ. Сумматор отклонения В является сумматором минимального отклонения и предназначен для работы в диапазоне минимальных отклонений. Сумматор отклонения С работает в диапазоне средних отклонений, сумматор отклонения D - в диапазоне высоких отклонений, а сумматор отклонения Е - в диапазоне критических отклонений.

Устройство работает следующим образом.

В ПИД-регулятор 1 поступил сигнал отклонения. Согласно закону регулирования вырабатывается сигнал ОР, который поступает в сумматор отклонения А, работающий при минимальном отклонении Δ, которое задается в ограничителе входного сигнала 2 параметром Δ0LIM. Если сигнал рассогласования Δ превышает задание диапазона Δ0LIM (ограничитель входного сигнала 2), то формируется сигнал Δ0 равный разности /Δ/ и Δ0LIM.

При изменении знака отклонения происходит формирование сигнала управления OP0 в блоке умножения 3 по формуле:

,

,

где K0 - коэффициент усиления сигнала.

Далее сигнал управления OP0 поступает в ограничитель выходного сигнала 4. Ограничение выходного воздействия задается параметром OP0LIM.

Сформированный сигнал OP0 из ограничителя выходного сигнала 4 поступает на вход сумматора 5, в котором происходит суммирование управляющих воздействий OP (выходной сигнал от ПИД-регулятора 1) и OP0, и формирование на выходе сигнала OPA.

При дальнейшем увеличении сигнала рассогласования Δ в работу вступает сумматор отклонения B. Если сигнал рассогласования Δ меньше Δ1LIM, то формируется нулевое значение сигнала, то есть OP1=0. Если сигнал рассогласования Δ превышает задание диапазона Δ1LIM (ограничитель входного сигнала 6), то формируется сигнал Δ1 равный разности /Δ/ и Δ1LIM. Далее в блоке умножения 7 происходит вычисление управляющего воздействия OP1 по формуле:

,

,

где K1 - коэффициент усиления сигнала.

Для исключения избыточного воздействия на регулирующий орган применяется ограничитель выходного сигнала 8, ограничение выходного воздействия задается параметром OP1LIM.

Сформированный сигнал OP1 из ограничителя выходного сигнала 8 поступает на вход сумматора 9, в котором происходит суммирование управляющих воздействий OPA и OP1, и формирование на выходе сигнала OPB.

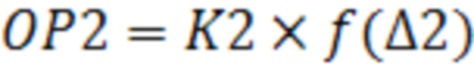

При дальнейшем увеличении сигнала рассогласования Δ в работу вступает сумматор C. Если сигнал рассогласования Δ меньше Δ2LIM, то формируется нулевое значение сигнала, то есть OP2=0. Если сигнал рассогласования Δ превышает задание диапазона Δ2LIM (ограничитель выходного сигнала 10), то формируется сигнал Δ2 равный разности /Δ/ и Δ2LIM. Далее в блоке умножения 11 происходит вычисление управляющего воздействия OP2 по формуле:

,

,

где K2 - коэффициент усиления сигнала.

Для исключения избыточного воздействия на регулирующий орган применяется ограничитель выходного сигнала 12, ограничение выходного воздействия задается параметром OP2LIM.

Сформированный сигнал OP2 из ограничителя выходного сигнала 12 поступает на вход сумматора 13, в котором происходит суммирование управляющих воздействий OPB и OP2, и формирование на выходе сигнала OPC.

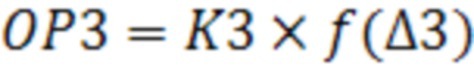

При дальнейшем увеличении сигнала рассогласования Δ в работу вступает сумматор отклонения D. Если сигнал рассогласования Δ меньше Δ3LIM, то формируется нулевое значение сигнала, то есть OP3=0. Если сигнал рассогласования Δ превышает задание диапазона Δ3LIM (ограничитель входного сигнала 14), то формируется сигнал Δ3, равный разности /Δ/ и Δ3LIM. Далее в блоке умножения 15 происходит вычисление управляющего воздействия OP3 по формуле:

,

,

где K3 - коэффициент усиления сигнала.

Для исключения избыточного воздействия на регулирующий орган применяется ограничитель выходного сигнала 16, ограничение выходного воздействия задается параметром OP3LIM.

Сформированный сигнал OP3 из ограничителя входного сигнала 16 поступает на вход сумматора 17, в котором происходит суммирование управляющих воздействий OPC и OP3, и формирование на выходе сигнала OPD.

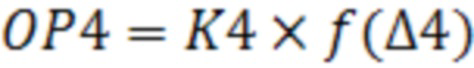

При дальнейшем увеличении сигнала рассогласования Δ в работу вступает сумматор отклонения E. Если сигнал рассогласования Δ меньше Δ4LIM, то формируется нулевое значение сигнала, то есть OP4=0. Если сигнал рассогласования Δ превышает задание диапазона Δ4LIM (ограничитель входного сигнала 18), то формируется сигнал Δ4 равный разности /Δ/ и Δ4LIM. Далее в блоке умножения 19 происходит вычисление управляющего воздействия OP4 по формуле:

,

,

где K4 - коэффициент усиления сигнала.

Для исключения избыточного воздействия на регулирующий орган применяется ограничитель выходного сигнала 20, ограничение выходного воздействия задается параметром OP4LIM.

Сформированный сигнал OP4 из ограничителя выходного сигнала 20 поступает на вход сумматора 21, в котором происходит суммирование управляющих воздействий OPD и OP4, и формирование на выходе сигнала OPE.

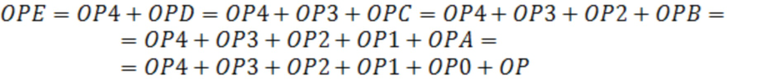

Общий управляющий сигнал OPE от сумматоров отклонений А, В, С, D, Е и от ПИД-регулятора направляется на исполнительный механизм 22 и рассчитывается по следующей формуле:

Предлагаемый ПИД-регулятор с сумматорами отклонений возможно выполнить на элементах цифровой и микропроцессорной техники.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР | 2002 |

|

RU2234116C1 |

| УСИЛИТЕЛЬ И УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ | 2012 |

|

RU2553086C1 |

| Самонастраивающаяся система комбинированного регулирования | 1986 |

|

SU1386957A1 |

| Самонастраивающаяся система комбинированного регулирования | 1987 |

|

SU1509828A1 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ | 2013 |

|

RU2541848C1 |

| Самонастраивающаяся система комбинированного регулирования | 1986 |

|

SU1388826A2 |

| Система автоматического управления процессом получения сернистого газа в производстве серной кислоты | 1989 |

|

SU1641770A1 |

| СПОСОБ ВЫРАБОТКИ УПРАВЛЯЮЩЕГО ВОЗДЕЙСТВИЯ ДЛЯ ПРОМЫШЛЕННОГО ОБЪЕКТА УПРАВЛЕНИЯ | 2011 |

|

RU2450303C1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА КОМБИНИРОВАННОГО РЕГУЛИРОВАНИЯ | 1989 |

|

RU2022313C1 |

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1988 |

|

SU1649501A1 |

Изобретение относится к автоматическим регуляторам, реализующим пропорционально-интегрально-дифференциальный закон регулирования, и может быть использовано для регулирования любых технологических объектов, имеющих дрейф параметров и подверженных неконтролируемым возмущениям. ПИД-регулятор включает по меньшей мере два последовательно установленных сумматора отклонений, каждый из которых состоит из последовательно соединенных между собой ограничителя входного сигнала, блока умножения, ограничителя выходного сигнала и сумматора, при этом ограничитель входного сигнала выполнен с возможностью задания диапазона работы сумматора отклонений, блок умножения выполнен с возможностью вычисления дополнительного управляющего воздействия на исполнительный механизм, ограничитель выходного сигнала выполнен с возможностью предотвращения избыточного выходного сигнала, а сумматор выполнен с возможностью суммирования выходного сигнала сумматора отклонения предыдущего диапазона работы с выходным сигналом от ограничителя выходного сигнала сумматора отклонения рабочего диапазона. Технический результат - расширение границы устойчивости и функциональных возможностей регулятора. 1 ил.

Пропорционально-интегрально-дифференциальный регулятор, включающий по меньшей мере два последовательно установленных сумматора отклонений, каждый из которых состоит из последовательно соединенных между собой ограничителя входного сигнала, блока умножения, ограничителя выходного сигнала и сумматора, при этом ограничитель входного сигнала выполнен с возможностью задания диапазона работы сумматора отклонений, блок умножения выполнен с возможностью вычисления дополнительного управляющего воздействия на исполнительный механизм, ограничитель выходного сигнала выполнен с возможностью предотвращения избыточного выходного сигнала, а сумматор выполнен с возможностью суммирования выходного сигнала сумматора отклонения предыдущего диапазона работы с выходным сигналом от ограничителя выходного сигнала сумматора отклонения рабочего диапазона.

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР С ОГРАНИЧЕНИЯМИ ВЫХОДНЫХ СИГНАЛОВ | 1999 |

|

RU2156992C1 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР | 2002 |

|

RU2234116C1 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНЫЙ РЕГУЛЯТОР С ОГРАНИЧЕНИЯМИ ВЫХОДНЫХ СИГНАЛОВ | 1998 |

|

RU2120655C1 |

| CN 102043380 A, 04.05.2011 | |||

| JP 2008181378 A, 07.08.2008. | |||

Авторы

Даты

2023-01-24—Публикация

2022-06-02—Подача