Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

Известны схемы двухтактных выходных каскадов усилителей мощности на комплементарных выходных транзисторах, которые являются базовым функциональным узлом современной аналоговой микросхемотехники [1-24].

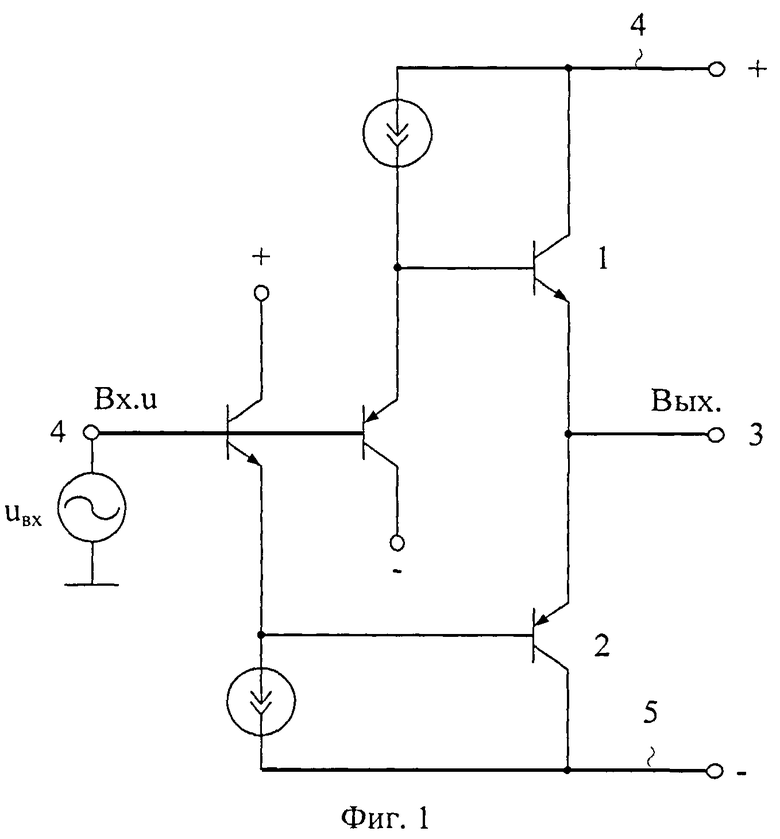

Ближайшим прототипом заявляемого устройства является выходной каскад (ВК) усилителя мощности фиг.1, представленный в патенте US №7.411.455. Он содержит первый 1 и второй 2 выходные транзисторы разного типа проводимости, эмиттеры которых связаны с выходом устройства 3, первую 4 шину питания, связанную с коллектором первого 1 выходного транзистора, вторую 5 шину источника питания, соединенную с коллектором второго 2 выходного транзистора, вход устройства 4.

Существенный недостаток выходного каскада-прототипа состоит в том, что он не обеспечивает высокое входное сопротивление, а также имеет коэффициент усиления по току Ki, зависящий от численных значений β=50÷100 транзисторов.

Основная задача предлагаемого изобретения состоит в повышении на несколько порядков входного сопротивления ВК и его коэффициента усиления по току при достаточно высоком уровне стабильности сквозного тока выходных транзисторов.

Поставленная задача достигается тем, что в выходном каскаде усилителя мощности на основе комплементарных транзисторов, содержащем первый 1 и второй 2 выходные транзисторы разного типа проводимости, эмиттеры которых связаны с выходом устройства 3, первую 4 шину питания, связанную с коллектором первого 1 выходного транзистора, вторую 5 шину источника питания, соединенную с коллектором второго 2 выходного транзистора, вход устройства 4, предусмотрены новые элементы и связи вход устройства 4 соединен с затворами первого 6 и второго 7 входных транзисторов с управляющим р-n-переходом, стоки которых подключены ко второй 5 шине источника питания, база первого 1 выходного транзистора соединена с истоком первого 6 входного транзистора и стоком первого 8 вспомогательного транзистора, затвор которого подключен к первой 4 шине источника питания, а исток связан с первой 4 шиной источника питания, база второго 2 выходного транзистора соединена с истоком второго 7 входного транзистора и стоком второго 9 дополнительного транзистора, затвор которого соединен с первой 4 шиной источника питания, а исток соединен с первой 4 шиной источника питания через первую 10 цепь последовательно-параллельно соединенных р-n-переходов.

Схема усилителя-прототипа показана на фиг.1.

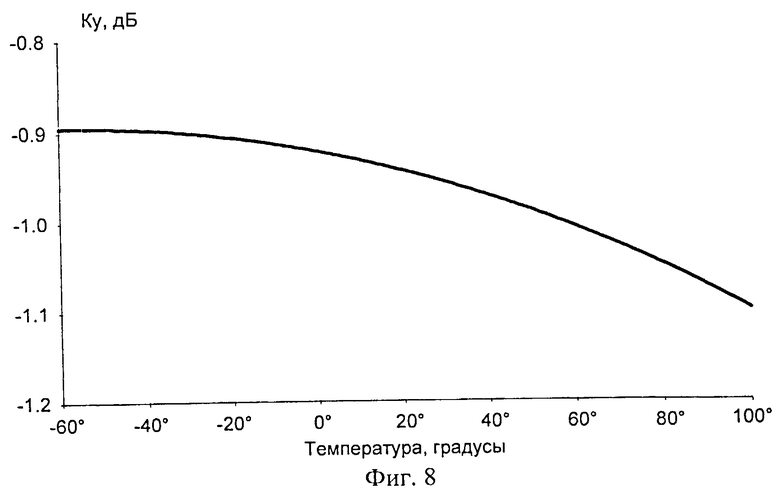

На фиг.2 приведена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

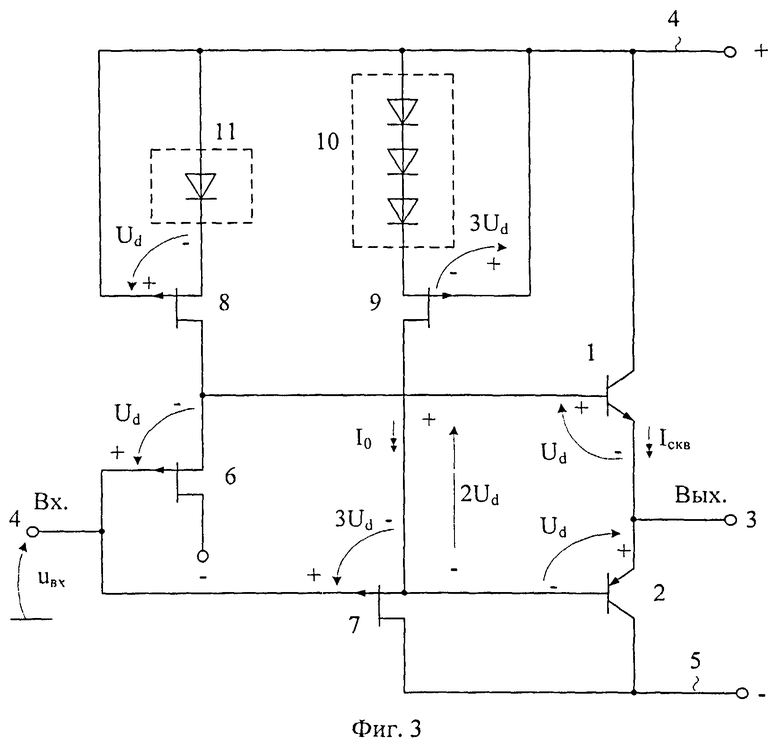

На фиг.3 в соответствии с п.2 формулы изобретения.

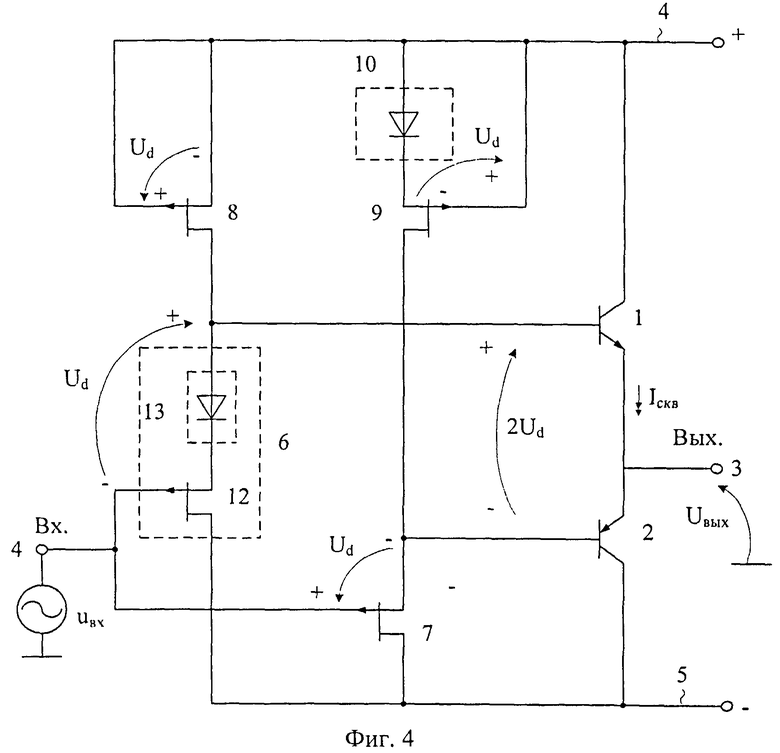

На фиг.4 показана схема в соответствии с п.3 формулы изобретения.

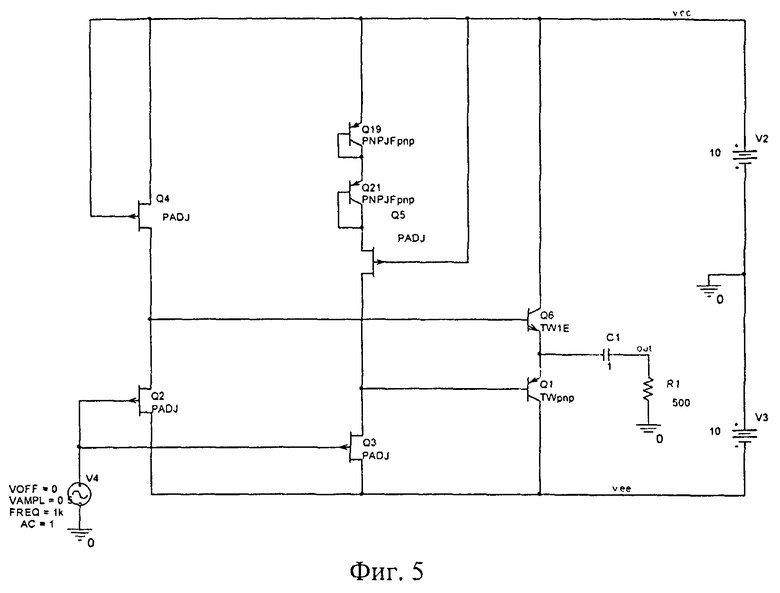

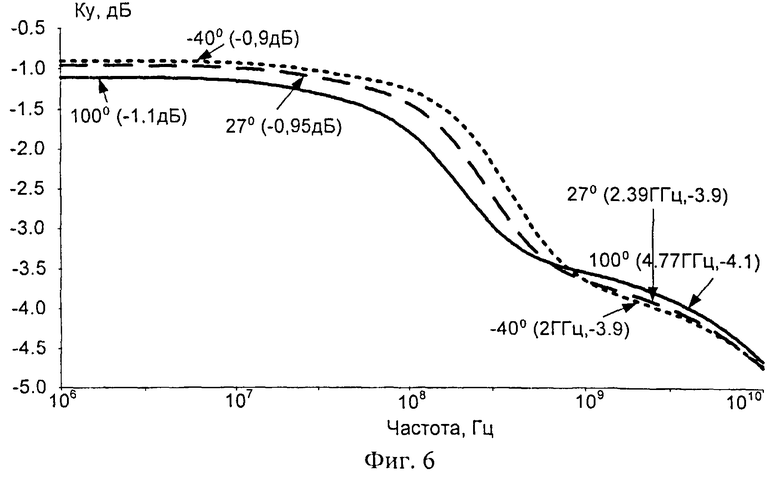

На фиг.5 приведена схема заявляемого устройства (фиг.2) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НИИ «Пульсар», а фиг.6 иллюстрирует зависимость его коэффициента усиления по напряжению, выраженного в децибелах, от частоты при значениях температуры схемы -40°С, 27°С и 100°С.

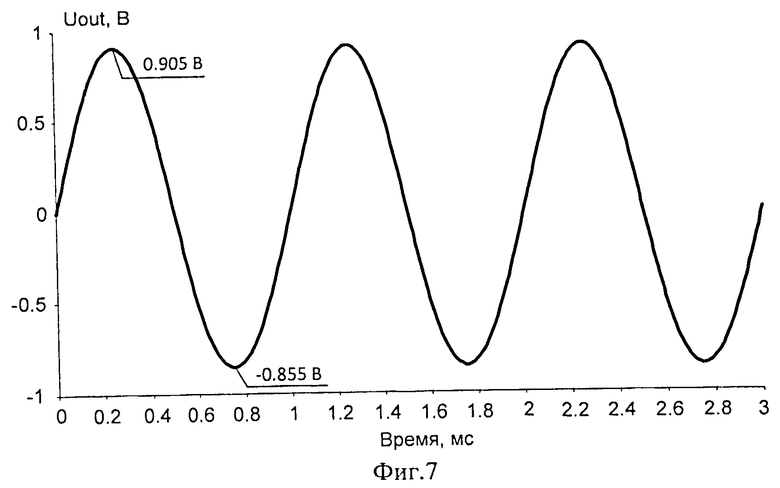

На фиг.7 показана осциллограмма на выходе схемы фиг.5 при подаче на вход сигнала с амплитудой 1 В.

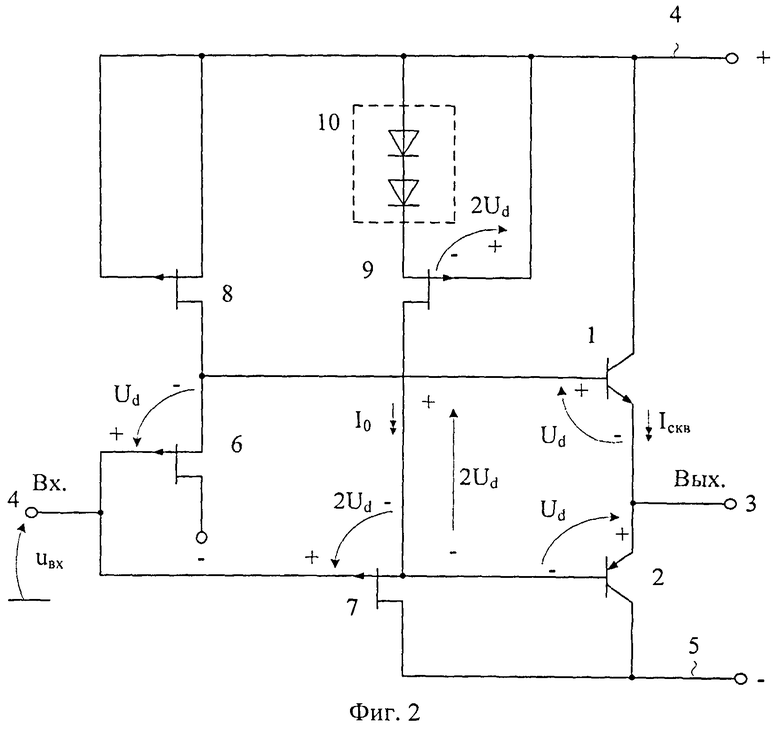

Фиг.8 иллюстрирует зависимость коэффициента усиления по напряжению схемы фиг.5, выраженного в децибелах от температуры.

Выходной каскад усилителя мощности на основе комплементарных транзисторов фиг.2 содержит первый 1 и второй 2 выходные транзисторы разного типа проводимости, эмиттеры которых связаны с выходом устройства 3, первую 4 шину питания, связанную с коллектором первого 1 выходного транзистора, вторую 5 шину источника питания, соединенную с коллектором второго 2 выходного транзистора, вход устройства 4. Вход устройства 4 соединен с затворами первого 6 и второго 7 входных транзисторов с управляющим р-n-переходом, стоки которых подключены ко второй 5 шине источника питания, база первого 1 выходного транзистора соединена с истоком первого 6 входного транзистора и стоком первого 8 вспомогательного транзистора, затвор которого подключен к первой 4 шине источника питания, а исток связан с первой 4 шиной источника питания, база второго 2 выходного транзистора соединена с истоком второго 7 входного транзистора и стоком второго 9 дополнительного транзистора, затвор которого соединен с первой 4 шиной источника питания, а исток соединен с первой 4 шиной источника питания через первую 10 цепь последовательно-параллельно соединенных р-n переходов.

На фиг.3, в соответствии с п.2 формулы изобретения, исток первого 8 вспомогательного транзистора связан с первой 4 шиной источника питания через вторую 11 цепь последовательно-параллельно соединенных р-n-переходов. Структура этой цепи зависит от построения выходных в общем случае составных транзисторов 1 и 2. Если первый 1 и второй 2 выходные транзисторы реализованы на основе одиночных биполярных транзисторов, то вторая 11 цепь последовательно-параллельно соединенных транзисторов, как это показано на фиг.3, может содержать один р-n-переход, а первая 10 цепь последовательно-параллельно соединенных р-n-переходов может включать три диода (фиг.3).

На фиг.4, в соответствии с п.3 формулы изобретения, в качестве первого 6 входного транзистора используется составной полевой транзистор, содержащий основной полевой транзистор 12 с управляющим р-n-переходом, в исток которого включена третья 13 цепь последовательно-параллельно включенных р-n-переходов. В частном случае, при использовании в схеме фиг.4 одиночных биполярных транзисторов 1 и 2 третья 13 цепь последовательно-параллельно включенных р-n-переходов может содержать один диод.

Рассмотрим статический режим ВК фиг.2.

При нулевом входном сигнале и реализации первой 10 цепи последовательно-параллельных р-n-переходов на двух диодах напряжение затвор-исток второго 9 дополнительного и второго 7 входного транзисторов будут одинаковы и равны Uзи.7=Uзи.9=2Ud≈1,4В, а напряжение затвор-исток транзисторов 8 и 6 близко к нулю. Поэтому между базами транзисторов 1 и 2 устанавливается статическое напряжение

Поэтому сквозной ток 1СКВ, протекающий в эмиттерной цепи транзисторов 1 и 2, определяется величиной 10:

При изменении температуры (или уровня радиации) величина Iскв≈const остается постоянной.

За счет изменения числа диодов в первой 10 цепи последовательно-параллельно соединенных р-n-переходов можно устанавливать другие заданные значения напряжения между базами транзисторов 1 и 2, которые могут выполняться в виде составных транзисторов по схеме Дарлингтона или схеме Линна (n-p-n- и p-n-р-транзисторы).

В схеме фиг.3 за счет выбора различных комбинаций числа диодов в первой 10 и второй 11 цепях последовательно-параллельно соединенных р-n-переходов обеспечивается более широкий диапазон напряжений между базами транзисторов 1, 2 и, следовательно, сквозного тока Iскв.

Особенность схемы фиг.4 - близкий к нулю уровень выходного статического напряжения, что обеспечивается введением новых элементов в соответствии с п.3 формулы изобретения.

Входное сопротивление заявленного каскада соответствует входному сопротивлению входных полевых транзисторов 6 и 7 и достигает десятков-сотен мегаом. Эти транзисторы играют в схеме фиг.2 и другую важную роль - обеспечивают заданный разработчиком уровень сквозного тока выходных транзисторов.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №7.411.455, fig.1.

2. DE 102011122077, fig.8.

3. Патент США №6.268.769 fig.3.

4. Патент США №6.420.933.

5. Патент США №5.223.122.

6. Патентная заявка США №2004/0196101.

7. Патентная заявка США №2005/0264358 fig.1.

8. Патентная заявка США №2002/0175759.

9. Патент США №5.049.653 fig.8.

10.Патент США №4.837.523.

11.Патент США №5.179.355.

12.Патент Японии JP 10.163.763.

13.Патент Японии JP 10.270.954.

14.Патент США№5.170.134 fig.6

15.Патент США №4.540.950.

16.Патент США №4.424.493.

17.Патент Японии JP 6310950.

18.Патент США №5.378.938.

19.Патент США №4.827.223.

20.Патент США №6.160.451.

21.Патент США №4.639.685.

22.А.СВ. СССР 1506512.

23.Патент США №5.399.991.

24.Патент США №6.542.032.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАССИВНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2012 |

|

RU2517699C1 |

| ГИБРИДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2519373C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615066C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| ВЫХОДНОЙ КАСКАД BIJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668981C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

Изобретение относится к области радиотехники и связи, а именно к устройствам усиления мощности. Технический результат: повышение на несколько порядков входного сопротивления ВК и его коэффициента усиления по току при достаточно высоком уровне стабильности сквозного тока выходных транзисторов. Устройство содержит: первый (1) и второй (2) выходные транзисторы разного типа проводимости, эмиттеры которых связаны с выходом устройства (3), первую (4) шину питания, связанную с коллектором первого (1) выходного транзистора, вторую (5) шину источника питания, соединенную с коллектором второго (2) выходного транзистора, вход устройства (4) соединен с затворами первого (6) и второго (7) входных транзисторов с управляющим р-n-переходом, стоки которых подключены ко второй (5) шине источника питания, база первого (1) выходного транзистора соединена с истоком первого (6) входного транзистора и стоком первого (8) вспомогательного транзистора, затвор которого подключен к первой (4) шине источника питания, а исток связан с первой (4) шиной источника питания, база второго (2) выходного транзистора соединена с истоком второго (7) входного транзистора и стоком второго (9) дополнительного транзистора, затвор которого соединен с первой (4) шиной источника питания, а исток соединен с первой (4) шиной источника питания через первую (10) цепь последовательно-параллельно соединенных р-n-переходов. 2 з.п. ф-лы, 8 ил.

1. Выходной каскад усилителя мощности на основе комплементарных транзисторов, содержащий первый (1) и второй (2) выходные транзисторы разного типа проводимости, эмиттеры которых связаны с выходом устройства (3), первую (4) шину питания, связанную с коллектором первого (1) выходного транзистора, вторую (5) шину источника питания, соединенную с коллектором второго (2) выходного транзистора, вход устройства (4), отличающийся тем, что вход устройства (4) соединен с затворами первого (6) и второго (7) входных транзисторов с управляющим р-n-переходом, стоки которых подключены ко второй (5) шине источника питания, база первого (1) выходного транзистора соединена с истоком первого (6) входного транзистора и стоком первого (8) вспомогательного транзистора, затвор которого подключен к первой (4) шине источника питания, а исток связан с первой (4) шиной источника питания, база второго (2) выходного транзистора соединена с истоком второго (7) входного транзистора и стоком второго (9) дополнительного транзистора, затвор которого соединен с первой (4) шиной источника питания, а исток соединен с первой (4) шиной источника питания через первую (10) цепь последовательно-параллельно соединенных р-n-переходов.

2. Выходной каскад усилителя мощности на основе комплементарных транзисторов по п.1, отличающийся тем, что исток первого (8) вспомогательного транзистора связан с первой (4) шиной источника питания через вторую (11) цепь последовательно-параллельно соединенных р-n переходов.

3. Выходной каскад усилителя мощности на основе комплементарных транзисторов по п.1, отличающийся тем, что в качестве первого (6) входного транзистора используется составной полевой транзистор, содержащий основной полевой транзистор (12), в исток которого включена третья (13) цепь последовательно-параллельно включенных р-n-переходов.

| US 7411455 B2, 12.08.2008 | |||

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384937C1 |

| ЗУБОПРОТЕЗНАЯ КЮВЕТА | 1932 |

|

SU36590A1 |

Авторы

Даты

2014-07-27—Публикация

2013-01-11—Подача