Предполагаемое изобретение относится к области радиотехники и может использоваться в качестве базового функционального узла (операционного усилителя) многих устройств автоматики, вычислительной техники, систем связи и приборостроения.

В современной микроэлектронике широкое распространение получили операционные усилители с входным дифференциальным каскадом на полевых (или биполярных) транзисторах и промежуточным каскадом, выполненным на основе биполярных транзисторов с их включением по схеме так называемого «перегнутого» каскода [1-21]. Данная архитектура является основой многих серийных операционных усилителей российских и зарубежных фирм.

В практических схемах ОУ входная дифференциальная пара реализуются как на полевых, так и на биполярных транзисторах, что определяется используемыми технологическими процессами. Однако, перспективный арсенид-галлиевый техпроцесс [22], осваиваемый Минским НИИ радиоматериалов (https://mniirm.by/), обеспечивает создание только p-n-p и nJFet транзисторов. Отсутствие n-p-n транзисторов создает схемотехнические проблемы построения GaAs двухкаскадных ОУ с простейшей архитектурой. Кроме этого, данная простейшая архитектура ОУ имеет повышенный уровень систематической составляющей напряжения смещения нуля (Uсм). Это не позволяет создать высокотемпературные GaAs ОУ, востребованные в ряде важных отраслей науки и техники - космическом приборостроении, нефтегазовой, автомобильной и авиационной промышленности.

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в патенте US 6.144.234, 2000, fig.9. Он содержит первый 1 и второй 2 входы устройства, а также выход 3 устройства, входной дифференциальный каскад 4 на полевых транзисторах с первым 5 и вторым 6 токовыми выходами, согласованными с первой 7 шиной источника питания, общая истоковая цепь 8 входного дифференциального каскада 4 соединена со второй 9 шиной источника питания через первый 10 источник опорного тока, первый 5 токовый выход дифференциального каскада 4 соединен с эмиттером первого 11 выходного биполярного p-n-p транзистора, второй 6 токовый выход входного дифференциального каскада 4 соединен с эмиттером второго 12 выходного биполярного p-n-p транзистора, коллектор первого 11 выходного биполярного p-n-p транзистора связан со входом буферного усилителя 13 и через второй 14 источник опорного тока подключен ко второй 9 шине источника питания, причем выход буферного усилителя 13 является выходом 3 устройства, базы первого 11 и второго 12 выходных биполярных p-n-p транзисторов объединены и подключены к цепи смещения потенциалов 15, первый 16 и второй 17 вспомогательные резисторы.

Существенный недостаток ОУ – прототипа состоит в том, что он не реализуется в рамках арсенид-галлиевого технологического процесса, осваиваемого Минским НИИ радиоматериалов в интересах Союзного государства, из-за отсутствия n-p-n биполярных арсенид-галлиевых транзисторов, без которых невозможна реализация n-p-n токовых зеркал, которые в традиционных схемах ОУ используются в качестве управляемого источника опорного тока 14.

Основная задача предполагаемого изобретения состоит в создании схемы операционного усилителя, которая реализуется в рамках совмещенного GaAs технологического процесса, позволяющего создавать только p-n-p биполярные и nJFet полевые транзисторы. Дополнительная задача – создание схемы ОУ с малым уровнем систематической составляющей напряжения смещения нуля без применения токовых зеркал на n-p-n или nJFet транзисторах.

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, а также выход 3 устройства, входной дифференциальный каскад 4 на полевых транзисторах с первым 5 и вторым 6 токовыми выходами, согласованными с первой 7 шиной источника питания, общая истоковая цепь 8 входного дифференциального каскада 4 соединена со второй 9 шиной источника питания через первый 10 источник опорного тока, первый 5 токовый выход дифференциального каскада 4 соединен с эмиттером первого 11 выходного биполярного p-n-p транзистора, второй 6 токовый выход входного дифференциального каскада 4 соединен с эмиттером второго 12 выходного биполярного p-n-p транзистора, коллектор первого 11 выходного биполярного p-n-p транзистора связан со входом буферного усилителя 13 и через второй 14 источник опорного тока подключен ко второй 9 шине источника питания, причем выход буферного усилителя 13 является выходом 3 устройства, базы первого 11 и второго 12 выходных биполярных p-n-p транзисторов объединены и подключены к цепи смещения потенциалов 15, первый 16 и второй 17 вспомогательные резисторы, предусмотрены новые элементы и связи - коллектор второго 12 выходного биполярного p-n-p транзистора соединен с эмиттером дополнительного биполярного транзистора 18, база которого подключена ко входу буферного усилителя 13, а коллектор соединен со второй 9 шиной источника питания, первый 10 источник опорного тока выполнен в виде двух идентичных и параллельно-включенных первого 19 и второго 20 элементарных источников опорного тока, каждый из которых выполнен на первом 21 дополнительном полевом транзисторе, затвор которого подключен ко второй 9 шине источника питания, а исток связан со второй 9 шиной источника питания через первый 22 дополнительный резистор, второй 14 источник опорного тока идентичен первому 19 и второму 20 элементарным источникам опорного тока, эмиттер первого 11 выходного биполярного p-n-p транзистора соединен с затвором второго 23 дополнительного полевого транзистора, сток которого соединен с первой 7 шиной источника питания, а исток подключен к эмиттеру первого 11 биполярного p-n-p транзистора через второй 17 вспомогательный резистор, эмиттер второго 12 выходного биполярного p-n-p транзистора соединен с затвором третьего 24 дополнительного полевого транзистора, сток которого подключен к первой 7 шине источника питания, а исток соединен с эмиттером второго 12 выходного биполярного p-n-p транзистора через первый 16 вспомогательный резистор, кроме этого, эмиттер второго 12 выходного биполярного p-n-p транзистора соединен с затвором четвертого 25 дополнительного полевого транзистора и через третий 26 вспомогательный резистор подключен к эмиттеру второго 12 выходного биполярного p-n-p транзистора, эмиттер первого 11 выходного биполярного p-n-p транзистора соединен с затвором пятого 27 дополнительного полевого транзистора, сток которого подключен к первой 7 шине источника питания, а исток соединен с эмиттером первого 11 выходного биполярного p-n-p транзистора через четвертый 28 вспомогательный резистор.

На чертеже фиг. 1 показана схема операционного усилителя – прототипа.

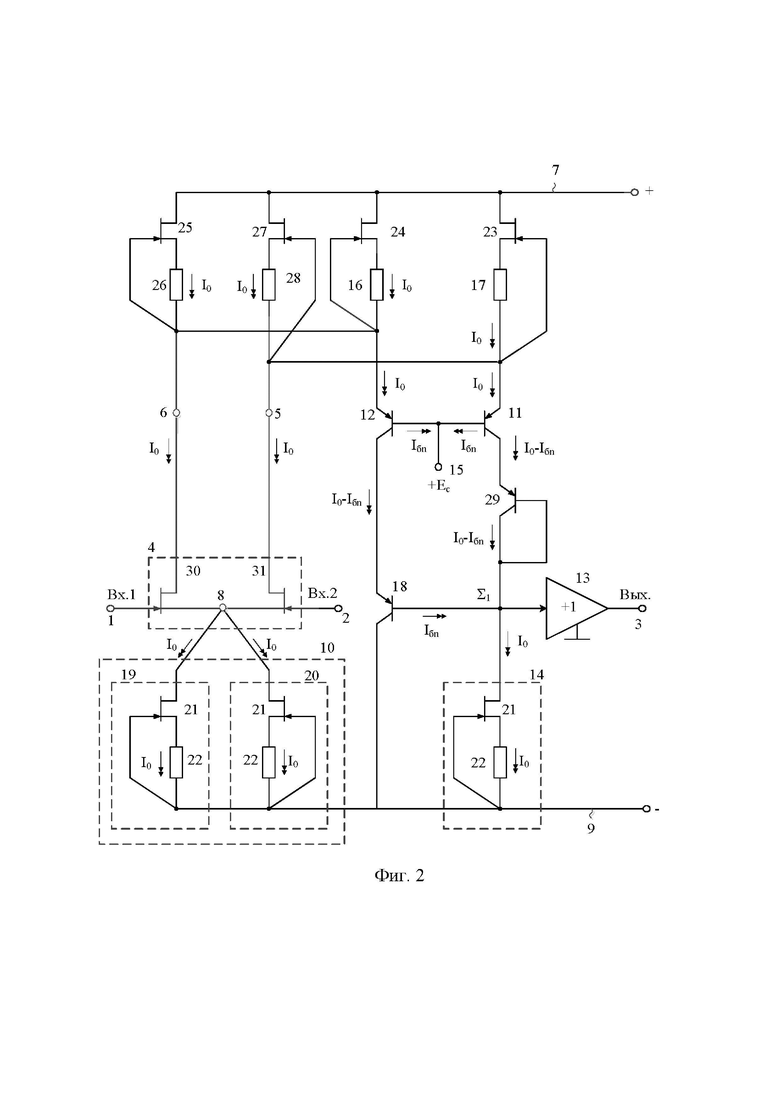

На чертеже фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

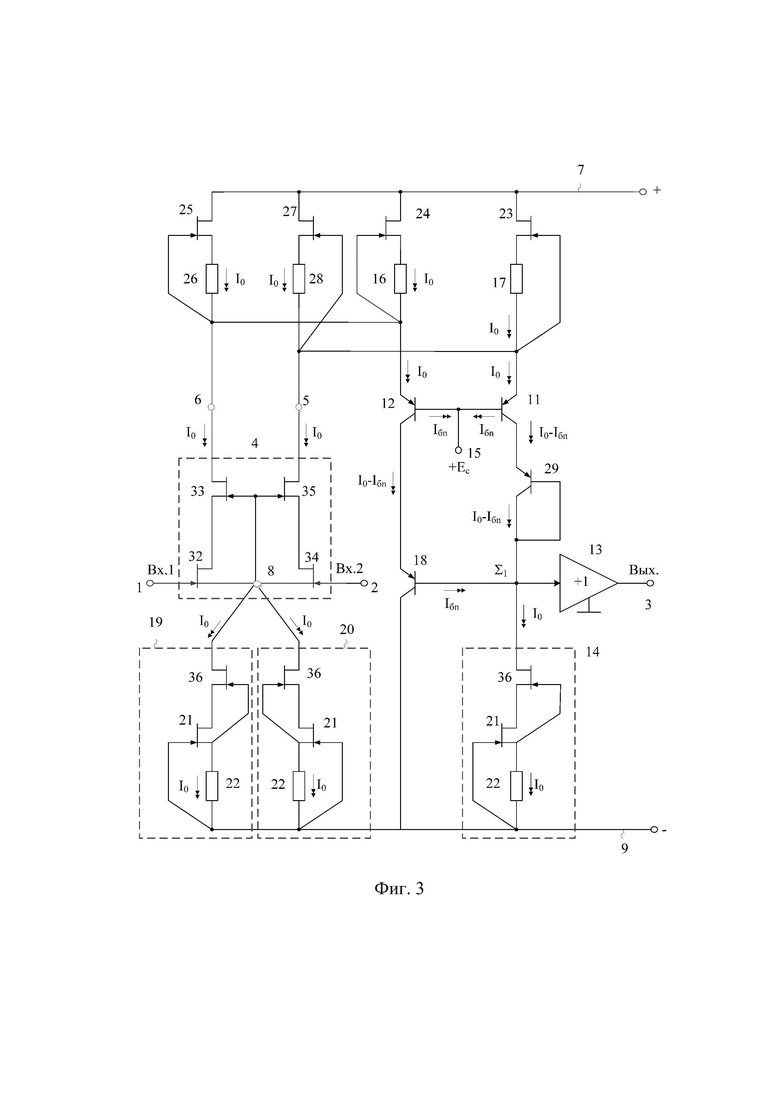

На чертеже фиг. 3 приведена схема заявляемого устройства в соответствии с п. 2 формулы изобретения.

На чертеже фиг. 4 показан статический режим ОУ фиг. 3 при работе транзисторов в режиме микротоков (I=80,2 мкА) при R1÷R7 = 17.15 кОм, C1 = 10 пФ, V4 = 6.6 В, vcc= +10 В, vee = -10 В.

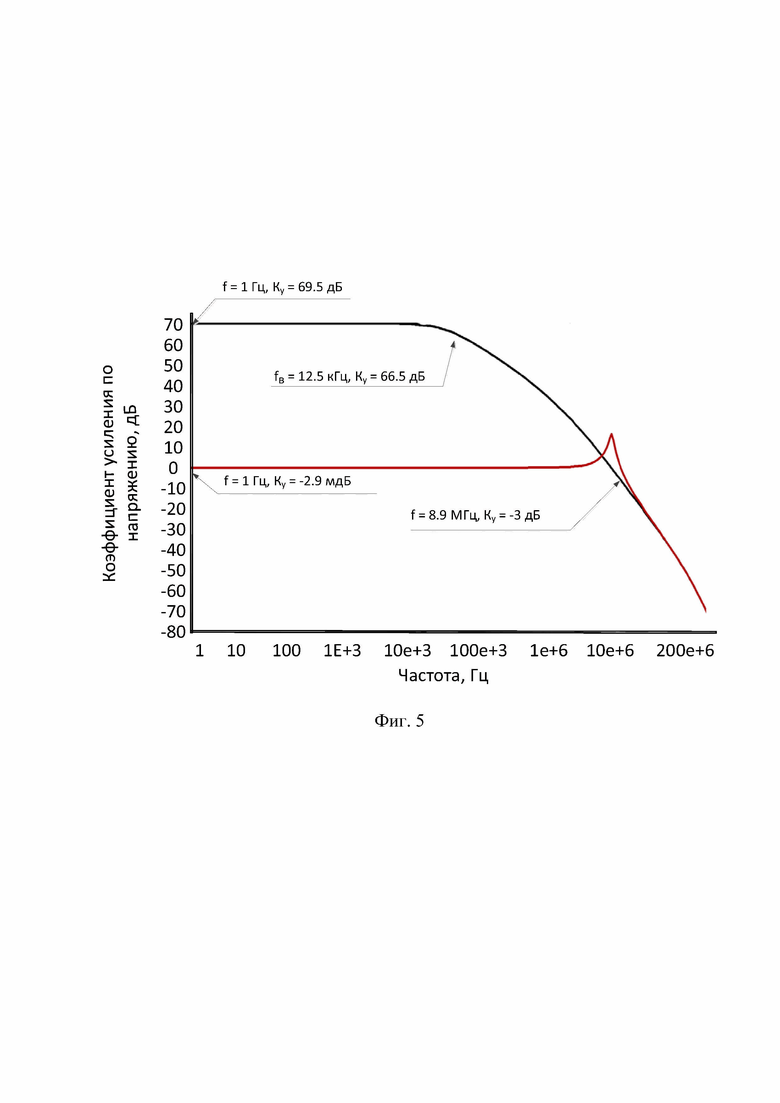

На чертеже фиг. 5 представлена амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ фиг. 3.

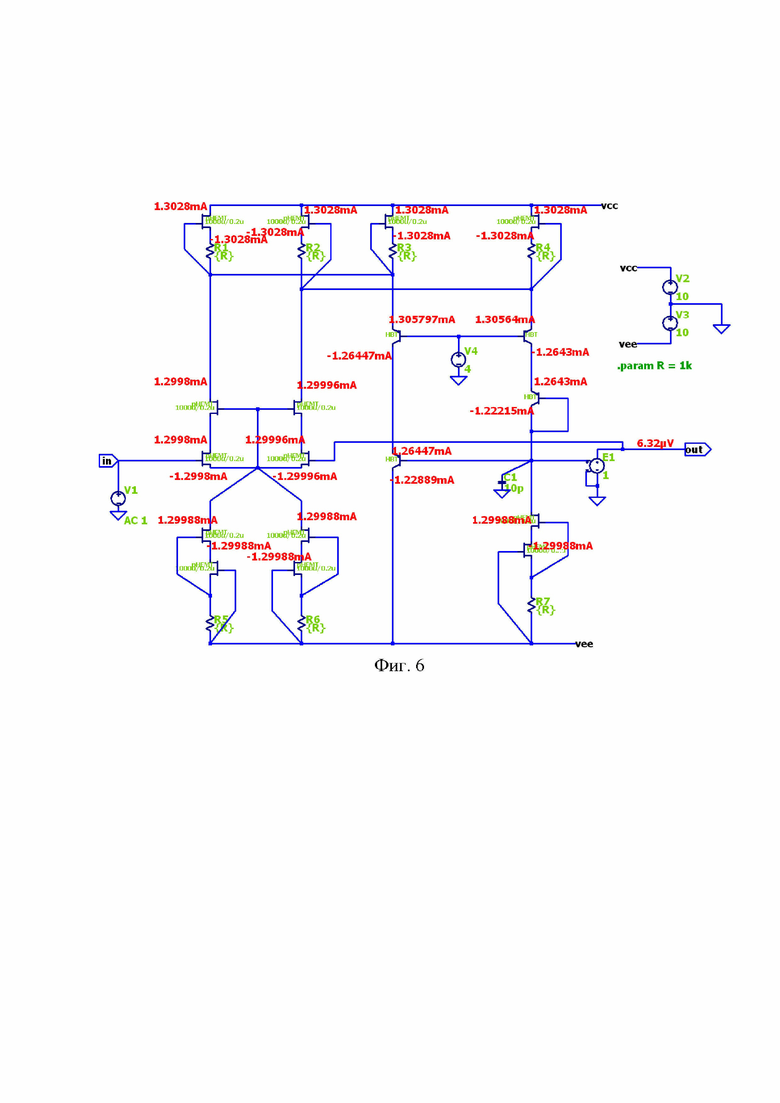

На чертеже фиг. 6 показан статический режим ОУ фиг. 3 при работе транзисторов в режиме миллиамперных токов (I=1,2 мА) при R1÷R7 = 1 кОм, C1 = 10 пФ, V4 = 4 В, vcc= +10 В, vee = -10 В.

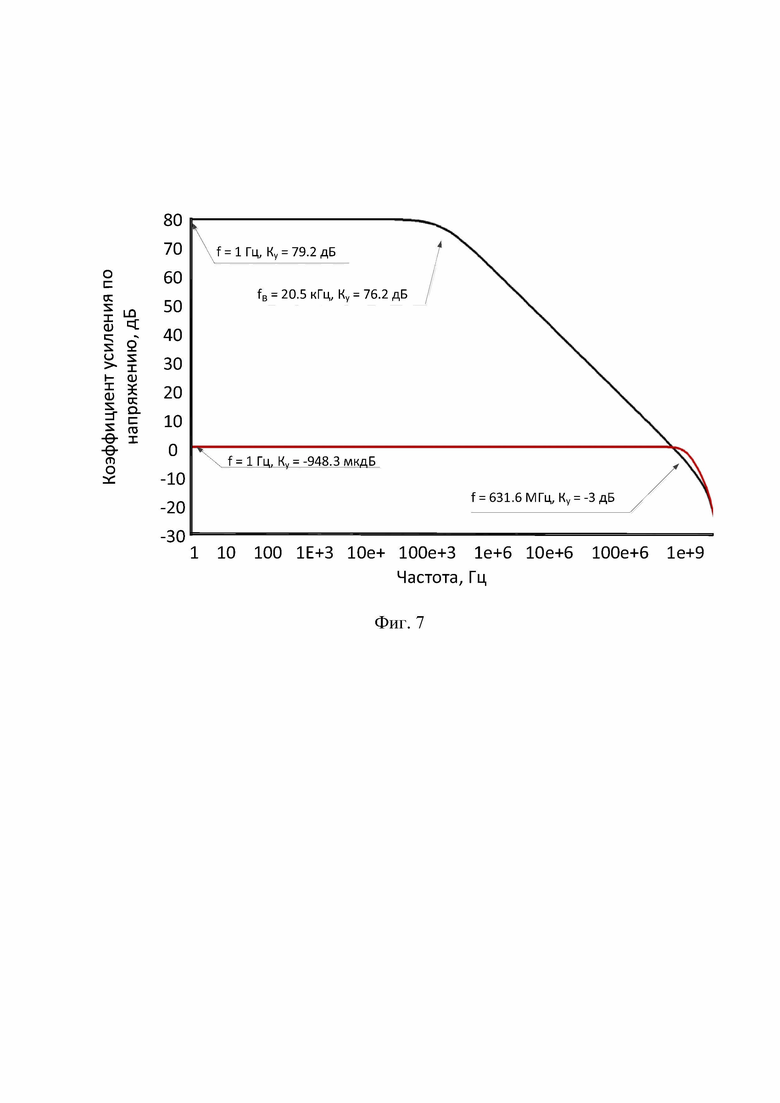

На чертеже фиг. 7 приведена амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ фиг. 6.

Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля фиг. 2 содержит первый 1 и второй 2 входы устройства, а также выход 3 устройства, входной дифференциальный каскад 4 на полевых транзисторах с первым 5 и вторым 6 токовыми выходами, согласованными с первой 7 шиной источника питания, общая истоковая цепь 8 входного дифференциального каскада 4 соединена со второй 9 шиной источника питания через первый 10 источник опорного тока, первый 5 токовый выход дифференциального каскада 4 соединен с эмиттером первого 11 выходного биполярного p-n-p транзистора, второй 6 токовый выход входного дифференциального каскада 4 соединен с эмиттером второго 12 выходного биполярного p-n-p транзистора, коллектор первого 11 выходного биполярного p-n-p транзистора связан со входом буферного усилителя 13 и через второй 14 источник опорного тока подключен ко второй 9 шине источника питания, причем выход буферного усилителя 13 является выходом 3 устройства, базы первого 11 и второго 12 выходных биполярных p-n-p транзисторов объединены и подключены к цепи смещения потенциалов 15, первый 16 и второй 17 вспомогательные резисторы, отличающийся тем, что коллектор второго 12 выходного биполярного p-n-p транзистора соединен с эмиттером дополнительного биполярного транзистора 18, база которого подключена ко входу буферного усилителя 13, а коллектор соединен со второй 9 шиной источника питания, первый 10 источник опорного тока выполнен в виде двух идентичных и параллельно-включенных первого 19 и второго 20 элементарных источников опорного тока, каждый из которых выполнен на первом 21 дополнительном полевом транзисторе, затвор которого подключен ко второй 9 шине источника питания, а исток связан со второй 9 шиной источника питания через первый 22 дополнительный резистор, второй 14 источник опорного тока идентичен первому 19 и второму 20 элементарным источникам опорного тока, эмиттер первого 11 выходного биполярного p-n-p транзистора соединен с затвором второго 23 дополнительного полевого транзистора, сток которого соединен с первой 7 шиной источника питания, а исток подключен к эмиттеру первого 11 биполярного p-n-p транзистора через второй 17 вспомогательный резистор, эмиттер второго 12 выходного биполярного p-n-p транзистора соединен с затвором третьего 24 дополнительного полевого транзистора, сток которого подключен к первой 7 шине источника питания, а исток соединен с эмиттером второго 12 выходного биполярного p-n-p транзистора через первый 16 вспомогательный резистор, кроме этого, эмиттер второго 12 выходного биполярного p-n-p транзистора соединен с затвором четвертого 25 дополнительного полевого транзистора и через третий 26 вспомогательный резистор подключен к эмиттеру второго 12 выходного биполярного p-n-p транзистора, эмиттер первого 11 выходного биполярного p-n-p транзистора соединен с затвором пятого 27 дополнительного полевого транзистора, сток которого подключен к первой 7 шине источника питания, а исток соединен с эмиттером первого 11 выходного биполярного p-n-p транзистора через четвертый 28 вспомогательный резистор.

На чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, входной дифференциальный каскад 4 выполнен на входных полевых транзисторах 30 и 31.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, коллектор первого 11 выходного биполярного p-n-p транзистора соединен со входом буферного усилителя 13 через эмиттерно-базовый переход согласующего биполярного транзистора 29.

На чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, в качестве входных полевых транзисторов 30 и 31 входного дифференциального каскада 4 используются каскодные составные транзисторы 32-33 и 34-35, причем первый 19 и второй 20 элементарные источники опорного тока в структуре первого 10 источника опорного тока, а также второй 14 источник опорного тока выполнены на каскодных составных транзисторах и содержат дополнительные выходные полевые транзисторы 36.

На чертежах фиг. 2, фиг. 3, в соответствии с п. 5 формулы изобретения, в качестве полевых транзисторов используются полевые транзисторы с управляющим p-n переходом. В других случаях в качестве этих активных элементов могут использоваться КМОП транзисторы со встроенным каналом.

Рассмотрим работу заявляемого ОУ фиг. 3.

Статический режим операционного усилителя устанавливается первым 19, вторым 20 элементарных источников опорного тока, вторым 14 источником опорного тока, а также токостабилизирующими двухполюсниками на втором 23, третьем 24, четвертом 25, пятом 27 дополнительных полевых транзисторах, выполненных по идентичным схемам на полевых транзисторах с управляющим p-n переходом. На базы первого 11 и второго 12 выходных биполярных p-n-p транзисторов подается статическое напряжение цепи смещения потенциалов 15. Согласующий биполярный транзистор 29 обеспечивает симметрирование статических режимов по напряжению коллектор-база первого 11 и второго 12 выходных биполярных p-n-p транзисторов.

В качестве входных полевых транзисторов 30 и 31 рекомендуется применять их составные каскодные аналоги 32, 33, 34, 35 (фиг. 3). Аналогично, первый 19, второй 20 элементарные источники опорного тока и второй 14 источник опорного тока при повышенных требованиях к ослаблению входного синфазного сигнала рекомендуется выполнять на соответствующих каскодных составных транзисторах 21 и 36.

Данные схемотехнические меры направлены на взаимную компенсацию основных составляющих статических токов в высокоимпедансном узле Σ1 (фиг. 5), для которого можно составить следующее уравнение по первому закону Кирхгофа

где IR – токи в резисторах 28, 17, 26, 16,

Iэ (Iк) – токи эмиттера (коллектора) транзисторов 11, 12,

I0 – параметр источников опорного тока, устанавливаемый разработчиком.

Таким образом, напряжение смещения нуля предлагаемого арсенид-галлиевого ОУ определяется уравнением

где gDK – крутизна усиления входного дифференциального каскада со входов 1, 2 к высокоимпедансному узлу Σ1.

Следовательно, за счет введения новых связей в заявляемом ОУ решается проблема взаимной компенсации составляющих токовой ошибки в высокоимпедансном узле Σ1, что уменьшает Uсм.

Результаты компьютерного моделирования схемы ОУ фиг. 3 представленные на чертеже фиг. 4, показывают, что систематическая составляющая напряжения смещения нуля ОУ имеет малую величину (51,35 мкВ). Аналогичные выводы можно сделать в результате анализа статического режима ОУ на чертеже фиг. 6, в котором сопротивление всех резисторов R1-R7 равняется 1 кОм, а статические токи транзисторов имеют миллиамперные значения. В данной схеме Uсм также мало (6,32 мкВ).

Рассматриваемая схема ОУ имеет разомкнутый коэффициент усиления (фиг. 7), близкий к 80 дБ, что достаточно для многих применений.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом и может использоваться для построения высокотемпературных микросхем на GaAs, а также на других широкозонных полупроводниках (GaN, SiC).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

ОУ с входным каскадом на JFET и перегнутым каскодом на p-n-p биполярных транзисторах

1. Патент US 6144234, fig. 9, 2000 г.

2. Патент US 4406990, fig.4, 1983 г.

ОУ с входным каскадом на JFET и перегнутым каскодом на n-p-n биполярных транзисторах

3. Патент RU 2615070, fig. 1,

ОУ с входными каскадами на КМОП и перегнутым каскодом на p-n-p биполярных транзисторах

4. Патент US 4390850, 1983 г.

5. Патент US 5963085, fig. 3, 1999 г.

6. Патент US 5734296, fig. 3, fig. 4, 1998 г.

ОУ с входными каскадами на КМОП и перегнутым каскодом на n-p-n биполярных транзисторах

7. Патент US 7411451, fig. 5, 2008 г.

8. Патент US 7215200, fig. 6, 2007 г.

9. Патент US 5952882, 1999 г.

Входной каскад на биполярных n-p-n и перегнутым каскодом на p-n-p биполярных транзисторах

10. Патент US 4837523, fig. 1, fig. 4, 1989 г.

11. Патент US 6788143, fig. 2, 2004 г.

12. Патент US 5327100, fig. 2, 1994 г.

13. Патент RU 2193273, fig. 1,

14. Патент US 6529076, 2003 г.

15. Патент US 6236273, fig. 1, 2001 г.

16. Патент 4600893, fig. 7, 1986 г.

Входной на p-n-p, выходной на n-p-n

17. Патент US 6456162, fig. 1, fig.2, fig.3, 2002 г.

18. Патентная заявка US 2002/1096079, 2002 г.

19. Патент US 5422600, fig. 2, 1995 г.

20. Патент US 6542030, fig.1, fig. 2, 2003 г.

Серийные ОУ с входными JFET и перегнутым каскодом на n-p-n биполярных транзисторах

21. OPA42, 140УД30

22. Унифицированные схемотехнические решения аналоговых арсенид-галлиевых микросхем / Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. // Известия вузов. Электроника. 2022. Т. 27. № 4. С. 475–488. DOI: https://doi.org/10.24151/1561-5405-2022-27-4-475-488.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

Изобретение относится к области радиотехники. Технический результат: создание схемы операционного усилителя, которая реализуется в рамках совмещенного GaAs технологического процесса, позволяющего создавать только p-n-p биполярные и nJFet полевые транзисторы, а также разработка схемы ОУ с малым уровнем систематической составляющей напряжения смещения нуля без применения токовых зеркал на n-p-n или nJFet транзисторах. Для этого предложен операционный усилитель, в который введены дополнительный биполярный транзистор (18), первый (19) и второй (20) элементарный источник опорного тока, каждый из которых выполнен на первом (21) дополнительном полевом транзисторе, первый (22) дополнительный резистор, второй (23) дополнительный полевой транзистор, третий (24) дополнительный полевой транзистор, четвертый (25) дополнительный полевой транзистор, третий (26) вспомогательный резистор, пятый (27) дополнительный полевой транзистор, четвертый (28) вспомогательный резистор. 4 з.п. ф-лы, 7 ил.

1. Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля, содержащий первый (1) и второй (2) входы устройства, а также выход (3) устройства, входной дифференциальный каскад (4) на полевых транзисторах с первым (5) и вторым (6) токовыми выходами, согласованными с первой (7) шиной источника питания, общая истоковая цепь (8) входного дифференциального каскада (4) соединена со второй (9) шиной источника питания через первый (10) источник опорного тока, первый (5) токовый выход дифференциального каскада (4) соединен с эмиттером первого (11) выходного биполярного p-n-p транзистора, второй (6) токовый выход входного дифференциального каскада (4) соединен с эмиттером второго (12) выходного биполярного p-n-p транзистора, коллектор первого (11) выходного биполярного p-n-p транзистора связан со входом буферного усилителя (13) и через второй (14) источник опорного тока подключен ко второй (9) шине источника питания, причем выход буферного усилителя (13) является выходом (3) устройства, базы первого (11) и второго (12) выходных биполярных p-n-p транзисторов объединены и подключены к цепи смещения потенциалов (15), первый (16) и второй (17) вспомогательные резисторы, отличающийся тем, что коллектор второго (12) выходного биполярного p-n-p транзистора соединен с эмиттером дополнительного биполярного транзистора (18), база которого подключена ко входу буферного усилителя (13), а коллектор соединен со второй (9) шиной источника питания, первый (10) источник опорного тока выполнен в виде двух идентичных и параллельно-включенных первого (19) и второго (20) элементарных источников опорного тока, каждый из которых выполнен на первом (21) дополнительном полевом транзисторе, затвор которого подключен ко второй (9) шине источника питания, а исток связан со второй (9) шиной источника питания через первый (22) дополнительный резистор, второй (14) источник опорного тока идентичен первому (19) и второму (20) элементарным источникам опорного тока, эмиттер первого (11) выходного биполярного p-n-p транзистора соединен с затвором второго (23) дополнительного полевого транзистора, сток которого соединен с первой (7) шиной источника питания, а исток подключен к эмиттеру первого (11) биполярного p-n-p транзистора через второй (17) вспомогательный резистор, эмиттер второго (12) выходного биполярного p-n-p транзистора соединен с затвором третьего (24) дополнительного полевого транзистора, сток которого подключен к первой (7) шине источника питания, а исток соединен с эмиттером второго (12) выходного биполярного p-n-p транзистора через первый (16) вспомогательный резистор, кроме этого, эмиттер второго (12) выходного биполярного p-n-p транзистора соединен с затвором четвертого (25) дополнительного полевого транзистора, исток которого через третий (26) вспомогательный резистор подключен к эмиттеру второго (12) выходного биполярного p-n-p транзистора, эмиттер первого (11) выходного биполярного p-n-p транзистора соединен с затвором пятого (27) дополнительного полевого транзистора, сток которого подключен к первой (7) шине источника питания, а исток соединен с эмиттером первого (11) выходного биполярного p-n-p транзистора через четвертый (28) вспомогательный резистор.

2. Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля по п. 1, отличающийся тем, что коллектор первого (11) выходного биполярного p-n-p транзистора соединен со входом буферного усилителя (13) через эмиттерно-базовый переход согласующего биполярного транзистора (29).

3. Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля по п. 1, отличающийся тем, что входной дифференциальный каскад (4) выполнен на входных полевых транзисторах (30) и (31).

4. Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля по п. 1, отличающийся тем, что в качестве входных полевых транзисторов (30) и (31) входного дифференциального каскада (4) используются каскодные составные транзисторы (32)-(33) и (34)-(35), причем первый (19) и второй (20) элементарные источники опорного тока в структуре первого (10) источника опорного тока, а также второй (14) источник опорного тока выполнены на каскодных составных транзисторах и содержат дополнительные выходные полевые транзисторы (36).

5. Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля по пп. 1-4, отличающийся тем, что в качестве полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

| US 6144234 A1, 07.11.2000 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| US 6501333 B1, 31.12.2002 | |||

| Операционный усилитель | 1974 |

|

SU500574A1 |

Авторы

Даты

2024-02-05—Публикация

2023-11-01—Подача