Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных усилителей и выходных каскадов в различных аналоговых устройствах (операционных усилителях, драйверах линий связи и т.п.).

В современной аналоговой микросхемотехнике находят широкое применение буферные усилители класса АВ на комплементарных n-p-n и p-n-p выходных транзисторах, в которых для улучшения линейности амплитудной характеристики вводится общая отрицательная обратная связь (ООС). В практических схемах ООС реализуется на двух входных комплементарных дифференциальных каскадах класса dual-input-stage [1-10].

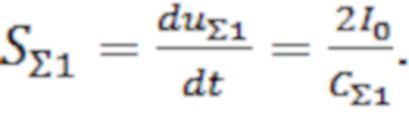

Ближайшим прототипом заявляемого устройства является буферный усилитель (фиг. 1), представленный в патенте US 6724260, fig. 12, 2004 г. Схема БУ-прототипа фиг. 1 содержит вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, общая эмиттерная цепь которых связана через первый 5 источник опорного тока с первой 6 шиной источника питания, первое 7 токовое зеркало, согласованное со второй 8 шиной источника питания, вход которого соединен с коллектором первого 3 входного транзистора, а выход связан с коллектором второго 4 входного транзистора и базой первого 9 выходного транзистора, база первого 3 входного транзистора соединена со входом 1 устройства, а база второго 4 входного транзистора соединена с эмиттером первого 9 выходного транзистора и связана с выходом устройства 2, третий 10 и четвертый 11 входные транзисторы, общая эмиттерная цепь которых соединена через второй 12 источник опорного тока со второй 8 шиной источника питания, второе 13 токовое зеркало, согласованное с первой 6 шиной источника питания, вход которого соединен с коллектором третьего 10 входного транзистора, а выход связан с коллектором четвертого 11 входного транзистора и базой второго 14 выходного транзистора, база третьего 10 входного транзистора подключена ко входу 1 устройства, а база четвертого 11 входного транзистора соединена с эмиттером второго 14 выходного транзистора и связана с выходом устройства 2, причем коллектор первого 9 выходного транзистора соединен со второй 8 шиной источника питания, а коллектор второго 14 выходного транзистора связан с первой 6 шиной источника питания.

Существенный недостаток БУ-прототипа состоит в том, что он имеет сравнительно небольшие значения максимальной скорости нарастания выходного напряжения при больших импульсных изменениях входного сигнала. Это ограничивает области его применения, не позволяет применять данное схемотехническое решение в качестве выходных каскадов быстродействующих ОУ, драйверов линий связи и т.п.

Основная задача предполагаемого изобретения состоит в создании буферного усилителя с повышенными (в 8-10 раз) значениями максимальной скорости нарастания выходного напряжения (SR).

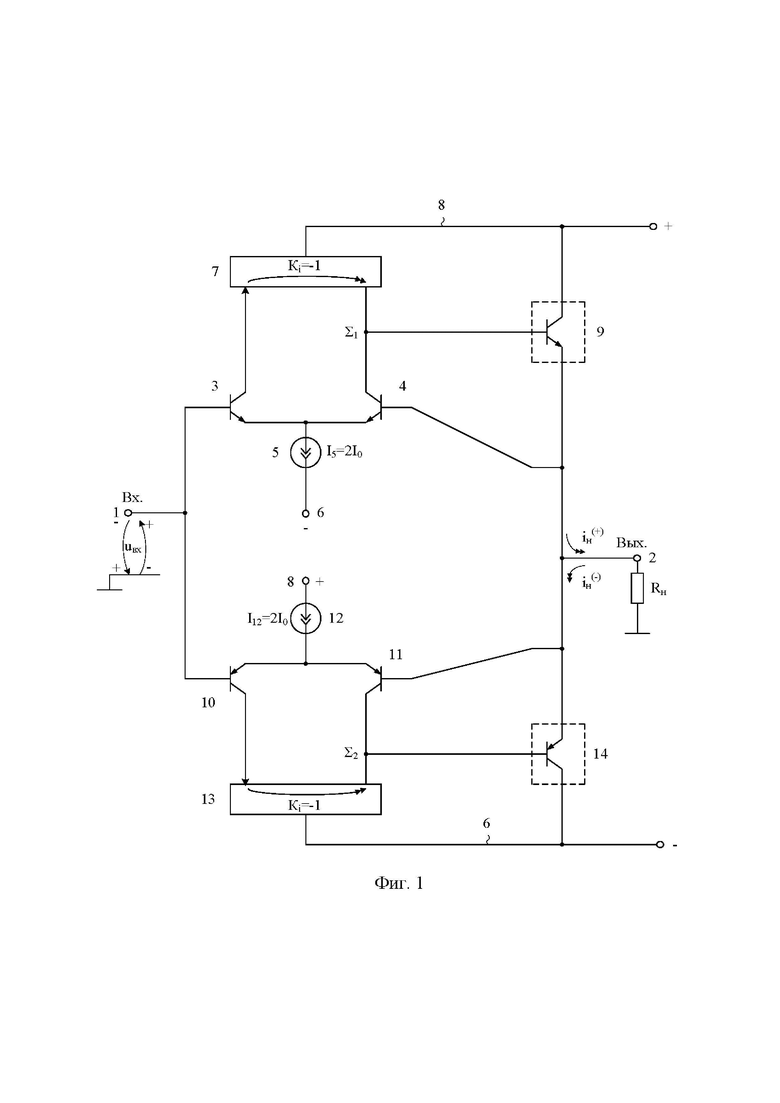

Поставленная задача решается тем, что в буферном усилителе фиг. 1, содержащем содержащий вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, общая эмиттерная цепь которых связана через первый 5 источник опорного тока с первой 6 шиной источника питания, первое 7 токовое зеркало, согласованное со второй 8 шиной источника питания, вход которого соединен с коллектором первого 3 входного транзистора, а выход связан с коллектором второго 4 входного транзистора и базой первого 9 выходного транзистора, база первого 3 входного транзистора соединена со входом 1 устройства, а база второго 4 входного транзистора соединена с эмиттером первого 9 выходного транзистора и связана с выходом устройства 2, третий 10 и четвертый 11 входные транзисторы, общая эмиттерная цепь которых соединена через второй 12 источник опорного тока со второй 8 шиной источника питания, второе 13 токовое зеркало, согласованное с первой 6 шиной источника питания, вход которого соединен с коллектором третьего 10 входного транзистора, а выход связан с коллектором четвертого 11 входного транзистора и базой второго 14 выходного транзистора, база третьего 10 входного транзистора подключена ко входу 1 устройства, а база четвертого 11 входного транзистора соединена с эмиттером второго 14 выходного транзистора и связана с выходом устройства 2, причем коллектор первого 9 выходного транзистора соединен со второй 8 шиной источника питания, а коллектор второго 14 выходного транзистора связан с первой 6 шиной источника питания, предусмотрены новые элементы и связи – в схему введены первый 15, второй 16, третий 17 и четвертый 18 дополнительные транзисторы, базы первого 15 и второго 16 дополнительных транзисторов подключены к выходу 2 устройства, эмиттер первого 15 дополнительного транзистора соединен со второй 8 шиной источника питания через первый 19 дополнительный источник опорного тока и соединен с базой третьего 17 дополнительного транзистора, коллектор которого согласован со второй 8 шиной источника питания, эмиттер второго 16 дополнительного транзистора соединен с первой 6 шиной источника питания через второй 20 дополнительный источник опорного тока и соединен с базой четвертого 18 дополнительного транзистора, коллектор которого согласован с первой 6 шиной источника питания, коллектор второго 16 дополнительного транзистора соединен со второй 8 шиной источника питания, коллектор первого 15 дополнительного т транзистора связан с первой 6 шиной источника питания, эмиттер третьего 17 дополнительного транзистора соединен с объединенными эмиттерами третьего 10 и четвертого 11 входных транзисторов, а эмиттер четвертого 18 дополнительного транзистора соединен с объединенными эмиттерами первого 3 и второго 4 входных транзисторов.

На чертеже фиг. 1 представлена схема буферного усилителя-прототипа по патенту US 6724260, fig. 12, 2004 г.

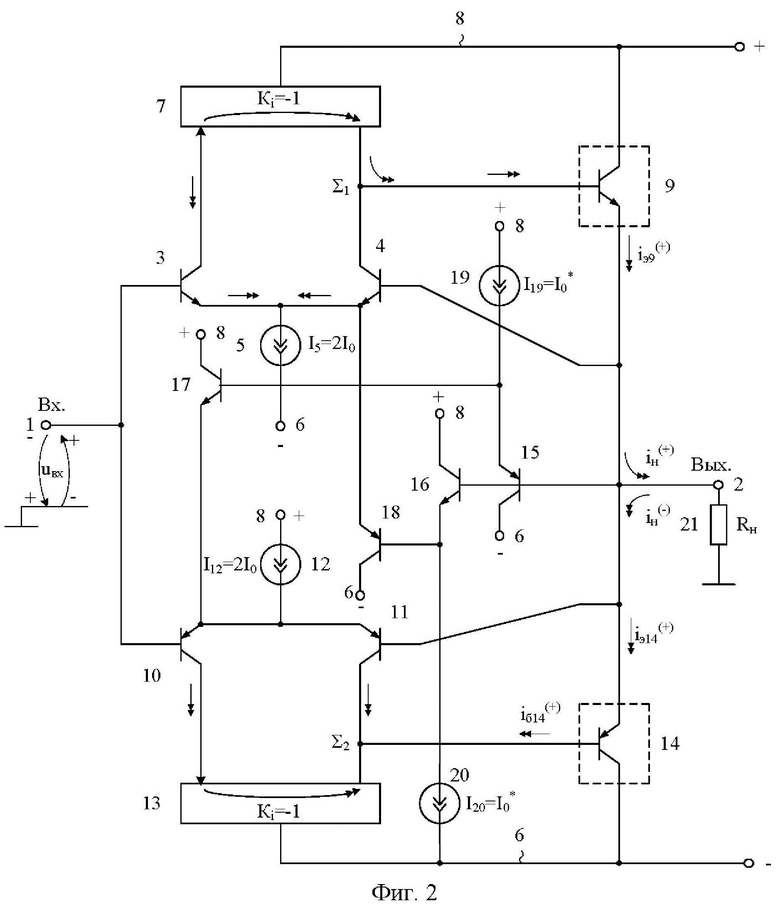

На чертеже фиг. 2 приведена схема заявляемого буферного усилителя в соответствии с формулой изобретения.

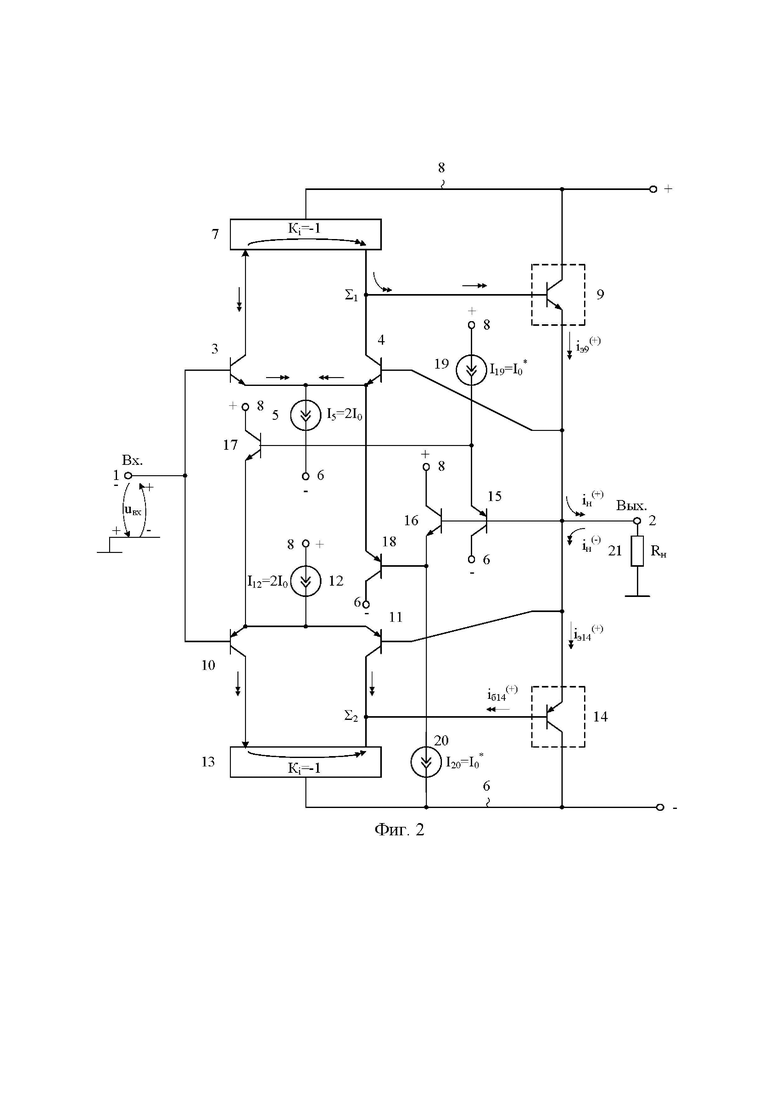

На чертеже фиг. 3 показана схема для моделирования БУ-прототипа фиг. 1 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=200 мкА.

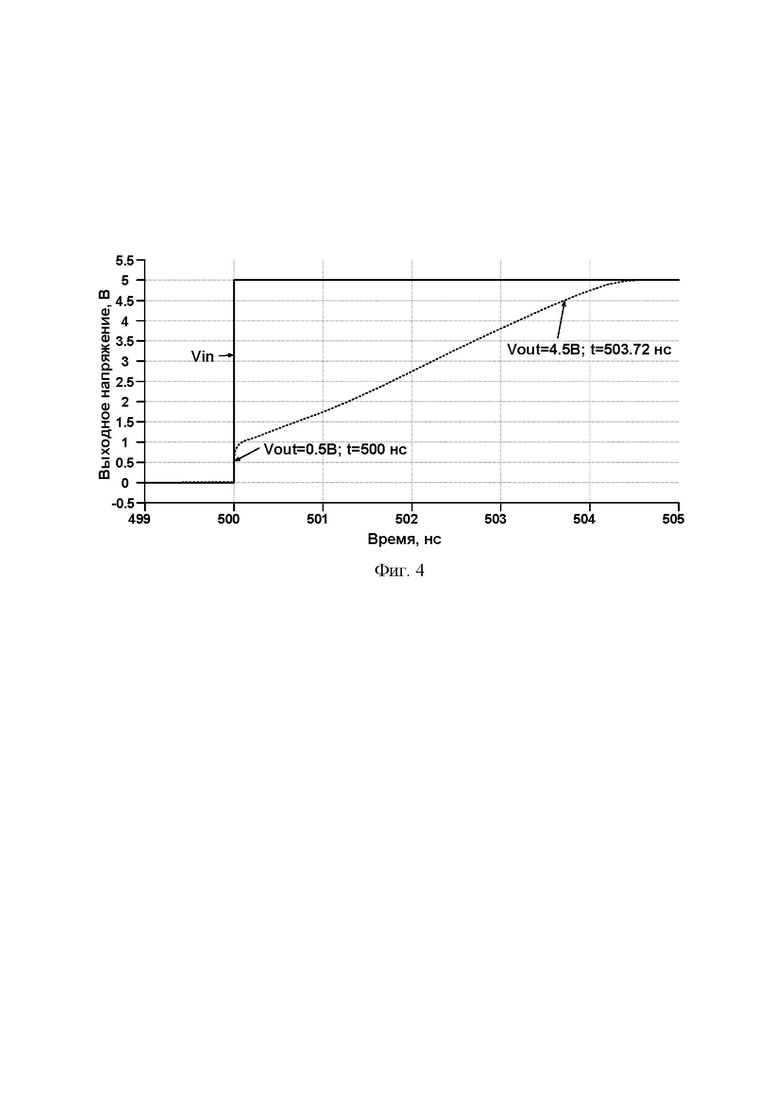

На чертеже фиг. 4 представлена переходная характеристика переднего фронта БУ-прототипа фиг. 3 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=200 мкА.

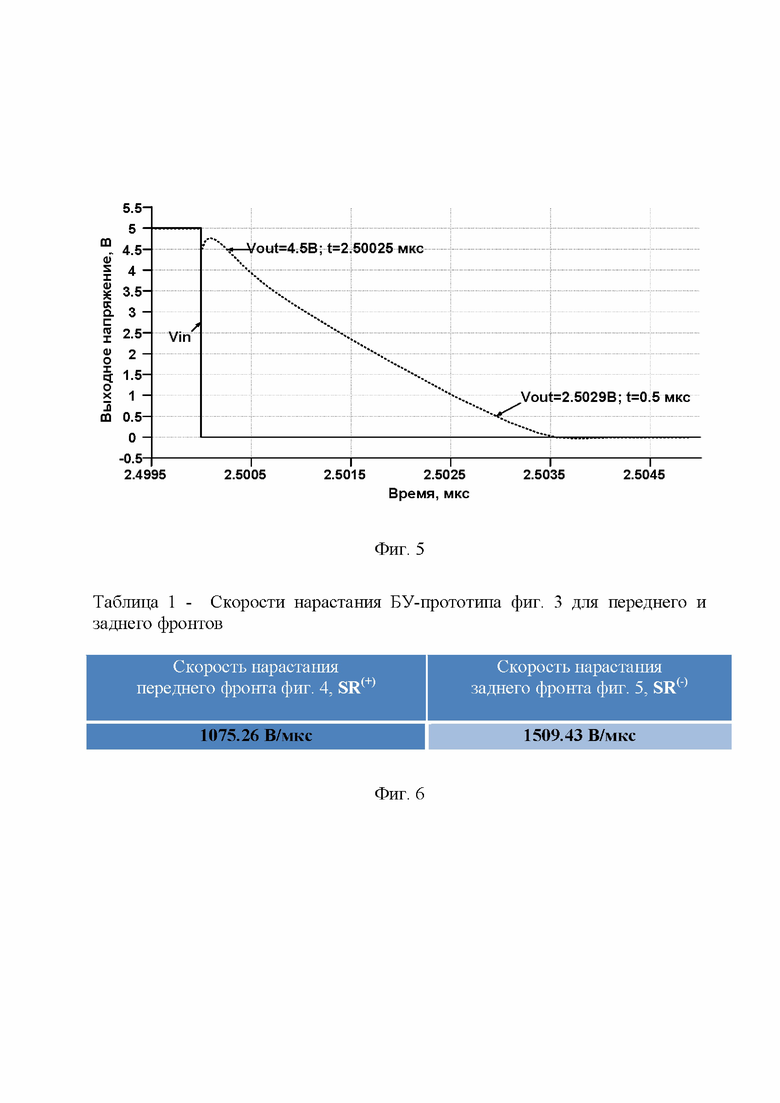

На чертеже фиг. 5 приведена переходная характеристика заднего фронта БУ-прототипа фиг. 3 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=200 мкА.

На чертеже фиг. 6 в таблице 1 показаны скорости нарастания БУ-прототипа фиг. 3 для переднего и заднего фронтов.

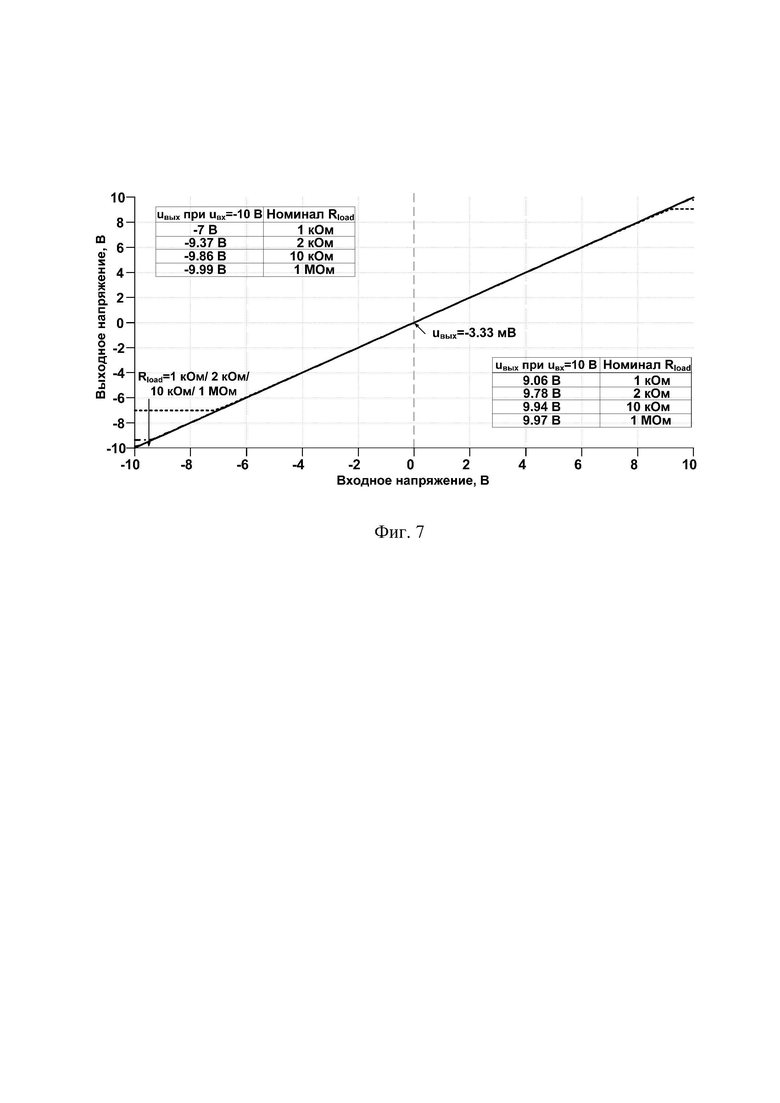

На чертеже фиг. 7 представлена амплитудная характеристика БУ-прототипа фиг. 3 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, I1= I2=200 мкА, Rload= 1 кОм/2 кОм/ 10кОм/1 МОм.

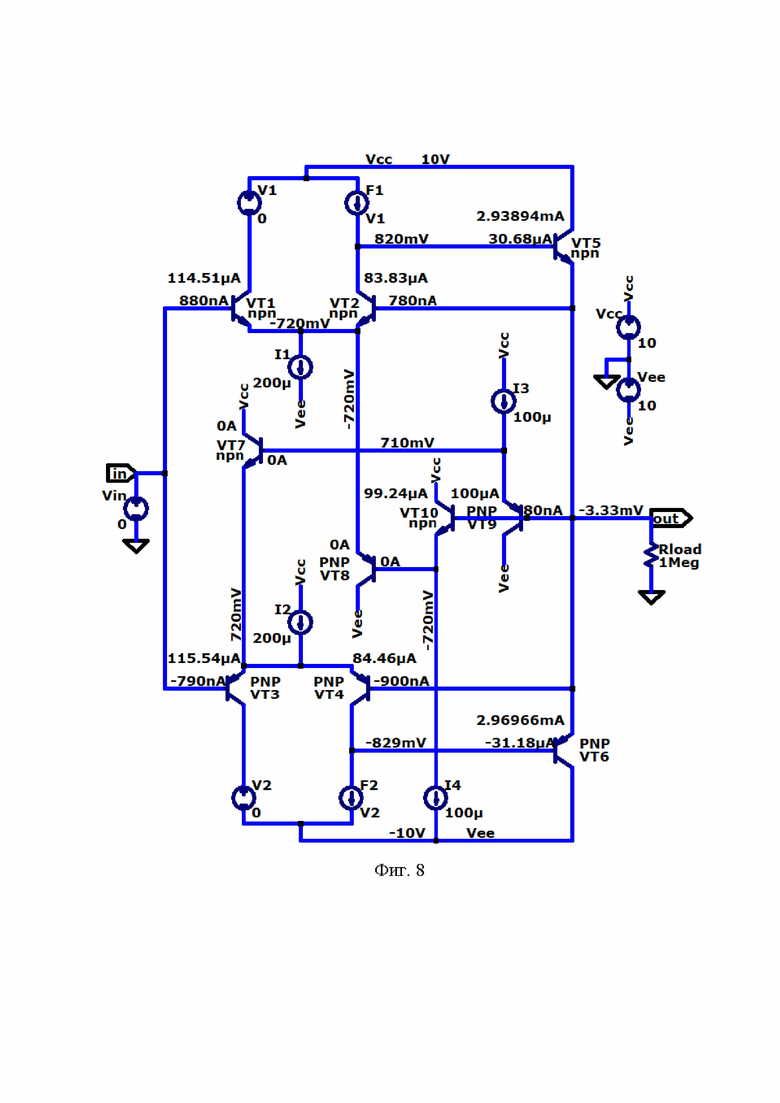

На чертеже фиг. 8 приведена схема для моделирования предлагаемого быстродействующего БУ фиг. 2 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=200 мкА, I3= I4=100 мкА.

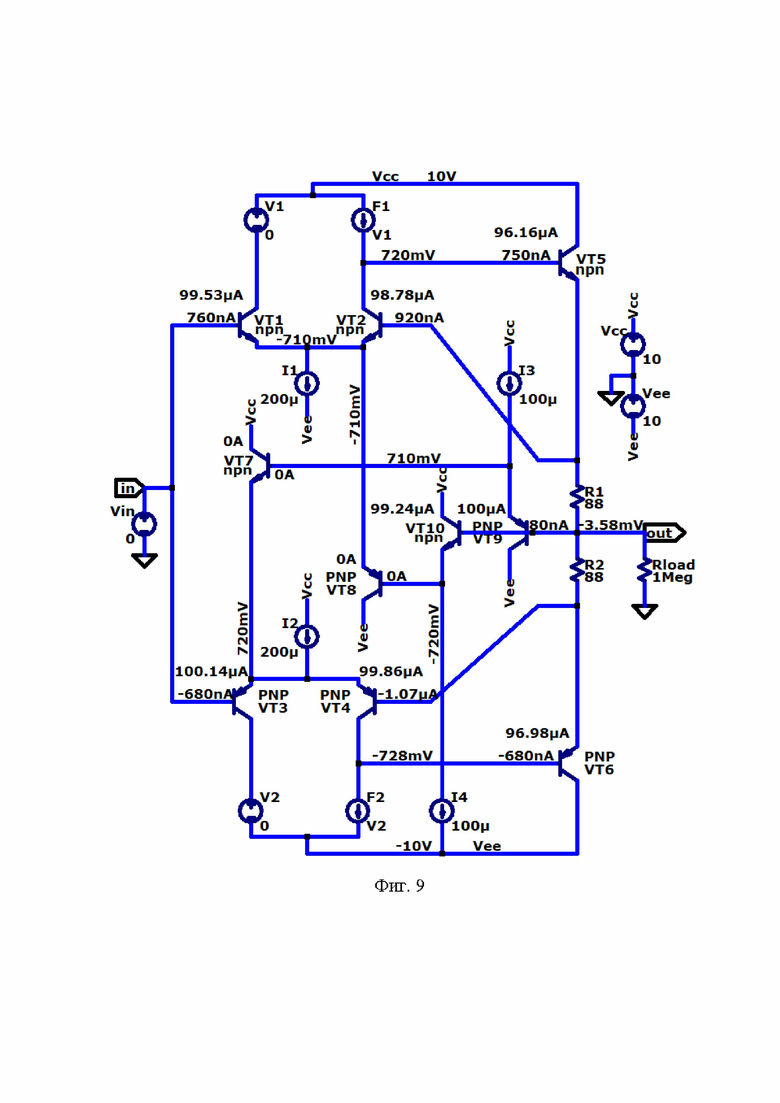

На чертеже фиг. 9 показана частная схема для моделирования предлагаемого быстродействующего БУ фиг. 2 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=200 мкА, I3= I4=100 мкА, для случая, когда с целью уменьшения статических токов эмиттера транзисторов VT5 и VT6 с 2,9 мА до 96 мкА в схему введены вспомогательные резисторы R1=R2= 88 Ом.

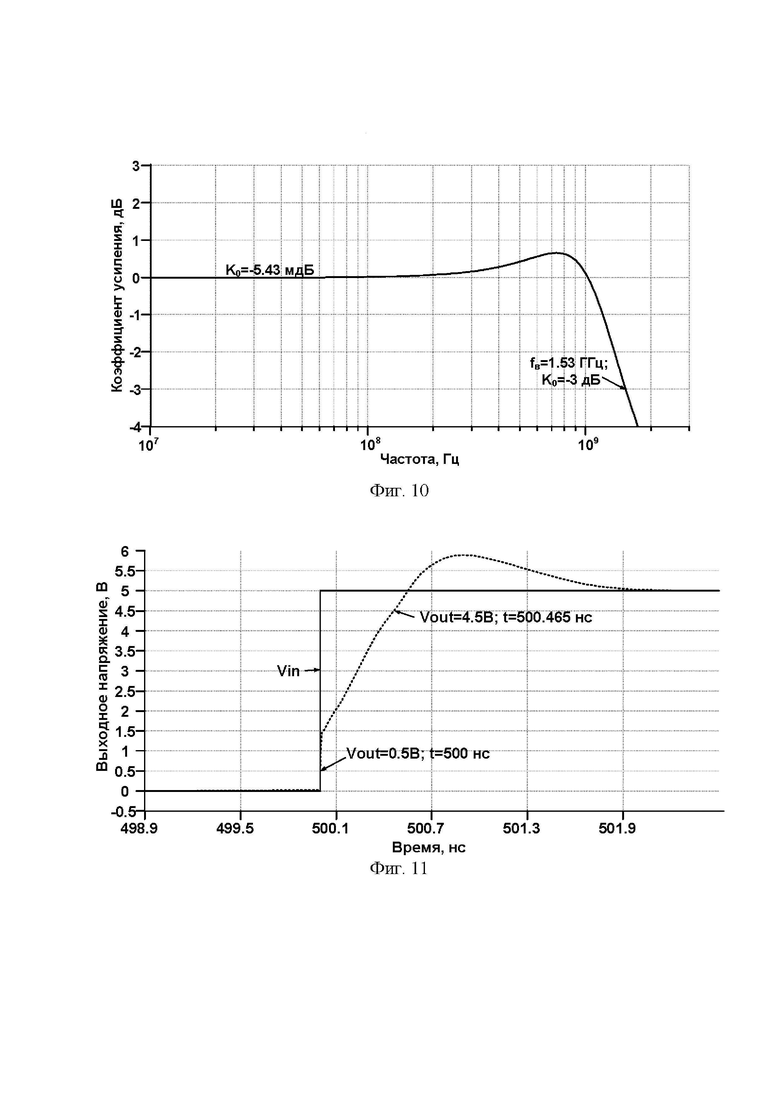

На чертеже фиг. 10 представлена логарифмическая амплитудно-частотная характеристика коэффициента передачи предлагаемого быстродействующего БУ фиг. 9.

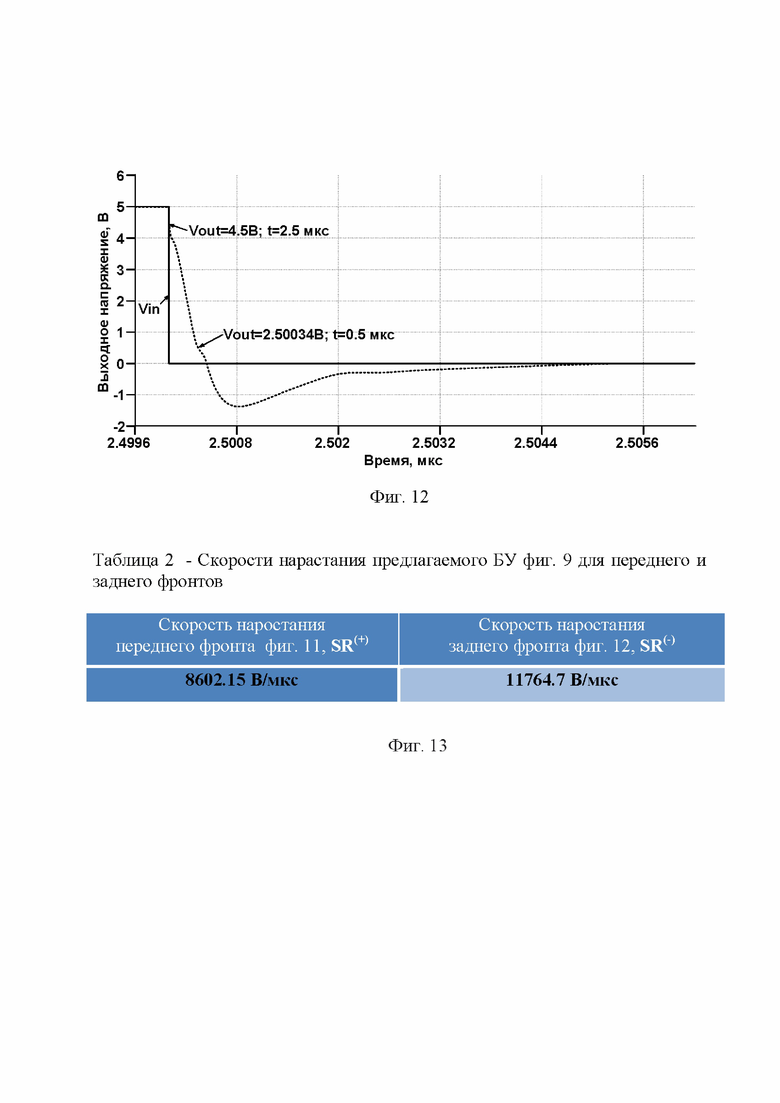

На чертеже фиг. 11 приведена переходная характеристика переднего фронта предлагаемого быстродействующего БУ фиг. 9 в среде LTspice.

На чертеже фиг. 12 показана переходная характеристика заднего фронта предлагаемого быстродействующего БУ фиг. 9 в среде LTspice.

На чертеже фиг. 13 в таблице 2 представлены скорости нарастания предлагаемого БУ фиг. 9 для переднего и заднего фронтов.

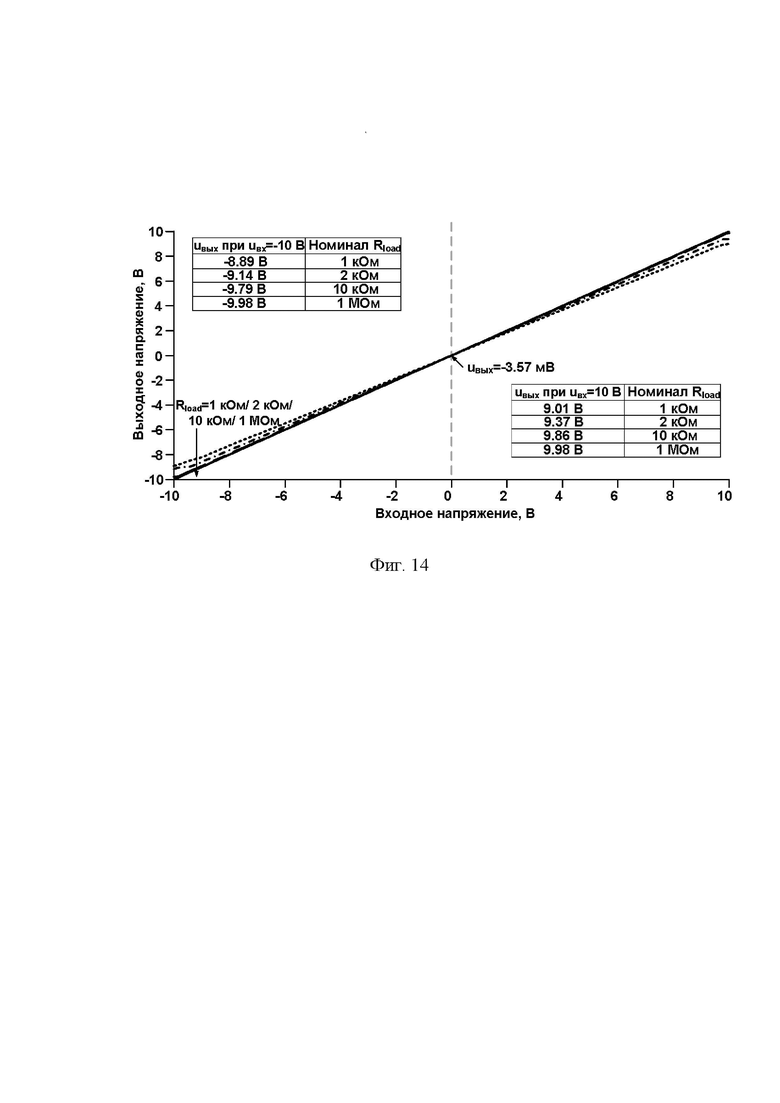

На чертеже фиг. 14 приведена амплитудная характеристика предлагаемого быстродействующего БУ фиг. 9 в среде LTspice.

Быстродействующий буферный усилитель с нелинейной коррекцией класса АВ фиг. 2 содержит вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, общая эмиттерная цепь которых связана через первый 5 источник опорного тока с первой 6 шиной источника питания, первое 7 токовое зеркало, согласованное со второй 8 шиной источника питания, вход которого соединен с коллектором первого 3 входного транзистора, а выход связан с коллектором второго 4 входного транзистора и базой первого 9 выходного транзистора, база первого 3 входного транзистора соединена со входом 1 устройства, а база второго 4 входного транзистора соединена с эмиттером первого 9 выходного транзистора и связана с выходом устройства 2, третий 10 и четвертый 11 входные транзисторы, общая эмиттерная цепь которых соединена через второй 12 источник опорного тока со второй 8 шиной источника питания, второе 13 токовое зеркало, согласованное с первой 6 шиной источника питания, вход которого соединен с коллектором третьего 10 входного транзистора, а выход связан с коллектором четвертого 11 входного транзистора и базой второго 14 выходного транзистора, база третьего 10 входного транзистора подключена ко входу 1 устройства, а база четвертого 11 входного транзистора соединена с эмиттером второго 14 выходного транзистора и связана с выходом устройства 2, причем коллектор первого 9 выходного транзистора соединен со второй 8 шиной источника питания, а коллектор второго 14 выходного транзистора связан с первой 6 шиной источника питания. В схему введены первый 15, второй 16, третий 17 и четвертый 18 дополнительные транзисторы, базы первого 15 и второго 16 дополнительных транзисторов подключены к выходу 2 устройства, эмиттер первого 15 дополнительного транзистора соединен со второй 8 шиной источника питания через первый 19 дополнительный источник опорного тока и соединен с базой третьего 17 дополнительного транзистора, коллектор которого согласован со второй 8 шиной источника питания, эмиттер второго 16 дополнительного транзистора соединен с первой 6 шиной источника питания через второй 20 дополнительный источник опорного тока и соединен с базой четвертого 18 дополнительного транзистора, коллектор которого согласован с первой 6 шиной источника питания, коллектор второго 16 дополнительного транзистора соединен со второй 8 шиной источника питания, коллектор первого 15 дополнительного т транзистора связан с первой 6 шиной источника питания, эмиттер третьего 17 дополнительного транзистора соединен с объединенными эмиттерами третьего 10 и четвертого 11 входных транзисторов, а эмиттер четвертого 18 дополнительного транзистора соединен с объединенными эмиттерами первого 3 и второго 4 входных транзисторов. Резистор 21 моделирует свойства нагрузки Rн, подключаемой к выходу устройства 2.

Рассмотрим вначале работу схемы буферного усилителя – прототипа фиг. 1.

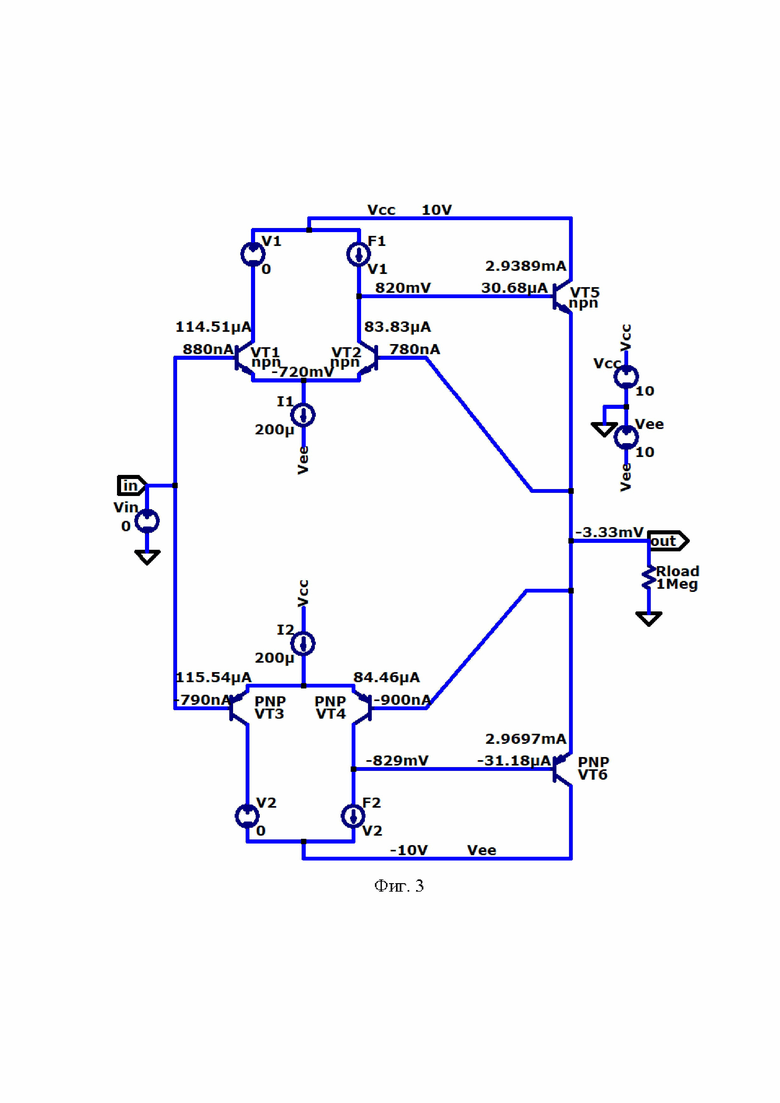

При импульсном изменении входного напряжения положительной полярности первый 3 входной транзистор практически мгновенно переключается - его эмиттерный и коллекторный токи становятся равными току первого 5 источника опорного тока, а второй 4 входной транзистор запирается по цепи эмиттера. Как следствие, суммарная емкость СΣ1 в высокоимпедансном узле Σ1 перезаряжается сравнительно малым током I5=2I0 и имеет «пилообразную» форму с крутизной

(1)

(1)

Как следствие, напряжение в высокоимпедансном узле Σ1 (uΣ1) передается через эмиттерный повторитель на первом 9 выходном транзисторе на выход 2 устройства. Поэтому максимальная скорость нарастания выходного напряжения БУ-прототипа также определяется формулой (1), из которой следует, что при фиксированных значениях  , которое определяется суммой емкостей база-коллектор первого 9 выходного и первого 4 входного транзисторов, в схеме известного БУ приходится увеличивать ток I5=2I0, что отрицательно сказывается на энергопотреблении БУ в статическом режиме. Об этом свидетельствуют графики переходных характеристик на чертежах фиг. 4 и фиг. 5, а также данные таблицы фиг. 6.

, которое определяется суммой емкостей база-коллектор первого 9 выходного и первого 4 входного транзисторов, в схеме известного БУ приходится увеличивать ток I5=2I0, что отрицательно сказывается на энергопотреблении БУ в статическом режиме. Об этом свидетельствуют графики переходных характеристик на чертежах фиг. 4 и фиг. 5, а также данные таблицы фиг. 6.

Введение новых элементов и связей между ними в соответствии с формулой изобретения позволяет повысить максимальную скорость нарастания выходного напряжения БУ фиг. 2 в 8-10 раз при сохранении статического токопотребления на уровне БУ-прототипа. Действительно, при импульсном изменении входного напряжения положительной полярности в схеме фиг. 2 импульсный коллекторный ток первого 3 входного транзистора не ограничивается уровнем I5=2I0 - к нему добавляется импульсный ток эмиттера iэ18(+) открывающегося четвертого 18 дополнительного транзистора . Этот ток зависит от разности входного и выходного напряжения БУ. Когда эта разность велика (начальный участок переходного процесса), то ток iэ18(+) принимает большие значения, что способствует более быстрому перезаряду паразитной емкости  в высокоимпедансном узле Σ1. Как следствие, это значительно повышает максимальную скорость нарастания напряжения на выходе 2 БУ. Об этом свидетельствуют графики переходного процесса на чертежах фиг. 11, а также данные таблицы 2 на чертеже фиг. 13, из которых следует, что SR увеличивается в 8 раз.

в высокоимпедансном узле Σ1. Как следствие, это значительно повышает максимальную скорость нарастания напряжения на выходе 2 БУ. Об этом свидетельствуют графики переходного процесса на чертежах фиг. 11, а также данные таблицы 2 на чертеже фиг. 13, из которых следует, что SR увеличивается в 8 раз.

При больших отрицательных импульсных сигналах получаются аналогичные результаты, что отражено на графиках фиг. 12 и в таблице 2 на чертеже фиг. 13 – максимальная скорость нарастания улучшается в 7,8 раз.

Введение в некоторых случаях вспомогательных резисторов R1, R2 в схеме фиг. 9 позволяет уменьшить статические коллекторные токи первого 9 и второго 14 выходных транзисторов до уровня менее 100 мкА.

Дальнейшее увеличение SR в рассматриваемой схеме БУ фиг. 2 в 10-100 раз возможно за счет уменьшения зоны нечувствительности нелинейных параллельных каналов на третьем 17 и четвертом 18 дополнительных транзисторах. Это можно осуществить включением дополнительных низкоомных резисторов или p-n переходов в эмиттеры транзисторов первого 15 и второго 16 дополнительных транзисторов, которые создадут начальное смещение эмиттерно-базовых переходов третьего 17 и четвертого 18 дополнительных транзисторов и обеспечат их переход из отсечки в активный режим при меньшей разности между входным и выходным напряжениями БУ. В конечном итоге такой схемотехнический прием позволяет получить более высокие значения SR в рассматриваемом БУ.

Таким образом, предлагаемый буферный усилитель имеет существенные преимущества в сравнении с БУ-прототипом по быстродействию.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.724.260, fig. 12, 2004 г.

2. Патент US 6.724.260 B2, fig. 12, 2004 г.

3. Патент US 5.291.149, fig. 3, 1994 г.

4. Патент US 6.268.769, fig. 3, 2001 г.

5. Патент US 4.636.743, fig. 1, 1987 г.

6. Патент US 4.783.637, fig. 1, 1988 г.

7. Патент US 5.225.791, fig. 2, 1993 г.

8. Патент US 5.512.859, fig. 1, 1996 г.

9. Патент US 3.968.451, fig. 7, 1976 г.

10. Патент SU 1220105, fig. 1, 1982 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2022 |

|

RU2790616C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786191C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА n-p-n БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786630C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных усилителей. Технический результат: создание буферного усилителя с повышенными (в 8-10 раз) значениями максимальной скорости нарастания выходного напряжения, который достигается тем, что в схему введены дополнительные транзисторы, причем базы первого (15) и второго (16) дополнительных транзисторов подключены к выходу (2) устройства, эмиттер первого (15) дополнительного транзистора соединен со второй (8) шиной источника питания и соединен с базой третьего (17) дополнительного транзистора, коллектор которого согласован со второй (8) шиной источника питания, эмиттер второго (16) дополнительного транзистора соединен с первой (6) шиной источника питания и соединен с базой четвертого (18) дополнительного транзистора, коллектор которого согласован с первой (6) шиной источника питания, коллектор второго (16) дополнительного транзистора соединен со второй (8) шиной источника питания, коллектор первого (15) дополнительного транзистора связан с первой (6) шиной источника питания, эмиттер третьего (17) дополнительного транзистора соединен с объединенными эмиттерами третьего (10) и четвертого (11) входных транзисторов, а эмиттер четвертого (18) дополнительного транзистора соединен с объединенными эмиттерами первого (3) и второго (4) входных транзисторов. 14 ил.

Быстродействующий буферный усилитель с нелинейной коррекцией класса АВ, содержащий вход (1) и выход (2) устройства, первый (3) и второй (4) входные транзисторы, общая эмиттерная цепь которых связана через первый (5) источник опорного тока с первой (6) шиной источника питания, первое (7) токовое зеркало, согласованное со второй (8) шиной источника питания, вход которого соединен с коллектором первого (3) входного транзистора, а выход связан с коллектором второго (4) входного транзистора и базой первого (9) выходного транзистора, база первого (3) входного транзистора соединена со входом (1) устройства, а база второго (4) входного транзистора соединена с эмиттером первого (9) выходного транзистора и связана с выходом устройства (2), третий (10) и четвертый (11) входные транзисторы, общая эмиттерная цепь которых соединена через второй (12) источник опорного тока со второй (8) шиной источника питания, второе (13) токовое зеркало, согласованное с первой (6) шиной источника питания, вход которого соединен с коллектором третьего (10) входного транзистора, а выход связан с коллектором четвертого (11) входного транзистора и базой второго (14) выходного транзистора, база третьего (10) входного транзистора подключена ко входу (1) устройства, а база четвертого (11) входного транзистора соединена с эмиттером второго (14) выходного транзистора и связана с выходом устройства (2), причем коллектор первого (9) выходного транзистора соединен со второй (8) шиной источника питания, а коллектор второго (14) выходного транзистора связан с первой (6) шиной источника питания, отличающийся тем, что в схему введены первый (15), второй (16), третий (17) и четвертый (18) дополнительные транзисторы, базы первого (15) и второго (16) дополнительных транзисторов подключены к выходу (2) устройства, эмиттер первого (15) дополнительного транзистора соединен со второй (8) шиной источника питания через первый (19) дополнительный источник опорного тока и соединен с базой третьего (17) дополнительного транзистора, коллектор которого согласован со второй (8) шиной источника питания, эмиттер второго (16) дополнительного транзистора соединен с первой (6) шиной источника питания через второй (20) дополнительный источник опорного тока и соединен с базой четвертого (18) дополнительного транзистора, коллектор которого согласован с первой (6) шиной источника питания, коллектор второго (16) дополнительного транзистора соединен со второй (8) шиной источника питания, коллектор первого (15) дополнительного транзистора связан с первой (6) шиной источника питания, эмиттер третьего (17) дополнительного транзистора соединен с объединенными эмиттерами третьего (10) и четвертого (11) входных транзисторов, а эмиттер четвертого (18) дополнительного транзистора соединен с объединенными эмиттерами первого (3) и второго (4) входных транзисторов.

| US 6724260 B2, 20.04.2004 | |||

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2668985C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615066C1 |

| US 20090039961 A1, 12.02.2009 | |||

| US 5378938 A, 03.01.1995. | |||

Авторы

Даты

2023-02-28—Публикация

2022-12-08—Подача