Способ и устройство аналого-цифрового преобразования относятся к области вычислительной техники и могут использоваться в системах цифровой обработки аналоговой информации.

Известны различные способы аналого-цифрового преобразования (SU1128380A1; RU2693647C1; SU481132A1), основанные на преобразовании входного сигнала во временной интервал путём его сравнения с линейно изменяющимся уравновешивающим сигналом. Недостатком этих методов является большое время, затрачиваемое на получение цифрового отсчёта.

Известны также способы аналого-цифрового преобразования, в которых с целью ускорения процесс преобразования разбивается на ряд этапов, каждый из которых обеспечивает формирование своей, начиная с первой, старшей разрядной ступени, группы разрядов выходного кода(SU 472453A1;RU 2430465 C2).

Наиболее близким к заявленному способу относится метод, используемый ваналого-цифровом преобразователе последовательного счёта с промежуточным преобразованием во временной интервал (SU748856A1), в котором перед каждым этапом, на основе оценки величины рассогласования между входным и уравновешивающим сигналами, производится выбор очередной рабочей ступени (этапа).

Данный способ имеет следующие недостатки:

1. Предварительный анализ величины рассогласования перед каждым этапом приводит к задержке обработки и, как следствие, снижает точность преобразования.

2. Предварительная оценка рассогласования и выбор рабочей ступени перед каждым этапом требуют дополнительных аппаратурных затрат.

Целью предлагаемого решения является повышение точности преобразования и снижение аппаратурных затрат на реализацию устройства.

Поставленная цель достигается тем, что в способ аналого-цифрового преобразования последовательного счёта с промежуточным преобразованием во временной интервал, в котором с целью ускорения процесс кодирования разбит на ряд этапов, реализуемых каждый своей ступенью, и обеспечивающих последовательное, начиная со старших, формирование групп разрядов выходного кода, знак приращений уравновешивающего сигнала при переходе от одного этапа к следующему меняется на противоположный.

На каждом этапе преобразования при изменении знака рассогласования между преобразуемыми уравновешивающим сигналами подсчёт тактовых импульсов соответствующей ступенью прекращается.

При этом выходной код преобразователя образуется путём присоединения прямых кодов секций счётчика нечётных ступеней и инверсных кодов, снимаемых с секций чётных ступеней.

В аналого-цифровом преобразователе поставленная цель достигается путём подключения входов аналоговых ключей нечётных и чётных ступеней к соответствующим выходам разнополярных напряжений источника опорных напряжений, соединением выхода компаратора через инвертор с третьими входами трёхвходовых элементов И управления режимом чётных ступеней и с третьими входами элементов И управления счётом нечётных ступеней, выходной код преобразователя снимается с прямых выходов соответствующих разрядов секций счётчика нечётных ступеней и с инверсных выходов разрядов секций счётчика чётных ступеней преобразователя.

Аналого-цифровой преобразователь (фиг. 1) содержит общие для всего преобразователя интегратор (поз.1), ключ обнуления (поз.2), компаратор (поз.3), источник опорных напряжений (поз. 4), генератор тактовых импульсов (поз. 5), и несколько разрядных ступеней, количество которых не превышает числа разрядов преобразователя, каждая из которых, начиная с первой, старшей разрядной ступени, предназначена для формирования своей группы

разрядов выходного кода и включает в себя (для 1-й, 2-й и 3-ей ступеней) соответствующую секцию двоичного счётчика (поз. 5,6,7), аналоговый ключ (поз. 8,9,10), R-S триггер режима (поз. 11,12,13), R- вход которого соединён с выходом трёхвходового элемента И управления режимом (поз. 14,15,16), S-вход R-S триггера режима 11 первой, старшей разрядной ступени, соединён с выходом двухвходового элемента И(поз. 17), а S- входы триггеров режима второй 12 и каждой последующей ступеней соединены с R- входами триггеров режима предшествующей ступени, R- вход R-S триггера режима последней, младшей разрядной ступени (поз. 13), соединён с управляющим входом ключа обнуления (поз. 2), вход которого подключён к земляной шине, а выход - к выходу интегратора и к первому входу компаратора 3, второй вход которого соединён со входом преобразователя, счётный вход каждой секции двоичного счётчика подключён к выходу трёхвходового элемента И управления счётом (поз. 18,19,20) соответствующей ступени, первые входы трёхвходовых элементов И управления счётом всех ступеней объединены с первым входом двухвходового элемента И (поз. 17), первыми входами элементов И управления режимами (поз. 14,15,16)и выходом генератора тактовых импульсов 5, второй вход двухвходового элемента И 17 подключён к входу «ПУСК», второй вход трёхвходового элемента И управления режимом каждой ступени соединён с вторым входом трёхвходового элемента И управления счётом, выходом R-S триггера режима и управляющим входом аналогового ключа соответствующей ступени, выходы аналоговых ключей соединены с входом интегратора, выход компаратора соединён с третьими входами трёхвходовых элементов И управления режимом нечётных ступеней и третьими входами трёхвходовых элементов И управления счётом чётных ступеней, входы аналоговых ключей нечётных и чётных ступеней подключены к соответствующим выходам разнополярных опорных напряжений источника опорных напряжений 4, выход компаратора подключён к входу инвертора (поз. 21), соединённого выходом с третьими входами трёхвходовых элементов И управления режимом чётных ступеней и

с третьими входами элементов И управления счётом нечётных ступеней, выходной код преобразователя снимается с прямых выходов соответствующих разрядов секций счётчика нечётных ступеней и с инверсных выходов разрядов секций счётчика чётных ступеней.

Устройство работает следующим образом.

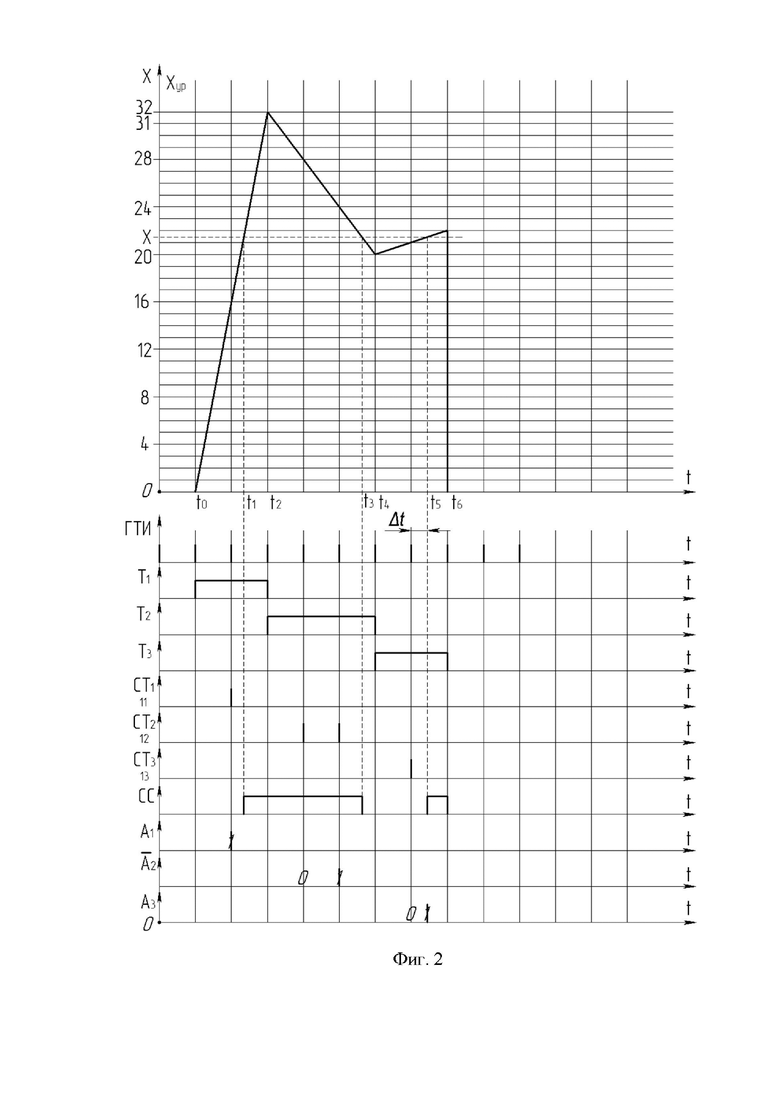

В момент t0 (фиг. 2) триггер режима первой ступени 11 (фиг. 1) переводится в единичное состояние. При этом замыкается ключ 8 и опорное напряжение E1 подключается ко входу интегратора1. На выходе интегратора начинается формирование линейно изменяющегося уравновешивающего напряжения Хур1.Одновременно открывается трёхвходовой элемент И управления счётом 18 первой ступени и начинается подсчёт таковых импульсов секцией старших разрядов 5 счётчика.

В момент наступления неравенства: Х – Хур1 ≤ 0 (момент времени t1) компаратор 3 переходит в единичное состояние. При этом закрывается элемент И управления счётом 18 первой ступени и подсчёт импульсов секцией старших разрядов 5 счётчика прекращается.

Очередной тактовый импульс в момент времени t2 через открытый элемент И управления режимом 14 переводит R-S триггер режима 11 первой ступени в нулевое состояние, а R-S триггер режима 12 второй ступени - в единичное. При этом замыкается ключ 9 и опорное напряжение-Е2подключается ко входу интегратора 1.

Одновременно открывается трёхвходовой элемент И управления счётом 19 секции счётчика второй ступени и начинается подсчёт тактовых импульсов секцией 6 счётчика на интервале t2÷ t3.

В момент пересечения уравновешивающим сигналом уровня входного сигнала (момент t3) компаратор 3 переходит в нулевое состояние. При этом закрывается трёхвходовой элемент И управления счётом 19 второй ступени и открывается элемент И 15 управления режимом второй ступени. Следующий тактовый импульс проходит через этот элемент и сбрасывает в нулевое состояние R-S-триггер управления режимом 12 второй ступени и переводит в единичное состояние R-S триггер управления режимом 13 третьей ступени. Преобразователь переходит к третьему этапу кодирования. При этом открывается ключ 10 и на вход интегратора 1подаётся напряжение Е3. Начинается подсчёт тактовых импульсов секцией младших разрядов 7 счётчика на интервале t4÷ t5.

Процесс подсчёта тактовых импульсов на этом интервале заканчивается в момент пересечения уравновешивающим сигналом уровня преобразуемого сигала. Следующий тактовый импульс через открытый трёхвходовой элемент И 16 управления режимом сбрасывает триггер режима 13 и открывает ключ обнуления 2, обеспечивающий разряд интегратора.

Выражая временные интервалы через численные эквиваленты кодов, полученных секциями счётчика к моменту t5, можно получить численный эквивалент обратного кода, записанного в секции второй ступени, и численные эквиваленты прямых кодов первой и третьей ступеней.

Таким образом, выходной код А в преобразователе на фиг. 1 образуется присоединением прямого кода А1 первой ступени к обратному кодуĀ2 второй и прямому коду А3 третьей ступени:

В преобразователях с произвольным числом ступеней k выходной код будет формироваться путём присоединения прямых кодов нечётных ступеней к обратным кодам чётных:

где • - знак присоединения. Символ * в этом выражении заменяется знаком инверсии для чётных k и опускается- для нечётных.

Применение заявляемого устройства позволяет исключить избыточное накопление заряда в интеграторе при переходе от одного этапа преобразования к следующему. В результате повышается точность кодирования.

Заявляемый аналого-цифровой преобразователь обеспечивает сохранение естественной последовательности чередования этапов кодирования без потери точности. При этом в структуре преобразователя отсутствует блок анализа и используется только один компаратор, что сокращает аппаратурные затраты на реализацию.

Способ аналого-цифрового преобразования последовательного счёта с промежуточным преобразованием входной величины во временной интервал, в котором с целью ускорения процесс кодирования разбивается на ряд этапов, каждый из которых реализуется своей ступенью и обеспечивает последовательное, начиная с первой, старшей разрядной ступени, формирование групп разрядов выходного кода, отличающийся тем, что в с целью повышения точности преобразования в момент достижения уравновешивающим сигналом на соответствующем этапе уровня входного сигнала подсчёт тактовых импульсов секцией счётчика данной ступени прекращается, а очередной тактовый импульс осуществляет подготовку преобразователя к выполнению следующего этапа, при этом уменьшается величина и изменяется знак коэффициента наклона линейно изменяющегося уравновешивающего сигнала а выход генератора тактовых импульсов отключается от счётного входа данной и подключается к счётному входу секции счётчика следующей ступени, выходной код преобразователя снимается с прямых выходов секций счётчика нечётных ступеней и с инверсных выходов секций чётных ступеней.

Аналого-цифровой преобразователь последовательного счёта с промежуточным преобразованием входной величины во временной интервал отличающееся тем, что входы аналоговых ключей нечётных и чётных ступеней подключены к соответствующим выходам разнополярных опорных напряжений источника опорных напряжений, выход компаратора подключён к входу инвертора, соединённого выходом с третьими входами трёхвходовых элементов И управления режимом чётных ступеней и с третьими входами элементов И управления счётом нечётных ступеней, выходной код преобразователя снимается с прямых выходов соответствующих разрядов секций счётчика нечётных ступеней и с инверсных выходов разрядов секций счётчика чётных ступеней.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный аналого-цифровой преобразователь | 2023 |

|

RU2815253C1 |

| Интегрирующий аналого-цифровой преобразователь | 2023 |

|

RU2802872C1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018234A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1979 |

|

SU964981A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| Устройство для компенсации реактивной мощности | 1982 |

|

SU1070644A1 |

| Преобразователь напряжения в код с плавающей запятой | 1981 |

|

SU978340A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах цифровой обработки аналоговой информации. Технический результат - повышение точности кодирования. Для этого осуществляют аналого-цифровое преобразование последовательного счёта с промежуточным преобразованием во временной интервал, в котором процесс кодирования разбит на ряд этапов, реализуемых каждый своей ступенью, которое обеспечивает последовательное, начиная со старших, формирование групп разрядов выходного кода, знак приращений уравновешивающего сигнала при переходе от одного этапа к следующему меняется на противоположный. При изменении знака рассогласования между преобразуемым и уравновешивающим сигналами подсчёт тактовых импульсов соответствующей ступенью счётчика прекращается. Выходной код преобразователя снимается с прямых выходов секций счётчика нечётных ступеней преобразователя и инверсных выходов секций чётных ступеней. 2 н.п. ф-лы, 2 ил.

1. Способ аналого-цифрового преобразования последовательного счёта с промежуточным преобразованием входной величины во временной интервал, в котором с целью ускорения процесс кодирования разбивается на ряд этапов, каждый из которых реализуется своей ступенью и обеспечивает последовательное, начиная с первой, старшей, разрядной ступени формирование групп разрядов выходного кода, отличающийся тем, что с целью повышения точности на каждом этапе преобразования в момент достижения уравновешивающим сигналом уровня входного сигнала подсчёт тактовых импульсов соответствующей секцией счётчика прекращается, а очередной тактовый импульс осуществляет подготовку преобразователя к выполнению следующего этапа, при этом уменьшается величина и изменяется знак коэффициента наклона линейно изменяющегося уравновешивающего сигнала, а выход генератора тактовых импульсов отключается от счётного входа данной и подключается к счётному входу секции счётчика следующей ступени, выходной код преобразователя снимается с прямых выходов секций счётчика нечётных ступеней и с инверсных выходов секций чётных ступеней.

2. Аналого-цифровой преобразователь последовательного счёта с промежуточным преобразованием во временной интервал, содержащий интегратор (1), ключ обнуления (2), компаратор (3), источник опорных напряжений (4), генератор тактовых импульсов (5) и несколько разрядных ступеней, количество которых не превышает числа разрядов преобразователя, каждая из которых, начиная с первой, старшей, разрядной ступени, предназначена для формирования своей группы разрядов выходного кода и включает в себя соответствующую секцию двоичного счётчика (5, 6, 7), аналоговый ключ (8, 9, 10), R-S триггер режима (11, 12, 13), R-вход которого соединен с выходом трёхвходового элемента И управления режимом (14, 15, 16), S-вход R-S триггера режима (11) первой, старшей, разрядной ступени соединен с выходом двухвходового элемента И (17), а S-входы триггеров режима второй (12) и каждой последующей ступеней соединены с R-входами триггеров режима предшествующей ступени, R-вход R-S триггера режима последней, младшей, разрядной ступени (13) соединен с управляющим входом ключа обнуления (2), вход которого подключен к земляной шине, а выход - к выходу интегратора (1) и к первому входу компаратора (3), второй вход которого соединен со входом аналого-цифрового преобразователя, счётный вход каждой секции двоичного счётчика подключен к выходу трёхвходового элемента И управления счётом (18, 19, 20) соответствующей ступени, первые входы трёхвходовых элементов И управления счётом всех ступеней объединены с первым входом двухвходового элемента И (17), первыми входами элементов И управления режимами (14, 15, 16) и выходом генератора тактовых импульсов (5), второй вход двухвходового элемента И (17) подключен к входу «ПУСК», второй вход трёхвходового элемента И управления режимом каждой ступени соединен с вторым входом трёхвходового элемента И управления счётом, выходом R-S триггера режима и управляющим входом аналогового ключа соответствующей ступени, выходы аналоговых ключей соединены с входом интегратора (1), выход компаратора (3) соединен с третьими входами трёхвходовых элементов И управления режимом нечётных ступеней и третьими входами трёхвходовых элементов И управления счётом чётных ступеней, входы аналоговых ключей нечётных и чётных ступеней подключены к соответствующим выходам разнополярных опорных напряжений источника опорных напряжений (4), выход компаратора подключен к входу инвертора (21), соединенного выходом с третьими входами трёхвходовых элементов И управления режимом чётных ступеней и с третьими входами элементов И управления счётом нечётных ступеней, выходной код преобразователя снимается с прямых выходов соответствующих разрядов секций счётчика нечётных ступеней и с инверсных выходов разрядов секций счётчика чётных ступеней.

| Многоотсчетный цифровой вольтметр время-импульсного преобразования | 1978 |

|

SU748856A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU783979A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| US 20080204290 A1, 28.08.2008. | |||

Авторы

Даты

2023-10-24—Публикация

2023-02-03—Подача