Предлагаемое устройство относится к области аналого-цифровых преобразователей и может быть использовано в области связи, вычислительной и измерительной техники, а также в автрматизированнцх системах управления технологическими процессами и системах автоматизации научных исследований.

Известны следяыие аналого-цифровые преобразователи, содержащ 1е, как правило, элемент сравнения, на входы которого поступают входное и образUcsBoe напряжения, генератор тактовых импульсов, реверсивный счетчик ч ци(ро-аналоговый преобразователь, на выходе которого формируется образцо вое напряжение, а его ,вход связан с выходом реверсивного счетчика. Направление счета в реверсивном счетчи.ке зависит от ответов элемента сравнения l.

Недостатком этих устройств является большое время преобразования.

Известен также следяи ий аналогоци(5ровой преобразователь, содержащий генератор тактовых импульсов, аналоговое запоминающее устройство, элемент сравнения, ци ро-аналоговый

преобразователь, логический элемент, реверсивный счетчик, линию задержки и группу элементов И, у которого пер5 вый вход элемента сравнения соединён ,с выходом аналогового запоминающего устройства, вход которого соединен с источником входного сигнала;} второй вход элемента сравнения соединен с to выходом цифроаналогового:- преобразователя, входы которого соединены с выходами разрядов реверсивного счетчика; выход элемента сравнения соединен со входом логического элемента, . выходы которого соединены со входами реверсивного счетчика 2.

Недостатком этого устройства является большое время преобразования при малых и большая погрешность при боль2Q ших .изменениях входного сигнала.

Целью изобретения является повышение быстродействия и расширение дна- пазона изменений входного сигнала.

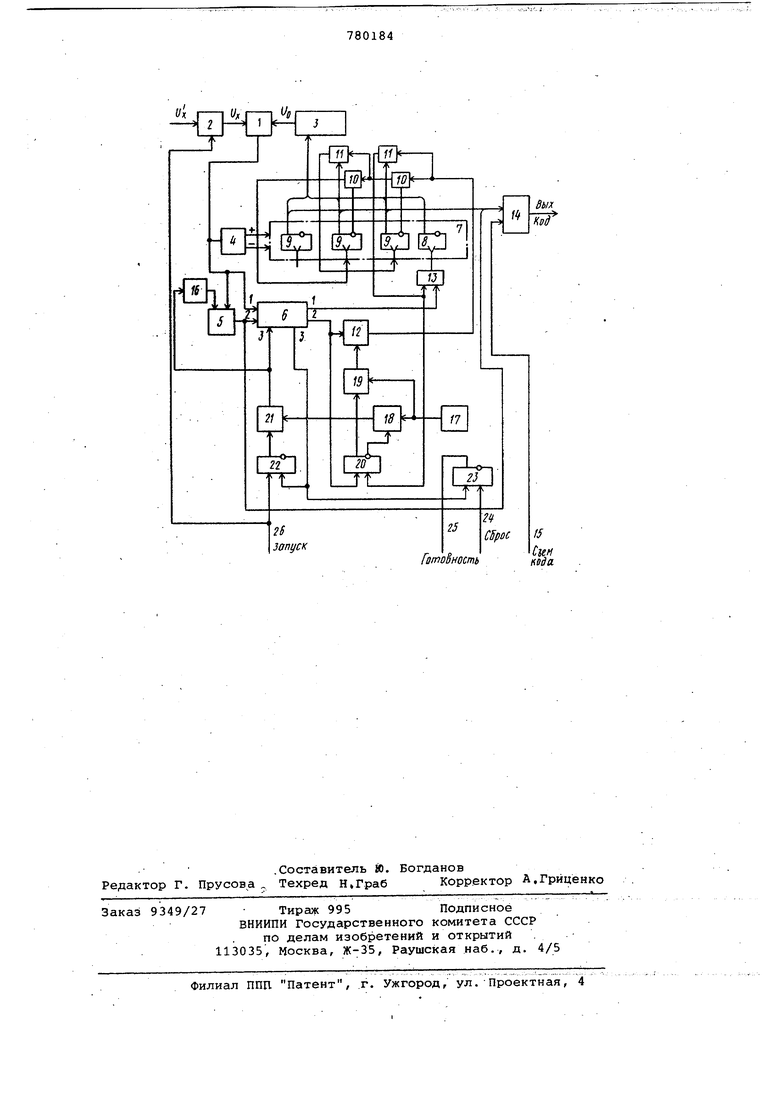

Поставленная цель достигается тем, 25 что в преобразователь, содержащий генератор тактовых импульсов, аналоговое запоминающее устройство, элемент, сравнения, цифpoiaнaлoгoвый; преобразователь, логический элемент, реверсивный счетчик .линию задержки и первую группу элементов И, у которого первый вход элемента сравнения соеди нен с выходом аналогового запоминающего устройства, вход которого соеди нен с источником входного сигнала; второй вход элемента сравнения соеди нен с выходом цифроаналогового: ripeобраэователя, входы которого соедине ны с выходами разрядов реверсивного очетчика; выход элемента сравнения соединен со. входом логического элемента, выходы которого соединены со входами реверсивного счетчика, допол нительно введены две группы элементов И, блок контроля, четыре триггера, триэлемента И и два элемента ИЛИ, причем выход элемента сравнения соединен с первьйм входом первого триггера и с входом блока кон троля, второй вход первого триггера соединен с выходом линии задержки; выход первого триггера соединен со вторым входом блока контроля и с пер вым входом младшего элемента И из второй группы, первые входы остальных элементов И второй группы соединены с выходами соответствующих триг геров реверсивного счетчика; третий вход блока контроля соединен с выходом первой схемы И и со входом линии задержки; первый выход блока контроля соединен со вторым входом первого элемента ИЛИ, второй выход блока кон троля соединен с первым входом вто-. рого элемента ИЛИ и с единичным входом второго триггера; третий выход блока контроля соединен .с нулевым вх дом третьего триггера и с единичным входом четвертого триггера, единичные выходы триггеров реверсивного счетчика, кроне старшего и младшего разрядов, соединены с первыми входам элементов И третьей группы; нулевые выходы триггеров реверсивного счбгтчи ка, кроме триггеров старшего и младшего разрядов, соединены с первыми входами элементов И первой группы; вторые входы элементов И из первой и третьей группы, соединенных с пред последним разрядом реверсивного счетчика, соединены с выходом второго элемента ИЛИ, вторые входы элементов И из первой и третьей группы, соединенные со следующими разрядами реверсивного счетчика, соединены с выходом:: элемента Ииз первой группы, первый вход которого соединен с более младшим разрядом; викод элемейта И из .первой группы, соединенно го со вторЕШ разрядом резверсиёногс счетчика, соединей со счетяым вкодом триггера второго рг13р.яда выход каждого элемента И из третьей группы соединен со счетнь№1 входом триггера соседнего более мт«адшего разряда; выход элемента И из третьей группы, соединенного с предпоследним разрядом соединен с первым входом первого элеsieHia ИЛИ, выход которого соединен со счетным входом младшего разряда реверсивного счетчика; первый в-ход первого элемента ИЛИ соединен с нулевым входом второго триггера; выход генератора тактовых импульсов соединен с первыми входами второго и третьего элементов И, второй вход второго элемента И соединен с нулевьт выходом второго триггера, а второй вход третьего элемента И соединен с единичным выходом второго триггера; выход третьего элемента И соединен со вторым входом второго элемента ИЛИ, а выход; второго элемента И соединен с первым входом первого элемента И, второй вход которого соединен с единичным выходом третьего триггера, вторые, входы всех элементов И второй группы соединены с.шиной съем кода, нулевой вход четвертого триггера соединен с ШИНОЙ сброс, а единичный выход четвертого Триггера соединён с шиной готовность ; единичный вход третьего триггера и управляющий вход аналогового запоминающего устройства; соединены с шиной запуск. Сущность изобретения поясняется чертежом, где изображена функциональная электрическая схема устройства. Следящий аналого-цифровой преобразователь, содержит элемент 1 сравнения, первый вход которого соединен с выходом Аналогового запоминающего устройства 2, на вход которого поступает входной сигнал. Второй вход элемента 1 сравнения соединен с выходом цифроаналогового: преобразователя 3. Выход элемента 1 сравнения соединен со входом логического элемента 4, с первым вхЪдом.первого триггера 5 и с первым входом блбка 6контроля. Выходы логического элемента 4 соединены со входами установки режима реверсййного счетчика 7, состоящего из триггеров 8 и 9, причем триггер 8 соответствует младшему разряду реверсивного .счётчика. Нулевые выходы триггеров 9, кроме старшего, соединены с первыми входами первой группы элементов 10 И. Единичные выходы триггеров 9, кроме старшего, соединены с первыми входами второй группы эле- . ментов 11 И. Вторые входц элементов 10 и 11 И соединенных с предпоследним разрядом 9 реверсивного счётчика 7/ соединены с выходом .первого элемента 12 ИЛИ. Вторые входы элементов 10 и 11 И, соединенных со следующими разрядами реверсивного счетчика, соединены сВЫХОДОМ элемента 10 И, первый вход которого соединен с более младшим разрядом. Выход элемента 10 И, соединенного со. вторым разрядом реверсивного счетчика, соединён do счетным входом триггера 9 второго разряда. Выход каждого элемента 11 И соединен со счетаым входом триггера 9 соседнего более младшего разряда. Выход элемента 11 И, соединенного с предпоследним разрядом, соединен с первым входом второго элемента 13 ИЛИ, выход которого соединен со счет ным входом триггера младшего разряда 8} второй вход второго элемента 13 ИЛИ соедйней спервым выходомблока 6 контроля. Выходы всех триггеров 8 и 9 реверсивного счетчика соединены .с, цифровыми входами .цифроаналогово-го -преобразователя. 3. Выходы всех лтрйггербв 9 соединены с первнгми входами соответствующих элементов 14 И третьей группы, Первый вход младшего элемента 14 И из третьей Группы соед нен с выходом первого триггера 5} вт рые входы йсех элементов 14 И третьей группы соединены с шино 5 съем йода. Второй вход триггера 5 . соединен с выходом линии 16 задержки Выход генератора 17 тактовых импульсов соединен с первыми входами пер- вого элемента 18 И и второго эл€ ента 19 И. Второй вход первого элемента 18 И соединен с нулевым выходом второго триггера 20, а второй вход BTOgioro элемента 19 И, соединен с единичном выходом второго триггера 20. Выход второго элемента 19 И, соединен со вторым входом первого элемента 12 ИЛИ, а выход первого эле мента 18 И соединен с первым входом третьего элемента 21 И, второй вход которого соединен с единичным выходом .третьего триггера 22. Выход третьего элемента 21 И соединен с третьим входом блока б контроля. Выход рервого триггера соединен со вторум ахоДом блока б контроля. Второй его Выход соединен с первым входом перво го элемента 12 ИЛИ и с единичным вхо дом второго триггера 20. Третий выход блока б контроля соединен с нулевым входом третьего триггера 22 и с единичным входом четвертого тригге ра 23. Нулевой вход триггера. 23 соединен с шиной 24 сброс, а единичный выход триггера 23 соединен с шиной 25 готовность. Единичный вход третьего триггера 22 соединен с управляющим входом аналогового запоминающего устройства.2 и с шиной 26 .запуск. Нулевой вход второго триггера 20 соединен с первым входом вто рого элемента 13 ИЛИ. Выход третьего элемента 21 И. соединен со входом линии 16 задержки. . .Элементы И первой и второй групп обеспечивают поразредный алгоритм преобразования. Дервый триггер 5 пр назначен для запоминания ответа эле мента 1 сравнения и для хранения зн чения младшего разряда числового эк вивалента входного сигнала. Второй триггер 20 управляет работой элемен та поразрядного преобразования, состоящего из первой и второй групп элементов 10 и 11 И. Третий триггер 22 разрешает работу блока б контрол Устройство работает следующим обазом. Перед началом работы сигнал наальной установки устанавливает пер-: ый 5/ второй 20, третий 23 и четверый 23 триггеры в нулевое состояние, реверсивный счетчик 7 - в любое неетное состояние. Рассмотрим несколько конкретных римеров, считая к.вант равным единие. . Пусть на реверсивном счетчике 7 аходится код 0...0101 5.С прихоом сигнала запуска третий триггер 22 устанавливается в 1, а аналоговое запоминающееустройство 2 запоминает текущее.значение сигнала, например равное 5,2. Так как значение сигнала больше образцового уробня (/) VQ ) . то схема сравнения выдает Сигнал 5, . по которому логический элемент 4 переводит реверсивный счетчик в режим сложения. Сигнал от генератора 17 тактовыхимпульсов, пройдя через первый 18 и третий 21 элемент И поступит на третий вход блока б контроля, который выдаст сигнал на первый выход, KOTopttii пройдя через второй элемент . 13 ИЛИ произведёт добавление единицы к реверсивному счетчику 7, получим код 0...0110. Кроме того, сигнал с выхода ли.нии 16 задержки перепишет значение ответа элемента сравйения « на первый .триггер 5, так как в данном случае на вьвсоде элемента сравнения сигнал , то первый триггер 5 будет установлен.в нулевое состояние. На следующем такте элемент сравнения выдаст сигнал S (V(j 55- Vt }, по кЪторОму логический элемент 4 переведет реверсивный счетчик 7 в режим вычитания. Так как ответ элемента сравнения изменился, то блок контроля 6 Выдаст сигнал на первый и третий выход. Сигнал с первого выхода блока контроля 6 произведет вычитание единицы из реверсивного счетчика, на котором зафиксируется код 0... .0101, а сигнал с третьего выхода блока контроля 6 переведет в единичное состояние триггер 23 и в нулевое состояние третий триггер 22, тем самым закончит преобразование. На триггере 5будет установлена 1. Формула изобретения Следящий аналого-цифровой преобразователь, содержащий генератор тактовых импульсов, ансшоговое запоминающее устройство, элемент сре внения, цифроаналоговый преобразователь, логический элемент, реверсивный счетчик, линию задержки и первую группу элементов И, причем первый вход элемента сравнения соединен с выходом аналогового запоминающего устройства, вход которого соединен с источником входного сигнала; второй вход элемента сравнения соединен с выходом цифро аналохового преобразователя, входы которого соединены с выходами разрядов реверсивного счетчикаj выход элемента сравнения соединен со входом логическогсэ элемента , выходи которого соединены со входами реверсивного счетчика, отличающий с я тем, что, с целью повышения быстродействия и расширения диапазона изменений входного сигнала, в устройство введены две группы элементов И, блок контроля, четыре триггера, три элемента И и два элемента ИЛИ, причем выход элемента сравнения соединен с первьв входом первого триггера и с первым входом блока контроля, второй вход первого триггера соединен с выходом линии задержки; выход первого т эиггера соединен со втбрым входом, блока контроля.и с первым входом младшего элемента И из второй группы,

первые входы остальных элементов И второй группы соединены с выходами соответствуищих триггеров реверсивного счетчика; третий вход блока контроля соединен с выходом первой схемы И и со входом.линии задержки; первый выход блока контроля соединен со вторым входом первого элемента ИЛИ, второй выход блока кбнтроля соединен с первым входом второго элемента ИЛИ и с единичным входом второго триггера; третий вйход блока контроля соединен с нулевым входом третьего триггера и с единичным вхоом четвертого триггера; единичные выходы триггеров реверсивного счетчика, кроме старшего и младшего разядов соединены с первыми входами элементов И третьей группы; нулевые выходы триггеров реверсивного счетика, кроме триггеров старшего и младего разрядов, соединены, с первыми входами элементов И первой группы; входы элементов И из первой и третьей группы, соединенных с предоследним разрядом реверсивного счетика, соединены с выходом второго лемента ИЛИ; вторые входы элементов з первой и третьей группы, соединен8

ных со следующими разрядами реверсивного счетчика, соединены с выходом элемента И из первой группы, первый вход которого соединен с более младшим разрядом; выход элемента И из перв.ой группы, соединенного со вторым разрядом реверсивного счетчика, соединен со счетным входом триггера второго разряда; выход каждого элемента И из третьей группы соединен со счетным входом триггера соседнего более младшего разряда; выход элемента И из третьей группы, соединенного с предпоследним разрядом, соединен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом младшего разряда реверсивного счетчика; первый вход первого элемента ИЛИ соединен с нулевым вхЬдом второго триггера; выход генератора такTOBbix импульсов соединен с первыми входами второго и третьего элементов И, второй вход второго элемента И соединен с нулевым выходом второго триггера, а второй вход третьего элемента-. И соединен с единичнымвыходом второго триггера; выход третьего элемента И соединен со вторым входом второго элемента ИЛИ, а выход второго элемента И соединен с первым входом первого элемента И, второй вход которого соедийен с единичным выходом третьего триггера} вторые входы всех элементов И второй группы соединены . с шиной съем кода, нулевой вход четвертого триri7epа соединен с шиной сброс, а единичный выход четвертого триггера соединен с шиной готовность ; единичный вход третьего триггера и управляющий вход аналогового запоминайщего устройства соединены с шиной запуск.

Источники информации, принятые во внимание при экспертизе

1.Смолов В. В., Смирнов Н. А. и др. Полупроводниковые кодирующие и декодирующие преобразователи напряжения, Л., Энергия, 1967, с. 135.

2.Авторское свидетельство СССР № 324639f кл. G 06 .J 3/00, 18.03.68 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1594691A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU924852A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU824431A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1228282A1 |

Авторы

Даты

1980-11-15—Публикация

1978-12-25—Подача