1. Область техники, к которой относится изобретение

Это изобретение относится к интегральным микросхемам, в частности к организации памяти и соответствующих путей доступа в интегральной микросхеме.

2. Описание предшествующего уровня техники

Компьютеры и другие типы электронных систем часто имеют иерархию памяти с несколькими различными уровнями. Эти уровни могут включать в себя энергонезависимую память (например, накопитель на жестком диске), оперативную память (RAM) и один или более уровней кэш-памяти. Системы на базе процессора могут содержать процессор, имеющий одно или более ядер, в котором каждое из одного или более ядер содержит одну или более кэш-памятей. Например, много процессоров содержат по меньшей мере одно ядро процессора, имеющее кэш команд и кэш данных, которые могут быть на вершине иерархии памяти. Кэш-память на вершине иерархии памяти может именоваться кэшем первого уровня (или L1). Много процессоров также содержат кэш второго уровня (или L2), который может совместно использоваться кэшами данных и команд ядра процессора и, кроме того, может совместно использоваться множеством ядер процессора в многоядерных процессорах.

Если некоторые из этих типов памятей, такие как кэши L2, обеспечиваются на интегральной схеме (ИС; IC), то они могут быть организованы в то, что известно как суперячейки памяти. Суперячейка памяти является 2-мерным массивом банков памяти (например, строки и столбцы банков памяти), которые совместно используют общий интерфейс (иногда называемый «точкой отвода»). В частности, при проектировании ИС каждый банк памяти может быть в виде ячейки, местоположение которой на кристалле ИС и соединения c другими заданными ячейками и/или другими функциональными блоками могут манипулироваться с помощью средства проектирования ИС. Суперячейка памяти является просто набором таких ячеек банков памяти, соединенных для формирования большой, единой ячейки памяти, которая также может быть расположена на ИС с помощью средства проектирования.

В такой суперячейке памяти заданный адрес отображается на один банк суперячейки. Информация, передаваемая суперячейке во время операции записи, может быть принята интерфейсом и затем направлена к местоположению в банке памяти, обозначенном адресом, который на нем отображен. Точно также при выполнении операции чтения информация может быть направлена из адресуемого местоположения в одном из банков памяти суперячейки к интерфейсу и, таким образом, к запрашивающему устройству.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Раскрыта интегральная схема. В одном варианте воплощения интегральная схема содержит множество запросчиков памяти и суперячейку памяти. Суперячейка памяти содержит множество банков памяти, каждый из которых формирует соответствующий диапазон отдельно адресуемых местоположений памяти, при этом суперячейка памяти организована во множество групп банков. Каждая группа из множества групп банков содержит подмножество множества банков памяти и соответствующий выделенный порт доступа. Кроме того, интегральная схема содержит коммутационный блок, подсоединенный между множеством запросчиков памяти и суперячейкой памяти. Коммутационный блок выполнен с возможностью в качестве реакции на запрос памяти со стороны заданного одного из множества запросчиков памяти соединять маршрут передачи данных между этим заданным запросчиком памяти и выделенным портом доступа конкретной одной из групп банков, к которой обращен запрос памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Другие аспекты изобретения станут очевидными после прочтения нижеследующего подробного описания со ссылками на прилагаемые чертежи, в которых:

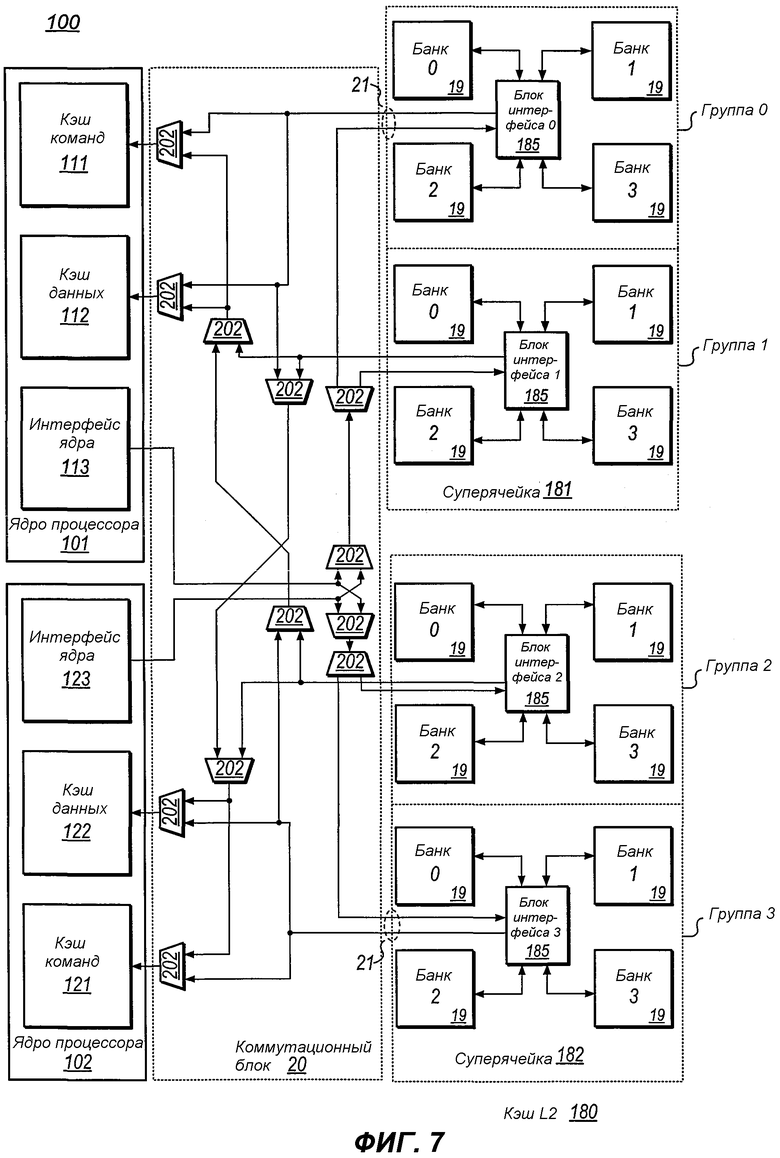

фиг.1 является блок-схемой одного варианта воплощения интегральной схемы;

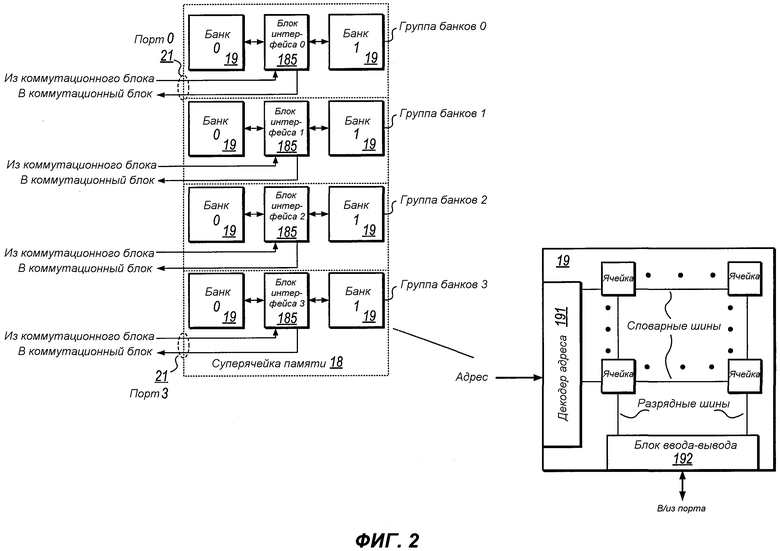

фиг.2 является блок-схемой одного варианта воплощения суперячейки памяти;

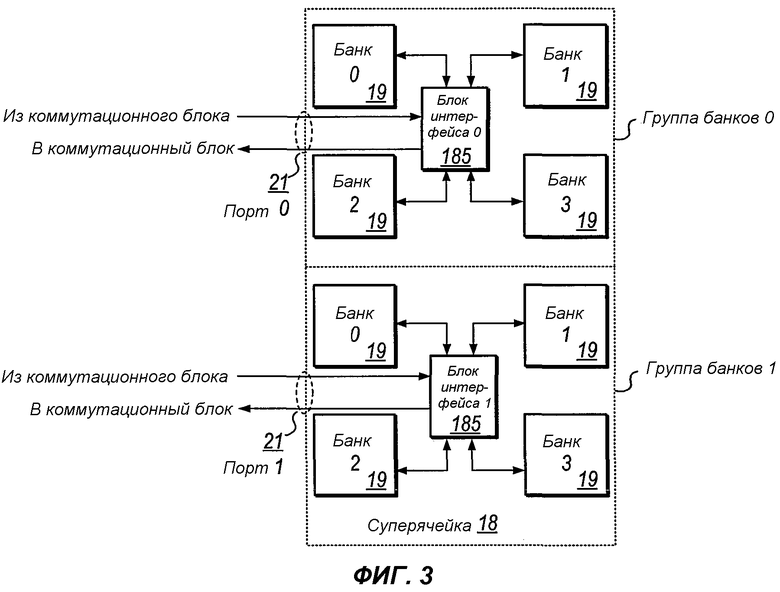

фиг.3 является блок-схемой другого варианта воплощения суперячейки памяти;

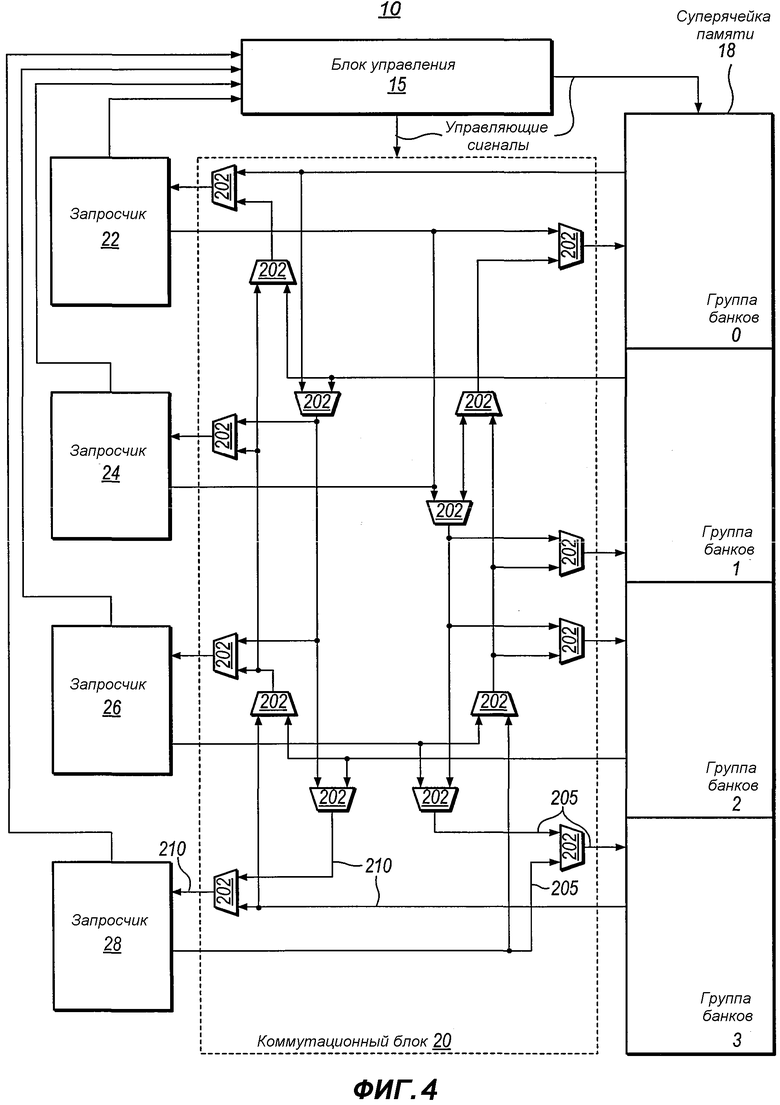

фиг.4 является блок-схемой интегральной схемы, более подробно изображающей один вариант воплощения коммутационного блока;

фиг.5 является блок-схемой, которая изображает дополнительные подробности одного варианта воплощения интегральной схемы;

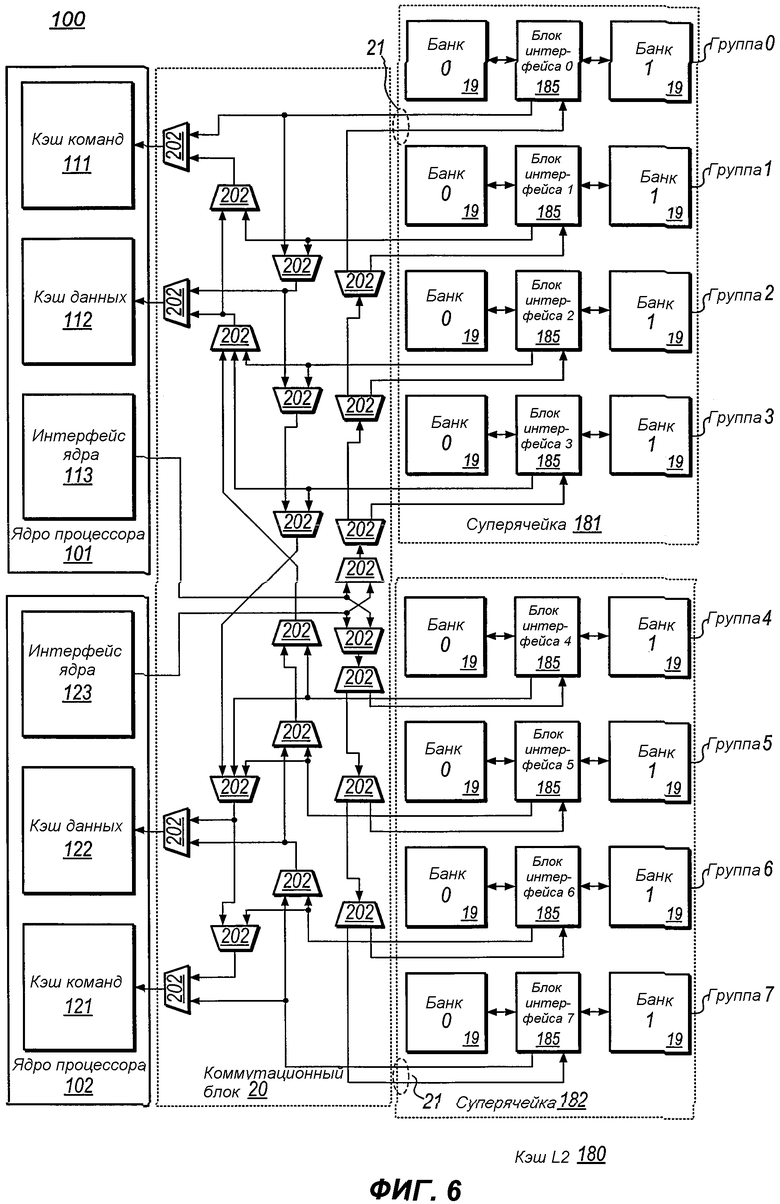

фиг.6 является блок-схемой, которая изображает один вариант воплощения интегральной схемы, которая содержит множество ядер процессора и пару суперячеек памяти; и

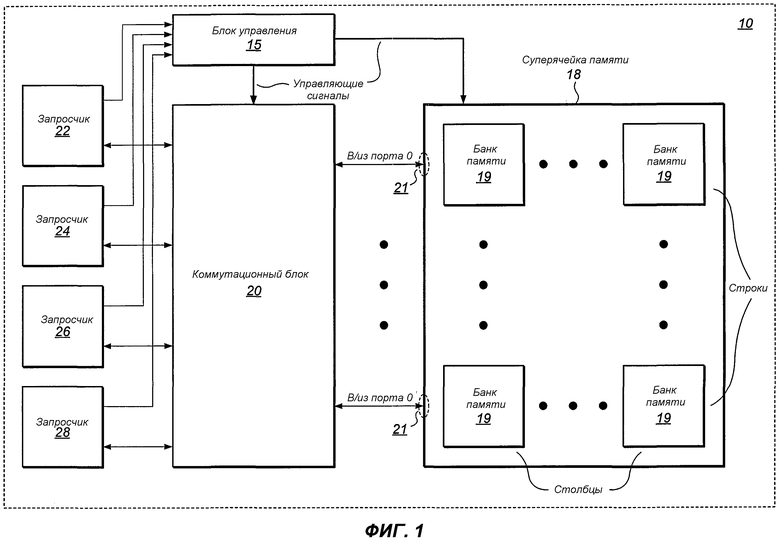

фиг.7 является блок-схемой, которая изображает другой вариант воплощения интегральной схемы, которая содержит множество ядер процессора и пару суперячеек памяти.

Хотя возможны различные изменения и альтернативные формы изобретения, его конкретные варианты воплощения приведены в качестве примера в чертежах и будут подробно описаны в настоящем документе. Следует, однако, понимать, что чертежи и описание к ним не ограничивают изобретение конкретной раскрытой формой, но, напротив, изобретение охватывает все изменения, эквиваленты и варианты в пределах сущности и объема настоящего изобретения, как определено прилагаемой формулой изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Обратимся теперь к фиг.1, где показана блок-схема одного варианта воплощения интегральной схемы. В изображенном варианте воплощения интегральная схема 10 (ИС; IC) содержит запросчики 22, 24, 26 и 28, каждый из которых соединен с блоком 15 управления и коммутационным блоком 20. ИС 10 также содержит суперячейку 18 памяти, соединенную с коммутационным блоком 20. В некоторых вариантах воплощения различные компоненты ИС 10, показанные на фиг.1, могут быть реализованы на одном кристалле ИС. В показанном варианте воплощения коммутационный блок 20 физически расположен между (и вне) суперячейкой 18 памяти и запросчиками 22-28.

Каждый из запросчиков 22-28 представляет собой любую подсистему или устройство, которое требует доступа к памяти, являющейся внешней по отношению к нему, например суперячейке 18 памяти. Такой доступ может содержать доступ для чтения, доступ для записи, либо и для того и другого. В некоторых вариантах воплощения каждый из запросчиков 22-28 может быть идентичным функциональным блоком (например, ядрами симметричного многоядерного процессора, включающими, например, кэш команд и кэш данных и т.д.). В других вариантах воплощения по меньшей мере один из запросчиков 22-28 может отличаться от других запросчиков (например, ядра в асимметричном многоядерном процессоре). Конкретное число запросчиков может быть разным в разных вариантах воплощения и может быть больше или меньше, чем показанное здесь. Возможны и предусмотрены варианты воплощения только с одним запросчиком.

В показанном варианте воплощения суперячейка 18 памяти содержит множество банков 19 памяти. Как обсуждалось выше, во время этапа проектирования ИС каждый из банков памяти может быть задан как ячейка, которой можно манипулировать с помощью средства проектирования. На концептуальном уровне аналогично может быть задано, что суперячейка 18 памяти позволяет манипулирование с помощью средств проектирования ее местоположения и соединений с другими ячейками или функциональными блоками. Суперячейка 18 памяти в показанном варианте воплощения содержит двумерный массив банков 19 памяти. Их размещение таково, что по меньшей мере два банка 19 памяти расположены вдоль первого направления (например, строки), и по меньшей мере два банка 19 памяти расположены вдоль второго направления (например, столбцы). Конкретное число банков 19 памяти вдоль каждого направления двумерного массива может быть разным в разных вариантах воплощения. Каждый банк 19 памяти может формировать соответствующий диапазон отдельно адресуемых ячеек памяти. Каждый из запросов доступа к памяти может обращаться к одной или более из этих отдельно адресуемых ячеек памяти.

Суперячейка 18 памяти на фиг.1 соединена с коммутационным блоком 20 через порты 21 (иногда называемые «точками отвода»), обозначенные как порт 0 и порт 1 в этом варианте воплощения. Как обсуждается ниже, множество банков 19 памяти, показанных на фиг.1, может быть организовано в отдельные группы банков. Передача данных (термин "данные", использующийся здесь, подразумевается включающим в себя также машинные команды) в или из банков заданной группы банков может происходить исключительно через порт 21, который соответствует этой конкретной группе банков, в то время как передача данных в/из другой группы банков происходит через другой порт, что также обсуждается более детально ниже.

Каждый из запросчиков 22-28 в показанном варианте воплощения выполнен с возможностью подачи в блок 15 управления сигналов, обозначающих запрос на доступ к суперячейке 18 памяти. При подаче запроса на доступ к суперячейке 18 памяти конкретный запросчик 22-28 может предоставлять информацию блоку 15 управления, указывающую адрес, по которому нужно осуществить доступ, а также указывающую, является ли запрос запросом чтения или запросом записи. Блок 15 управления выполнен с возможностью в ответ определять маршрут для передачи данных между местоположением в памяти, определенным в запросе, и соответствующим запросчиком. В частности, блок 15 управления может быть выполнен с возможностью определять различные сегменты в коммутационном блоке 20 для формирования маршрута между портом суперячейки 18 памяти, соответствующим запрашиваемому местоположению памяти, и соответствующим запросчиком. В качестве реакции на прием управляющих сигналов от блока 15 управления коммутационный блок 20 выполнен с возможностью выбора сегментов, которые формируют маршрут между запросчиком и портом суперячейки 18 памяти, соответствующим запросу.

Блок 15 управления может также подавать некоторые управляющие сигналы непосредственно в группу банков, которая содержит запрашиваемое местоположение памяти. Такие управляющие сигналы могут содержать сигналы разрешения (например, разрешения чтения, разрешения записи) и сигналы выбора (например, для выбора банка и адреса, соответствующего запросу). В ситуациях, когда приняты несколько ожидающих выполнения запросов доступа, блок 15 управления может выполнять функции установления приоритетов для определения порядка выполнения запросов.

Обратимся теперь к фиг.2, где показана блок-схема одного варианта воплощения суперячейки 18 памяти. Фиг.2 также изображает образец одного из множества банков 19 памяти. В показанном варианте воплощения суперячейка 18 памяти содержит восемь банков 19 памяти, которые организованы в четыре строки и два столбца. Кроме того, суперячейка 18 памяти организована в виде четырех блоков памяти, обозначенных здесь как группа 0 банков, группа 1 банков, группа 2 банков и группа 3 банков. Каждая из этих групп банков включает в себя соответствующий порт 21, соединенный с соответствующим блоком 185 интерфейса (I/F), например, группа 0 банков содержит порт 0, который соединен с блоком 0 интерфейса, и т.д. Каждый порт 21 заданной группы памяти является единственным для банков 19 памяти этой группы. Аналогично каждый блок 185 интерфейса заданной группы памяти является единственным для банков 19 памяти этой группы. Например, передача данных в или из любого из банков памяти группы 0 банков происходит через порт 0 и блок 0 интерфейса, а передача данных в или из любого из банков памяти группы 3 банков происходит через порт 3 и блок 3 интерфейса. Каждый из блоков 185 интерфейса обеспечивает интерфейс для передачи данных между банками памяти этой конкретной группы банков и соответствующим портом 21 этой конкретной группы памяти. Каждый блок 185 интерфейса может содержать схему коммутации (например, мультиплексоры, демультиплексоры и т.д.), выполненную с возможностью направлять заданные между заданным банком 19 памяти и соответствующим портом 21 во время доступа к местоположению в этом банке. В некоторых вариантах воплощения каждый блок 185 интерфейса может также подавать информацию об адресах и/или другие управляющие сигналы в банки 19 памяти его конкретной группы банков. Однако также возможны и предусмотрены варианты воплощения, где информация об адресах и управляющие сигналы предоставляются другими функциональными блоками (например, напрямую блоком 15 управления по фиг.1).

В показанном варианте воплощения каждый из банков 19 памяти заданной группы банков физически находится ближе к своему соответствующему порту 21, чем к портам 21, соответствующим другим группам банков. Например, банки 19 памяти группы 0 банков физически находятся ближе к порту 0, чем к портам, соответствующим любой из групп 1-3 банков. В отличие от вариантов воплощения, в которых может быть обеспечен один порт для суперячейки памяти (и, таким образом, один блок интерфейса порта), расположение, показанное на фиг.2, может минимизировать расстояние, на которое передаются данные в/из данного банка 19 памяти в пределах суперячейки 18 памяти из/в внешнего источника. Также отметим, что электрическая схема, образующая каждый блок 185 интерфейса, может физически располагаться в центральной части между банками 19 памяти данной группы банков.

При реализации в интегральной схеме, такой как ИС 10, каждый порт 21 суперячейки 18 памяти может соединяться для приема данных от коммутационного блока 20 по первому маршруту и соединяться для подачи данных в коммутационный блок по второму маршруту (то есть в вариантах воплощения, в которых используются однонаправленные маршруты для записи данных и чтения данных). Соответственно, как обсуждается более подробно ниже, это размещение может позволить одновременные операции чтения и записи, в которых информация записывается в местоположение памяти в первой группе банков и считывается из местоположения памяти во второй группе банков.

Как отмечалось выше, фиг.2 также изображает один вариант воплощения типичного банка 19 памяти. Другие типы банков памяти также возможны и предусмотрены для реализации в суперячейке 18 памяти. В показанном варианте воплощения банк 19 памяти содержит множество одноразрядных ячеек памяти, расположенных в массиве строк и столбцов. Одноразрядные ячейки памяти в заданной строке соединены друг с другом словарными шинами, а одноразрядные ячейки памяти в заданном столбце соединены друг с другом разрядными шинами. В показанном варианте воплощения каждая одноразрядная ячейка памяти соединена с одной разрядной шиной, хотя возможны и предусмотрены варианты воплощения, в которых одноразрядные ячейки памяти соединены с двухразрядными шинами (например, для передачи основных и дополнительных данных).

Банк 19 памяти в показанном варианте воплощения содержит декодер 191 адреса и блок 192 ввода-вывода (I/O). Декодер 191 адреса соединен для приема адреса от внешнего источника (например, от блока 185 интерфейса или от блока 15 управления согласно вариантам воплощения, которые обсуждались выше) и выполнен с возможностью декодировать принятый адрес. Блок 192 ввода-вывода может содержать различные электрические схемы для считывания информации из ячеек памяти и/или записи информации в ячейки памяти. Например, в одном варианте воплощения блок 192 ввода-вывода содержит множество усилителей считывания, каждый из которых соединен с соответствующей разрядной шиной. Блок 192 ввода-вывода может также содержать множество задающих контуров, каждый из которых соединен с соответствующей разрядной шиной.

В показанном варианте воплощения декодер 191 адреса выполнен с возможностью декодирования адреса для активации словарной шины, соответствующей ему. При активации заданная словарная шина может сделать ячейки памяти, соединенные с ней, прозрачными для их соответствующих разрядных шин (то есть выбрать ячейки памяти декодируемого адреса). Во время операций чтения данные, хранящиеся в выбранных ячейках памяти, могут быть считаны усилителями считывания из состава блока 192 ввода-вывода и переданы из банка 19 памяти в соответствующий блок 185 интерфейса (и, таким образом, также на соответствующий порт 21). Во время операций записи данные могут быть приняты задающими контурами в блоке 192 ввода-вывода и, таким образом, записаны в выбранные ячейки памяти. Когда операция чтения или записи завершена, словарная шина выбранных ячеек памяти деактивируется, и, таким образом, данные, только что записанные в ячейки памяти, сохраняются.

Фиг.3 является блок-схемой другого варианта воплощения суперячейки 18 памяти. В этом конкретном варианте воплощения суперячейка 18 памяти содержит две группы банков вместо четырех, показанных в варианте воплощения по фиг.2. Соответственно суперячейка 18 памяти по фиг.3 содержит два порта 21 и два блока 185 интерфейса. Каждая из групп банков в этом конкретном варианте воплощения содержит четыре банка 19 памяти.

Вообще говоря, суперячейки 18 памяти могут быть реализованы в самых различных конфигурациях в соответствии с настоящим описанием изобретения. Каждая суперячейка памяти может содержать множество групп банков, каждая из которых содержит множество банков памяти. Каждая группа банков может включать в себя порт и блок интерфейса, каждый из которых предназначен исключительно для этой конкретной группы банков (то есть заданный порт предназначен для передачи данных, записываемых в или считываемых из местоположения в соответствующей группе банков (то есть не передает данные в/из других групп банков)). Кроме того, банки памяти определенной группы банков могут быть физически ближе к порту, соответствующему этой группе банков, чем к портам, соответствующим другим группам банков. Это может уменьшить расстояние, на которое передаются данные между определенным банком памяти в группе банков и портом этой группы банков, и, таким образом, общее расстояние до заданного запросчика памяти. Сокращение общей величины расстояния, на которое передаются данные, может привести к относительно более низкому энергопотреблению, а также может уменьшить задержку, связанную с передачей данных.

Фиг.4 является схемой ИС 10, которая более подробно изображает один вариант воплощения коммутационного блока 20. Элементы по фиг.4, которые соответствуют таковым на чертежах, которые обсуждались выше, нумеруются для простоты идентично. Следует отметить, что суперячейка 18 памяти, как показано на фиг.4, среди прочего может быть реализована согласно конфигурации по фиг.2 или конфигурации по фиг.3.

В показанном варианте воплощения коммутационный блок 20 содержит множество схем 202 выборки и, кроме того, содержит множество сегментов 205 и 210. Для простоты обозначены только типичные образцы сегментов. Сегменты 205 образуют первое подмножество множества сегментов и применяются для передачи информации (записи данных) от запросчиков 22-28 в выбранную группу банков суперячейки 18 памяти. Сегменты 210 образуют второе подмножество множества сегментов и применяются для передачи информации (чтения данных) из выбранной группы банков суперячейки 18 памяти одному из запросчиков 22-28. Таким образом, сегменты 205 являются однонаправленными в первом направлении, в то время как сегменты 210 являются однонаправленными во втором направлении. Каждый сегмент может содержать множество сигнальных шин (например, проводников), на которые подаются биты информации для передачи данных между суперячейкой 18 памяти и одним из запросчиков 22-28.

Каждая схема 202 выбора в этом варианте воплощения выполнена с возможностью электрически соединять конкретные сегменты из множества сегментов с по меньшей мере одним другим сегментом из множеством сегментов. В показанном варианте воплощения каждая схема 202 выбора выполнена с возможностью выполнять мультиплексирующую функцию. В частности, каждая из схем 202 выбора в этом варианте воплощения выполнена с возможностью выбирать один из двух сегментов для электрического соединения с другим сегментом. Вообще говоря, могут быть реализованы различные варианты воплощения коммутационного блока 20 с использованием схем 202 выбора, которые выполняют мультиплексирующую функцию, демультиплексирующую функцию, функцию коммутирования или их различные комбинации. Схемы 202 выбора, которые выполняют мультиплексирующую функцию, могут соединять два или более входных сегментов с третьим (выходным) сегментом. Схемы 202 выбора, которые выполняют демультиплексирующую функцию, могут соединять входной сегмент с одним из двух или более выходных сегментов. Схемы 202 выбора, которые выполняют функцию коммутирования, при включении могут соединять входной сегмент с выходным сегментом.

Хотя это явно не показано здесь, каждая схема 202 выбора в показанном варианте воплощения соединена для приема одного или более управляющих сигналов от блока 15 управления. В частности, каждая схема 202 выбора в этом варианте воплощения соединена для приема, по меньшей мере, сигнала выбора, который указывает, какой из двух соответствующих входных сегментов должен быть электрически соединен с соответствующим выходным сегментом. В некоторых вариантах воплощения каждая схема 202 выбора может также быть соединена для приема сигнала включения. Сигнал включения может приводиться в состояние "истина" для включения схемы 202 выбора, когда она должна использоваться для формирования маршрута между одним из запросчиков 22-28 и одной из групп банков 0-3 суперячейки 18 памяти. Сигнал включения, подаваемый на схему 202 выбора, может выводиться из состояния "истина", когда эта схема выбора не используется. При отключении схема 202 выбора может привести к переходу сигнальных шин выходного сегмента в высокоимпедансное состояние.

Так как показанный вариант воплощения делит множество сегментов на отдельные первое и второе подмножества (то есть на первое подмножество, содержащее сегменты 205, и второе подмножество, содержащее сегменты 210), то могут поддерживаться одновременные чтение и запись. Например, данные от запросчика 22 могут записываться в некое мостоположение в группе 0 банков, в то время как одновременно данные могут считываться запросчиком 28 из группы банков 3. Одновременные чтение и запись, задействующие одну и ту же группу банков и/или один и тот же запросчик, также могут поддерживаться в некоторых вариантах воплощения. Например, в таком варианте воплощения запросчик 24 может записывать данные в местоположение в группе 1 банков, при этом одновременно считывая данные из местоположения в группе 2 банков. В другом примере один из таких вариантов воплощения может поддерживать запись запросчиком 26 данных в первое местоположение группы 2 банков, в то время как запросчик 24 одновременно считывает данные из второго местоположения по другому адресу группы 2 банков. Как отмечалось выше, блок 15 управления может быть выполнен с возможностью выполнять функции установления приоритетов и, таким образом, может планировать одновременные доступы для чтения и записи в вариантах воплощения, где эти одновременные доступы поддерживаются. Блок 15 управления может также быть выполнен с возможностью предотвращения одновременных чтений и записей в определенных ситуациях (например, если имеется запрос на чтение и запись по одному и тому же местоположению памяти).

Фиг.5 является блок-схемой, изображающей примеры выбора маршрутов между запросчиком и группой банков памяти. Пример, показанный здесь, основан на варианте воплощения по фиг.4, и, таким образом, элементы, показанные на фиг.5, пронумерованы также, как соответствующие элементы на фиг.4. Маршруты, показанные в этом примере, содержат сегменты, которые обозначены пунктирными линиями и соответствующими номерами позиций. Другие сегменты, показанные как сплошные линии без соответствующих номеров позиций, не являются частью обозначенных маршрутов этого примера.

В примере, показанном на фиг.5, запросчик 22 соединен с группой 0 банков через первый маршрут, образуемый сегментами 205D и 205E. Соответственно запросчик 22 соединен для записи информации в местоположение памяти в группу 0 банков. В этом же примере запросчик 26 соединен с группой 2 банков вторым маршрутом, образуемым сегментами 210E, 210F и 210G. Соответственно запросчик 26 в этом примере соединен для считывания данных из группы 2 банков. Эти маршруты могут иметь показанную конфигурацию для обеспечения записи запросчиком 22 данных в местоположение в группе 0 банков и одновременного чтения запросчиком 26 данных из местоположения в группе 2 банков. Возможность считывать данные из первого местоположения суперячейки 18 памяти при одновременной записи в нее данных по другому местоположению может обеспечить эффективную общую работу. Однако маршруты, показанные в этом примере, могут быть сконфигурированы для обеспечения возможности проведения вышеупомянутых операций чтения и записи в различные моменты времени, не одновременно.

Пример, показанный на фиг.5, таков, что при передаче данных от запросчика 22 к порту 0 группы 0 банков данные передаются только по тем сегментам 205, которые электрически соединяют запросчик 22 с портом 0. Аналогично показанный пример таков, что при передаче данных из группы 2 банков запросчику 26 данные передаются только по тем сегментам 210, которые электрически соединяют порт 2 с запросчиком 26. Вообще, когда заданный запросчик должен записать данные в местоположение в суперячейке 18 памяти в показанном варианте воплощения, данные передаются только по тем сегментам 205, которые электрически соединены между запросчиком-инициатором и портом, соответствующим местоположению в памяти, в которое должны быть записаны данные. Точно так же, когда заданный запросчик должен считать данные из некоего местоположения какому-то адресу в суперячейке 18 памяти в показанном варианте воплощения, данные передаются только по тем сегментам 210, которые электрически соединяют порт, соответствующий местоположению в памяти, из которого должны быть считаны данные, с входом запросчика-инициатора. В результате может быть обеспечен относительно короткий маршрут передачи данных, таким образом получая в результате более короткое расстояние, по которому передаются сигналы, соответствующие данным. Это, в свою очередь, может привести к сравнительно низкому энергопотреблению.

В общем, схема 20 коммутации выполнена с возможностью предписывать контекстным схемам 202 выбора выбирать различные сегменты из сегментов 205, чтобы сделать возможными операции записи из любого из запросчиков 22-28 в любую из групп 0-3 банков. Точно также схема 20 коммутации выполнена с возможностью предписывать контекстным схемам 202 выбора выбирать различные сегменты 210, чтобы сделать возможными операции чтения из любой из групп 0-3 банков любым из запросчиков 22-28. Выбор конкретных сегментов может быть выполнен под руководством блока 15 управления в соответствии с типом запроса (чтение или запись) и запрошенным местоположением. Когда нет никаких конфликтов (например, нет никаких попыток одновременно читать и записывать в один и тот же адрес), могут выполняться одновременные операции чтения и записи.

Обратимся теперь к фиг.6, где показана блок-схема одного варианта воплощения процессорной системы, реализованной на интегральной схеме и имеющей множество ядер процессора и суперячеек памяти. В показанном варианте воплощения процессор 100 содержит первое ядро 101 процессора и второе ядро 102 процессора. Каждое из ядер 101 и 102 процессора соединено с коммутационным блоком 20. Коммутационный блок 20, в свою очередь, соединен с кэшем 180 L2, который сформирован совместно суперячейками 181 и 182 памяти. Схема, формирующая коммутационный блок 20, может быть физически расположена между кэшем 180 L2 и парой ядер процессора, показанных на фигуре. Процессор 100 может также содержать блок управления, подобный блоку 15 управления согласно вариантам воплощения, описанным выше, хотя это и не показано здесь для простоты.

Ядро 101 процессора содержит кэш 111 команд, кэш 112 данных и интерфейс 113 ядра. Точно также ядро 102 процессора содержит кэш 121 команд, кэш 122 данных и интерфейс 123 ядра. В этом варианте воплощения кэши команд и данных ядер 101 и 102 процессора образуют кэши уровня 1 (L1). В этом варианте воплощения интерфейсы 113 и 123 ядер являются кэшами обратной записи, выполненными с возможностью записи информации из соответствующих кэшей L1 в кэш 180 L2. Интерфейсы 113 и 123 ядра могут также содержать дополнительную функциональность интерфейса, которая обеспечивает связь между соответствующими им ядрами процессора и другими функциональными блоками.

В этом конкретном варианте воплощения, как обсуждалось выше, ядра 101 и 102 процессора выполняют роль запросчиков. В роли запросчиков ядра 101 и 102 процессора могут принимать данные из суперячеек 181 и 182 памяти через вводы к их соответствующим кэшам команд и данных. Информация может выводиться из ядер 101 и 102 процессора в этом варианте воплощения через их соответствующие интерфейсы ядер. Однако следует отметить, что возможны и предусмотрены варианты воплощения, в которых каждый кэш команд, кэш данных и интерфейс ядра, показанные на чертеже, могут самостоятельно выполнять роль запросчиков. Также, когда эти блоки выполняют роль запросчиков, они могут инициировать запросы на доступ, которые приводят к передаче данных в кэш 180 L2 и/или получению данных из кэша 180 L2.

Как указывалось выше, в варианте воплощения, показанном на фиг.6, кэш 180 L2 содержит первую суперячейку 181 памяти и вторую суперячейку 182 памяти. Каждая из суперячеек 181 и 182 памяти, показанных на фиг.6, скомпонована аналогично варианту воплощения суперячейки 18 памяти, показанному на фиг.2. То есть каждая из суперячеек 181 и 182 памяти содержит четыре группы банков из двух банков памяти каждый, где каждая группа банков включает в себя ее собственный порт 21 памяти и ее собственный блок 185 интерфейса.

Строка кэша в показанном варианте воплощения может быть сохранена в обеих суперячейках 181 и 182 памяти в этом варианте воплощения (например, для 64-байтовой строки кэша, 32 байта данной строки кэша могут быть сохранены в соответствующем банке памяти суперячейки 181 памяти, а 32 остающихся байта могут быть сохранены в соответствующем банке памяти суперячейки 182 памяти). Соответственно процессорная система 100 может поддерживать запись в местоположение памяти группы банков в суперячейке 181 памяти одновременно с записью в местоположение памяти группы банков в суперячейке 182 памяти. Точно также процессор 100 может также выполнять чтение из местоположения памяти в группе банков суперячейки 181 памяти одновременно с чтением из местоположения памяти в группе банков суперячейки 182 памяти. В различных вариантах воплощения процессорная система 100 может позволять одновременное чтение и запись различных строк кэша. Таким образом, этот вариант воплощения процессора 100 может поддерживать две операции чтения (одна из суперячейки 181 памяти и одна из суперячейки 182 памяти для первой строки кэша), которые выполняются одновременно с двумя операциями записи (одна в суперячейку 181 памяти и одна в суперячейку 182 памяти для второй строки кэша).

Фиг.7 является блок-схемой, изображающей другой вариант воплощения процессорной системы. В этом конкретном варианте воплощения каждая из суперячеек 181 и 182 памяти кэша 180 L2 воплощена согласно конфигурации по фиг.3, которая обсуждалась выше. Каждая группа банков содержит соответствующий порт 21 и соответствующий блок 185 интерфейса. Как и в варианте воплощения, который обсуждался выше, передача строк кэша может включать в себя одновременное чтение из обеих суперячеек 181 и 182 памяти или запись в суперячейки 181 и 182 памяти.

Хотя настоящее изобретение было описано со ссылкой на конкретные варианты воплощения, понятно, что варианты воплощения являются иллюстративными и что объем изобретения не является настолько ограниченным. Возможны любые вариации, изменения, дополнения и усовершенствования описанных вариантов воплощения. Эти вариации, изменения, дополнения и усовершенствования могут попадать в рамки объема изобретения, определяемого нижеследующей формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТОБРАЖЕНИЕ ВСТРОЕННОГО АДРЕСА ЕСС | 2014 |

|

RU2644529C2 |

| УПРАВЛЕНИЕ ВРЕМЕНЕМ ОБРАЩЕНИЯ К ПАМЯТИ | 2014 |

|

RU2618938C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБЕСПЕЧЕНИЯ ПОТОКОВ НА ОСНОВЕ ИДЕНТИФИКАТОРА ЧЕРЕЗ ШИНУ PCI EXPRESS | 2010 |

|

RU2509348C2 |

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| УСТАНОВКА, СПОСОБ И СИСТЕМА КЭШИРОВАНИЯ | 2008 |

|

RU2483347C2 |

| ПАРАЛЛЕЛЬНАЯ СОРТИРОВКА СЛИЯНИЕМ | 2014 |

|

RU2667385C2 |

| МЕХАНИЗМ ЗАПРОСА ПОЗДНЕЙ БЛОКИРОВКИ ДЛЯ ПРОПУСКА АППАРАТНОЙ БЛОКИРОВКИ (HLE) | 2008 |

|

RU2501071C2 |

| УСОВЕРШЕНСТВОВАННОЕ УСТРОЙСТВО ОБРАБОТКИ СЕТЕВОЙ СТАТИСТИКИ | 2005 |

|

RU2346399C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБЕСПЕЧЕНИЯ ПОТОКОВ НА ОСНОВЕ ИДЕНТИФИКАТОРА ЧЕРЕЗ ШИНУ PCI EXPRESS | 2010 |

|

RU2559727C2 |

| УПРАВЛЕНИЕ ПАМЯТЬЮ | 2014 |

|

RU2643499C2 |

Изобретение относится к организации памяти и соответствующих путей доступа в интегральной микросхеме. Технический результат заключается в обеспечении соединения маршрута передачи множества запросчиков памяти, таким образом, что были соединены конкретный запросчик памяти и выделенный порт доступа конкретной одной из групп банков, к которой обращен запрос памяти. Интегральная схема содержит множество запросчиков памяти и суперячейку памяти. Суперячейка памяти содержит множество банков памяти, каждый из которых формирует соответствующий диапазон отдельно адресуемых ячеек памяти, при этом суперячейка памяти состоит из множества групп банков. Каждая из множества групп банков содержит подмножество множества банков памяти и соответствующий выделенный порт доступа. Кроме того, интегральная схема содержит коммутатор, соединенный между множеством запросчиков памяти и суперячейкой памяти. Коммутатор выполнен с возможностью в качестве реакции на запрос памяти со стороны конкретного одного из запросчиков множества запросчиков памяти соединять маршрут передачи данных между этим конкретным запросчиком памяти и выделенным портом доступа конкретной одной из групп банков, к которой обращен запрос памяти. 2 н. и 17 з.п. ф-лы, 7 ил.

1. Интегральная схема, содержащая

множество запросчиков памяти;

суперячейку памяти, которая содержит множество банков памяти, каждый из которых формирует соответствующий диапазон отдельно адресуемых местоположений памяти, при этом суперячейка памяти организована во множество групп банков, при этом каждая из множества групп банков содержит подмножество множества банков памяти и соответствующий выделенный порт доступа, при этом соответствующий выделенный порт доступа для каждой из множества групп банков физически расположен по центру между банками памяти этой группы;

коммутационный блок, подключенный между множеством запросчиков памяти и суперячейкой памяти, при этом коммутационный блок выполнен с возможностью в качестве реакции на запрос памяти со стороны конкретного одного из множества запросчиков памяти соединять соответствующий маршрут передачи данных между этим конкретным запросчиком памяти и выделенным портом доступа конкретной одной из групп банков, к которой обращен запрос памяти.

2. Интегральная схема по п.1, в которой каждый банк памяти из множества банков памяти содержит декодер адреса.

3. Интегральная схема по п.1, в которой коммутационный блок содержит множество сегментов и множество схем выбора, при этом каждая из множества схем выбора выполнена с возможностью электрически соединять конкретные сегменты из множества сегментов с по меньшей мере одним другим сегментом из множества сегментов для формирования маршрута между конкретным запросчиком и либо первым, либо вторым портом доступа, при этом первое подмножество множества сегментов выполнено с возможностью передавать данные в суперячейку памяти, а второе подмножество множества сегментов выполнено с возможностью передавать данные из суперячейки памяти.

4. Интегральная схема по п.1, в которой во время запроса записи, инициированного конкретным запросчиком для записи данных в местоположение памяти первой группы банков, данные из этого кокретного запросчика передаются по маршруту к первому порту доступа без передачи данных по сегментам, соединенным со вторым портом доступа.

5. Интегральная схема по п.1, в которой во время запроса чтения, инициированного конкретным запросчиком для считывания данных из местоположения памяти первой группы банков, данные передаются по маршруту от первого порта доступа к этому конкретному запросчику, без передачи данных по сегментам, соединенным с другими запросчиками из множества запросчиков.

6. Интегральная схема по п.1, в которой суперячейка памяти сконфигурирована так, что данные, которые соответствуют запросам, обращенным к местоположениям памяти первого подмножества множества банков памяти, подаются исключительно через первый порт доступа, и так, что данные, которые соответствуют запросам, обращенным к местоположениям памяти второго подмножества множества банков памяти, подаются исключительно через второй порт доступа, при этом коммутационный блок выполнен с возможностью, в ответ на запрос памяти со стороны конкретного запросчика памяти из множества запросчиков памяти, соединять первый соответствующий маршрут передачи данных между этим конкретным запросчиком памяти и первым портом доступа, если запрос памяти обращен к местоположению памяти первого подмножества множества банков памяти, и соединять второй маршрут передачи данных между этим конкретным запросчиком памяти и вторым портом доступа, если запрос памяти обращен к местоположению памяти второго подмножества множества банков памяти.

7. Интегральная схема по п.6, в которой множество банков памяти организовано в двумерный массив в суперячейке памяти, при этом двумерный массив содержит по меньшей мере два банка памяти, расположенных в первом направлении, и по меньшей мере два банка памяти, расположенных во втором направлении.

8. Интегральная схема по п.7, в которой первое подмножество множества банков памяти образуется первой парой смежных банков памяти в первой строке двумерного массива, а второе подмножество множества банков памяти образуется второй парой смежных банков памяти во второй строке двумерного массива.

9. Интегральная схема по п.8, в которой суперячейка памяти содержит множество дополнительных пар смежных банков памяти, при этом суперячейка памяти сконфигурирована так, что данные, соответствующие запросам, обращенным к местоположениям памяти каждой дополнительной пары смежных банков памяти, подаются исключительно через дополнительный соответствующий порт доступа.

10. Интегральная схема по п.6, в которой первое подмножество множества банков памяти находится физически ближе к первому порту доступа, чем к второму порту доступа, при этом второе подмножество множества банков памяти ближе ко второму порту доступа, чем к первому порту доступа.

11. Интегральная схема по п.1, в которой коммутационный блок содержит множество сегментов и множество схем выбора, каждая из которых выполнена с возможностью соединять конкретные сегменты из множества сегментов с по меньшей мере одним другим сегментом из множества сегментов, при этом суперячейка памяти содержит множество банков памяти, организованных в двумерный массив в суперячейке памяти, при этом множество банков памяти разделено на множество групп банков, каждая из которых включает в себя соответствующее подмножество множества банков памяти, при этом каждая из групп банков соединена с коммутационным блоком независимо от других групп из множества групп банков в суперячейке памяти, и интегральная схема дополнительно содержит контроллер, соединенный с коммутационным блоком и каждым из одного или более запросчиков, при этом контроллер выполнен с возможностью, в качестве реакции на запрос на доступ к суперячейке памяти от одного из запросчиков, предписывать коммутационному блоку конфигурировать схемы выбора для выбора сегментов, соответствующих маршруту между этим одним из запросчиков и группой банков, соответствующей местоположению памяти, связанному с запросом.

12. Интегральная схема по п.11, в которой каждый из запросчиков является ядром процессора, которое включает в себя кэш данных и кэш команд, при этом кэш данных и кэш команд каждого ядра процессора соединены с коммутационным блоком.

13. Интегральная схема по п.12, в которой суперячейка памяти образует по меньшей мере часть кэша второго уровня (L2).

14. Интегральная схема по п.11, в которой первое подмножество множества сегментов выполнено с возможностью передавать данные в суперячейку памяти, при этом другое подмножество множества сегментов выполнено с возможностью передавать данные из суперячейки памяти.

15. Способ работы интегральной схемы, которая содержит множество запросчиков памяти; суперячейку памяти, которая содержит множество банков памяти, каждый из которых формирует соответствующий диапазон отдельно адресуемых местоположений памяти, при этом суперячейка памяти организована во множество групп банков, при этом каждая из множества групп банков содержит подмножество множества банков памяти и соответствующий выделенный порт доступа; коммутационный блок, подключенный между множеством запросчиков памяти и суперячейкой памяти, при этом способ включает в себя этап, на котором

в качестве реакции на запрос памяти со стороны конкретного одного из множества запросчиков памяти соединяют с помощью коммутацинного блока соответствующий маршрут передачи данных между этим конкретным запросчиком памяти и выделенным портом доступа конкретной одной из групп банков, к которой обращен запрос памяти, при этом соответствующий выделенный порт доступа для каждой из множества групп банков физически расположен по центру между банками памяти этой группы.

16. Способ по п.15, в котором коммутационный блок содержит множество сегментов и множество схем выбора и при соединении маршрута передачи данных электрически соединяют конкретные сегменты из множества сегментов с по меньшей мере одним другим сегментом из множества сегментов для формирования маршрута между конкретным запросчиком и либо первым, либо вторым портом доступа, при этом первое подмножество множества сегментов выполнено с возможностью передавать данные в суперячейку памяти, а второе подмножество множества сегментов выполнено с возможностью передавать данные из суперячейки памяти.

17. Способ по п.15, дополнительно содержащий этап, на котором во время запроса записи, инициированного конкретным запросчиком для записи данных в местоположение памяти первой группы банков, передают данные от этого конкретного запросчика по маршруту к первому порту доступа, без передачи данных по сегментам, соединенным со вторым портом доступа.

18. Способ по п.15, дополнительно содержащий этап, на котором во время запроса чтения, инициированного конкретным запросчиком для считывания данных из местоположения памяти первой группы банков, передают данные по маршруту от первого порта доступа к этому конкретному запросчику, без передачи данных по сегментам, соединенным с другими запросчиками из множества запросчиков.

19. Способ по п.15, дополнительно содержащий этапы, на которых

подают данные, соответствующие запросам, которые обращены к местоположениям памяти первого подмножества множества банков памяти, исключительно через первый порт доступа; и

подают данные, соответствующие запросам, которые обращены к местоположениям памяти второго подмножества множества банков памяти, исключительно через второй порт доступа.

| ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА С ЗАЩИТНЫМ ПОКРЫТИЕМ ПОВЕРХНОСТИ | 1999 |

|

RU2213390C2 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 6108233 A, 22.08.2000 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

Авторы

Даты

2013-05-10—Публикация

2010-02-12—Подача