1

Изобретение относится к автоматике и вычислительной технике для нахождения тригонометрических функдий и может быть применено в пифровых устройствах обработки информации.

Известно устройство, содержащее два усилителя, выходы которых соединены с входами сумматора и два блока памятиГ1.

Недостатком этого устройства является ограниченный диапазон измерения аргумента.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее три блока памяти, два умножителя и сумматор, входы которого соединены с выходами умножителей, выходы первого и второго блоков памяти соединены с входами первого умножителя, входы второго умножителя соединены с выходом третьего блока , памяти и входом части аргумента устройства, другие разряды которого соединены с входами первого и второго блоков памяти Г2 .

Недостатком известного устройства является низкая точность.

Цель изобретения - увеличение точности вычисления функций.

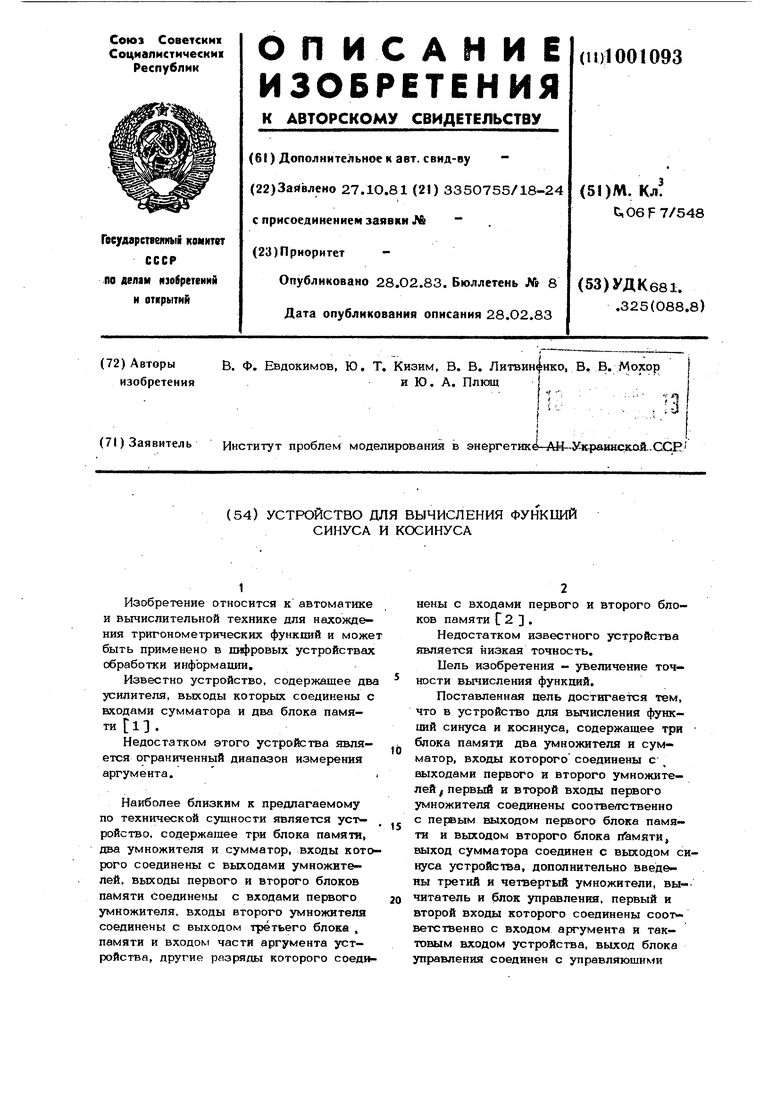

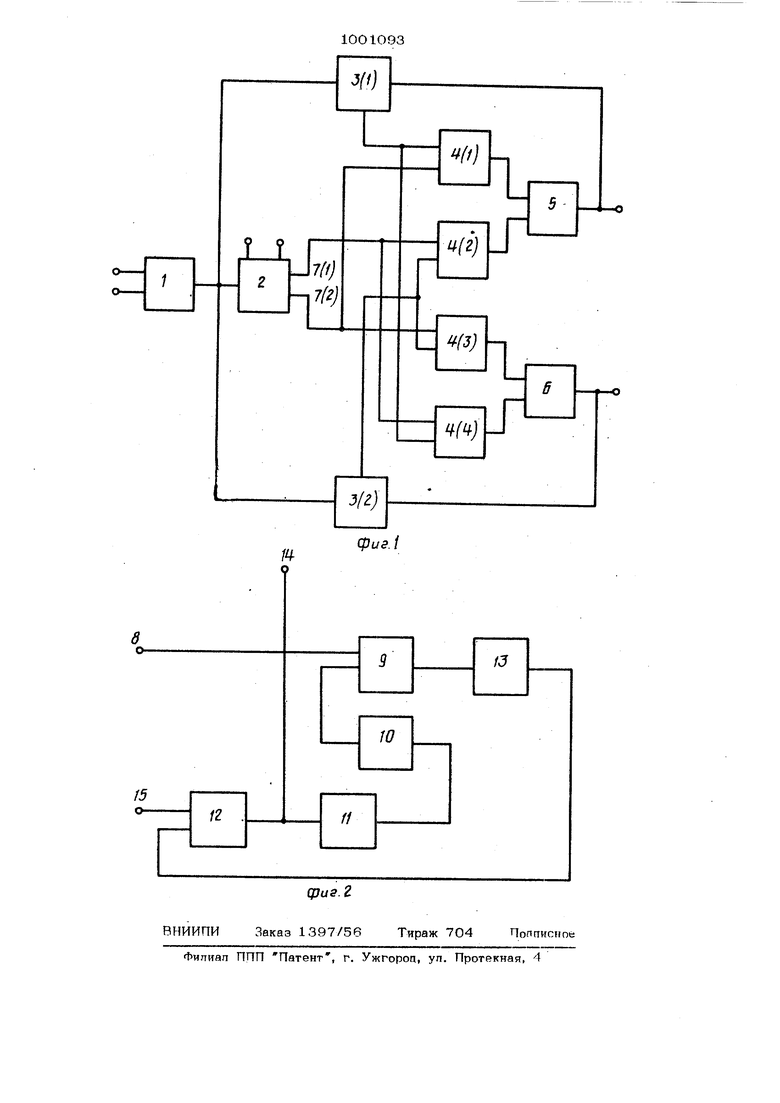

Поставленная цель достигаетх;я тем, что в устройство для вычисления функций синуса и косинуса, содержащее три блока памяти два умножителя и сумматор, входы которого соединены с выходами первого и второго умножителей первый и второй входы первого умножителя соединены соответственно с первым выходом первого блока памяти и выходом второго блока памяти, выход сумматора соединен с выходом синуса устройства, дополнительно введены третий и четвертый умножители, вычитатель и блок управления, первый и второй входы которого соединены соответственно с входом аргумента и тактовым входом устройства, выход блока упр авления соединен с управляющими входами 67JOKOB памяти второй выход первого блока памяти соединен с пер выми входами второго и третьего умножителей, второй вход третьего умножите ля соединен с выходом второго блока памяти, выход третьего блока памяти соединен с вторым входом второго и первым входом четвертого умножителей, второй вход четвертого умножителя соединен с первым выходом первого блока памяти, информационный вход которого соединен с входом опорного значения функции устройства, выходы третьего и четвертого умножителей соединены с входами вычитателя, выход которого со- единен с информационным входом второго блока памяти и выходом косинуса устройства, выход сумматора соединен с информационным входом третьего блок памяти. Блок управления содержит элемент И счетчик, группу элементов НЕ, сумматор по модулю два и элемент И-НЕ, вход и выход которого соединены соответственн с выходом сумматора по модулю два и первым входом элемента И, второй вход и выход которого соединены соответственно с вторым входом блока управления и входом счетчика, выходы разрядов которого черед соответствующие элементы НЕ группы соединены с первой группой разрядных входов сумматора по модулю два. вторая группа которых соединена с первым входом блока управления, выход которого соединен с выходом элемента И, На фиг, 1 представлена блок-схема устройства; на фиг, 2 - вариант реализа ции блока управления. Устройство для вычисления функций синуса и косинуса содержит блок 1 упра ления, блоки 2 и 3 памяти, умножители 4, сумматор 5, вычислитель 6, выходы 7 блока 2 памяти. Цифры в скобках показывают аналогичность реализации указанных блоков.

Блок 1 управления содержит вход 8 аргумента, сумматор 9 по модулю два, группу 10 элементов НЕ, счетчик 11,, элемент И 12, элемент И-НЕ 13, выход 14 и вход 15 тактовых импульсов.

Работу устройства рассмотрим на примере. Пусть необходимо вычислить синус и косинус угла 10, На информадионном входе блока 2 памяти имеем значение sin 1° и со 1°. Блок 2 памяти может быть выполнен на группе элементов И.

После перемножения соответствующие произведения поступают на сумматор 5

и вычитатель 6, На выходе сумматора 5 получаем значение 2 , на выходе вычитателя 6 - значение cos 2, которые заносятся соответственно в блоки 3(1) и 3(2) памяти,

На следующих тактах работы преобразователя находим синус и косинус ТГ и 4° и так далее до значения аргумента, синус и косинус которого нужНа первом такте работы устройства на вход 8 поступает аргумент Данной функции. Данный аргумент и значение, записанное в счетчике 11, симмируются в сумматоре 9 по модулю два, причем всумматор 9 из счетчика 11 поступает инверсное значение. При несовпадении значений, подаваемых на сумматор 9, на выходе группы И-НЕ 13 получаем I, Этот сигнал поступает на элемент И 12 и при подаче на вход 15 синхроимпульс попадает в счетчик 11, блок 2 памяти иблоки 3(1) и 3(2) памяти, На выходе 7(1) блока 2 памяти, при поступлении на него сигнала, получаем Sin 1°, на выходе 7(2) - значение cos 1° . Значение si подается с выхода 7(1) блока 2 на входы умножителей 4(2) и 4(4), значение cos 1° - на входы умножителей 4(1) и 4(3), В это же время из блока 3(1) памяти по сигналу, идущему с блока 1 управления, поступает на вход умножителей 4(1) и 4(4) записанный ранее О, из блока 3(2) памяти на вход умножителей 4(2) и 4(3)записанная ранее 1, Полученное на выходе умножителя 4(2) значение sin 1 поступает через сумматор 5 в блок 3(1) памяти. Полученное на выходе умножителя 4(3) значение со5 1 поступает через вычислитель 6 в блок 3(2) памяти, На втором такте работы цифрового преобразователя снова происходит суммирование по модулю два аргумента и кода, записанного в счетчике, В случае их неравенства на выходах элемента И-НЕ снова получаем сигнал, поступающий в счетчик 11, блок 2 памяти, блоки 3(1) и 3(2) памяти. При этом с выхода 7(1) полученный 51 п 1 подае1х;я на входы умножителей 4(2) и 4(3), полученное значение cos 1 поступает на входы умножителей 4(1) и 4(4), Из блока 3(1) памяти поступает на вход умножителей 4(1) и 4(4) значение siti 1 , из блока 3(2) памяти поступает на вход умножителей 4(2) и 4(3) значение COS 1°,

но опредепить. При равенстве зна«чения, записанного в счетчике, со4 значением аргумента на выходе элемента И-НЕ появляется О, устройство прекращает свою работу и на его выходе будут значения синуса и косинуса аргумента, подаваемогр на вход устройства. Число тактов работы определяется величиной аргумента и выбра1Нным шагом.

формула изобретения

1. Устройство для вычисления функций синуса и косинуса, содержащее три блока памяти, два умножителя и сумматор, входы которого .соединены с выходами первого и второго умножителей, первый и второй входы первого умножителя соединены соответственно с первым впкодом первого блока памяти и выходом второго блока памяти, выход сумматора соединен с выходом синуса устройства, отличающееся тем, что, с 1юлью увеличения точности вычисления, в него введены третий и четвертый умножители, вычитатель и блок управления, первый и второй входы которого соединены соответственно с входом аргумента и тактовым входом устройства, выход блока управления соединен с управлякнщими входами блоков памяти, второй выход первого блока памяти соединен с первыми входами второго и третьего умножителей, второй вход третьего умножителя соединен с выходом второго блока памяти выход третьего блока памяти соединен с вторым входом второго и перовым входом четвертого умножителей, второй вход четвертого умножителя соединен с первым выходом первого блока памяти, информационный вход которого соединен . с входом опорного значения функшт устройства, выходы третьего и четвертого умножителей соединены с входами вычит теля, выход которого соединен с информационным входом второго блока памяти и выходом косинуса устройства, выход сумматора соединен с информационным Входом третьего блока памяти.

2. Устройство по п. 1, о т л и ч а - ю щ е е с я тем, что, блок управления содержит элемент И, счетчик, группу элементов НЕ, сумматор по модулю два и элемент И-НЕ, вход и выход которого соединены соответственно с выходом сумматора по модулю два и первым входом элемента И, второй вход и выход которого соединены соответственно с вторым входом блоки управления и входом счетчика, выходы которого через соответст вутощие элементы НЕ группы соединены с первой группой разрядных входов сумматора по модулю два, вторая группа которых соединена с первым входом блока управления, выход которого соединен с выходом элемента И.

Источники информашш, принятые во внимание при экспертизе

1.Оранский А. М . Аппаратные методыв цифровой вычислительной технике, . с. 49-5О, рис. 2.6.

2.Смолов В. Б. Функциональные преобразователи информации. Л., Энергоиздат, с. ЗО, рис. 2.8 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1983 |

|

SU1140116A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1012249A1 |

| Устройство для воспроизведения кардиоиды | 1981 |

|

SU1007102A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для вычисления функций синуса и косинуса | 1985 |

|

SU1272331A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU926651A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Устройство для вычисления функций синуса и косинуса | 1984 |

|

SU1205140A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1171785A1 |

Авторы

Даты

1983-02-28—Публикация

1981-10-27—Подача