чем старший разряд 1-го преобразователя прямого кода в дополнительный, где 1 1,2,,..Зт-1, соединен с управляющим входом (i+l)-ro преобразователя прямого кода в дополнительный, входы первого преобразователя прямого кода в дополнительный

соединены с входом блока управления, выходы j-ro (j+l)-ro и (j+2)-ro преобразователей прямого кода в дополнительный, где j 1,4,7р..,,3m-2,

соединен с (у-)-м выходе 6jjoKa управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для вычисления функций @ и @ | 1980 |

|

SU978146A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления функций @ = @ , @ = х @ | 1989 |

|

SU1674113A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

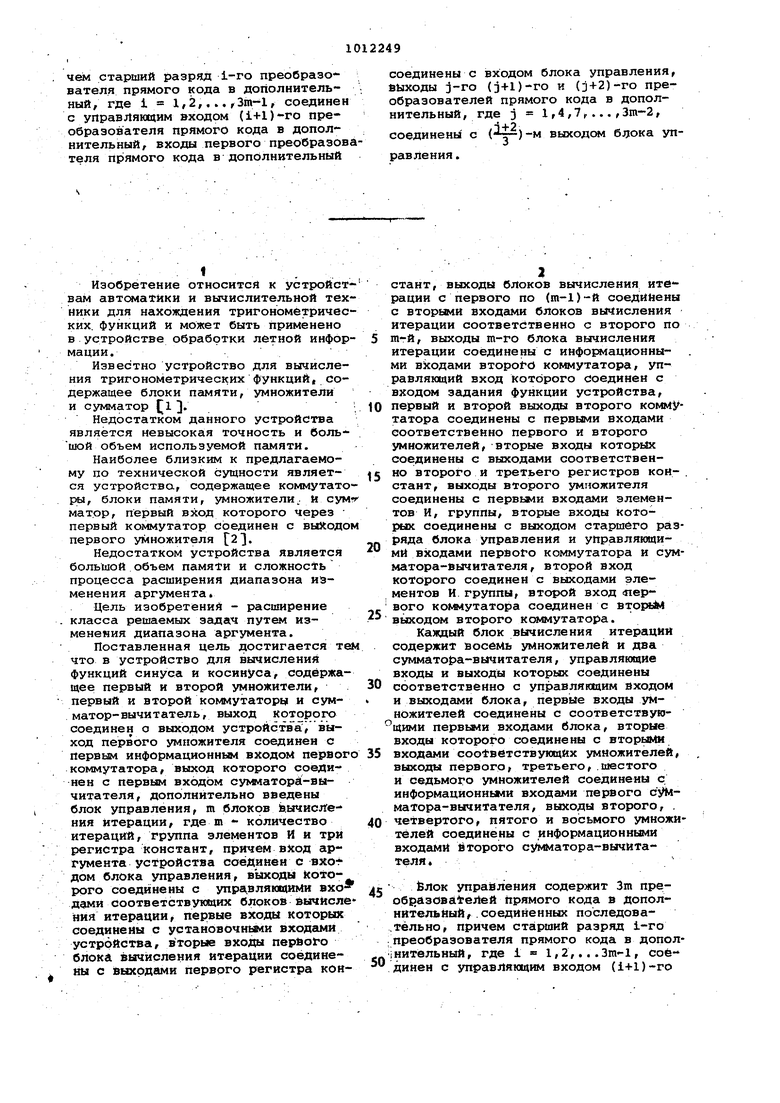

1. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ СИНУСА И КОСИНУСА, содержащее первый и второй умножители, первый и второй Коммутаторы, и сукматор-вычитатель, вькод которого соединен с выходом устройства, выход первого ynt ножйтеля соединен с первым информа-. ционным входом первого ксллмутатора, выход которого соединен с первым входом c Ф1aтopa-вычитaтeля, о т .л и ч а ю щ е е с я тем, что, с целью рарширения диапазона вычисл емых функций Путем изменения ajpryMeHTa, в него введены блок управления, m блоков вычисления итерации, где m количество итераций, группа элементов И и три регистра констаит,причем вход,аргумента .устройства соединен с входом блока управления, выходы которого соединены с управляющими входами соответствующих блоков вычисления итерации, первые входы которых соединены с yctaнoвoчнымн входами устройства, вторые входы первого блока вычисления итерации воедйиекы с выходами первого регистра констант/ выходы блоков вычисления итерапии, с первого по {т-1)-й, соединены с вторьми входами блоков вычисления .итерации соответственно со второго по й-и, выходы т-го блока вычисления итерации соединены с информационньми входсши второго кЬммутатора, управляющий вход которого соединен с входсвл задания функции устройства, первый и второй выходы второго коммутатора, соединены С Первыми входами соответственно первого и вторбго умножителей, вторые входы которых соеди нены с выходами соотьетствейно второго и третьего регистровконстайт,выходы второго умножителя соединены с первьми входами элементов И группы, вторые входы которых соединены с выходом CTajpiaero разряда, блока управления и управляющими входами первого коммутатора и сумматрра-вычита- .д теля,второй вход которого соединен с выходамиэлементов И группы,, вто.рой вход первого коммутатора соединен с вторым выходом второго коммута тора. 2.Устройство по П.1, о т л и ч аю ц е е с я тем, что каждый блок Г ычисления итерации содержит умножителей и два сумматора-, вычитателя, управляющие входы и выходы которых соединены соответственно с управляющим входом и выхо дамн блока, первые входы умножителей соединены с соответствующими первьоли входги4И блока, вторые входы которого соединены с вторыми входами соответствующих умножителей, выходы первого, третьего, шестого и седьмого умножителей соединены с. информационньали входами первого сукматора-вычитателя, выходы второго, четвертого, пятого и восьмого 5 ножителей соединены с информационными входами второго сумМатора-вычитателя. 3.Устройство по п.1, о т л и чающееся т&л, что блок управления содержит 2 т преобразовав тёлей прямого кода в дополнительный, соединенных последовательно, при

Изобретение относится к устройствам автоматики и вычислительной техники для нахождения тригонометрических, функций и может быть применено в устройстве обработки летной информации.

Известно устройство для вычисления тригонометрических функций, содержащее блоки памяти, умножители и сумматор 13

Недостатком данного устройства является невысокая точность и боль шой объем используемой пгиляти.

Наиболее близким к предлагаемому оо технической сущности является устройства, содержащее коммутаторы, блоки памяти, умножители, н сум матор, первый вход которого через первый коммутатор соединен с выходом первого умножителя .

Недостатком устройства является большой объем памяти и сложность процесса расширения диапазона изменения аргумента.

Цель изобретений - расширение класса решаемых задач путем изменения диапазона аргумента.

Поставленная цель достигается тем что в устройство Для вычислений функций синуса и косинуса, содержащее первый и второй умножители, первый и второй коммутаторы и csMматор-вычитатель, выход которого соединен о выходом устройств а:, выход первого умножителя соединен с первым информационным входом первого коммутатора, выход которого соединен с первым входом сумматорй-вычитателя, дополнительно введены блок управления, m блоков вычисления итерации, где m - количество итераций, группа элементов И к три регистра констант, причем вход аргумента устройства соединен с входом блока управления, выходы Которого соединены с управляющими вхо дэми соответствующих блоков вычйсле ния итерации, первые входы которых соединены с установочн1:Ф 1И входг1МИ устройства, вторые входы nepSot-o блока вычисления итерации соединены с выходами первого регистра констант, выходы блоков вычисления итерации с первого по (т-1)й соединены с вторыми входсми блоков вычисления итерации соответственно с второго по

т-й, выходы т-го блока вычисления итерации соединены с инфо 1ационными входами BTopotd коммутатора, управляющий вход Которого соединен с входом задания функции устройства,

первый и второй выходы второго коммутатора соединены с первыми входами соответственно первого и второго умножителей, вторые входы которых соединены с выходами соответственно второго и третьего регистров кон-, стант, выходы второго умножителя соединены с первыми входами элементов И, группы, вторые входы которых соединены с выходом старшего разряда блока управления и управляющими входами первого коммутатора и сумматора-вычитателя, второй вход которого соединен с выходами элементов И группы, второй вход спер вого коммутатора соединен с BTOpiA выходом второго ксячмутатора.

Каждый блок вЁписления итерации содержит восемь умножителей и два суммато а-в ычитателя, управ ляющие входы и выходы которых соединены соответственно с управляющим входом и выходами блока, первые входы умножителей соединены с соответствую щими первыми входами блока, вторые входы которого соединены с вторыми входами соответствующих умножителей, выходы первого третьего,.шестого и седьмого умножителей соединены с информационными входами первого сУМматора-вычитателя, выходы второго, . четвертого, пятого и восьмого умножителей соединены с информационными входами йторого сумматора-вычитателя.

Д5 блок упрайления содержит 3т преобразоваТеЛеЙ прямого кода в дополнительный, .соединенных последова.тельно, причем старший разряд i-ro ;преобразователя прямого кода в допол.нительный, где 1 1,2, ...Зга-1, динен с управЛяпщим входом (1+1)-го

;Л1реобразователя прямого кода в до. полните ль ный/ входы первого образователя прямого кода в дополнительный соединены с входой блока управления, выходы j-ro, (j+l)-ro (j-f2)-ro пр1еобразователей прямого кода в дополнительный где j. . 1, Зга-2 соединены с

()-м вв«одом блока упраавления.

fc. . -

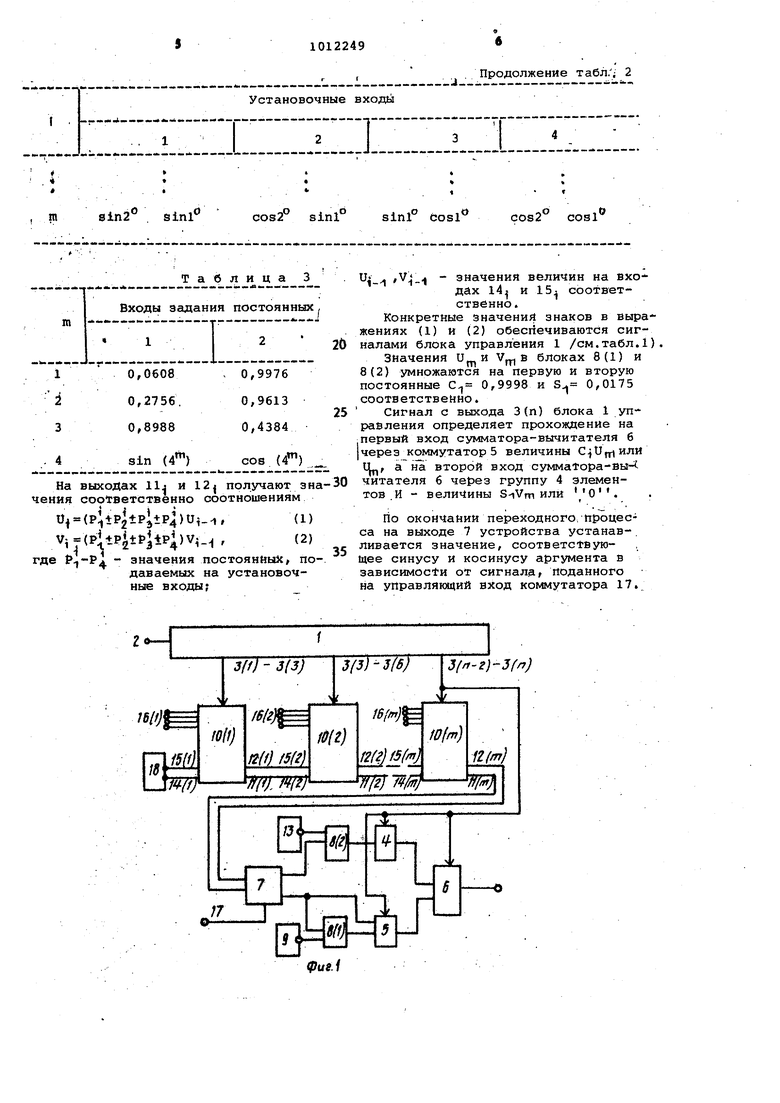

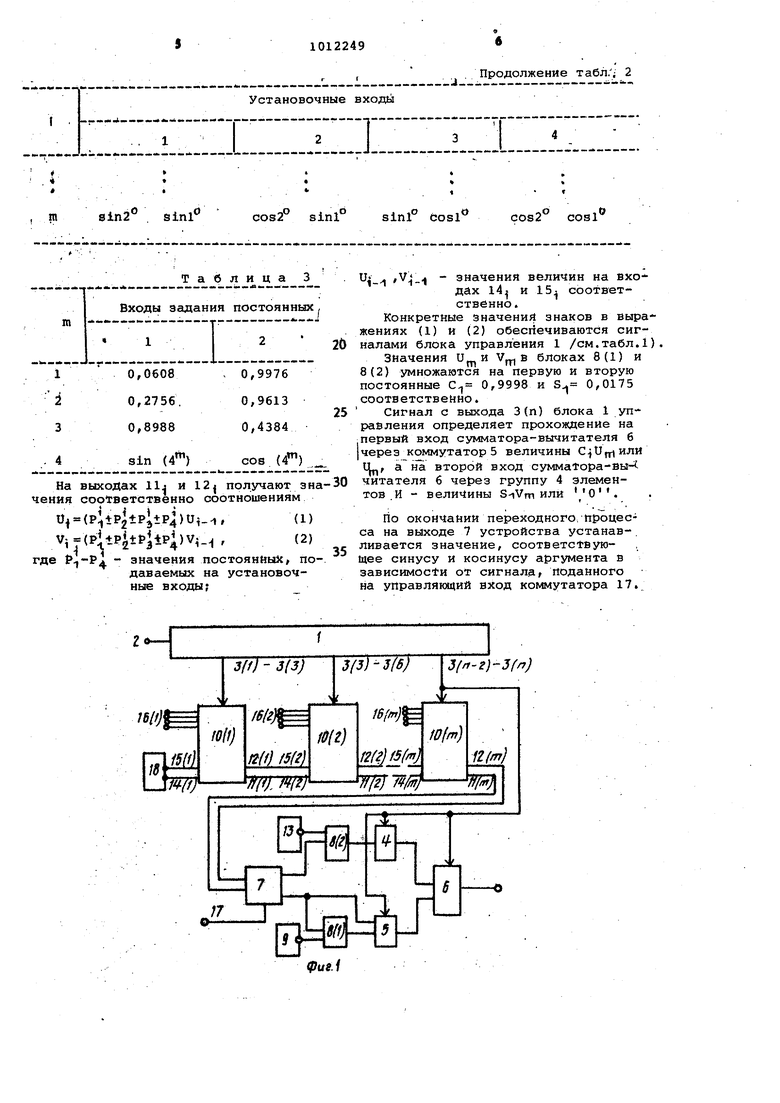

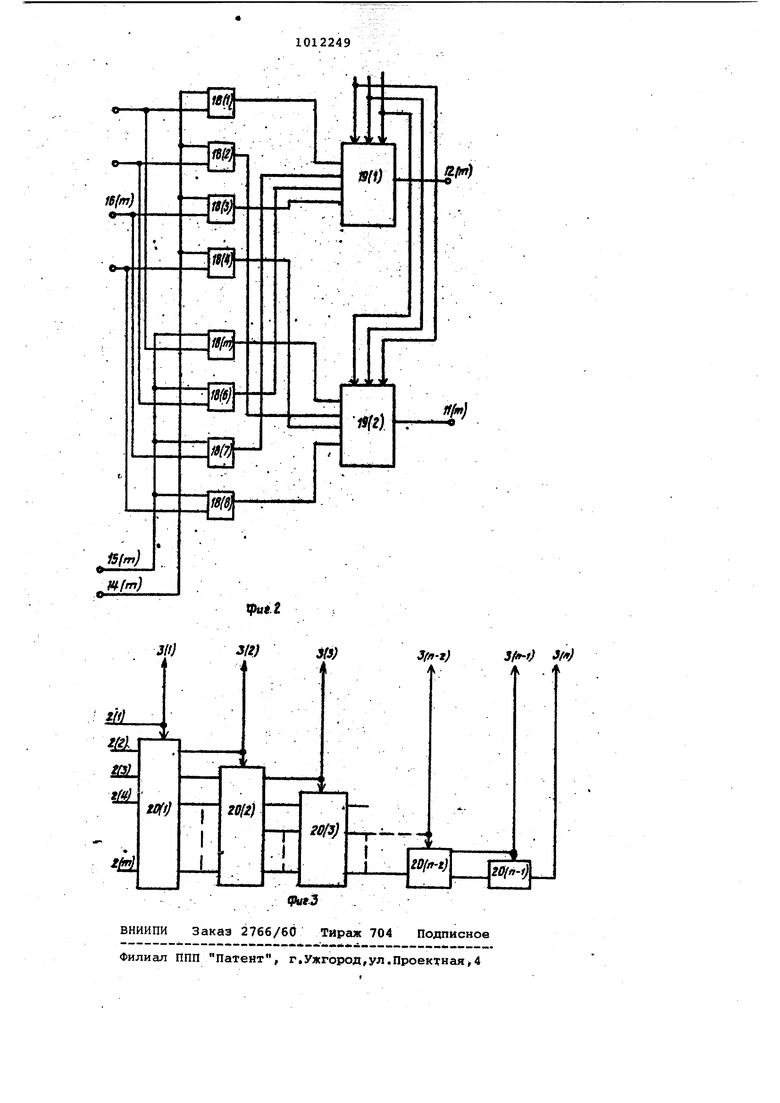

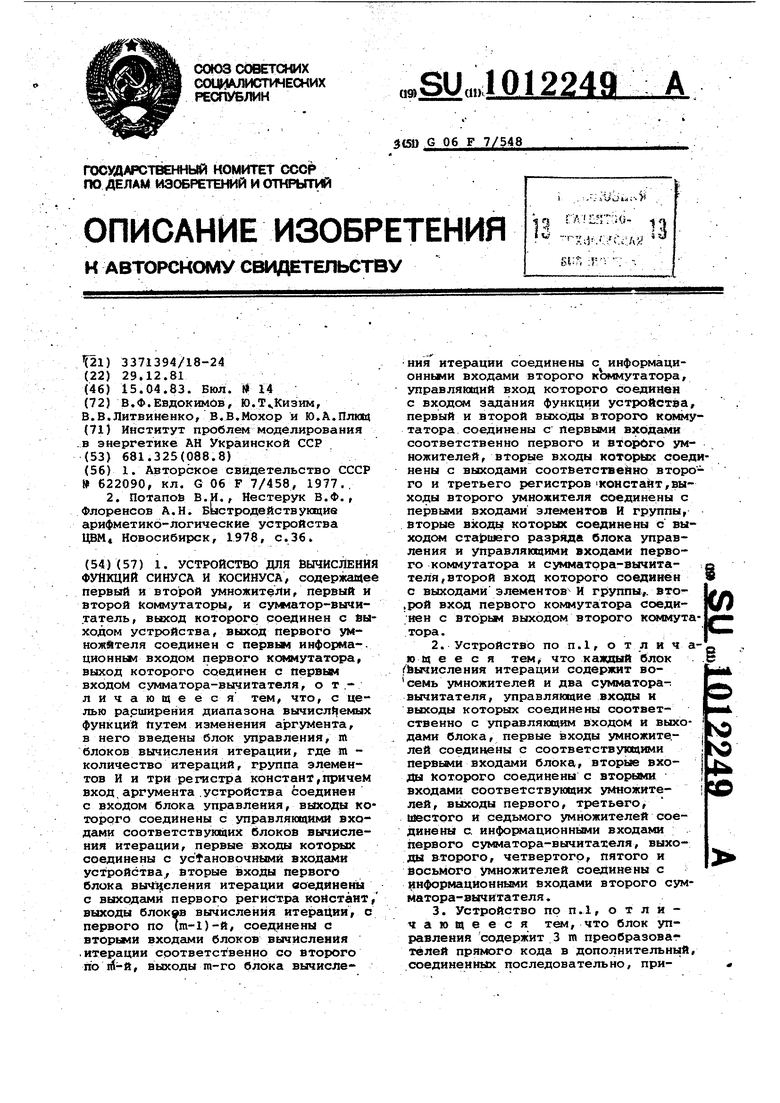

На фиг. 1 представлена с Груктурная схейа устройства; на фиг.2 структурная схема блока вычисления итерации, вариант выполнения; на фиг.З - |5лок-схема блока управления, вариант выполнения.

Устройство содержит блок, упрешления 1-, вход 2 .устройства, выходы 3 блока управления, группу 4 элементов И, коммутатор 5, csn«uiaToвычитатель 6, ксянмутатор 7, умножители 8 и Sj, регистр 9, блоки вычисления итераций, выхо ды 11.,-11„ и , блоков йычисления итерации, регистр 13, входы и ,, блоков ВЕЛчисления итерации, вход 17 задания функции.

I Блок 10 вы:«1исления итерации соджит умножители 18-j-18(| и сумматорывычитатели 19 и 192. .

I Блок управленид 1 содержит преобразователи прямого кода в дополнительный.

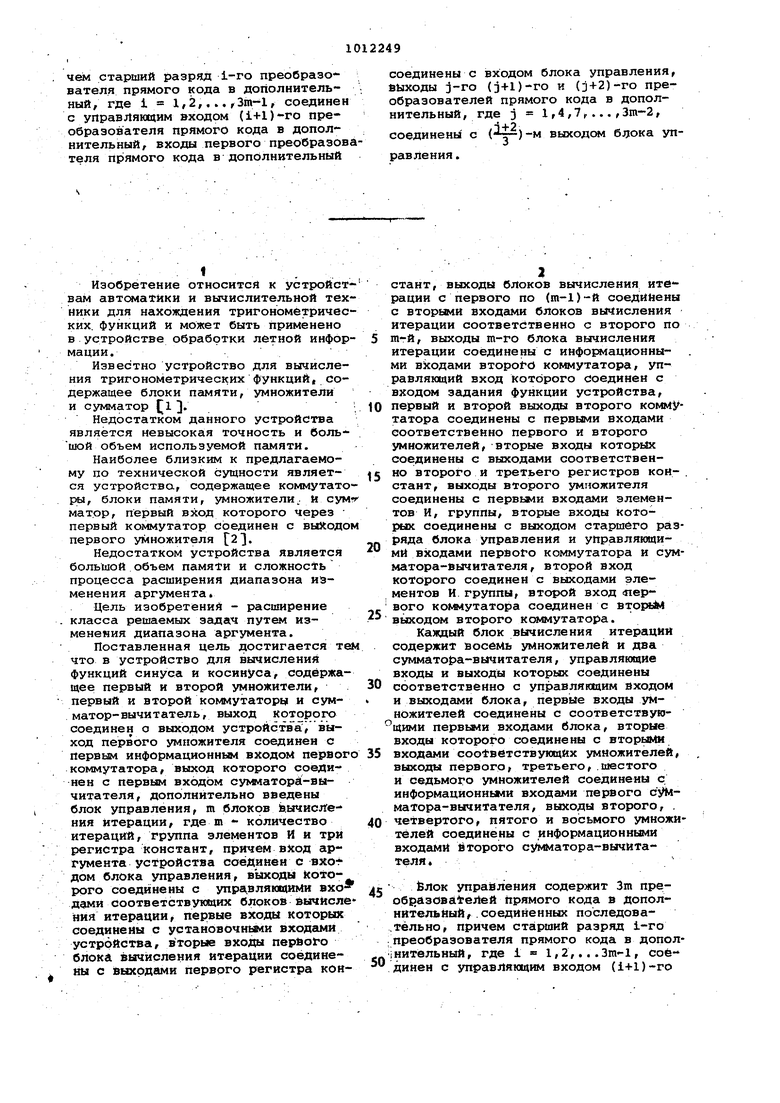

Табл.1 поясняет принцип формирования сигналов управления: при раCTapiiiero разряда

йе не тве

поступающей На преобразователь кодовой комбинации происходит преобразование прямого кода и дополнительный, при равенстве 1 i j6jBt)yTC следующие младшие 1 зрядЫ «кбдЫвой комбинации без пребё а зования я „h-2 . 1з1п2sin2. 2sin2sin2 3sin2 sin2IT а б л и ц-а- 1

10

15

20

25;

примечание. с1„- значение

30

аргумента, подаваемого на вход устройства t

Х,- - значение старшего |зазряда. Значение О, старшего разряда ;определяет знак -, «i - . 35 знак + вычислении функции |СиИуса, для вычисления функции ко,синуса - наоборот. ,

j Устройство работает следующим обI разом. ф

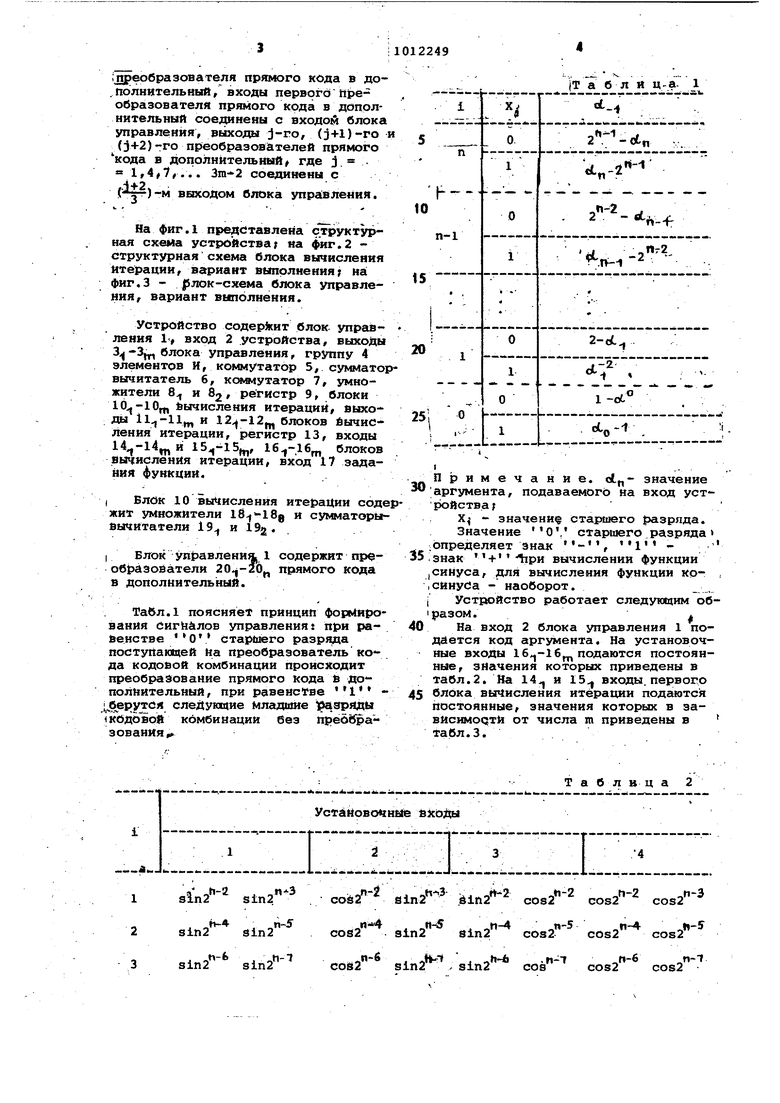

40 На вход 2 блока управления 1 подается код аргумента. На установочные входы 16,-1 бj подаются постоянные, значения которых приведены в табл.2. На 14 и 15 входы.первого 45 блока вычисления итерации подаются постоянные, значения которых в завИсимортИ от числа m приведены в табл.3.

Таблица 2 cos:/ 61 2 .eln2 cos2 cos2 2 2 cos2sin2 Sin2cos2cos2cos2 сов2sin2 . sin2coscos2cos2 -П-4, H- . „11-4 n-5 11-4 Л-У -П-6. , .M-T n-6 . 1 h , 1 . .-.- ins±n2 . sinl T a 6 Входьа задания m --«..;--I , . .«i 10,0608 , ., . 20,2756. 30,8988 - 4 sin (4) -..:„«- « -, На выходах llj и 12 п чения соответственно соот W (P tP2 P3-P4 i- у.-/pi .4.pi. ) V J { 1j 2- J- 4 i-l где ,-Р4 значения пост даваемых на у ныв входы

311) - 3(3)

1В(гу

foU)

т

J5{1}

М 15(2}

ВД ft(i)

тт

Ж П

J7

|ТЙ§

J/J/-J// ;

3(1-г)-3(п)

16{т}

fOff)

12(f5(in)

П(т) /W ,,. .Продолжение табл.- 2 Установочныевходи Ь.«.......тл .ЛА- ж. А Г . , . - . . i ,. . cos2° sinl° slnl° Cosl cos2° a значения величин на вхо постоянньзх ,ственно. .j Конкретные значений знаков в выра.жениях (1) и (2) обеспечиваются сиг 2Uналами блока управления 1 /см.табл.1). значения и и V в блоках 8(1) и 0,99768(2) умножаются на первую и вторую 0,9613соответственно. 25 Сигнал с выхода 3(п) блока 1 уп0,4384равления определяет прохождение на cos (4)|через коммутатор5 величины .,.1, а на второй вход сумматора-вы- олучают зна-30читателя 6 через группу 4 элеменношениямтов И - величины S-iVm или . ) По окончании переходного прЪцес(2) выходе 7 устройства устанав -ливается значение, соответс вуюоянных, по-щее синусу и косинусу аргумента в становоч-зависимос и от сигнала, поданного на управляющий вход коммутатора 17. --- соответпостоянные С-, 0,9998 и S 0,0175 Iпервый вход сумматора-вычитателя 6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU622090A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Потапов В.И., Нестерук В.Ф., Флоре нсов А.Н | |||

| Выетродейств ующив арифметико-логические устройства ЦВМ, Новосибирск, 1978, с.36. | |||

Авторы

Даты

1983-04-15—Публикация

1981-12-29—Подача