Изобретение относится к вычислительной технике и может быть исполь-зовано в устройствах дискретной связи и передачи информации.

Известно многоканальное устройство для приема информации, содержеицее в каждом канале входной элемент И, первый вход которого подключен к информационному входу устройства, второй вход соединен с управляющим входом устройства, а выход с входом блока памяти, выход которого подключен к информационному выходу устройства 1..

Недостатком этого устройства явля1ется низкая надежность в работе.

Наиболее близким к изобретению по технической сущности является многоканальное устройство для приема информации, содержащее в каждом ин.формацирнном канале входной элемент И, первый вход которого подключен к информационному входу устройства, второй вход соединен с управляющим входом устройства, а выход - с входом блока Памяти, выход которого подключен-к информационному выхбду устройства, схему сравнения, входы ,которой подключены к входу входного элемента И и выходу блока памяти.

выход схемы сравнения соединен свыходом элемента ИЛИ, -общим для всех каналов, выход которого связан с выходом устройства t2.

Недостатками этого устройства являются возможность зацикливания работы по приему информации в случае чередования:сбойных ситуаций, а также неопределённость момента считы10вания информации.

Цель изобретения - повышение быстродействия устройства путем одного повторного запроса - занесения информации и определение момента готов15ности устройства к приему новой информёщии.

Поставленная цель достигается тем, что в устройство для приема дискретной информацииг содержащее элемент

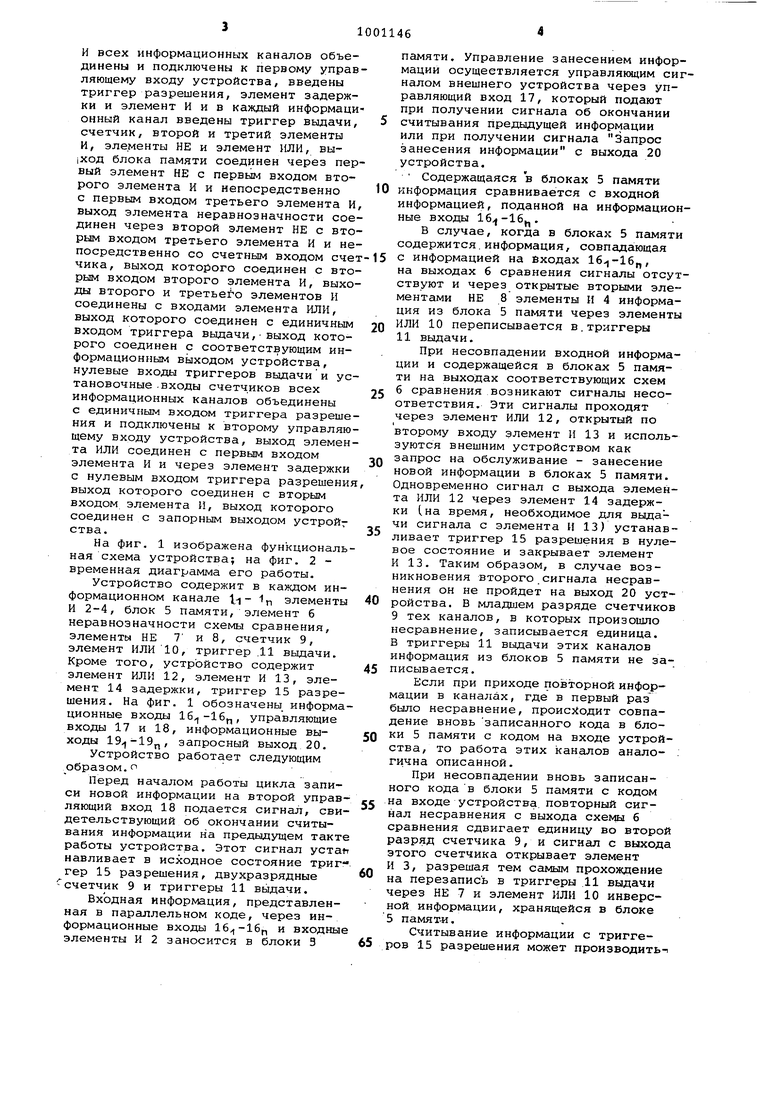

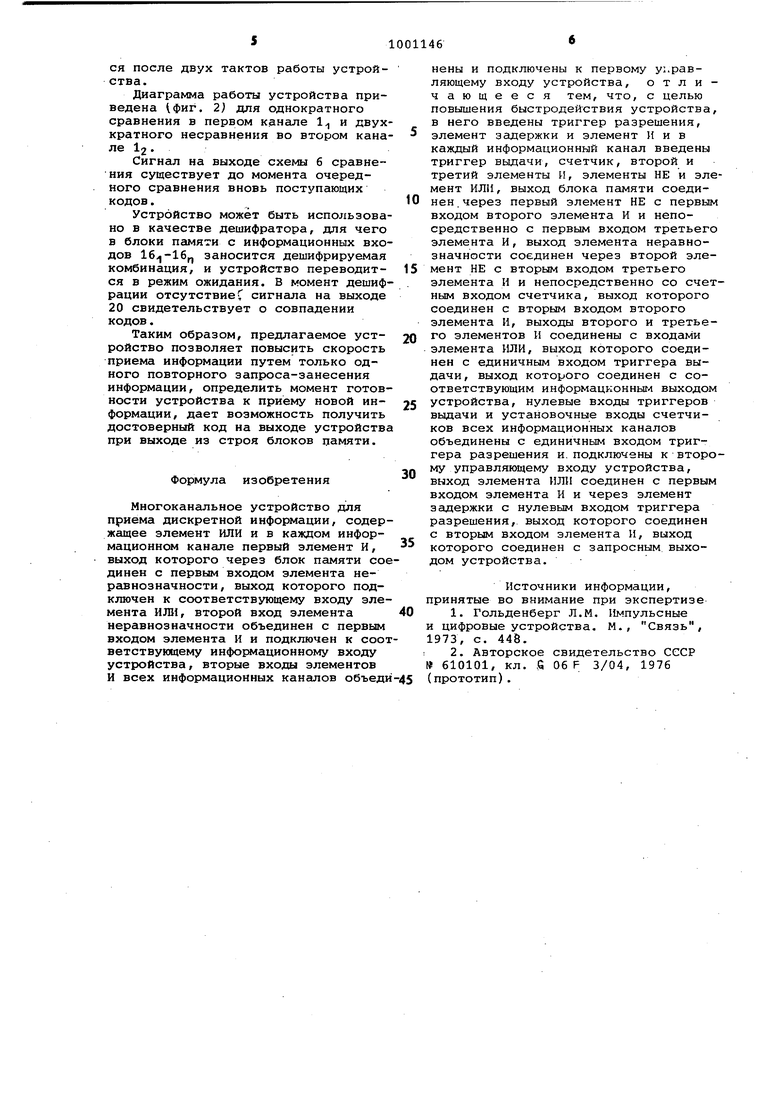

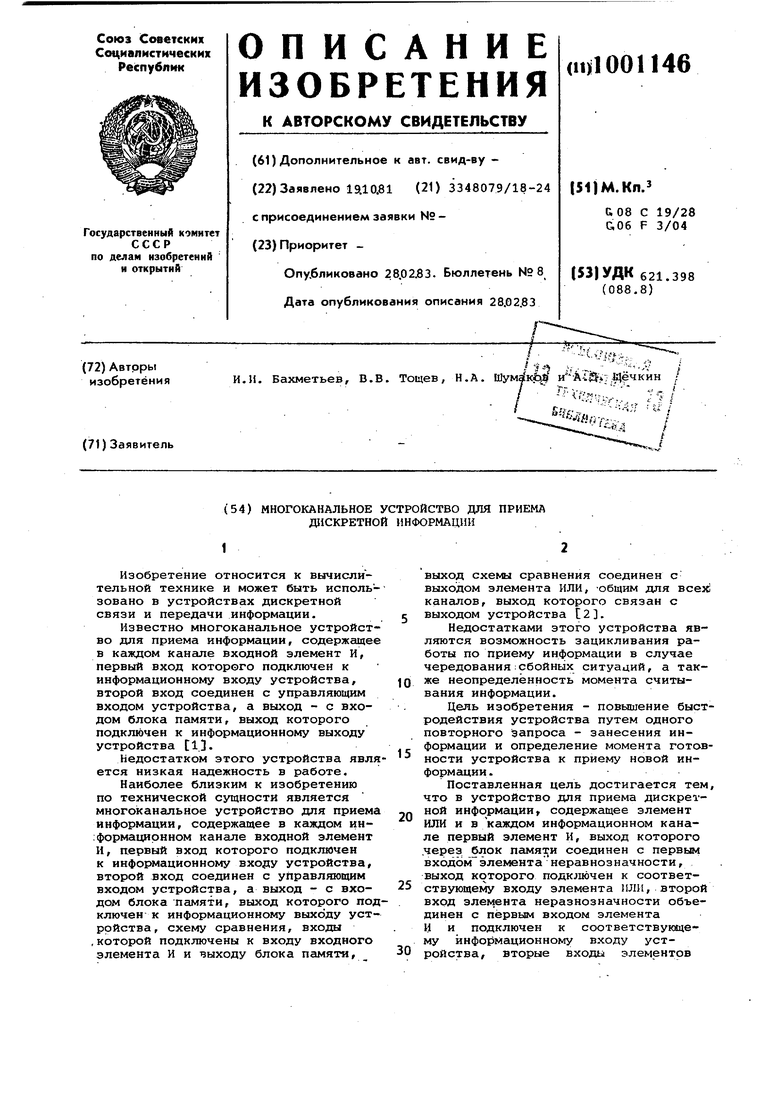

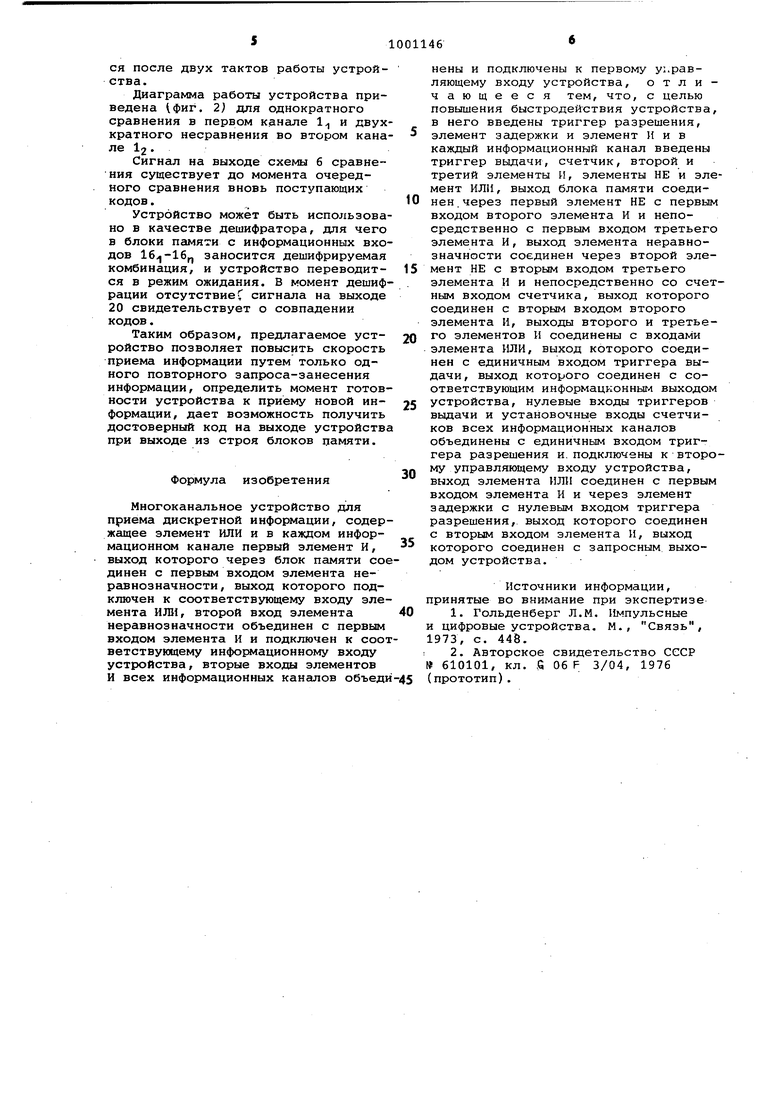

20 ИЛИ и в каждом информационном канале первый элемент И, выход которого .через блок памяти соединен с первым входом элемента неравнозначности, выход которого подключен к соответ25ствующему входу элемента ИЛИ, второй вход элемента неразнозначности объединен с первым входом элемента И и подключен к соответствующему информационному входу уст30ройства, вторые входы элементов И всех информационных каналов объединены и подключены к первому управ ляющему входу устройства, введены триггер разрешения, элемент задержки и элемент И и в каждый информаци онный канал введены триггер выдачи, счетчик, второй и третий элементы И, элементы НЕ и элемент ИЛИ, вы|ХОД блока памяти соединен через пер вый элемент НЕ с первым входом второго элемента И и непосредственно с первым входом третьего элемента И выход элемента неравнозначности сое динен через второй элемент НЕ с вто рым входом третьего элемента И и не посредственно со счетным входом сче чика, выход которого соединен с вто рым входом второго элемента И, выхо ды второго и TpeTbefo элементов И соединены с входами элемента ИЛИ, выход которого соединен с единичным входом триггера выдачи,выход которого соединен с соответствующим информационным выходом устройства, нулевые входы триггеров выдачии ус тановочные .входы счетч.иков всех информационных каналов объединены с единичным входом триггера разреше ния и подключены к второму управляю щему входу устройства, выход элемен та ИЛИ соединен с первым входом элемента И и через элемент задержки с нулевым входом триггера разрешения выход которого соединен с вторым входом элемента И, выход которого соединен с запорным выходом устройг ства. На фиг. 1 изображена функциональ ная схема устройства; на фиг. 2 временная диаграмма его работы. Устройство содержит в каждом информационном канале l-i- п элементы И 2-4, блок 5 памяти, элемент б неравнозначности схемы сравнения, элементы НЕ 7 и 8, счетчик 9, элемент ИЛИ 10, триггер .11 выдачи. Кроме того, устройство содержит элемент ИЛИ 12, элемент И 13, элемент 14 задержки, триггер 15 разрешения. На фиг. 1 обозначены информа ционные входы , управляющие входы 17 и 18, информационные выходы 19x|-19j,, запросный выход 20. Устройство работает следующим образом. Перед началом работы цикла записи новой информации на второй управляющий вход 18 подается сигнал, свидетельствующий об окончании считывания информации на предыдущем такте работы устройства. Этот сигнал ycTat навливает в исходное состояние триг гер 15 разрешения, двухразрядные счетчик 9 и триггеры 11 выдачи. Входная информация, представленная в параллельном коде, через информационные входы , и входные элементы И 2 заносится в блоки 3 памяти. Управление занесением информации осуществляется управляющим сигналом внешнего устройства через управляющий вход 17, который подают при получении сигнала об окончании считывания предыдущей информации или при получении сигнала Запрос занесения информации с выхода 20 устройства. Содержащаяся в блоках 5 памяти информация сравнивается с входной информацией, поданной на информационные входы 16.(-16f,. В случае, когда в блоках 5 памяти содержится. инф.ормация, совпадающая с информацией на входах , на выходах 6 сравнения сигналы отсутствуют и через открытые вторыми элементами НЕ 8 элементы И 4 информация из блока 5 памяти через элементы ИЛИ 10 переписывается в.триггеры 11 выдачи. При несовпадении входной информации и содержащейся в блоках 5 памяти на выходах соответствующих схем 6 сравнения возникают сигналы несоответствия. Эти сигналы проходят через элемент ИЛИ 12, открытый по второму входу элемент И 13 и используются внешним устройством как запрос на обслуживание - занесение новой информации в блоках 5 памяти. Одновременно сигнал с выхода элемента ИЛИ 12 через элемент 14 задержки (на время, необходимое для выдачи сигнала с элемента И 13) устанавливает триггер 15 разрешения в нулевое состояние и закрывает элемент И 13. Таким образом, в случае возникновения второго сигнала несравнения он не пройдет на выход 20 устройства. В младшем разряде счетчиков 9 тех каналов, в которых произошло несравнение, записывается единица. В триггеры 11 выдачи этих каналов информация из блоков 5 памяти не записывается. Если при приходе повторной информации в каналах, где в первый раз было несравнение, происходит совпадение вновь записан.ного кода в блоки 5 памяти с кодом на входе устройства, то работа этих каналов анало- . гична описанной. При несовпадении вновь записанного кода в блоки 5 памяти с кодом На входе устройства, повторный сигнал несравнения с выхода схемы 6 сравнения сдвигает единицу во второй разряд счетчика 9, и сигнал с выхода этого счетчика открывает элемент И 3, разрешая тем самым прохождение на перезапись в триггеры 11 выдачи через НЕ 7 и элемент ИЛИ 10 инверсной информации, хранящейся в блоке 5 памят-и. Считывание информации с триггеров 15 разрешения может производить-i ся после двух тактов работы устройства. Диаграмма работы устройства приведена фиг. 2) для однократного сравнения в первом канале 1 и двух кратного несравнения во втором кана ле 12 . Сигнал на выходе схемы б сравнения существует до момента очередного сравнения вновь поступающих кодов. Устройство может быть использова но в качестве дешифратора, для чего в блоки памяти с информационных вхо дов , заносится дешифрируемая комбинация, и устройство переводится в режим ожидания. В момент дешиф рации отсутствие; сигнала на выходе 20 свидетельствует о совпадении кодов. Таким образом, предлагаемое устройство позволяет повысить скорость приема информации путем только одного повторного запроса-занесения информации, определить момент готовности устройства к приему новой информации, дает возможность получить достоверный код на выходе устройства при выходе из строя блоков памяти. Формула изобретения Многоканальное устройство для приема дискретной информации, содер жащее элемент ИЛИ и в каждом информационном канале первый элемент И, выход которого через блок памяти сое динен с первым входом элемента неравнозначности, выход которого подключен к соответствующему входу элемента ИЛИ, второй вход элемента неравнозначности объединен с первым входом элемента И и подключен к соот ветствующему информационному входу устройства, вторые входы элементов И всех информационных каналов объеди нены и подключены к первому управляющему входу устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены триггер разрешения, элемент задержки и элемент Нив каждый информационный канал введены триггер выдачи, счетчик, второй и третий элементы И, элементы НЕ и элемент ИЛИ, выход блока памяти соединен . через первый элемент НЕ с первым входом второго элемента И и непосредственно с первьам входом третьего элемента И, выход элемента неравнозначности соединен через второй элемент НЕ с вторым входом третьего элемента И и непосредственно со счетным входом счетчика, выход которого соединен с вторым входом второго элемента И, выходы второго и третьего элементов И соединены с входами элемента ИЛИ, выход которого соединен с единичным входом триггера выдачи, выход которого соединен с соответствующим информационные выходом устройства, нулевые входы триггеров вьщачи и установочные входы счетчиков всех информационных каналов объединены с единичным входом триггера разрешения и. подключены к второму управляющему входу устройства, выход элемента ИЛИ соединен с первым входом элемента И и через элемент задержки с нулевым входом триггера разрешения, выход которого соединен с вторым входом элемента И, выход которого соединен с запросным выходом устройства, Источники информации, ринятые во внимание при экспертизе 1. Гольденберг Л.М, Импульсные цифровые устройства. М., Связь, 973, с. 448. 2. Авторское свидетельство СССР 610101, кл. б 06F 3/04, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1984 |

|

SU1264182A2 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1989 |

|

SU1679492A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения абонентов с каналами связи | 1984 |

|

SU1233158A1 |

| Устройство для восстановления информации в многоканальных вычислительных системах | 1986 |

|

SU1305683A1 |

| Устройство для счета изделий | 1985 |

|

SU1305737A1 |

| Устройство для обмена информацией между эвм и магнитным накопителем | 1984 |

|

SU1218391A1 |

вмл. htiatti

Mriulotn I xf

Авторы

Даты

1983-02-28—Публикация

1981-10-19—Подача