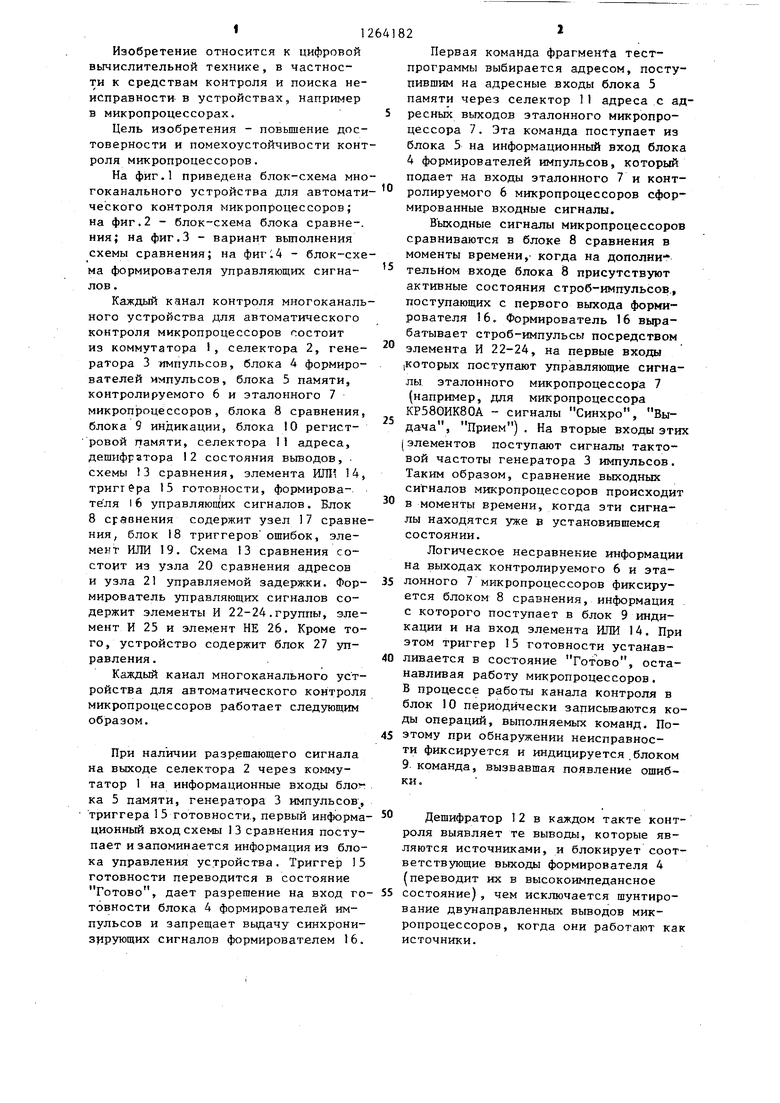

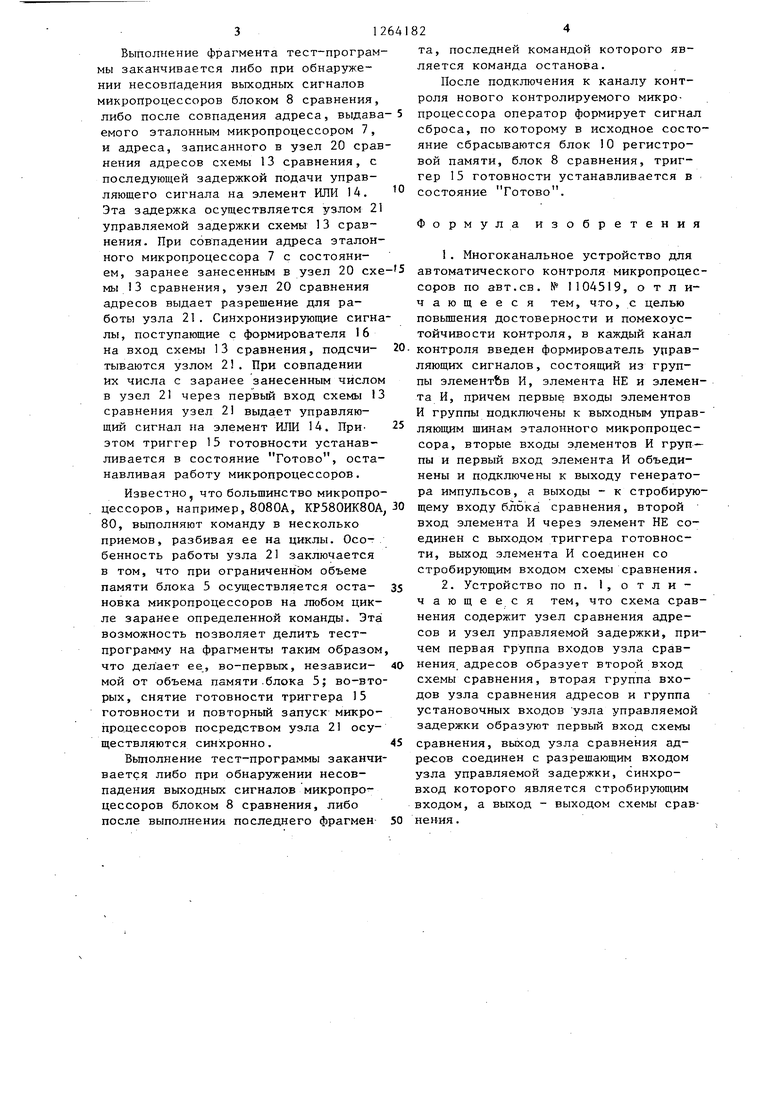

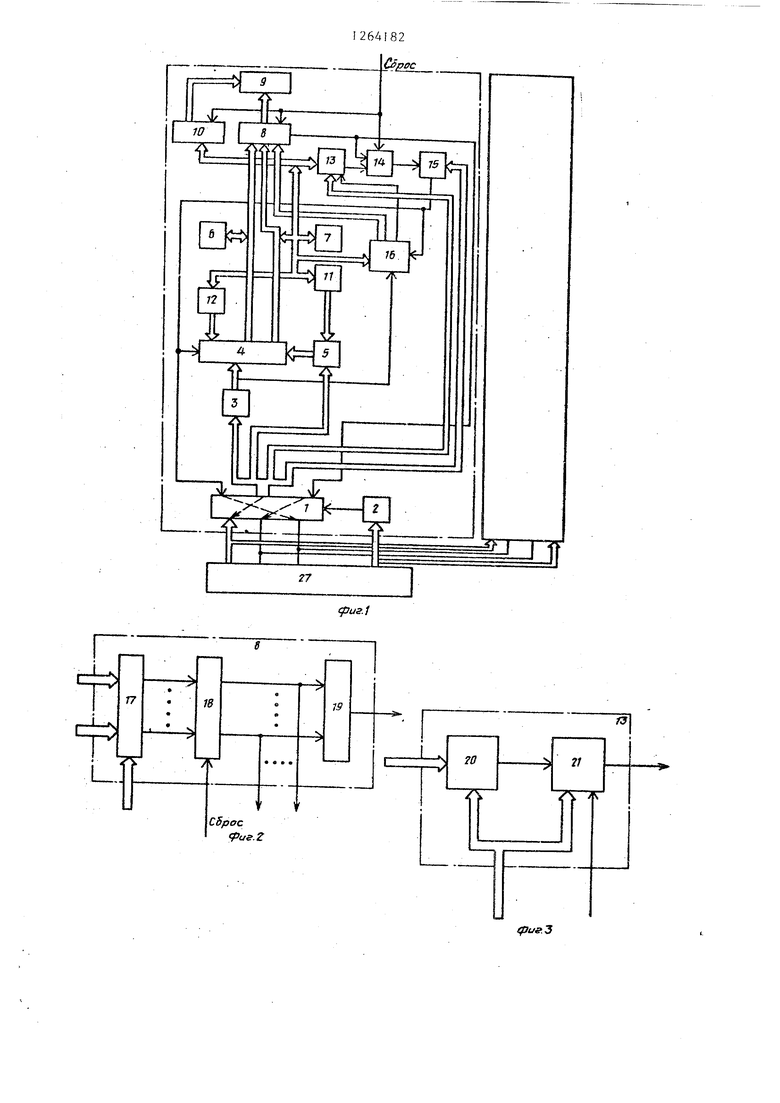

Го Изобретение относится к цифровой вычислительной технике, в частности к средствам контроля и поиска неисправности в устройствах, например в микропроцессорах. Цель изобретения - повьшение достоверности и помехоустойчивости конт роля микропроцессоров. На фиг.1 приведена блок-схема мно гоканального устройства для автомати ческого контроля микропроцессоров; На фиг.2 - блок-схема блока сравне-. ния; на фиг.З - вариант вьшолнения схемы сравнения; на фиг 14 - блок-схе ма формирователя управляющих сигналов . Каждый канал контроля многоканаль ного устройства для автоматического контроля микропроцессоров постоит из коммутатора 1, селектора 2, генератора 3 импульсов, блока 4 формирователей импульсов, блока 5 памяти, контролируемого 6 и эталонного 7 микропроцессоров, блока 8 сравнения, блока 9 индикации, блока 10 регистровой памяти, селектора 11 адреса, дешифратора 12 состояния вьгоодов, . схемы 3 сравнения, элемента ШП 14, триггера 15 готовности, формирователя 1б управляющих сигналов. Блок 8 сравнения содержит узел 17 сравне ния, блок 18 триггеровошибок, элемент ИЛИ 19. Схема 13 сравнения состоит из узла 20 сравнения адресов и узла 21 управляемой задержки. Формирователь управляющих сигналов содержит элементы И 22-24.группы, элемент И 25 и элемент НЕ 26. Кроме того, устройство содержит блок 27 управления . Каждый канал многоканального устройства для автоматического контроля микропроцессоров работает следзпощим образом. При наличии разрешающего сигнала на выходе селектора 2 через коммутатор 1 на информационные входы блог ка 5 памяти, генератора 3 импульсов триггера 1 5 готовности., первый информа ционный вход схемы 13 сравнения поступает и запоминается информация из бло ка управления устройства. Триггер 15 готовности переводится в состояние Готово, дает разрешение на вход го товности блока А формирователей импульсов и запрещает выдачу синхронизирующих сигналов формирователем 16 Первая команда фpaгмeнta тестпрограммы выбирается адресом, поступившим на адресные входы блока 5 памяти через селектор 11 адреса с адресных выходов эталонного микропроцессора 7. Эта команда поступает из блока 5 на информационный вход блока 4 формирователей импульсов, который подает на входы эталонного 7 и контролируемого 6 микропроцессоров сформированные входные сигналы. Выходные сигналы микропроцессоров сравниваются в блоке 8 сравнения в моменты времени, когда на дополни- тельном входе блока 8 присутствуют активные состояния строб-импульсов., поступающих с первого выхода формирователя 16„ Формирователь 16 вырабатывает строб-импульсы посредством элемента И 22-2А, на первые входы |Которых поступают управляющие сигналы эталонного микропроцессора 7 (например, для микропроцессора КР580ИК80А - сигналы Синхро, Выдача, Прием) . На вторые входы этих (элементов поступают сигналы тактовой частоты генератора 3 импульсов. Таким образом, сравнение выходных сигналов микропроцессоров происходит в моменты времени, когда эти сигналы находятся уже в установившемся состоянии. Логическое несравнение информации на выходах контролируемого 6 и эталонного 7 микропроцессоров фиксируется блоком 8 сравнения, информация . с которого поступает в блок 9 индикации и на вход элемента ИЛИ 14. При этом триггер 15 готовности устанавливается в состояние Готово, останавливая работу микропроцессоров. В процессе работы канала контроля в блок 10 периодически записываются коды операций, выполняемых команд. Поэтому при обнаружении неисправности фиксируется и индицируется.блоком 9. команда, вызвавшая появление ошибки. Дешифратор 12 в каждом такте контроля выявляет те выводы, которые являются источниками, и блокирует соответствующие выходы формирователя 4 (переводит их в высокоимпедансное состояние), чем исключается шунтирование двунаправленных выводов микропроцессоров, когда они работают как источники.

312

Выполнение фрагмента тест-программы заканчивается либо при обнаружении несовпадения выходных сигналов микропроцессоров блоком 8 сравнения, либо после совпадения адреса, выдава емого эталонным микропроцессором 7, и адреса, записанного в узел 20 сравнения адресов схемы 13 сравнения, с последующей задержкой подачи управляющего сигнала на элемент ИЛИ 14. Эта задержка осуществляется узлом 21 управляемой задержки схемы 13 сравнения. При совпадении адреса эталонного микропроцессора 7 с состоянием, заранее занесенным в узел 20 схе мы 13 сравнения, узел 20 сравнения адресов выдает разрешение для работы узла 21. Синхронизирующие сигналы, поступающие с формирователя 16 на вход схемы 13 сравнения, подсчитываются узлом 2. При совпадении их числа с заранее занесенным числом в узел 21 через первый вход схемы 13 сравнения узел 2 выдает управляющий сигнал на элемент ИЛИ 14. Приэтом триггер 15 готовности устанавливается в состояние Готово, останавливая работу микропроцессоров.

Известно, что большинство микропроцессоров, например, 8080А, КР580ИК80А, 80, выполняют команду в несколько приемов, разбивая ее на циклы. Особенность работы узла 21 заключается в том, что при ограниченном объеме памяти блока 5 осуществляется остановка микропроцессоров на любом цикле заранее определенной команды. Эта возможность позволяет делить тестпрограмму на фрагменты таким образом что делает ее, во-первых, независи- мой от объема памяти.блока 5; во-вторых, снятие готовности триггера 15 готовности и повторный запуск микропроцессоров посредством узла 2 осуществляются синхронно.

Вьтолнение тест-программы заканчивается либо при обнаружении несовпадения выходных сигналов микропроцессоров блоком 8 сравнения, либо после выполнения последнего фрагмен

824

та, последней командой которого является команда останова.

После подключения к каналу контроля нового контролируемого микропроцессора оператор формирует сигнал сброса, по которому в исходное состояние сбрасываются блок 10 регистровой памяти, блок 8 сравнения, триггер 15 готовности устанавливается в состояние Готово.

Формула изобретения

1.Многоканальное устройство для автоматического контроля микропроцессоров по авт.св. № 1104519, отличающееся тем, что, с целью повьшения достоверности и помехоустойчивости контроля, в каждый канал контроля введен формирователь управляющих сигналов, состоящий из группы элементов И, элемента НЕ и элемента И, причем первые входы элементов

И группы подключены к выходным управляющим шинам эталонного микропроцессора, вторые входы элементов И группы и первый вход элемента И объединены и подключены к выходу генератора импульсов, а выходы - к стробирующему входу блока сравнения, второй вход элемента И через элемент НЕ соединен с выходом триггера готовности, выход элемента И соединен со стробирующим входом схемы сравнения.

2.Устройство по п, 1, о т л и чающееся тем, что схема сравнения содержит узел сравнения адресов и узел управляемой задержки, причем первая группа входов узла сравнения адресов образует второй вход схемы сравнения, вторая группа входов узла сравнения адресов и группа установочных входов узла управляемой задержки образуют первый вход схемы сравнения, выход узла сравнения адресов соединен с разрешающим входом узла управляемой задержки, синхровход которого является стробирующим входом, а выход - выходом схемы сравнения.

-а

гз

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Устройство для контроля параллельных микропроцессорных интерфейсов | 1982 |

|

SU1040489A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1182520A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

Изобретение относится к цифровой вычислительной технике, в частности к средствам контроля и поиска неисправности в микропроцессорах. .Цель изобретения - повышение достоверности и помехоустойчивости контроля микропроцессоров. Устройство состоит .из блока управления и N каналов контроля, каждый из которых содержит коммутатор, селектор, генератор, формирователь сигналов, блок памяти, селектор адреса, контролируемый и эталонный блоки, дешифратор состояйия выводов эталонного блока схему сравнения, элемент ИЛИ, триг- . гер готовности, блок регистровой памяти, блок сравнения, блок индикации, формирователь управляюпщх сигналов . Блок управления с большой частотой опрашивает каждый канал контроля и, если он готов, по частям заносит в него тест-программу и запускает ее. Контроль осзпцествляется посредством сравнения выходных сигналов контролируемого микропроi цессора с эталонным образцом. При несравнении информации блок индика(Л ции фиксирует код невыполняемой команды и разряды, в которых обнаружено несравнение. Последней командой тест-программы является команда останова, сигнализ11рующая об исправности контролируемого микропро1 Э цессора. 1 з.п. ф-лы, 4 ил. 00 ю

срие.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1984-06-22—Подача