Изобретение относится к вычислительной технике, а именно к запоми- наюищм устройствам .на цилиндрических магнитных доменах (ЦМД), и может быть использовано для переадресации информации в ЦМД-кристалл ах, имекицих дефектные регистры хранения.

Известно устройство переадресации, информации, jцeйcтвиe которого основано на взаимном отталкивании двух доменов, один из которых является записываемлм, а другой служит в качестве метки годности для регистра хранения

Недостатком этого устройства является низкая надежность из-за слабого .электростатического взаимодействия доменов.

: Наиболее близкой к предлагаемой по технической сущности является система памяти с дефектными регистрами, содержащая блок репрограммируемой памяти, первый и второй регистры, первый и второй счетчики, логические блоки, входной коммутатор, и позволяющая обходить дефектные регистры храт нения в ЦМД-кристсШлах 2..

Недостатком данного устройства является болыыая аппаратурная избыточность, которая связана с использова-;

нием устройства для переадресации информации в ЦМД-кристаллах с такой организацией, которая не предусматрис вает возможность копирования доменов при считывании. Это приводит к необходимости перезаписывать только, что считанную из регистров хранения и переданную в регистр ввода-вывода инjO формацию, что связано с большими временными затрат ами.

В настоящее время серийно выпускаются ЦМД-кристаллы с блочным копированием, что позволяет исключить про15цедуру перезаписи за счет расщепления домена при его переходе из регистра хранения в регистр ввода-вывода. В результате один домен остается в регистре, а другой по регистру ввода20вывода передается к датчику считывания. Наличие переключателей-репликаторов в ЦМД-кристалле позволяет значительно уменьшить аппаратурные затраты на организацию переадресации 25 информации в запоминающих устройствах на ЦМД и, как следствие, уменьшить их стоимость, габариты, потребление энергии, увеличить нгщежность. Цель изобретения - упрощение уст30ройства за счет уменьшения числа

счетчиков и регистров и иной органи , эации процесса выборки информации.

Указанная цель достигается тем, что устройство для переадресации информации , содержащее блок регфограммируемой памяти, выходы которого соединены с входами первого регистра, (счетчик, выходы которого соединены с входами первой группы логичечзкого Ълойа, а входы счетчика соединены с входами второй группы логического блока, входы третьей группы которого соединены с выходами входного коммутатора, входы первой, группы которого являются первыми информационными входами устройства, входы второй и третьей групп входного коммутатора соединены соответственно с первой и второй управляющими шинами, выходы ; логического блока соединены с входами первой группы второго регистра, входы второй группы которого соединены с третьей управляющей шиной, а выходы первой группы второго регистра соединены с входами четвертой группы логического блока, дополнительно содержит выходной коммутатор, входы первой группы которого соединены с выходами второй группы второго регистра, входы второй и третьей группы выходного коммутатора соединены соответственно с первыми и вто-. рыми управляющими шинами, входы пятой и шестой групп логического блока соединены соответственно с первыми и вторыми управляющилш шинами, входы четвертой группы входного коммутатора являются вторым информационным входом устройства, выходы первого регистра соединены с входами счетчика, первый и второй выходы выходного коммутатора являются соответственно первым и вторым информационными выходами устройства.

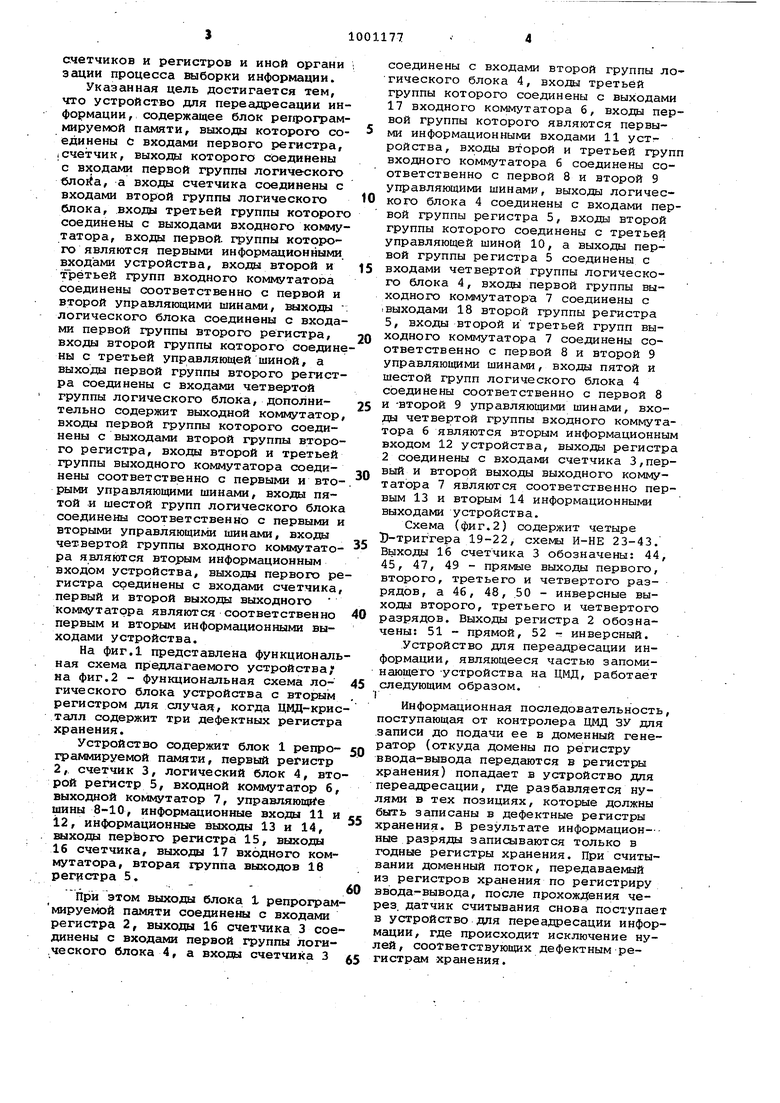

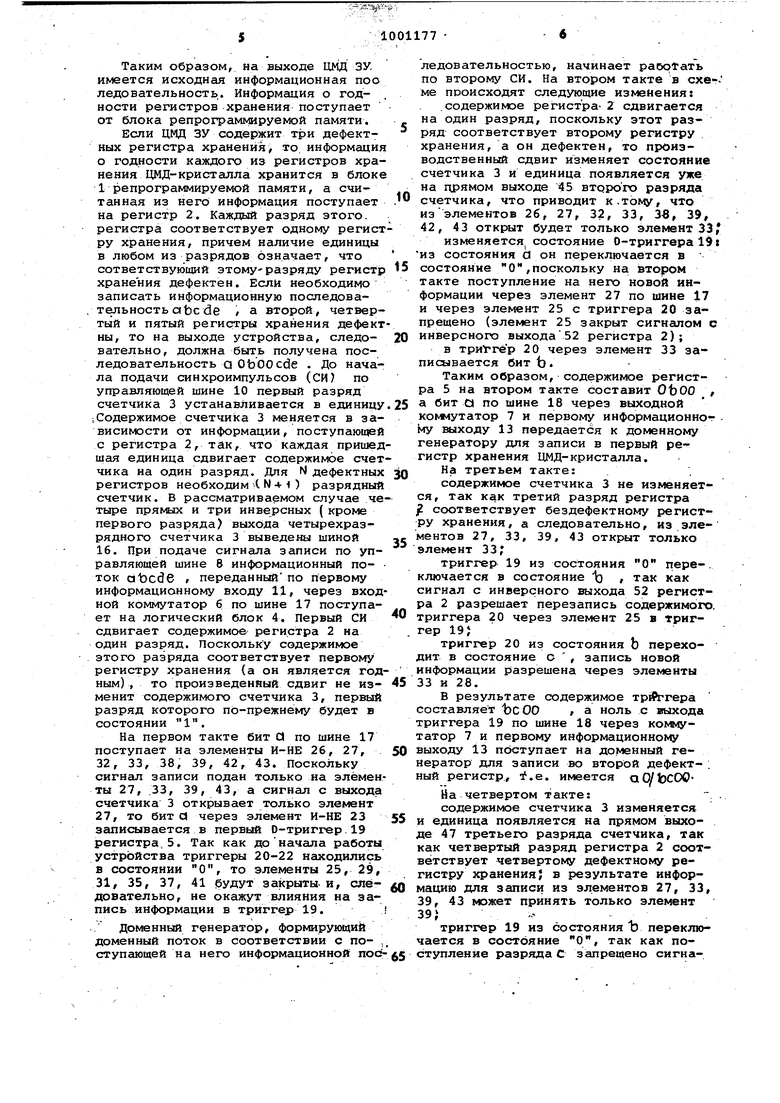

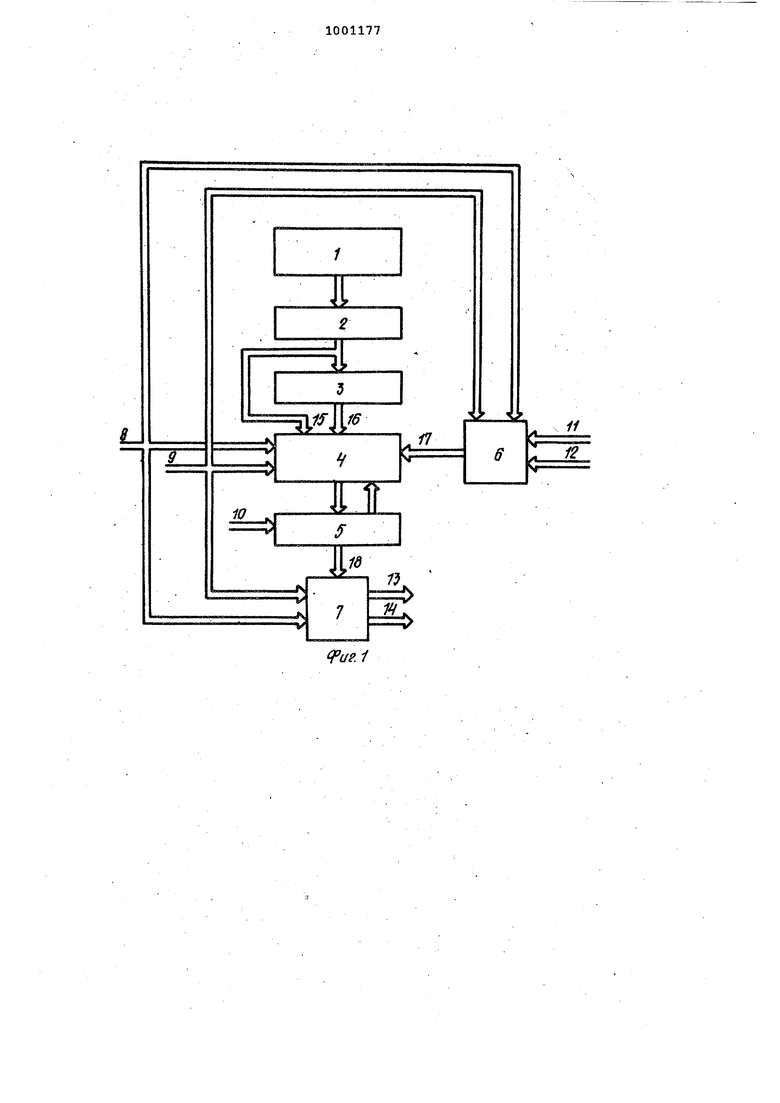

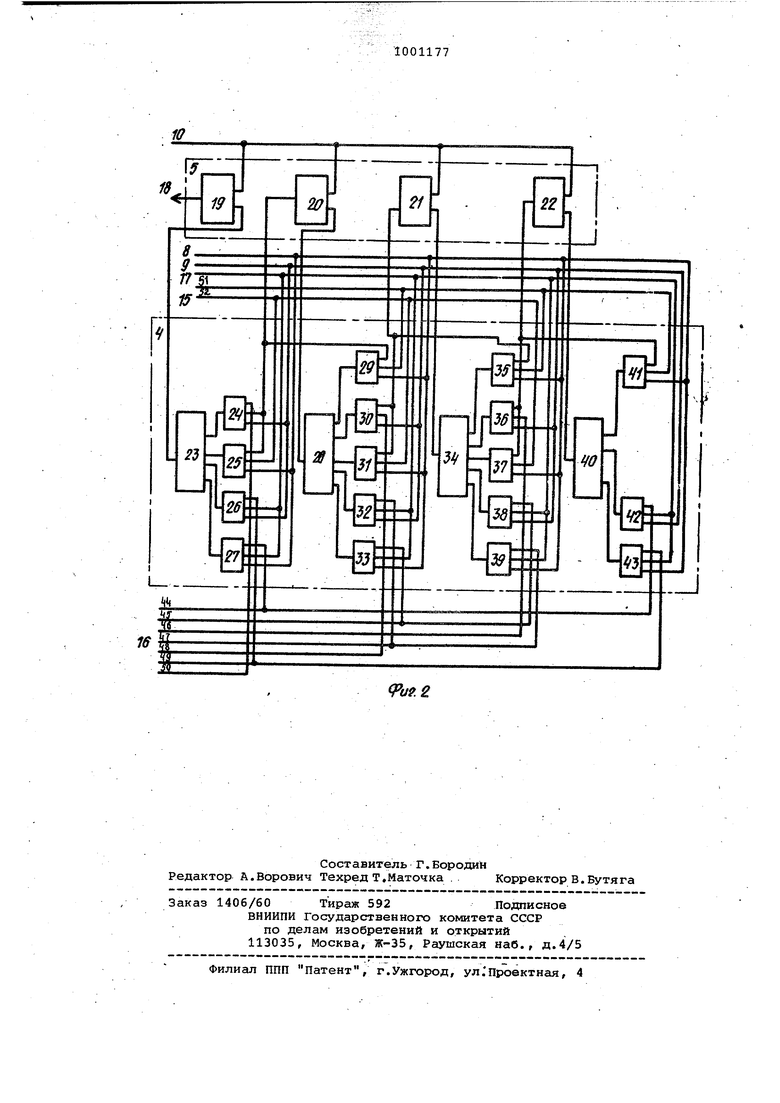

На фиг.1 представлена функциональная схема предлагаемого устройства, на фиг.2 - функциональная схема логического блока устройства с вторым регистром для случая, когда ЦМД-кристалл содержит три дефектных регистра хранения.

Устройство содержит блок 1 репрограммируемой памяти, первый регистр 2, счетчик 3, логический блок 4, второй регистр 5, входной коммутатор 6, выходной коммутатор 7, управляющие шины 8-10, информационные входы 11 и 12, информационные выходы 13 и 14, выходы первого регистра 15, выходы 16 счетчика, выходы 17 входного коммутатора, вторая группа выходов 18 регистра 5.

При этом выходы блока 1 репрограммируемой памяти соединены с входами регистра 2, выходы 16 счетчика 3 соединены с входами первой группы логи.ческого блока 4, а входы счетчика 3

соединены с входами второй группы лотического блока 4, входы третьей группы которого соединены с выходами 17 входного коммутатора б, входы первой группы которого являются первыми информационными входами 11 устг ройства, входы второй и третьей груп входного коммутатора 6 соединены соответственно с первой 8 и второй 9 управляющими шинами, выходы логического блока 4 соединены с входами первой группы регистра 5, входы второй группы которого соединены с третьей управляющей шиной 10, а выходы первой группы регистра 5 соединены с входами четвертой группы логического блока 4, входы первой группы выходного коммутатора 7 соединены с iвыходами 18 второй группы регистра 5, входы второй и третьей групп выходного коммутатора 7 соединены соответственно с первой 8 и второй 9 управляющими шинами, входы пятой и шестой групп логического блока 4 соединены соответственно с первой 8 и -второй 9 управляющими шинами, входы четвертой группы входного коммутатора 6 являются вторым информационны входом 12 устройства, выходы регистр 2 соединены с входами счетчика 3,первый и второй выходы выходного коммутатора 7 являются соответственно первым 13 и вторым 14 информационными выходами устройства.

Схема (фиг.2) содержит четыре D-триггера 19-22, cxetm И-НЕ 23-43. Выходы 16 счетчика 3 обозначены: 44, 45, 47, 49 - прямые выходы первого, второго, третьего и четвертого разрядов, а 46, 48, 50 - инверсные выходы второго, третьего и четвертого разрядов. Выходы регистра 2 обозначены: 51 - прямой, 52 -г инверсный.

Устройство для переадресации информации, являющееся частью запоминающего -устройства на ЦМД, работает следующим образом. Т

Информационная последовательность поступающая от контролера ЦМД ЗУ для .записи до подачи ее в доменный генератор (откуда домены по регистру ввода-вывода передаются в регистры хранения) попадает в устройство для переадресации, где разбавляется нулями в тех позициях, которые должны быть записаны в дефектные регистры хранения. В результате информацион-ные разряды записываются только в годные регистры хранения. При считывании доменный поток, передаваемый из регистров хранения по регистриру ввода-вывода, после прохождения через, датчик считывания снова поступае в устройство для переадресации информации, где происходит исключение нулей, соответствующих дефектным регистрам хранения. Таким образом, на выходе ЦМД ЗУ. имеется исходная информационная поо ледовательность. Информация о годности регистров хранения поступает от блока репрограммируемой памяти. Если ЦМД ЗУ содержит три дефектных регистра хранения, то информация 0годности каждого из регистров хранения ЦМД-кристалла хранится в блоке 1репрограммируемой памяти, а считанная из него информация поступает на регистр 2. Каждый разряд этого, регистра соответствует одному регист ру хранения, причем наличие единицы в любом из разрядов означает, что сответствующий этому-разряду регистр хранения дефектен. Если необходимо записать информационную последовательность afecde а второй, четвертый и пятый регистры хранения дефект ны, то на выходе устройства, следовательно, должна быть получена последовательность а ObOOcde . До начала подачи синхроимпульсов (СИ) по управляющей шине 10 первый разряд счетчика 3 устанавливается в единицу ;Содержимое счетчика 3 меняется в зависимости от информгщии, поступающей с регистра 2, так, что каждая пришед шая единица сдвигает содержикюе счет чика на один разряд. Для N дефектных регистров необходим ( N ц. О разрядный счетчик. В рассматриваемом случае че тыре прямых и три инверсных ( кроме первого разряда) выхода четырехразрядного счетчика 3 выведены шиной 16. При подаче сигнала записи по управляющей шине 8 информационный поток abode г переданныйпо первому информационному входу 11, через вход ной коммутатор 6 по шине 17 поступает на логический блок 4, Первый СИ сдвигает содержимое регистра 2 на один разряд. Поскольку содержимое этого разряда соответствует первому регистру хранения (а он является год ным) , то произведенный сдвиг не изменит содержимого счетчика 3, первый разряд которого по-прежнему будет в состоянии 1, На первом такте бит d по шине 17 поступает на элементы И-НЕ 26, 27, 32, 33, 38, 39, 42, 43. Поскольку сигнал записи подан только на элемен ты 27, .33, 39, 43, а сигнал с выхода счетчика 3 открывает только элемент 27, то бита через элемент И-НЕ 23 записывается в первый 0-триггер-19 регистра,5. Так как доначала работы устройства триггеры 20-22 находились в состоянии О, то элементы 25, 29, 31, 35, 37, 41 будут закрыты, и, следовательно, не окажут влияния на запись информации в триггер 19. Доменный генератор, формирующий доменный поток в соответствии с поступающей на него информационной поб ледовательностью, начинает по второму СИ. На втором такте в схе-ме ПРОИСХОДЯТ следующие изменения: .содержимое регистра- 2 сдвигается на один разряд, поскольку этот разряд соответствует второму регистру хранения, а он дефектен, то производственный сдвиг изменяет состояние счетчика 3 и единица появляется уже на дрямом выходе 45 второго разряда счетчика, что приводит к.тому, что изэлементов 26, 27, 32, 33, 36, 39, 42, 43 открыт будет только элемент 33 изменяется состояние 0-триггера 191 из состояния О он переключается в состояние О,поскольку на втором такте поступление на него новой информации через элемент 27 по шине 17 и через элемент 25 с триггера 20 запрещено (элемент 25 закрыт сигналом с инверсного выхода 52 регистра 2); в 20 через элемент 33 записывается бит b. Таким образом, содержимое регистра 5 на втором такте составит ОЪОО , а бит а по шине 18 через выходной коммутатор 7 и первому информационному выходу 13 передается к доменному генератору для записи в первый регистр хранения ЦМД-кристалла. На третьем такте: содержимое счетчика 3 не изменяется, так как третий разряд регистра f. соответствует бездефектному регистру хранения, а следовательно, из элементов 27, 33, 39, 43 открыт только элемент 33; триггер 19 из состояния О пере-, ключается в состояние , так как сигнал с инверсного выхода 52 регистра 2 разрешает перезапись содержимого, триггера 20 через элемент 25 в триггер 19 J триггер 20 из состояния Ь переходит в состояние о , запись новой информации разрешена через элементы 33 и 28. В результате содержимое тррРггера составляет ЪсОО / а ноль с выхода триггера 19 по шине 18 через KONwyтатор 7 и первому информационному выходу 13 псютупает на до.менный генератор для записи во второй дефект- ; ный регистр, т.е. имеется аСуЬсООНа четвертом такте:. . содержимое счетчика 3 изменяется и единица появляется на прямом выходе 47 третьего разряда счетчика, так как четвертый разряд регистра 2 соответствует четвертому дефектному регистру хранения; в результате информацию для записи из элементов 27, 33, 39, 43 может принять только элемент 39}..триггер 19 из состояния о переключается в состояние О, так как поступление разряда С запрещено сигнаом с инверсного выхода 52 региста 2 ;I

триггер 20 не изменяет своего остояния, так как информация переаписывается в него через элемент 9, который управляется сигналом с рямого выхода 51 регистра 2;

в триггер 21 через элемент 39 и 34 по шине 17 поступает бит d .

Таким образом, после четвертого И имеют ООЪ/Ос О .

На пятом такте: ;

содержимое счетчика 3 изменяется, диница появляется на прямом выходе 45 четвертого разряда счетчика, так как пятый разряд регистра 2 соответ- 15 ствует дефектному регистру хранения/ в результате для приема новой инфорации по шине 17 открыт только элемент 43;

триггер 19 остается в состоянии 20 О, так как на него не поступает ни информация по шине 17 через элемент 27, ни информация с триггера 20, i так как она закрыта сигналом с .инверсного выхода 52 регистра 2, 25

триггеры 20 и 21 не изменяют своего состояния: в триггер 20 перезаписывается Ъ через элемент 29, а в триггер 21 - С через элемент 35, что разрешено сигналом с прямого выхода JQ 51 регистра 2;

в триггер 22 записывается бит © через элементы 43 и 40.

Таким образом, имеют aObO/D.cde .

Начиная с шестого такта, регистр -. 5 йачинает работать как обычный сдвиговый регистр. Связь триггеров 19-22 осуществляется через элементы 25, 31, 37, на которые подан разрешающий сигнал. Все остальные информационные разряды, следующие за G , записыва- ются в триггер 22 по шине 17 через элементы 43 и 40.

При подаче по второй управляющей Шине 9 сигнала чтения на выход 17 коммутатора 6 поступает информация по 45 второму информационному входу 12, соединенному с датчиком считывания, который принимает информацию с регистров хранения ЦМД-кристалла qobOOcde .50

: До начала чтения первый разряд счетчика 3, так же, как и в случае записи, устанавливается в единицу, и производится обращение к блоку 1 репрограммируемой памяти для передачи 55 в регистр 2 информации о состоянии регистров хранения.

При чтении информации сдвиг рё- . гистра хранения карты годности начинается по второму СИ.

На первом такте информационный разряд Q поступает по шине 17 на элементы 26, 32, 38, 42, ко так как разрешающий сигнал с прямого выхода 44 первого разряда счетчика 3 подан 5

только на элемент 42, тос( через элемент 42 и 40, поступает на запись в триггер 22. Состояние триггеров 19-21 не изменяется, поскольку исходное , состояние регистра 5-0000. На втором такте происходит перезапись содержимого триггера 22 в триггер 21 через элементы 36 и 34 по разрешающему сигналу с инверсного выхода 46 второго разряда счетчика 3 (его содержимое при сдвиге регистра 2 не изменяется, так как первый разряд этого регистра соответствует первому регистру хранения, а он бездефектен). Очередной бит О по шине 17 записывается через элементы 43 и 40 в триггер 22. Таким образом, в регистре 5 имеют 0000.

На третьем такте второй разряд регистра 2 меняет содержимое счетчика 3, единица появляется на прямом выходе его второго разряда. Этот сигнал открывает элемент 38, и пришедший по шине 17 информационный разряд из третьего регистра хранения t) записывается в триггер 21.Содержимое триггера 21 перписывается через элементы 30 и 28 по разрешающему сигналу с инверсного выхода 48 третьего разряда счетчика 3 в триггер 20. Перезапись информации из триггера 22 в триггер 21 запрещена сигналом с инверсного выхода 46 второго разряда счетчика 3. В результате к концу третьего такта в регистре р имеют Оа b О .

На четвёртом такте содержимое счетчика 3 не изменяется, так как третьему разряду регистра 2 соответствует .бездефектный третий регистр хранения. Следовательно, разрешающий сигнал с прямого выхода 45 второго разряда счетчика 3.открывает элемент 38, и очередной бит информационного потока О по шине 17 через элементы 38, 34 записывается в триггер 21. Разрешающие сигналы с инверсных выходов 48, 50 третьего и четвертого разрядов счетчика 3 обеспечивают перезапись информации из триггеров 21 и 20 в триггерах 20 и 19 соответственно. Таким образом, в регистре 5 имеют аЬ 00 .

Начиная с пятого такта, на информационном выходе 14, соединенном с устройством управления запоминающего устройства, появляется считываемая информационная последовательность. Выход 14 через выходной коммутатор 7 соединен с выходом 18 регистра 5. Коммутация считанной информации на выход 14 происходит при подаче сигнала по второй управляющей шине 9..

На пятом такте происходит изменение содержимого счетчика 3 за счет единицы в четвертом разряде регистра 2, в результате на прямом выходе 47 третьего разряда счетчика 3, появляется единица которая открывает элемент 32, и очередной бит информацион ной последовательности О по шине 17 через элементы 32 и 28 записывается в триггер 20. Информация триггера 20Ь через элементы 24, 23 записывается по разрешающему сигналу с инверсного выхода 50 четвертого разряда счетчика 3 в триггер 19, а бита по шине 18 через выходной коммутатор 7 поступает на второй информационный выход 14, В результате содержимое регистра 5составляета/foOO На шестом такте снова меняется со держимое счетчика 3, так как пятый разряд регистра 2 соответствует пято му дефектному регистру хранения. На прямом выходе 49 четвертого разряда счетчика появляется 1, которая открывает элемент 26, и очередной бит информационной последовательности записывается:, через элементы 26 и 23 в триггер 19. Начиная с этого момента, все последующие информационные биты записываются в триггер 19, а на его выходе формируется выходная информационная последовательность. В результате в устройство управления передается информационная последовательность cifecde V Предлагаемое, устройство позволяет уменьшить аппаратурные затраты при трех дефектных регистрах на 25%, для десяти - на 15%. Произведя оценку ап паратурных затрат при трех дефектных регистрах хранения при реализации .устройства-прототипа на элементах се рии К155 (К133), получают два четырехразрядных счетчика (2 корпуса), два четырехразрядных регистра на D-триггерах (4 корпуса), задержку на три такта, реализованную на D-тригге рах (2 корпуса), 26 элементов 2И-НЕ, включая коммутатор (8 корпусов), два элемента ЗИ-НЕ {1 корпус). Итого 17 корпусов. Реализуя предлагаемое устроиство на элементах той же серии, получают четырехразрядный счетчик (1 корпус), четырехразрядный триггер на О-триггерах (2 корпуса), 6 элементов 2И-НЕ (для коммутаторов) (2 корпуса), 18 элементов ЗИ-НЕ (6 корпусов), два элемента 8И-НЕ и один 4И-НЕ (1 корпус). Итого 13 корпусов.. Как следствие уменьшения аппаратурных затрат, уменьшается потребление энергии, габариты устройства, число паяных соединений. Надежность устройства повышается, стоимость уменьшается. Формула изобретений Устройство для переадресации информации, содержащее блок репрограммируемой памяти, выходы которого соединены с входами первого регистра, счетчика, выходы которого соединены с входами первой группы логического Ьлока, а входы счетчика соединены с ; входами второй группы логичэского блока, входы третьей группы которого соединены с выходами входного коммутатора, входы первой 1РУППН которого являются першами информационными входами устройства, входы второй и третьей групп входного коммутатора соединены соответственно с первой и второй управляющими шинами, выходы логического блока соединены с входами первой группы второго регистра, входа второй группы которого, соединены с третьей управляющей шиной, а выходы первой группы второго регистра соединены с входами четвертой группы логического блока, отличающееся тем, что, с целью упрощения устройства, оно содержит выходной коммутатор, входы первой группы которого соединены с выходами второй группы второго регистра, входы второй и третьей группы выходного коммутатора Соединены соответственно с первыми и вторыми управляющими шинами, входы пятой . и шестой групп логического блока соединены соответственно с первыми и вторыми управляющими шинами, входы четвертой группы входного коммутатора являются вторым информационным входом устройства, выходы первого регистра соединены с входами счетчика, первый и второй выходы выходного коммутатора являются соответственно первым и BTOpBBvi информационными выходами устройства. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3921156, кл. 340-174 ТР, опублик. 1975. ,2. Патент США 4073012., кл. 365-1, опублик. 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Устройство для переадресации информации в доменной памяти | 1984 |

|

SU1188788A1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1352496A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357966A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357968A1 |

| Устройство управления для кассетной памяти на цилиндрических магнитных доменах | 1987 |

|

SU1495850A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

зЙ1

fe

иг.1

Ч о

11

/7 F

Авторы

Даты

1983-02-28—Публикация

1981-10-05—Подача