Изобретение относится к вычислительной технике, а именно к устрой- й твам для управления обменом информацией, и может быть использовано при обмене информацией между различными блоками вычислительных систем.

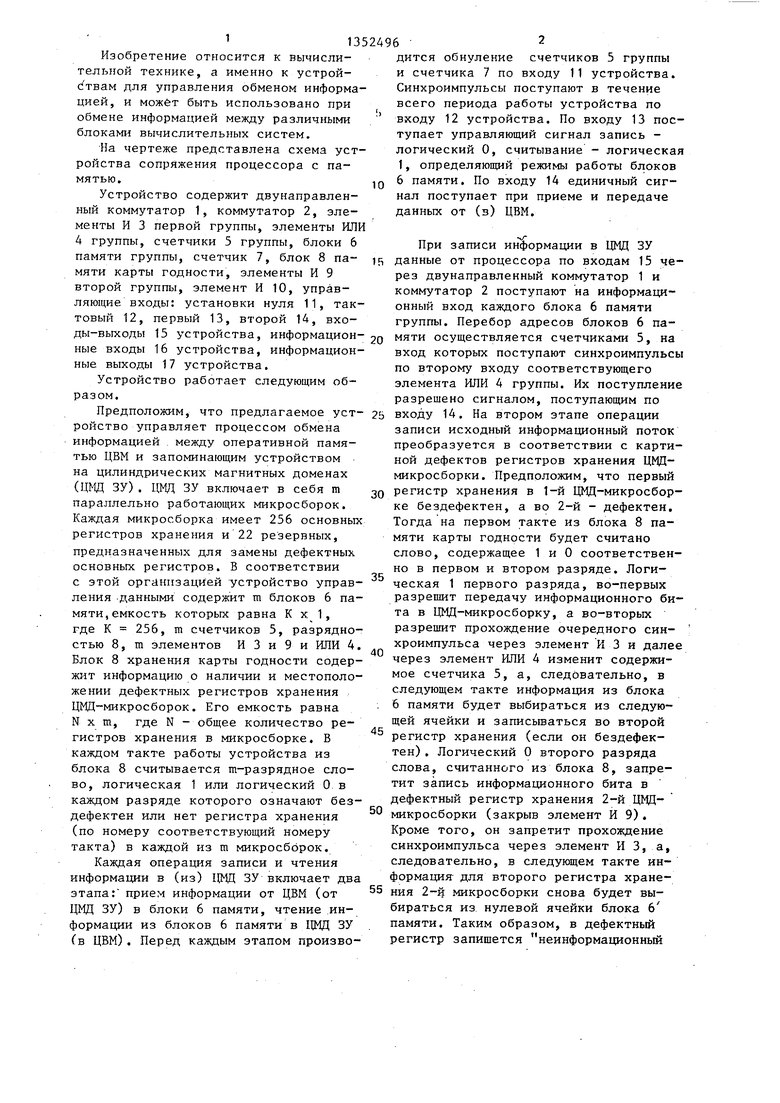

На чертеже представлена схема устройства сопряжения процессора с памятью.

Устройство содержит двунаправленный коммутатор 1, коммутатор 2, элементы И 3 первой группы, элементы ИЛИ 4 группы, счетчики 5 группы, блоки 6 памяти группы, счетчик 7, блок 8 памяти карты годности, элементы И 9 второй группы, элемент И 10, управляющие входы: установки нуля 11, тактовый 12, первый 13, второй 14, входы-выходы 15 устройства, информацион- 2о мяти осуществляется счетчиками 5, на

ные входы 16 устройства, информационные выходы 17 устройства.

Устройство работает следующим образом.

вход которых поступают синхроимпульсы по второму входу соответствующего элемента ИЛИ 4 группы. Их поступление разрешено сигналом, поступающим по

Предположим, что предлагаемое уст- 25 входу 14. На втором этапе операции

ройство управляет процессом обмена информацией между оперативной памятью ЦВМ и запоминающим устройством на цилиндрических магнитных доменах (ЦМД ЗУ). ЦМД ЗУ включает в себя m параллельно работающих микросборок. Каждая микросборка имеет 256 основных регистров хранения и 22 резервных, предназначенных для замены дефектных основных регистров. В соответствии с этой организацией устройство управления .данными содержит m блоков 6 памяти, емкость которых равна К , где К 256, m счетчиков 5, разрядностью 8, m элементов И 3 и 9 и ИЛИ 4. Блок 8 хранения карты годности содержит информацию о наличии и местоположении дефектных регистров хранения ЦМД-микросборок. Его емкость равна N X т, где N - общее количество регистров хранения в микросборке. В каждом такте работы устройства из блока В считывается т-разрядное слово, логическая 1 или логический О в каждом разряде которого означают бездефектен или нет регистра хранения (по номеру соответствующий номеру такта) в каждой из m микросборок.

Каждая операция записи и чтения информации в (из) ЦМД ЗУ включает два этапа: прием информации от ЦВМ (от ЦМД ЗУ) в блоки 6 памяти, чтение информации из блоков 6 памяти в ЦМД ЗУ (в ЦВМ). Перед каждым этапом произво

дится обнуление счетчиков 5 группы и счетчика 7 по входу 11 устройства. Синхроимпульсы поступают в течение всего периода работы устройства по входу 12 устройства. По входу 13 поступает управляющий сигнал запись - логический О, считывание - логическая 1, определяющий режимы работы блоков 6 памяти. По входу 14 единичный сигнал поступает при приеме и передаче данных от (з) ЦВМ.

При записи информации в ЦМД ЗУ данные от процессора по входам 15 через двунаправленный коммутатор 1 и коммутатор 2 поступают на информационный вход каждого блока 6 памяти группы. Перебор адресов блоков 6 павход которых поступают синхроимпульсы по второму входу соответствующего элемента ИЛИ 4 группы. Их поступление разрешено сигналом, поступающим по

0

5

0

записи исходный информационный поток преобразуется в соответствии с картиной дефектов регистров хранения ЦМД- микросборки. Предположим, что первый регистр хранения в 1-й ЦМД-микросбор- ке бездефектен, а во 2-й - дефектен. Тогда на первом такте из блока 8 памяти карты годности будет считано слово, содержащее 1 и О соответственно в первом и втором разряде. Логическая 1 первого разряда, во-первых разрешит передачу информационного бита в ЦМД-микросборку, а во-вторых разрешит прохождение очередного синхроимпульса через элемент И 3 и далее через элемент ИЛИ 4 изменит содержимое счетчика 5, а, следовательно, в следующем такте информация из блока . 6 памяти будет выбираться из следующей ячейки и записываться во второй регистр хранения (если он бездефектен) . Логический О второго разряда слова, считанного из блока 8, запретит запись информационного бита в дефектный регистр хранения 2-й ЦВД-

микросборки (закрыв элемент И 9) . Кроме того, он запретит прохождение синхроимпульса через элемент И 3, а, следовательно, в следующем такте информация для второго регистра хранеS ния 2-й микросборки снова будет выбираться из нулевой ячейки блока 6 памяти. Таким образом, в дефектный регистр запишется неинформационный

ноль, а исходная информация будет сохранена.

При чтении сначала информация из ЦМД ЗУ через коммутатор 2 поступает на соответствующие информационные входы блоков 6. При этом на входе 13 - логический О, на входе 14 - логический 0. Первые биты от всех ЦМД- микросборок записываются в нулевые ячейки блоков 6 независимо от годности первых регистров хранения. По окончании синхроимпульса на выходах блока 8 имеем картину дефектов первых регистров хранения. Предположим, что в 1-й микросборке первый регистр бездефектен, а во 2-й микросборке - дефектен. Тогда логическая 1 первого разряда слова, считанного из блока 8, разрешит прохождение очередного син- хроимпульса, в результате чего содержимое соответствующего счетчика 5 изменится на единицу, а, следовательно, следуюпшй очередной бит информационного потока будет адресован в первую ячейку блока 6 памяти.

Логический О второго разряда слова, принятого от блока 8, обеспечит сохранение содержимого соответствующего счетчика 6, в результате чего, очередной бит, принятый от 2-й микросборки снова запишется в нулевую ячейку, в которую на предьщущем такте был записан неинформационный ноль из дефектного регистра. Таким образом, по окончании приема информации от ЦМД ЗУ в блоках6 памяти будет записан исходный информационный потЬк. По входу 13 устанавливается логическая 1, по входу 14 - логическая 1, и данные из блоков 6 -памяти передаются через блок 1 в процессор.

Формула изобретения

Устройство сопряжения процессора с памятью, содержащее двунаправлен- ный коммутатор, счетчик адреса карты годности, коммутатор, две группы элементов И, группу счетчиков, блок памяти карты годности, группу блоков памяти, группу элементов ИЛИ, информационный вход-выход двунаправленног коммутатора является информационным

ВНИИ1Ш Заказ 5567/49 Тираж 671 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

0

5 Q

5

0

5

0

5

0

входом-выходом устройства, подключаемым к процессору, первый информационный вход коммутатора является информационным входом устройства, подключаемым к памяти, второй информационный вход коммутатора соединен с вы- ходом двунаправленного коммутатора, входы сброса счетчиков группы и счетчика адреса карты годности соединены с входом сброса устройства, счетный вход счетчика адреса карты годности, тактовые входы блоков памяти группы и первые входы элементов И первой группы соединены с тактовым входом устройства, выход счетчика адреса карты годности соединен с адресным входом блока памяти карты годности, каждый выход которого соединен с вторыми входами соответствующих элементов И первой и второй групп, выходы элементов И второй группы образуют информационный выход устройства, подключаемый к памяти, выход каждого элемента И первой группы соединен с первым входом соответствующего элемента ИЛИ группы, выход каждого блока памяти группы соединен с соответствующим разрядом информационного входа двунаправленного коммутатора, управляющий вход которого соединен с входом режима записи-считывания устройства, отличающееся тем, что, с целью упрощения устрой- . ства, оно содержит элемент И, первый вход которого соединен с управляющим входом коммутатора и является входом режима процессор - память устройства, второй вход элемента И соединен с тактовым входом устройства, вьпсод элемента И соединен с вторыми входами элементов ИЛИ группы, выход каждо го из которых соединен со счетным входом соответствующего счетчика группы, выходы которых соединены с адресными входами соответствующих блоков памяти группы, информационный вход каждого из которых соединен с соответствующим разрядом выхода коммутатора, управляющий вход которого соединен с входом режима записи-считывания устройства, выход каждого блока памяти группы соединен с первым входом соответствующего элемента И второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357968A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357966A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

| Устройство для переадресации информации | 1981 |

|

SU1001177A1 |

| Устройство для переадресации информации в доменной памяти | 1984 |

|

SU1188788A1 |

| Устройство для обхода дефектных регистров в доменной памяти (его варианты) | 1985 |

|

SU1305773A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления обменом информацией между процессором и памятью в вычислительных системах. Цель изобретения состоит в упрощении устройства. Устройство содержит приемник-передатчик 1, коммутатор 2, элементы ИЗ - первой группы, элементы ИЛИ 4 группы, счетчики 5 группы, блоки памяти 6 группы, счетчик 7, блок хранения карты годности 8, элементы И 9 второй группы, элемент И 10. 1 ил. со СП 1чЭ иЙ СО Ot)

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1324487, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1987-11-15—Публикация

1985-12-16—Подача