Изобретение относится к вычислительной технике, а именно к устройствам для управления обменом информаци- ей, и может быть использовано при организации обмена информацией между различными блоками вычислительных систем.

Целью изобретения является повьше- ние достоверности функционирования и повышение быстродействия.

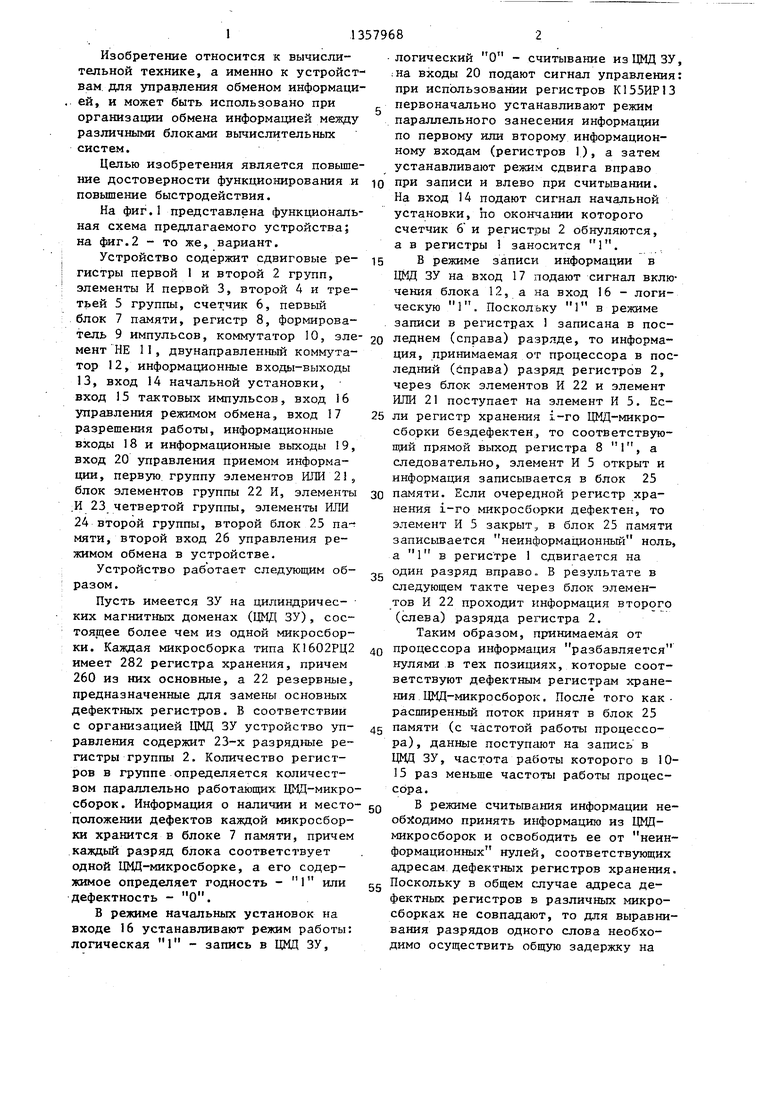

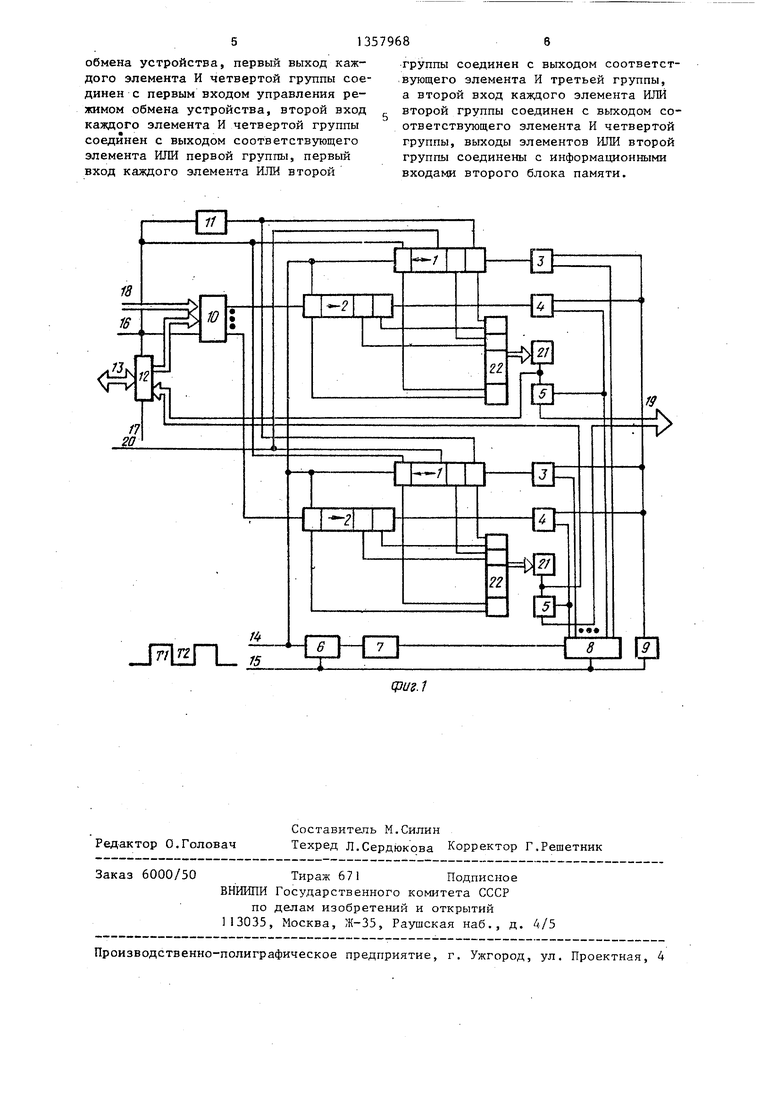

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - то же, вариант.

Устройство содержит сдвиговые регистры первой 1 и второй 2 групп, элементы И первой 3, второй 4 и третьей 5 группы, счетчик 6, первый блок 7 памяти, регистр 8, формирова135

тель 9 импульсов, коммутатор 10, эле- 2о леднем (справа) разряде, то информамент НЕ 11 , двунаправленн1)1й коммутатор 12, информационные входы-выходы 13, вход 14 начальной установки, вход 15 тактовых импульсов, вход 16 управления режимом обмена, вход 17 разрешения работы, информационные входы 18 и информационные выходы I9, вход 20 управления приемом информации, первую группу элементов РШИ 21, блок элементов группы 22 И, элементы .И 23 четвертой группы, элементы ИЛИ 24 второй группы, второй блок 25 па- мяти, второй вход 26 управления режимом обмена в устройстве.

Устройство работает следующим образом.

Пусть имеется ЗУ на цилиндричес- ких магнитных доменах (ЦМД ЗУ), сос- тоягцее более чем из одной микросборки. Каждая микросборка типа К1602РЦ2 имеет 282 регистра хранения, причем 260 из них основные, а 22 резервные, предназначенные для замены основных дефектньпс регистров. В соответствии с организацией ЦМД ЗУ устройство управления содержит 23-х разрядные регистры группы 2. Количество регистров в группе определяется количеством параллельно работающих ЦМД-микро- сборок. Информация о наличии и местоположении дефектов каждой микросборки хранится в блоке 7 памяти, причем каждый разряд блока соответствует одной ЦМД-микросборке, а его содержимое определяет годность - 1 или дефектность - О.

В режиме начальных установок на входе 16 устанавливают режим работы: логическая 1 - запись в ЦМД ЗУ,

30

35

ция, принимаемая от процессора в последний (справа) разряд регистров 2, через блок элементов И 22 к элемент ИЛИ 21 поступает на элемент И 5. Ес25 ли регистр хранения i-ro ЦМД-микро- сборки бездефектен, то соответствующий прямой выход регистра 8 1, а следовательно, элемент И 5 открыт и информация записывается в блок 25 памяти. Если очередной регистр хранения i-ro микросборки дефектен, то элемент И 5 закрыт, в блок 25 памяти записывается неинформационный ноль, а 1 в регистре 1 сдвигается на один разряд вправо В результате в следующем такте через блок элементов И 22 проходит информация второго (слева) разряда регистра 2.

Таким образом, принимаемая от процессора информация разбавляется нулями в тех позициях, которые соответствуют дефектным регистрам хранения ЦМД-микросборок. После того как расширенный поток принят в блок 25

45 памяти (с частотой работы процессора), данные поступгцот на запись в ЩЩ ЗУ, частота работы которого в 10- 15 раз меньше частоты работы процессора.

В режиме считьгоания информации не- обз4одимо принять информацию из ЦМД- микросборок и освободить ее от неинформационных нулей, соответствующих адресам дефектных регистров хранения.

gg Поскольку в общем случае адреса дефектных регистров в различных микросборках не совпадают, то для выравнивания разрядов одного слова необходимо осуществить общую задержку на

40

50

79682

логический О - считывание изЦМДЗУ, .на входы 20 подают сигнал управления: при использовании регистров К155ИР13 первоначально устанавливают режим параллельного занесения информации по первому или второму информационному входам (регистров 1), а затем устанавливают режим сдвига вправо

10 при записи и влево при считывании. На вход 14 подают сигнал начальной установки, по окончании которого счетчик 6 и регистры 2 обнуляются, а в регистры 1 заносится 1.

15 В режиме записи информации в ЦМД ЗУ на вход 17 подают сигнал включения блока 12, а на вход 16 - логическую 1. Поскольку 1 в режиме записи в регистрах 1 записана в пос0

5

ция, принимаемая от процессора в последний (справа) разряд регистров 2, через блок элементов И 22 к элемент ИЛИ 21 поступает на элемент И 5. Ес5 ли регистр хранения i-ro ЦМД-микро- сборки бездефектен, то соответствующий прямой выход регистра 8 1, а следовательно, элемент И 5 открыт и информация записывается в блок 25 памяти. Если очередной регистр хранения i-ro микросборки дефектен, то элемент И 5 закрыт, в блок 25 памяти записывается неинформационный ноль, а 1 в регистре 1 сдвигается на один разряд вправо В результате в следующем такте через блок элементов И 22 проходит информация второго (слева) разряда регистра 2.

Таким образом, принимаемая от процессора информация разбавляется нулями в тех позициях, которые соответствуют дефектным регистрам хранения ЦМД-микросборок. После того как расширенный поток принят в блок 25

5 памяти (с частотой работы процессора), данные поступгцот на запись в ЩЩ ЗУ, частота работы которого в 10- 15 раз меньше частоты работы процессора.

В режиме считьгоания информации не- обз4одимо принять информацию из ЦМД- микросборок и освободить ее от неинформационных нулей, соответствующих адресам дефектных регистров хранения.

g Поскольку в общем случае адреса дефектных регистров в различных микросборках не совпадают, то для выравнивания разрядов одного слова необходимо осуществить общую задержку на

0

0

23 такта. Устройство работает так же как и при записи, за исключением того, что первоначально логическая 1 в регистрах 1 заносится в первый (справа) разряд, а при каждом чтении из дефектного регистра хранения, эта 1 сдвигается влево.

При использовании блока 25 памяти информация первоначально заносится в него, а затем быстро считьтается в процессор.

Формула изобретения

1. Устройство сопряжения процессора с памятью, содержащее первую и вторую группы сдвиговых регистров, первзпо, вторую, третью группы элементов И, счетчик, первый блок памяти, регистр, формирователь импульсов, выход которого соединен с первым входом каждого элемента И первой и второй групп, вход начальной установки каждого сдвигового регистра первой и второй групп соединен с входом начальной установки счетчика и является входом начальной установки устройства, вход формирователя импульсов соединен со счетным входом счетчика и является входом тактовых импульсов устройства, выход каждого элемента И первой группы соединен с синхровхо- дом соответствующего сдвигового регистра первой группы, выход каждого элемента И второй группы соединен с синхровходом соответствующего сдвигового регистра второй группы, выходы элементов И третьей группы являются информационными выходами устройства, а первый вход каждого элемента И третьей группы соединен с выходом соответствующего разряда регистра, информационные входы регистра соединены с

выходами первого блока памяти, адрес- .ющееся тем, что, с целью

ный вход которого соединен с выходом счетчика, отличающееся тем, что, с целью повьшзения достоверности функционирования, оно дополниповышения быстродействия, дополнительно содержит четвертую группу элементов И, вторую группу элементов ИЛИ и второй блок памяти, выхогу

тельно содержит первую группу элемен- Q которого являются информационными

тов ИЛИ, группу блоков элементов И, элемент НЕ, коммутатор, двунаправленный коммутатор, информационные входы- выходы которого являются информационными входами-выходами устройства, первая группа информационных входов коммутатора является информационными входами устройства, вторая группа информационных входов коммутатора сое55

выходами устройства и соединены с и формационными входами двунаправленного коммутатора, адресный вход вто рого блока памяти соединен с выходо счетчика, вход выборки второго блок памяти соединен с входом тактовых и пульсов устройства, вход управления режимом второго блока памяти являет ся вторым входом управления режимом

динена с выходами двунаправленного коммутатора, вход управления режимом которого соединен с управляющим входом коммутатора, входом элемента НЕ, с первым информационным входом каждого сдвигового регистра первой группы и является первым входом управления режимом обмена устройства, стробирующий вход двунаправленного коммутатора является входом разрешения работы устройства, выход элемента НЕ соединен с вторым информационным входом каждого сдвигового регистра первой

группы, каждый выход коммутатора соединен с информационным входом соответствующего сдвигового регистра второй группы, входы управления приемом информации каждого регистра первой группы являются входами управления приемом информации устройства, второй вход каждого элемента И первой группы соединен с инверсным выходом соответствующего разряда регистра,

второй вход каждого элемента И второй группы соединен с прямым выходом соответствующего разряда регистра, синхровход которого соединен с входом тактовых импульсов устройства,

выходы элементов ИЛИ первой группы соединены с вторыми входами соответствующих элементов И третьей группы и с информационными входами двунаправленного коммутатора, вькоды каждого из блоков элементов И соединены с входами соответствующего элемента ИЛИ первой группы, первый вход каждого блока элементов И грзтпы соединен с выходом соответствующего сдвигового регистра первой группы, второй вход каждого блока элементов И группы соединен с выходом соответствующего сдвигового регистра второй группы. 2. Устройство ПОП.1, отли

повышения быстродействия, дополнительно содержит четвертую группу элементов И, вторую группу элементов ИЛИ и второй блок памяти, выхогул

которого являются информационными

выходами устройства и соединены с информационными входами двунаправленного коммутатора, адресный вход второго блока памяти соединен с выходом счетчика, вход выборки второго блока памяти соединен с входом тактовых импульсов устройства, вход управления режимом второго блока памяти является вторым входом управления режимом

обмена устройства, первый выход каждого элемента И четвертой группы соединен с первым входом управления режимом обмена устройства, второй вход каяодого элемента И четвертой группы соединен с выходом соответствующего элемента ИЛИ первой группы, первый вход каждого элемента ИЛИ второй

группы соединен с выходом соответствующего элемента И третьей группы, а второй вход каждого элемента ИЛИ второй группы соединен с выходом соответствующего элемента И четвертой группы, выходы элементов ИЛИ второй группы соединены с информационными входами второго блока памяти.

С| IP

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357966A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1352496A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство для переадресации информации в доменной памяти | 1984 |

|

SU1188788A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

| Устройство для обхода дефектных регистров в доменной памяти (его варианты) | 1985 |

|

SU1305773A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах управления обменом процессора с памятью. Целью изобретения является повьшение достоверности функционирования и быстродействия. Устройство содержит сдвиговые регистры 1, 2 групп, элементы И 3, 4, 5, 23 групп, счетчик 6, блоки 7, 25 памяти, формирователь 9 импульсов, двунаправленный коммутатор 12, коммутатор 10, элемент НЕ 11, элементы ИЛИ 21, 24, групп, группу блоков памяти, блок групп 22 элементов И, регистр 8. Цель изобретения достигается за .счет введения режимов ускоренного считывания информации и обхода неисправных ячеек памяти. 1 з.п. ф-лы, 2 ил. (О (Л

Редактор О.Головач

Составитель М.Силин

Техред Л.Сердюкова Корректор Г.Решетник

6000/50

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Стеклорез | 1984 |

|

SU1248966A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1985-04-29—Подача