Изобретение относится к вычислительной технике, а именно к устройствам для управления обменом информа- 1щей, и может быть использовано при организации обмена информацией между различными блоками вычислительных систем.

Целью изобретения является повьше- ние достоверности функционирования и повышение быстродействия.

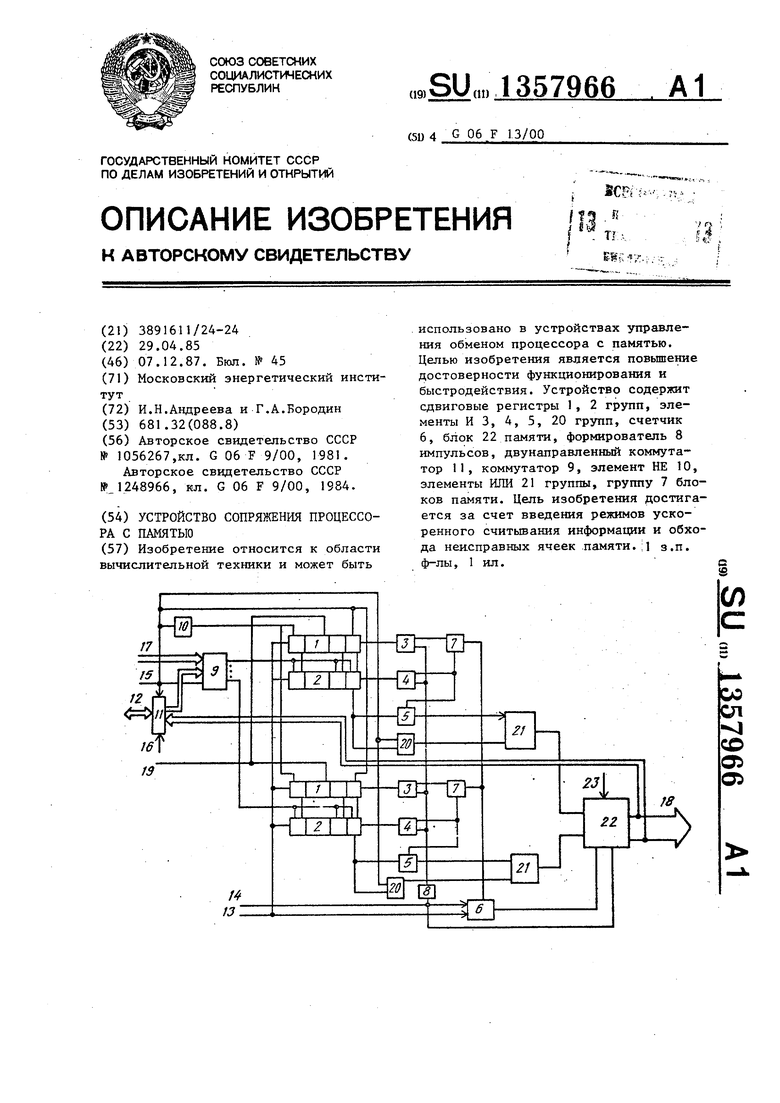

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит сдвиговые регистры первой 1 и второй 2 групп, элементы И первой 3, второй 4, третьей 5 групп, счетчик 6, блоки 7 памяти группы, формирователь 8 импульсов, коммутатор 9, элемент НЕ 10, двунаправленный коммутатор 1, информационные входы-выходы 1 2,, вход 3 начальной установки, вход 14 тактовых импульсов, вход 15 управления режимом обмена, вход 16 разрешения работы, информационные входы 17 и информационные выходы 18, вход 19 управления приемом информации, элементы И 20 четвертой группы, элементы ИЛИ 21 группы, блок 22 памяти и второй вход 23 управления режимом обмена.

Устройство работает следующим образом.

Блоки 7 памяти группы реализованы на ПЛМ (далее ШМ 7) .

Пусть имеется ЗУ на цилиндрических магнитных доменах (ЦМД ЗУ), состоящее более чем из одной микросборки . Каждая микросборка типа К1602РЦ2 имеет 282 регистра хранения, причем 260 из них основные, а 22 резервные, предназначенные для замены основных дефектных регистров. В соответствии с организацией ЦМД ЗУ устройство управления содержит 23-х разрядные регистры 2 группы. Количество регистров в группе определяется количеством параллельно работающих; ЦМД-микро- сборок. Информация о наличии и местоположении дефектов каждой микросборки хранится в блоке 7 памяти, причем каждый разряд блока соответствует одной ЦМД-микросборке, а его содержимое определяет годность 1 или дефектность VO регистров хранения этой микросборки.

В режиме начальных установок на входе 16 устанавливают режим работы:

логическая 1 - запись в ЦМД ЗУ, логический О - считывание из ЦМД ЗУ, на вход 19 подают сигнал параллельного занесения информации в первый (справа).разряд регистра 1 при записи и в последний (справа) разряд регистра 1 при чтении. Кроме того, устанавливают режим сдвига регистра 1

вправо при считыва1ши и влево - при записи. На &-ход 13 подают сигнал начальной установки, по окончании которого счетчик 6 и регистры 2 обнуляются, а в регистры 1 заносится единица.

Б режиме записи информации в ЦМД ЗУ по входу 6 запускается блок 11, а на вход 15 подают логическую 1, что .обеспечивает передачу ин- формации с входов 12 через коммутатор 9 на входы регистров 2 группь. Поскольку логическая 1 записана в перлом (справа) разряде регистров 1, то информация принимается только в первый (справа) разряд регистров 2.

Если регистр хранегшя i-й ЦМД-микро- сборки бездефектёб, то на прямом выходе i-й ПЛМ 1, и информация из первого разряда регистра 2 через элемент И 5 поступает на запись в

блок 22 памяти. По окончании тактового импульса содержимое регистра 2 сдвигается на один разряд вправо. Если регистр хранения i-й ЦМД-микро- сборки дефектен, информация из регистра 2 в блок 22 памяти не поступает (но при этом и него записывается неинформационный ноль), сдвига содержимого регистра 2 не производится. Кроме того, единицей с инверсного выхода i-й ПЛМ осуществляется сдвиг 1 из первого (справа) разряда регистра 1 во второй разряд, слеовательно, информация в следующем такте принимается уже во второй разряд регистра 2.

Таким образом, осуществляется преобразование информации, постзтающей от процессора, в соответствии с картой годности ЦМД-микросборок. В результате формируется поток, разряды которого содержат неинформационные нули в позициях, соответствующих дефектным регистрам хранения.

После того, как информация принята от процессора в блок 22 памяти, она переписывается в ЦМД ЗУ уже астотой его работы, которая в десятки раз меньше частоты работы проессора.

3 ,

В режиме считывания информации необходимо .принять информацию от ЦМД-микросборок и освободить ее от неинформационных нулей. Поскольку в общем случае адреса дефектных регистров хранения в различных микросборках не совпадают, то осуществляется общая задержка на 23 такта для выравнивания разрядов одного слова. При счйтьшании устройство работа

ет так же, как и при записи, только прием информации в регистрах 2 осуществляется с последнего (.справа) разряда, а 1 в регистрах 1 сдвигается слева направо. Если первые 22 регистра хранения в i-й ЦМД-микро- сборке оказываются дефектными, то через 23 такта информация начинает поступать с выхода регистра 2 через элемент И 20 и ИЛИ 21 в блок 22 памяти. Если в микросборке нет ни одного дефектного регистра, то вся информация, принимаемая от ЦМД ЗУ, поступает через последний разряд регистра 2 и, пройдя его, записываться в блок 22 памяти. Поскольку в течение первых 23-х .тактов в этот блок записывались нули, то для сокращения временных потерь перекачку информации в процессор можно начать с 24-го адреса блока 22. Установка, режима в блоке 22 осуществляется по входу 23.

Формул, а изобретения

1. Устройство сопряжения процессора с памятью, содержащее первую и вторую группы сдвиговых регистров.

первую, вторую, третью группы элемен- 40 двунаправленного коммутатора соединетов И, счетчик, формирователь импульсов , выход которого соединен с первым входом каждого элемента И первой и второй групп, вход начальной установки каждого сдвигового регистра первой и второй групп соединен с входом начальной установки счетчика и .является входом начальной установки устройства, вход формирователя импульсов соединен со счетным входом счетчика и является входом тактовых импульсов устройства, выход каждого элемента И первой группы соединен с синхровходом соответствующего сдвигового регистра первой группы, выход каждого элемента И второй группы соединен с синхровходом соответствующего сдвигового регистра второй группы, выход К-го регистра первой группы соединен с вторым информационным входом К-го регистра второй группы, К 1, М, где М - разрядность памяти, выходы элементов И третьей груп

пы являются информационными выходами устройства, а первый вход каждого элемента И третьей группы соединен с выходом соответствующего сдвигового регистра второй группы, отличающееся тем, что, с целью повышения достоверности функционирования, оно дополнительно содержит группы блоков памяти, коммутатор, элемент НЕ, двунаправленный коммутатор, информационные входы-выходы которого являются информационными входами- выходами устройства, первая группа информационных входов коммутатора

является информационными входают устройства, вторая группа информационных входов коммутатора соединена с выходами двунаправленного коммутатора, вход управления режимом которого соединен с управляющим входом коммутатора, входом элемента НЕ, первым информационным входом каждого из сдвигового регистра первой группы и является первым входом управления

режимом обмена устройства, стробирую- щий вход двунаправленного коммутатора является входом разрешения работы устройства, выход элемента НЕ соединен с вторым информационным входом каждого сдвигового регистра первой группы, каждый выход коммутатора соединен с первым информационным входом соответствующего сдвигового регистра второй группы, информационные входы

ны с выходами сдвиговых регистров второй группы, входы управления приемом информации каждого сдвигового регистра первой группы являются входа45 ми управления приемом информации уст- .ройства, второй вход каждого элемента И первой группы соединен с инверсным выходом соответствующего блока памяти группы, втор ые входы каждого

gQ элемента И второй и третьей групп соединены с прямым выходом соответствующего блока памяти группы, адресные входы блоков памяти группьх подключены к выходам счетчика.

55 2. Устройство поп.1,отли- ч ающе е с я тем, что, с целью повышения быстродействия, оно дополнительно содержит четвертую группу элементов И, группу ИЛИ и блок памя5 1357966в

ти, выходы которого являются информа-обмена устройства, второй вход каждо- диoнны и выходами устройства и соеди-го элемента И четвертой группы соединены с информационными входами дву-ней с выходом соответствующего сдви направленного коммутатора, адресныегового регистра второй группы, пер- входы блока памяти соединены с выхо-вый вход каждого элемента ИЛИ группы дами счетчика, вход выборки блокасоединен с выходом соответствующего памяти соединен с входом тактовых им- элемента И третьей группы, а второй пульсов устройства, вход чтения запи-вход каждого элемента ИЛИ группы сое- си блока памяти является вторым вхо-ю .динен с выходом соответствующего эле- дом управления режимом обмена уст-мента И четвертой группы, выход каж- ройства, первый вход каждого из эле-дого элемента ИЛИ группы соединен с ментов И четвертой группы соединенсоответствующим информационным вхо- с первым входом управления режимомдом блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357968A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1352496A1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство для переадресации информации | 1981 |

|

SU1001177A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Устройство для обхода дефектных регистров в доменной памяти (его варианты) | 1985 |

|

SU1305773A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах управления обменом процессора с памятью. Целью изобретения является повьшение достоверности функционирования и быстродействия. Устройство содержит сдвиговые регистры 1, 2 групп, элементы И 3, 4, 5, 20 групп, счетчик 6, блок 22 памяти, формирователь 8 импульсов, двунаправленный коммутатор 1I, коммутатор 9, элемент НЕ 10, элементы ИЛИ 21 группы, группу 7 блоков памяти. Цель изобретения достигается за счет введения режимов ускоренного считывания информации и обхода неисправных ячеек .памяти. :1 з.п. ф-лы, 1 ил. с (Л 00 сд со О5 О5

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР №,1248966, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1985-04-29—Подача