Изобретение относится к вычислительной технике, а именно к запоминающим устройствам на цилиндрических магнитных доменах (ЦМД), и может быть использовано для переадресации информации в микросборках ЦМД, имеющих дефектные регистры.

Целью изобретения является упрощение устройства.

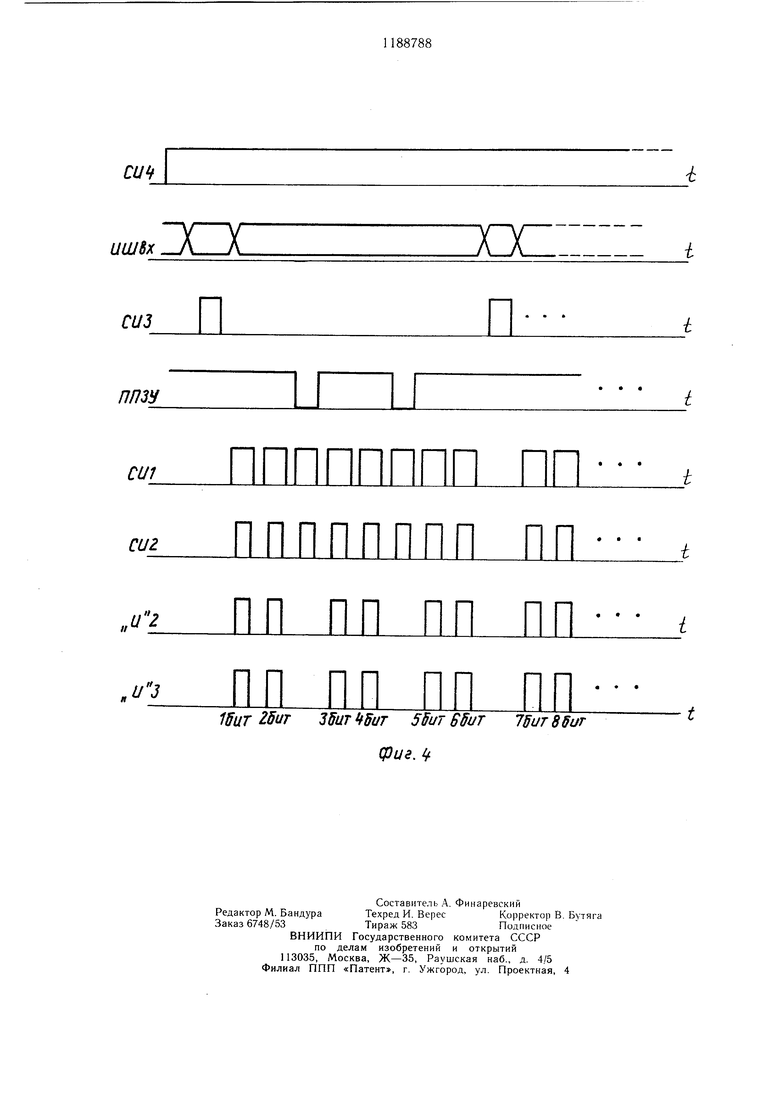

На фиг. 1 показана функциональная схема устройства; на фиг. 2-4 - временные диаграммы работы устройства.

I

Устройство для переадресации информации содер(:ит блок полупостоянной памяти (БПП) 1 с «картой годности. Выход БПП 1 подключен к первому входу схемы И 2 и к первому входу схемы И 3. Строб-вход БПП 1 подключен к первой управляющей шине 4. Выход схемы И 2 подключен к строб-входу БОП 5 (блок оперативной памяти). Выход схемы И 3 подключен к информационному входу БОП 5. Вход режима работы БОП 5 подключен к четвертой управляющей шине 6. Выход БОП 5 подключен к информационному входу младшего разряда регистра 7. Информационные входы регистра 7 подключены к первой информационной шине 8. Вход параллельной записи информации в регистр 7 подключен к третьей управляющей шине 9, а вход для синхроимпульсов сдвига информации в регистре 7 подключен ко второй управляющей шине 10 и ко второму входу схемы И 2. Выход старшего разряда регистра 7 подключен ко второму входу схемы И 3. Информационные выходы регистра 7 подключены ко второй информационной шине 11. Сигнал «Си 4 поступает по шине . 6 на вход БОП 5 и определяет режим работы БОП 5. Сигнал «Си 1 поступает по шине 4 на стробвход БПП 1. Сигнал «Си 2 по шине 10 поступает на вход схемы И 2 и на вход сдвига информации в регистре 7. Сигнал «Си 3 по шине 9 поступает на вход параллельной записи информации в регистр 7.

При использовании микросборок ЦМД со структурами регистр ввода-вывода /регистры хранения или регистр ввода/регистры хранения/регистр вывода возникает проблема обхода дефектных регистров хранения. Необходимо переадресовать информацию при записи, чтобы она не записывалась в дефектные регистры хранения. При чтении необходимо отделять информацию, считанную из дефектных регистров хранения, от истинной информации, считанной из годных регистров хранения. Переадресация информации производится по «карте годности, размещенной в постоянной или оперативной памяти.

Обход дефектных регистров усложняется при параллельной работе нескольких микросборок ЦМД. Это связано с тем, что-распределение дефектных регистров в микросборках ЦМД разное.

Устройство работает следующим образом. По входной информационной шине 8 поступает из устройства управления для записи в микросборки ЦМД страница информации, представляющая собой массив вида (mXn), где m - количество информационных слов; п - разрядность информационного слова. Предположим, что

0 и равно количеству параллельно работающих микросборок ЦМД.

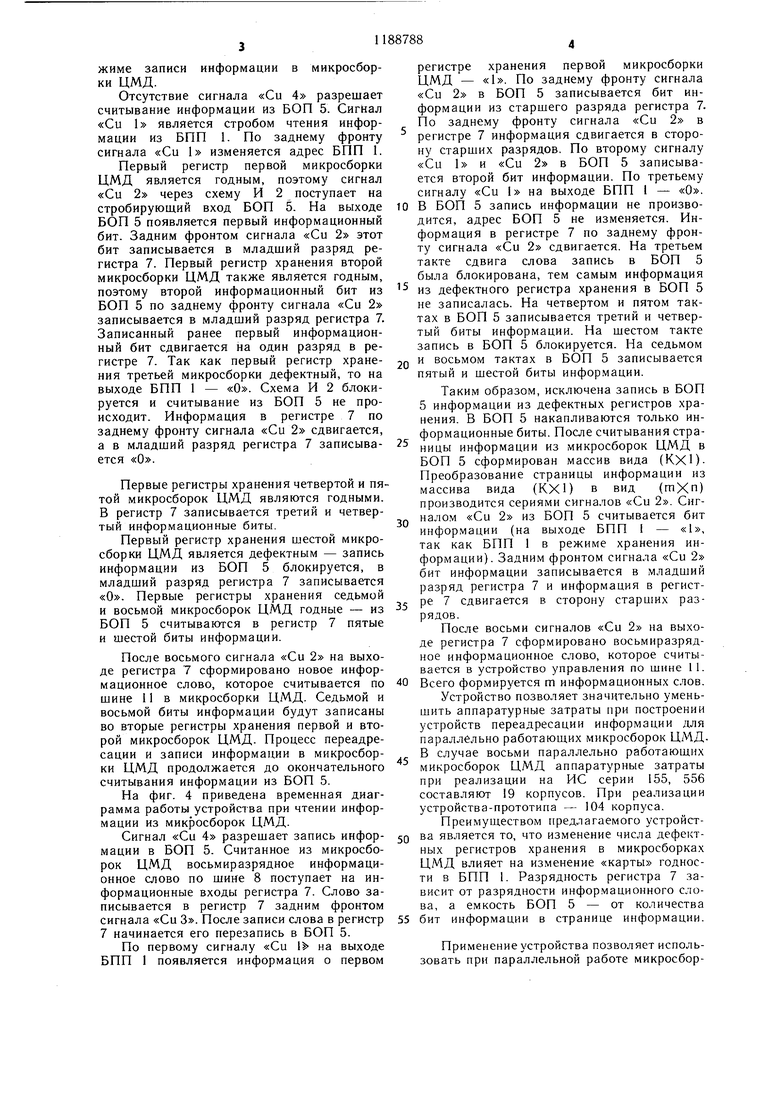

На фиг. 2 приведена временная диаграмма записи страницы информации в БОП 5. Информационное слово, поступающее по шине 8, параллельно записывается в регистр

7. Запись производится по заднему фронту сигнала «Си 3. Затем в регистре 7 производится сдвиг информации в сторону старших разрядов. Сдвиг происходит по заднему фронту сигнала «Си 2. Так как БПП 1

0 находится в режиме хранения информации, то на его выходе присутствует «1. Сигнал «Си 2 проходит через схему И 2. Сигнал с выхода схемы И 2 своим передним фронтом записывает в БОП 5 информацию с выхода схемы И 3, а задним

5 фронтом изменяет адрес в БОП 5. Восемь сигналов «Си 2 производят перезапись всего информационного слова из регистра 7 в БОП 5.

Сигналом «Си 3 в регистр 7 произвоQ дится запись следующего информационного слова. Процесс перезаписи информации из регистра 7 в БОП 5 повторяется.

Таким образом, страница информации преобразуется в массив вида (КХ1), где К,т- п.

После записи страницы информации в БОП 5 начинается переадресация информации и запись ее в микросборки ЦМД. Переадресация производится в соответствии с «картой годности, хранящейся в БПП 1.

0 «Карта годности представляет собой массив информации вида (ЕХ) где Е- количество регистров хранения во всех микросборках ЦМД. «1 на выходе БПП 1 соответствует годному регистру хранения, «О - дефектному регистру хранения.

Первый бит «карты годности соответствует первому регистру хранения первой микросборки и,МД, восьмой бит «карты годности - первому регистру хранения восьмой микросборки ЦМД, девятый бит

0 «карты годности - второму регистру первой микросборки и т. д., т. е. первые восемь разрядов «карты годности соответствуют первым регистрам хранения параллельно работающих микросборок ЦМД, а i-e восемь разрядов карты годности соответствуют i-м регистрам хранения микросборок ЦМД.

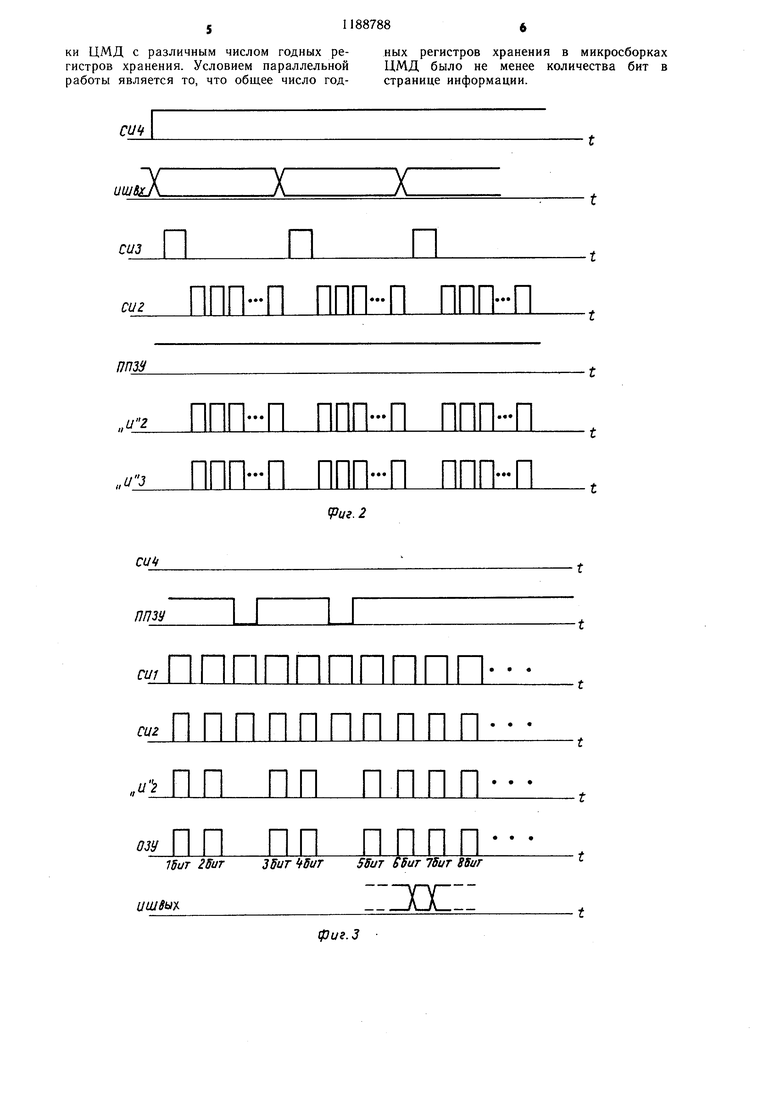

На фиг. 3 приведена временная диаграмма переадресации информации в режиме записи информации в микросборки ЦМД.

Отсутствие сигнала «Си 4 разрешает считывание информации из БОП 5. Сигнал «Си 1 является стробом чтения информации из БПП 1. По заднему фронту сигнала «Си 1 изменяется адрес БПП 1.

Первый регистр первой микросборки ЦМД является годным, поэтому сигнал «Си 2 через схему И 2 поступает на стробирующий вход БОП 5. На выходе БОП 5 появляется первый информационный бит. Задним фронтом сигнала «Си 2 этот бит записывается в младший разряд регистра 7. Первый регистр хранения второй микросборки ЦМД также является годным, поэтому второй информационный бит из БОП 5 по заднему фронту сигнала «Си 2 записывается в младший разряд регистра 7. Записанный ранее первый информационный бит сдвигается на один разряд в регистре 7. Так как первый регистр хранения третьей микросборки дефектный, то на выходе БПП 1 - «О. Схема И 2 блокируется и считывание из БОП 5 не происходит. Информация в регистре 7 по заднему фронту сигнала «Си 2 сдвигается, а в младший разряд регистра 7 записывается «О.

Первые регистры хранения четвертой и пятой микросборок ЦМД являются годными. В регистр 7 записывается третий и четвертый информационные биты.

Первый регистр хранения шестой микросборки ЦМД является дефектным - запись информации из БОП 5 блокируется, в младший разряд регистра 7 записывается «О. Первые регистры хранения седьмой и восьмой микросборок ЦМД годные - из БОП 5 считываются в регистр 7 пятые и шестой биты информации.

После восьмого сигнала «Си 2 на выходе регистра 7 сформировано новое информационное слово, которое считывается по шине 11 в микросборки ЦМД. Седьмой и восьмой биты информации будут записаны во вторые регистры хранения первой и второй микросборок ЦМД. Процесс переадресации и записи информации в микросборки ЦМД продолжается до окончательного считывания информации из БОП 5.

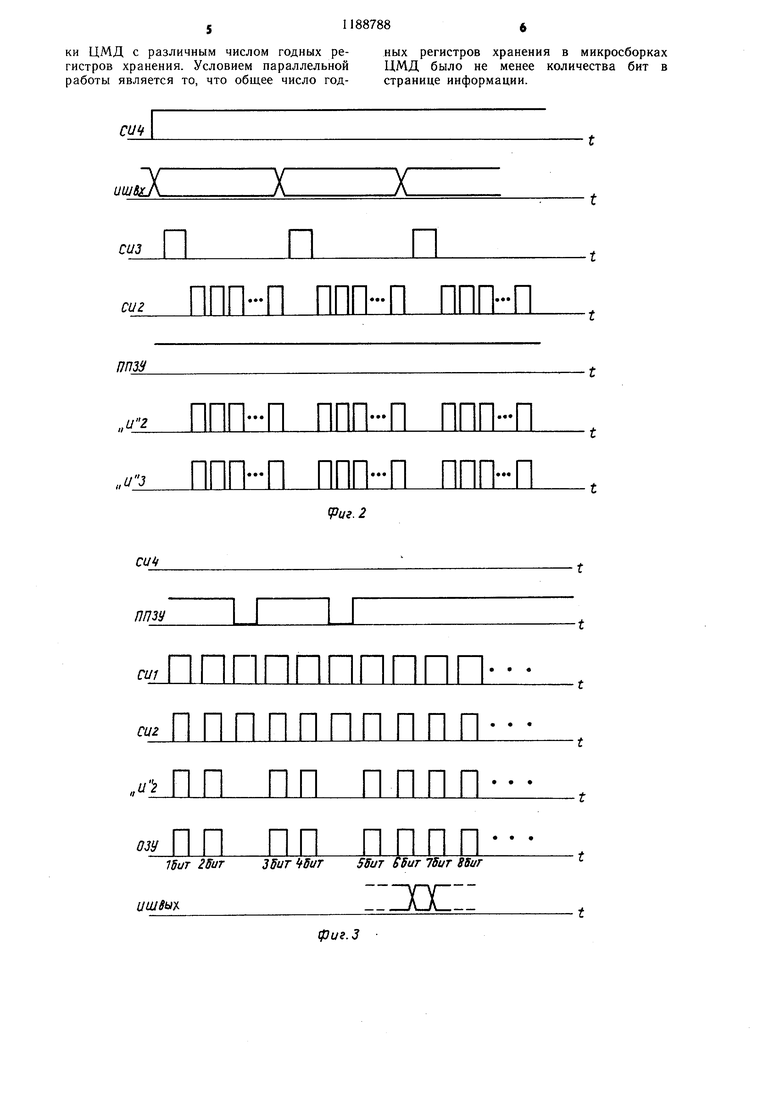

На фиг. 4 приведена временная диаграмма работы устройства при чтении информации из микросборок ЦМД.

Сигнал «Си 4 разрешает запись информации в БОП 5. Считанное из микросборок ЦМД восьмиразрядное информационное слово по шине 8 поступает на информационные входы регистра 7. Слово записывается в регистр 7 задним фронтом сигнала «Си 3. После записи слова в регистр 7 начинается его перезапись в БОП 5.

По первому сигналу «Си 11 на выходе БПП 1 появляется информация о первом

регистре хранения первой микросборки ЦМД - «1. По заднему фронту сигнала «Си 2 в БОП 5 записывается бит информации из старшего разряда регистра 7. По заднему фронту сигнала «Си 2 в регистре 7 информация сдвигается в сторону старших разрядов. По второму сигналу «Си 1 и «Си 2 в БОП 5 записывается второй бит информации. По третьему сигналу «Си I на выходе БПП I - «О.

0 В БОП 5 запись информации не производится, адрес БОП 5 не изменяется. Информация в регистре 7 по заднему фронту сигнала «Си 2 сдвигается. На третьем такте сдвига слова запись в БОП 5 была блокирована, тем самым информация

из дефектного регистра хранения в БОП 5 не записалась. На четвертом и пятом тактах в БОП 5 записывается третий и четвертый биты информации. На шестом такте запись в БОП 5 блокируется. На седьмом

Q и восьмом тактах в БОП 5 записывается пятый и шестой биты информации.

Таким образом, исключена запись в БОП 5 информации из дефектных регистров хранения. В БОП 5 накапливаются только информационные биты. После считывания страницы информации из микросборок ЦМД в БОП 5 сформирован массив вида (КХ1). Преобразование страницы информации из массива вида (КХ1) в вид (тХ) производится сериями сигналов «Си 2. Сигналом «Си 2 из БОП 5 считывается бит

0 информации (на выходе БПП 1 - «1, так как БПП 1 в режиме хранения информации). Задним фронтом сигнала «Си 2 бит информации записывается в младший разряд регистра 7 и информация в регист,5 ре 7 сдвигается в сторону старших разрядов.

После восьми сигналов «Си 2 на выходе регистра 7 сформировано восьмиразрядное информационное слово, которое считывается Б устройство управления по шине 11.

Всего формируется m информационных слов. Устройство позволяет значительно уменьшить аппаратурные затраты при построении устройств переадресации информации для параллельно работаюших микросборок ЦМД. В случае восьми параллельно работаюших микросборок ЦМД аппаратурные затраты при реализации на ИС серии 155, 556 составляют 19 корпусов. При реализации устройства-прототипа - 104 корпуса.

Преимушеством предлагаемого устройства является то, что изменение числа дефектных регистров хранения в микросборках ЦМД влияет на изменение «карты годности в БПП 1. Разрядность регистра 7 зависит от разрядности информационного слова, а емкость БОП 5 - от количества

бит информации в странице информации.

Применение устройства позволяет использовать при параллельной работе микросбор51188788«

ки ЦМД с различным числом годных ре- ных регистров хранения в микросборках гистров хранения. Условием параллельной ЦМД было не менее количества бит в работы является то, что общее число год-странице информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1352496A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357966A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство для переадресации информации | 1981 |

|

SU1001177A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357968A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

УСТРОЙСТВО ДЛЯ ПЕРЕАДРЕСАЦИИ ИНФОРМАЦИИ В ДОМЕННОЙ ПАМЯТИ, содержащее блок полупостоянной памяти и регистр сдвига, информационные входы которого являются информационными входами устройства, а информационные выходы регистра сдвига являются информационными выходами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит блок оперативной памяти и два элемента И, Фиг.-/ первый вход блока оперативной памяти является третьим управляющим входом устройства, а выход подключен к информационному входу регистра сдвига, второй вход блока оперативной памяти подключен к выходу первого элемента И, а третий вход блока оперативной памяти подключен к выходу второго элемента И, первый вход которого подключен к первому входу первого элемента И и к выходу блока полупостоянной памяти, второй вход второго элемента И подключен к информацинному выходу регистра сдвига, а второй вход первого элемента И подключен к первому управляющему входу регистра сдвига, который является первым управляющим входом устройства, второй управляющий вход регистра сдвига является вторым управляющим входом устройства, а вход блока полупостоянной памяти является четвертым управляющим входом устройства.

г.. ПППППППППП ПП ПППП

ПП ПППП

Збит fSuT SSur SSuT 7SuT 8Ш

фиг.З

8Sur

пг

си

-ь

иШ8х

тСХ

сиз

/7/7Jy

ппп

пппппппп пп пп пп If иг 2биг

п--пп пп пп 35ит hduT 5SuT BSuT 75ит 85иг пп пп i Cpus.

| Радиоэлектроника- за рубежом, 1983, № 20, с | |||

| Насос | 1917 |

|

SU13A1 |

| Устройство для переадресации информации | 1981 |

|

SU1001177A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-30—Публикация

1984-06-28—Подача