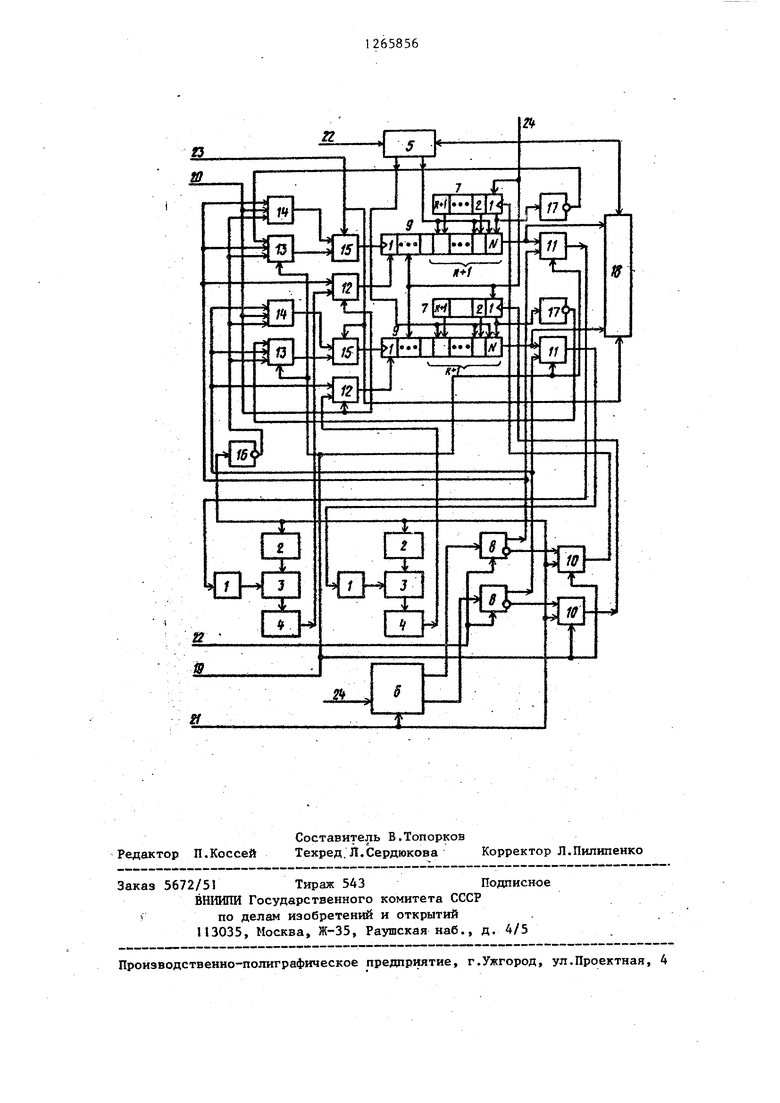

Изобретение относится к вычислительной технике,в частности к устройствам управления для памяти, и мо жет быть использовано в запоминающих устройствах на цилиндрических магнит ных доменах (ЦМД) для обхода дефект ных и избыточньк информационных регистров при параллельной работе нескольких накопителей с НМД при записи и считывании данных. Целью изобретения является повышение быстродействия устройства путем сокращения времени формирозания .слова в выходном регистре числа при совмещении работы нескольких накопителей с фЩ с различным расположением дефектных регистров. На чертеже представлена функциональная схема устройства управления для доменной памяти, Устройство управления для доменной памяти содержит формирователи 1 записи и формирователи 2 вращающегося магнитного поля, выходы которых подключаются ко входам микросборок 3 с ЦМД, выходы которых соединены с входами усилителей 4 считывания, входной регистр 5 числа, блок 6 полупостоянной памяти, регистры 7 позиционного кода, триггеры 8, регист ры 9 числа, первую группу элементов И 0, вторую группу элементов И П, третью группу элементов И 12, четвертую группу элементов И 13, пятую группу элементов И 14, группу элементов ИЛИ 15, элемент НЕ 16, группу элементов НЕ 17, выходной регист 18 числа, Показаны также кодовая шина 19 Запись, кодовая шина 20 Считывание, кодовая шина 21 такта, кодова шина 22 Прием, кодовая шина 23 Выдача, .кодовая шина 24 установки О. Показаны также (1,2,...5k+l)pa3 ряды регистров 7 позиционного кода, где k - число маскируемых дефектных и избыточных регистров в каждом из накопителей 3 с 1ЩД, причем (1) младший, (k+1)-старший разряды; (1,..,,N)-разряды регистров 9 числа где (1) - младший, (N) - старший ра ряды, причем количество используемых регистров в каждом из накопителей с ЦМД равно (N-1). Устройство работает следующим образом. Осуществляется прием М-разрядного числа во входной регистр 5 числа из других функциональных блоков ЭВМ при наличии разрешающего потенциала на кодовой шине 22 Прием, запись числа в микросборки 3 с ЦМД, считывание М-разрядных чисел из накопителя и выдача их в выходной регистр 18 числа при наличии разрешающего потенциала на кодовой шине 23 Вьщача, из регистра 18 число может поступать в другие функциональные блоки ЭВМ. На кодовую щину 2 такта поступают синхроимпульсы с частотой продвиженияЦМД в накопителе (частотой вращающегося магнитного поля). При установке разрешающего потенциала (логической I) на кодовой шине 24 установки О обнуляются входной регистр 5 и выходной регистр 18 числа, регистры 9 числа, заносятся 1 в младшие разряды регистров 7 позиционного кода, обеспечивается считывание информации из блока 6 полупостоянной памяти с начального адреса. Информационная емкость блока 6 памяти составляет Mx(N-l+k) бит. При считьшании логической 1 из блока 6 памяти по соответствующему выходу соответствующий регистр соответствующей микросборки воспринимается как годный (не маскируется), и в данную позицию осуществляется запись или информация о данной позиции воспринимается при считывании из накопителя с ЦМД. При считывании логического О из блока 6 памяти по соответствуйщему выходу соответствующий регистр накопителя с ЦМД маскируется: при записи информация сюда же заносится j при считывании из накопителя не воспринимается (не заносит.ся в регистры 9 числа) . Количество разрядов (k+) регистров 7 позиционного кода на 1 больше числа маскируемых регистров накопителя. Количество разрядов N регист- ров 9 числа на 1 больше числа используемых регистров в каждом из накопителей с ЦМД, поскольку сдвиг содержимого регистров 9 осуществляется в промежутках между подачей синхроимпульсов на кодовую шину 21 такта как при записи, таки при считывании данных из микросборок 3 с ЦМД. При записи информации в накопители с ЦМД на кодовой шине 19 Запись устанавливается.разрешающий потенциал уровень 1j . На кодовых шина 20 Считьтание и 23 Выдача - - запрещающий потенциал /уровень О). В режиме записи в каждом такте рабо ты устройства перед поступлением синхроимпульса на кодовую шину 21 -. такта на кодовой шине 22 Прием ус танавливается разрешающий потенциал и осуществляется занесение М-разрядного слова во входной регистр 5 числа, а триггеры 8 обнуляются. Первое М-разрядное слово в режиме записи заносится из регистра 5 в старшие разряды (N) регистров 9 числа, посколькулогическая 1 находит ся в младших (l разрядах регистров 7 позиционного кода. С приходом синх роимпульса на -кодовую шину 21 такта из блока 6 полупостоянной памяти считывается М-разрядное слово. Логические 1 в его разрядах переводят соответствующие триггеры 8 в единичное состояние, если же считан логический О, то соответствующий триггер 8 остается в нулевом состоянии. Если соответствующий триггер 8 находится в единичном состоянии, то информация из старших разрядов регистров 9 числа через элементы И 11 поступает на входы соответствующих формирователей 1 записи. Если соот- ветствующий триггер 8 остался в нулевом состоянии, то информация из старших разрядов соответствующих регистров 9 числа не передается, на входах соответствующих формирователей 1 записи - запрещающий потенциал . Если в первом такте из блбка 6 памяти считывается 1, то при наличии разрешающего потенциала на кодозой шине 21 такта на выходе соответствующего элемента И 10 присутствует запрещающий потенциал, и сдви га 1 из разряда (l) соответствующего регистра 7 позиционного кода не происходит. При этом на выходе соответствующего элемента НЕ 17 уровень О и на вход управления сдвигом регистра 9 числа с выхода соответствующего элемента ИЛИ 15 импульс сдвига не поступает, сдвиг содержимого не происходит, В следующем такте информация будет заноситься также в разряд (N) соответствующего регистра 9. Если Б первом такте из блока 6 памяти считьгоается О, то при нали564чии разрешающего потенциала на кодовой шине 21 такта на выходе соответствующего элемента И IО появляется разрешающий потенциал и происходит сдвиг 1 из разряда (1) соответствующего регистра 7 позиционного кода в разряд (2). Таким образом, в следующем такте информация будет заноситься в разряд (N-1) соответствующего регистра 9 числа. .Несмотря на то, что Г теперь находится в разряде (5) .регистра 7 и на выходе соответствующего элемента НЕ 17 уровень 1, после окончания синхроимпульса из-за того, что соответствующий триггер 8 находится внулевом состоянии, на выходах соответствующего элемента И 13 и элемента ИЛИ 15 присутствуют запрещающие потенциалы, и сдвига содержимого соответствующего регистра 9 не происходит. Таким образом, в режиме записи информация вьщается на входы формирователей 1 записи с выходов старших разрядов регистров 9, если в соответствующих разрядах слова, считываемого из блока 6 памяти, присутствуют 1. При наличии О осуществляется задержка записи в соответств-ующую микросборку 3 с ЩЗД до считывания 1 в соответствующем разряде слова из блока 6 памяти. Пусть во втором такте из блока 6 памяти считано слово с 1 в том разряде, в котором в первом такте бьш О. Тогда после окончания записи (и окончания синх-, роимпульса на кодовой шине 21 такта) соответствующий триггер 8 остается ДОследующего такта и приема нового М-разрядного числа в единичном состоянии, на выходах элементов НЕ 16, 17 и соответс твующего элемента И 13 появляется разрешающий потенциал и происходит сдвиг содержимого соответствующего регистра 9 числа наодин разряд в сторону старшего разряда так, что к началу третьего такта бит, подлежащий записи, находится в старшем разряде (N) регистра 9 числа. Таким образом, если регистр микросборки с ЦМД маскируется, то в следующем такте соответствующий бит М-разрядного слова из регистра 5 заносится в разряд регистра 9, .номер которого на единицу меньше предьщущего. Если в предыдущем такте в соответствующем разряде слова из блока 6 памяти была 1, то к началу следующего такта производится сдвиг содержимого регистра 9 числа на один разряд в сторону старшего разряда в случае, если в младшем разряде соответт ств.ующего регистра позиционного кода отсутствует 1. В регистрах 7 позиционным способом кодируется количество маскируемых регистров микросборок. После окончания записи подается разрешающий потенциал на кодовую шину 24 установки О.

При считьюании информации из накопителей с 1ЩД на кодовой шине 20 Считывание устанавливается разре- шающий потенциал. На кодовых шинах 19 Запись и 23 Выдача - запрещающий потенциал. В каждом такте работы устройства перед поступлением синхроимпульса на кодовую шину 21 такта на кодовой шине 22 Прием устанавливается разрешающий потенциал, обнуляющий триггер 8, однако занесение М-разрядного числа в регистр 5 не происходит.

Считанная из микросборок с ЦМД информация с выходов усилителей 4 считьюания через элементы И 12 заносится в младшие разряды (1) регистров 9 числа в случае наличия I в соответствующих разрядах слова, считанного из блока 6 полупостоянной памяти. Если в предыдущем такте соот ветствующий триггер 8 переведен вединичное состояние, то после занесения бита в младший разряд соответствующего регистра 9 и окончания cинxpoи fflyльca на кодовой шине 21 такта на выходах соответствующих элементов И 14 и HJIIi 15 появляется разрешающий потенциал и осуществляется сдвиг содержимого регистра 9 на один разряд в сторону старшего разряда. При наличии О в соответствующем разряде слова, считанного из блока 6 памяти, занесения информации в младший разряд регистра 9 и сдвига его содержимого не происходят.

В режиме вьщачи числа в выходной регистр 18 числа на кодовых шинах 19 Запись, 20 Считывание, 21 такта, 22 Прием присутствуют запрещающие потенциалы, на кодовую шину 23 Вьщача подаются разрешающие импульсы. При этом обеспечивается занесение слова из старших разрядов регистров 9 числа в выходной регистр 18 числа, откуда число может поступать в другие функциональные блоки ЭВМ, и сдвиг содержимого регистров 9 всторону старшего разряда за счет прохождения разрешающих импульсов на . выходы элементов ИЛИ 15.

Таким образом, использование изобретения позволяет повысить быстродействие устройства за счет сокращения времени формирования слова в выходном регистре числа при синхронных запуске и останове формирователей вращающегося магнитного поля и маскировании одинакового количества регистров во всех параллельно работающих микросборках с ЦМД. При этом в каждой из параллельно работающих микросборок с ЦМД хранятся одноименные разряды всех слов.

Формула изобретения

Устройство управления для доменной памяти, содержащее блок полупостоянной памяти, первый и второй входы которого соединены соответственно с кодовыми шинами такта и установки О, формирователи записи и формирователи вращающегося магнитного поля, выходы которых являются выходами устройства, усилители считывания, входы которьпс являются входами устройства, триггеры, первые входы которых соединены с соответствующими выходами блока полупостоянной памяти, первую, вторую и третью группы элементов И, причем первые входы элементов И первой группы соединены с кодовой шиной такта, первые входы элементов И второй группы подключены к кодовой шине Запись, вторые йходы - к единичным выходам соответствующих триггеров и первым входам элементов И третьей группы, а В| 1ходы - к входам формирователей записи, вторые входы элементов И третьей группы связаны с выходами соответствующих усилителей счьтьшания, а третьи входы - с. кодовой шиной Считывание, о т л ичающееся тем, что, с целью повышения быстродействия устройства, OHQ содержит регистры позиционного кода, входной регистр числа, регистры числа, четвертую и пятую группы элементов И, группу элементов ИШ, элемент НЕ, группу элементов НЕ и

выходной регистр числа, причем вход элемента НЕ соединен с входами формирователей вращающегося магнитного поля и подключен к кодовой шине такта, выход элемента НЕ соединен с первыми входами элементов И четвертой и пятой .групп., выходы которых соединены с первыми и вторыми входами соответствующих элементов ИЛИ, третьи входы которых связаны с входом разрешения приема выходного регистра числа и подключены к кодовой шине Выдача, а выходы элементов ИЛИ соединены с входами управления сдвигом регистров числа, информационные входы младших разрядов которых подключены к выходам элементов И третьей группы, а вход установки О соединен с информационными входами младших разрядов регистров позиционного кода входами установки в О входного и выходного регистров числа и подклю чей к кодовой щине установки О, выходы регистров позиционного кода соединены с информационными входами соответствующих разрядов регистров числа, входы разрешения приема которых связаны с соответствующими выходами входного регистра числа, вход разрешения приема которого подключен к шине Прием, выходы старших разрядов регистров числа соединены с соответствующими входами выходного регистра числа и третьими входами элементов И второй группы, выходы младших разрядов регистров пози ционного кода подключены к входам элементов НЕ группы, выходы которых связаны с вторыми входами соответствующих элементов И четвертой группы, третьи входь которых соединены с вторыми входами соответствующих элементов И пятой группы и подключены к. единичным выходам триггеров, нулевые выходы которых соединены с вторыми входами .элементов И первой группы, а вторые входы, являющиеся входами ус тановки О - с кодовой шиной Прием J четвертые входы элементов И четвертой группы соединены с третьими входами элементов И первой группы и

подключены к кодовой шине Запись, выходы элементов И первой группы связаны с входами управления сдвигом регистров позиционного кода, третьи входы элементов И пятой группы соединены с кодовой шиной Считы,вание.

гэ

2ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство для переадресации информации в доменной памяти | 1984 |

|

SU1188788A1 |

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления для памяти, и может быть использовано в запоминающих устройствах на цилиндрических магнитных доменах (ЦМД) для обхода дефектных и .избыточных информационных регистров при параллельной работе нескольких накопителей с ЦМД при записи и считьшании данных. Целью изобретения является повышение быстродействия устройства путем coicpa-. щения времени формирования слова в выходном регистре числа при совмещении работы нескольких накопителей с ЦМД с различным расположением дефектных регистров. Устройство содержит формирователи записи и формирователи вращающегося магнитного поля, выходами подключаемые к входам микросборок с ЦМД, выходы которых соединены с входами усилителей считьшания, входной регистр числа, блок полупостоянной памяти, регистры позиционного кода, триггеры, регистры числа, группы элементов И, группу элементов ИЛИ, элемент НЕ, группу элементов НЕ, выходной регистр числа. Изобретения позволяет повысить быстродействие устройства за счет сокращения времени формирования слова .1аИВ ЕГ %гаа в выходном регистре числа при синхронных запуске и останове формирователей вращающегося магнитного поля и маскировании одинакового количества регистров во всех параллельно работающих микросборках с ЦМД. При этом Ю в каждой из параллельно работающих Од микросборок с ЦМД хранятся одноимен01 ные разряды всех слов. 1 ил. СХ) СП 0

| Патент США 4225941, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-10-23—Публикация

1984-07-20—Подача