(З) СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронный музыкальный звонок | 1988 |

|

SU1748176A1 |

| Устройство электронного синтеза мелодии для часов | 1987 |

|

SU1499309A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Десятичный счетчик | 1973 |

|

SU660272A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для ввода информации | 1985 |

|

SU1267401A1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| Селектор импульсов заданной кодовой комбинации | 1987 |

|

SU1457169A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

1

Изобретение относится к вычислительной технике и автоматике и может быть использовано для счета импульсов.

Известен счетчик, содержащий в каждом разряде первый и второй триггеры памяти на элементах И-ИЛИ-НЕ с соответствующими связями П

Наиболее близким к предлагаемому по технической сущности является счетчик, содержащий в каждом разряде двоично-троичный триггер и коммутационный триггер, причем тактовые входы обоих триггеров соединены с вхо.дом счетчика, при этом выход каждого разряда соединен с входом последующего разряда, а в каждом из разрядов выходы двоично-троичного триггера соединены с соответствующими входами коммутационного триггера, выходы которого соединены с соответствующими информационными входами двоичнотроичного триггера ; л .

Недостатком известных счетчиков является низкая информационная емкость.

Цель изобретения - повышение информационной емкости счетчика.

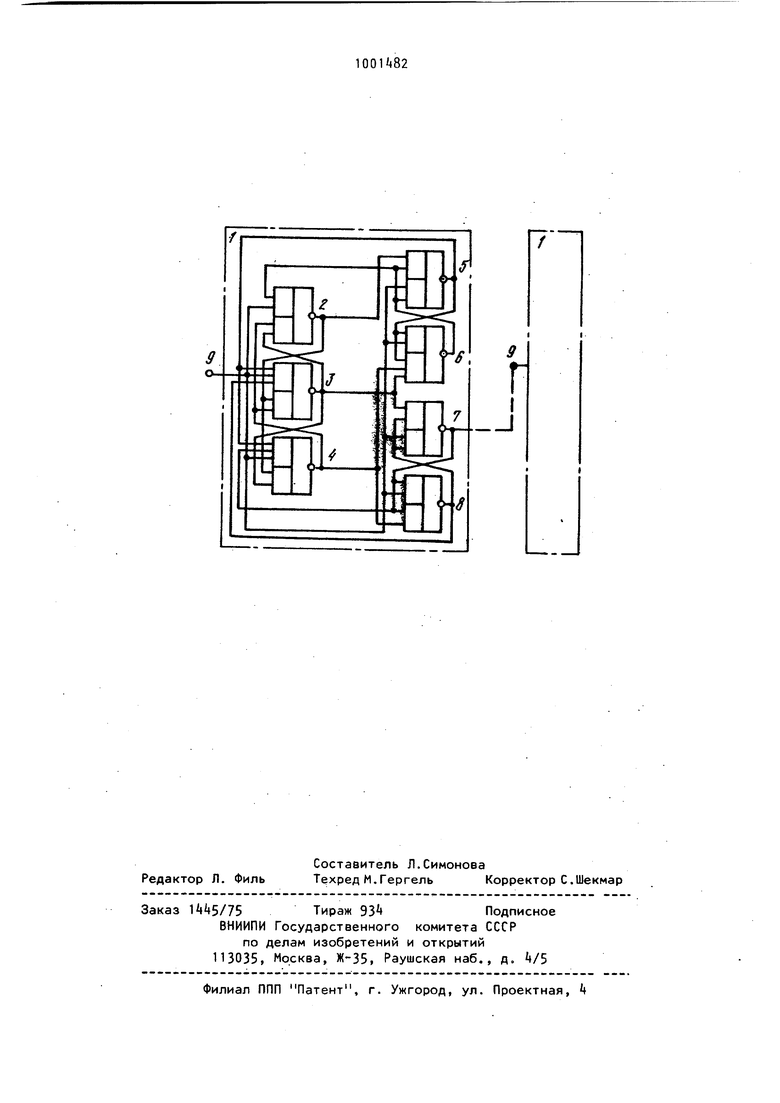

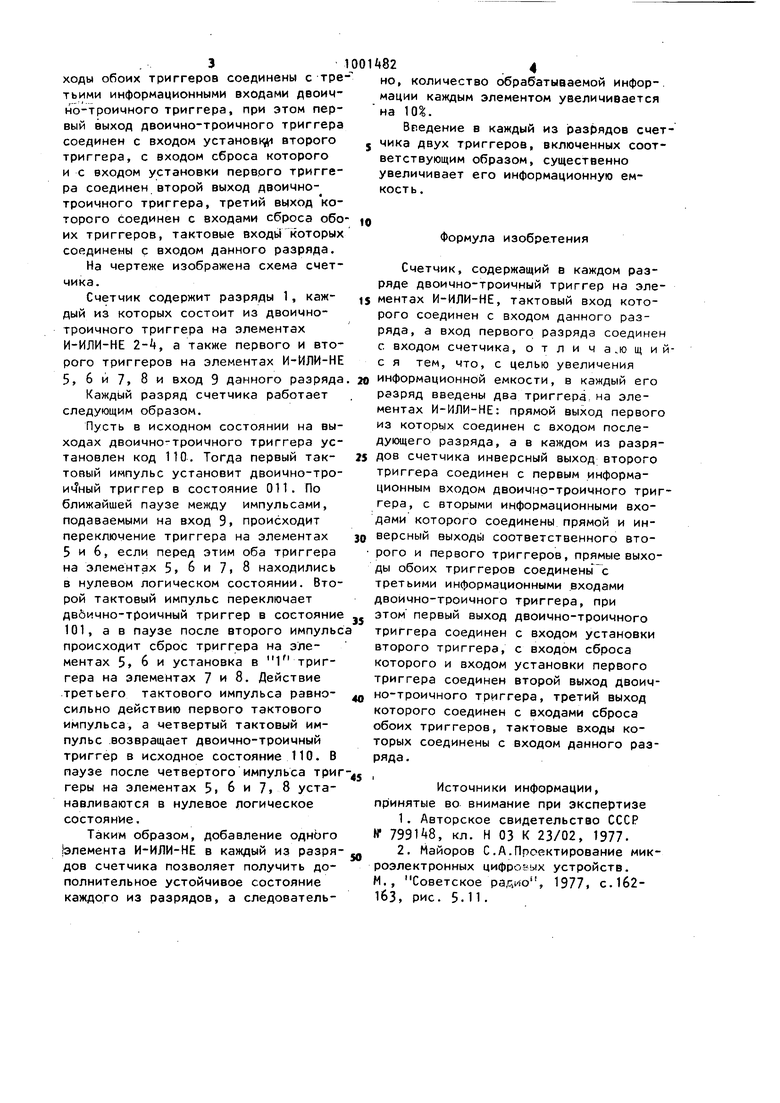

Поставленная цель достигается . тем, что в счетчик, содержащий в каждом, разряде двоично-троичный триг-гер на элементах ИгИЛИ-НЕ, тактовый вход которого соединен с входом данного разряда, а вход первого разряда соединен с входом счетчика, в каждый его разряд введены два триггера на элементах И-ИЛИ-НЕ, прямой выход первого из которых соединен с входом последукяцего разряда, а в каждом из разрядов счетчика инверсный выход второго триггера соединен с первым информационным входом двоично-троичного триггера, с вторыми информационными входами которого соединены прямой и инверсный выходы соответственно второго и первого триггеров, прямые выходы обоих триггеров соединены с тре тьими информационными входами двоично-троичного триггера, при этом первый выход двоично-троичного триггера соединен с входом установн; 1 второго триггера, с входом сброса которого и с входом установки первого триггера соединен второй выход двоичнотроичного триггера, третий выход которого соединен с входами сброса обо их триггеров, тактовые входы которых соединены с входом данного разряда. На чертеже изображена схема счетчика. Счетчик содержит разряды 1, каждый из которых состоит из двоичнотроичного триггера на элементах И-ИЛИ-НЕ 2-4, а также первого и второго триггеров на элементах И-ИЛИ-НЕ 5, 6 и 7, 8 и вход 9 данного разряда Каждый разряд счетчика работает следующим образом. Пусть а исходном состоянии на выходах двоично-троичного триггера установлен код 110. Тогда первый тактовый импульс установит двоично-трои4ный триггер в состояние 011. По ближайшей паузе между импульсами, подаваемыми на вход 9 происходит переключение триггера на элементах 5 и 6, если перед этим оба триггера на элементах 5 6 и 7. 8 находились в нулевом логическом состоянии. Второй тактовый импульс переключает двоично-Троичный триггер в состояни 101, а в паузе после второго импуль происходит сброс триггера на элементах 5 6 и установка в 1 триггера на элементах 7 и 8. Действие третьего тактового импульса равносильно действию первого тактового импульса, а четвертый тактовый импульс возвращает двоично-троичный триггер в исходное состояние 110. В паузе после четвертого импульса три геры на элементах 5i 6 и 7f 8 устанавливаются в нулевое логическое состояние. Таким образом, добавление одного элемента И-ИЛИ-НЕ в каждый из разря дов счетчика позволяет получить дополнительное устойчивое состояние каждого из разрядов, а следовательно, количество обрабатываемой информации каждым элементом увеличивается на 10. Вг.едение в каждый из разрядов счетчика двух триггеров, включенных соответствующим образом, существенно увеличивает его информационную емкость. Формула изобретения Счетчик, содержащий в каждом разряде двоично-троичный триггер на элементах И-ИЛИ-НЕ, тактовый вход которого соединен с входом данного разряда, а вход первого разряда соединен с входом счетчика, отлича.ющийс я тем, что, с целью увеличения информационной емкости, в каждый его разряд введены два триггера, на элементах И-ИЛИ-НЕ: прямой выход первого из которых соединен с входом последующего разряда, а в каждом из разрядов счетчика инверсный выход второго триггера соединен с первым информационным входом двоично-троичного триггера, с вторыми информационными входами которого соединены прямой и инверсный выходи соответственного второго и первого триггеров, прямые выходы обоих триггеров соединены с третьими информационными входами двоично-троичного триггера, при этом первый выход двоично-троичного Триггера соединен с входом установки второго триггера, с входом сброса которого и входом установки первого триггера соединен второй выход двоично-троичного триггера, третий выход которого соединен с входами сброса обоих триггеров, тактовые входы которых соединены с входом данного разряда . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Vf , кл. И 03 К 23/02, 1977. 2.Майоров С.А.Проектирование микроэлектронных цифровых устройств. М., Советское , 1977, с.1б21бЗ, рис. 5.11.

«7

u шI

Авторы

Даты

1983-02-28—Публикация

1981-05-07—Подача