Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на микросхемах динамической памяти.

Известно устройство управления динамической памятью (Микропроцессорные средства и системы, 1986, № 3, с 75), содержащее генератор импульсов регенерации, вход тактовых импульсов, двоичный счетчик адреса регенерации, мультиплексор адреса, дешифратор синхросигналов столбца, блок приема и арбитража .апросов на обращение в память и регенерацию памяти

Недостатком данного устройства является его невысокое быстродействие, связан- ное с выделением времени для

восстановления заряда в ячейках памяти после каждого обращения в память или обработки запроса на регенерацию

Наиболее близким к изобретению является устройство управления динамической памятью (Микропроцессорные средства и системы, 1989, № 1, с. 7), содержащее генератор импульсов регенерации, вход тактовых импульсов, блок приоритетного обслуживания, триггер готовности, инвертор, элемент ЗИ, триггер цикла, регистр тактов, двоичный счетчик, триггер разрядов адреса элемент ЗИ-НЕ первый элемент 2И- НЕ блок управления записью, мультиплексор адрес дешифратор синхросигналов столбца,

vj

00

00

ел с

ю

Недостатком этого устройства является его невысокое быстродействие при считывании информации Это связано с тем, что при обращении к любому банку памяти (группе выбираемых одновременно микросхем) синхросигнал строки РА подается на микросхемы всех банков памяти Поэтому следующее (или регенерация) допустимо только после паузы, необходимой для восстановления заряда в ячейках памяти строки матрицы ячеек памяти микросхем, к которой было обращение. Время восстановления заряда, например, для микросхем К565РУ5, К565РУ7 составляет до 40-50% от времени цикла обращения. Кроме того, при выполнении операции записи ответный сигнал окончания операции формируется устройством лишь после окончания синхросигналов строки и столбца, хотя в соответствии с техническими характеристиками для большинства микросхем динамической памяти, в том числе отечественной серии К565, подача входных данных, адреса и сигнала записи может быть прекращена вскоре после подачи переднего фронта синхросигнала столбца CAS. Поэтому известное устройство обладает низким быстродействием также при выполнении операции записи информации Предлагаемое устройство устраняет отмеченные недостатки.

Целью изобретения является повышение быстродействия устройства.

Указанная цель достигается гем, что устройство для управления динамической памятью, содержащее генератор импульсов регенерации, генератор тактовых импуль сов, блок приоритетного обслуживания, триггер готовности, инвертор, элемент ЗИ, триггер цикла, регистр тактов, двоичный счетчик, триггер разрядов адреса, элемент ЗИ-НЕ, первый элемент 2И-НЕ, блок управления записью, мультиплексор адреса, дешифратор синхросигналов столбца, причем выход генератора импульсов регенерации подключен к входу запроса регенерации блока приема и арбитража запросов, прямой выход генератора тактовых импульсов подключен к входу прямых тактовых импульсов блока приоритетного обслуживания, первому входу элемента ЗИ и синхровходу триггера разрядов адреса, инверсный выход генератора тактовых импульсов подключен к входу инверсных тактовых импульсов блока приоритетного обслуживания и синхропходу peincrpa тактов, выход тактового сигнала адреса регенерацииблока приоритетного обслуживания и синхровходу регистра тактов, РЫХОД тактового сигнала адреса реге

нерации блока приоритетного обслуживания подключен к счетному входу двоичного счетчика, выход сигнала регенерации блока подключен к входу инвертора, первому входу элемента ЗИ-НЕ и входу сигнала регенерации блока управления записью, выход сигнала занятости блока соединен с вторым входом элемента ЗИ, выход сигнала установки блока подключен к входу установки

триггера готовности, вход запроса обращения к памяти блока объединен с входом сброса триггера готовности и является входом сигнала запроса обращения к памяти устройства, выход триггера готовности яв5 ляется выходом сигнала готовности устройства, выход элемента ЗИ подключен к синхровходу триггера цикла, на информационный вход которого подан уровень логической единицы, выход триггера цикла

0 подключен к входу первого разряда регистра тактов, прямые выходы первого, второго и третьего разрядов регистра тактов подключены соответственно к входам второго, третьего и четвертого разрядов регистра

5 тактов, прямой выход первого разряда регистра тактов соединен с вторым входом элемента ЗИ-НЕ, первым входом первого элемента 2И-НЕ, информационным входом триггера разрядов адреса и первым такто0 вым входом блока управления записью, прямой выход второго разряда регистра тактов подключен к третьему входу элемента ЗИНЕ, выход которого соединен с входом рад- решения работы дешифратора

5 синхросигналов столбца, а также является выходом строба записи в регистр считывания устройства, прямой выход четвертого разряда регистра тактов соединен с вторым входом первого элемента 2И-НЕ, выход ко0 торого подключен к входу сброса триггера цикла, выходы дешифратора синхросигнй лов столбца являются выходами синхросигналов столбца устройства, второй тактовый вход блока управления записью подключен

5

0

5

к инверсному выходу третьего разряда реги стра тактов, первый и второй выходы блока управления записью являются соответственно выходами управления записью и младший и старший байты памяти, выход инвертора подключен к первому управляю щему входу мультиплексора адреса, второй управляющий вход которого соединен с вы ходом триггера разрядов адреса, первый информационный вход мультиплексора ад реса является входом адресных разрядор столбца устройства, второй информацией ный вход мультиплексора адреса является входом адресных разрядов строки устройст ва третий и четвертый информационны входы мультиплексора обьединрщ

и подключены к входу двоичного счетчика, выход мультиплексора адреса является выходом мультиплексированного адреса устройства, дополнительно содержит регистр состояния, блок анализа состояния, дешифратор синхроси налов строки, второй элемент 2И-НЕ, первый, второй, третий и четвертый элементы 2И, причем первый, второй и третий информационные входы регистра состояния являются соответственно первым, вторым и третьим разрядами адреса памяти устройства, четвертый и пятый информационные входы регистра состояния являются соответственно входом сигнала записи и входом сигнала записи байта устройства, шестой информационный вход регистра состояния соединен с выходом инвертора, выход первого, пятого и четвертого разрядов регистра состояния соответственно с входами младшего разряда адреса, сигнала записи байта и сигнала записи блока управления записью, выходы второго, третьего, четвертого и шестого разрядов регистра состояния подключены соответственно к первому и второму входам хранимого адреса, входу сигнала записи и первому входу сигнала регенерации блока анализа состояния, первый и второй входы следующего адреса блока анализа состояния являются соответственно вторым и третьим разрядами адреса памяти устройства, первый, второй и третий тактовые входы блока анализа состояния подключены соответственно к прямым выходам первого и второго разрядов и инверсному выходу второго разряда регистра тактов, второй вход сигнала регенерации блока анализа состояния подключен к выходу инвертора, вход синхросигнала строки подключен к инверсному выходу первого разряда регистра тактов, вход сброса блока анализа состояния подключен к выходу первого элемента 2И-НЕ. выход разрешения цикла блока анализа состояния соединен с третьим входом элемента ЗИ. а выход сброса блока анализа состояния соединен с входом сброса блока приоритетного обслуживания, первый вход второго элемента 2И-НЕ подключен к выходу инвертора, его второй вход соединен с прямым выходом первого разряда регистра тактов, первый информационный вход дешифратора синхросигналов строки объединен с первым информационном входом дешифратора синхросигналов столбца и подключен к выходу второго разряда регистра состояния, второй информационный вход дешифратора синхросигналов строки объединен с вторым информационным входом дешифратора синлросш мччов столбца и подключен к ВЫУОДУ ipft.,r-.r (мзрчда регистра состояния, вход разрешения оабогы дешифратора синхросигналов строки подключен к инверсному выходу мгрвого разрч 5 да регистра тактов, первый, второй, третий и четвертый выходы дешифратора синхросигнала строки подключены к первым входам соответственно первого, второго, третьего и четвертого элементов 2И, выходы

0 которых являются выходами синхросигналов строки устройства, первые ВУОДЫ первого, второго, третьего и четвертого элементов 2И объединены и подключены к выходу второго элемента 2И-НЕ.

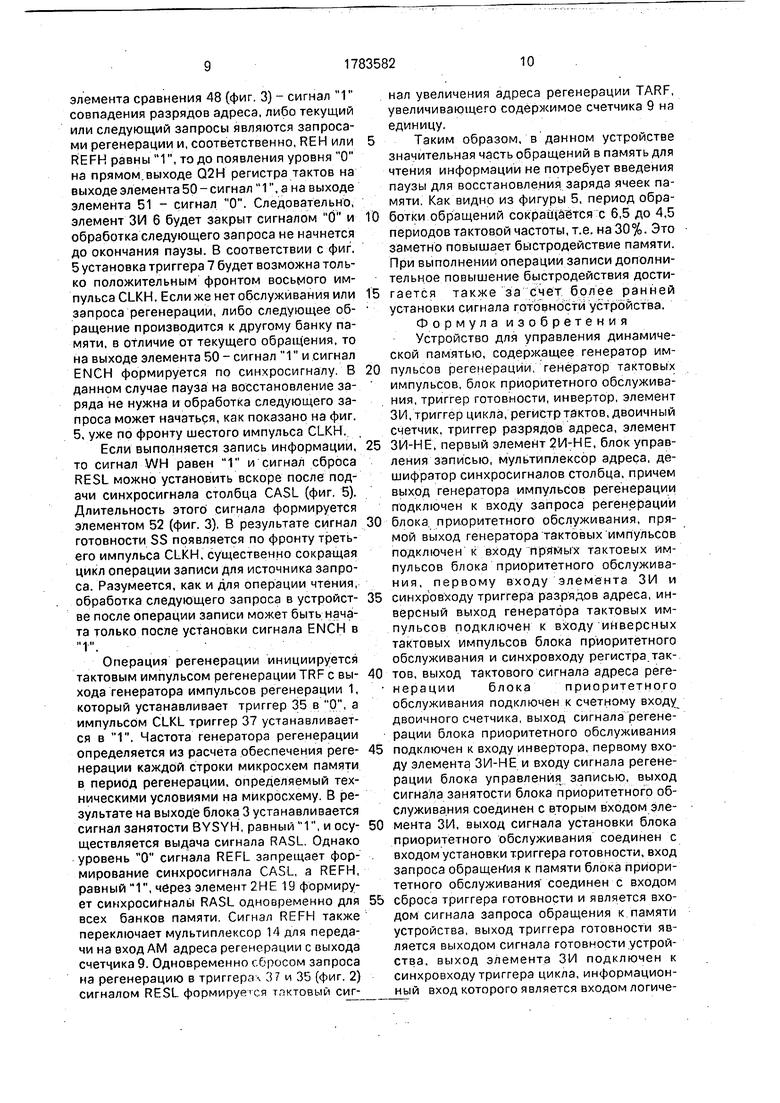

5На фиг. 1 приведена функциональная

схема устройства для управления динамической памятью, на фиг. 2 - схема блока приоритетного обслуживания; на фиг. 3 - схема блока анализа состояния; на фиг. 4 - схема

0 блока управления записью: на фиг. 5 - временные диаграммы сигналов предлагаемого устройства.

Показанный на фиг. 1 пример выполнения устройства дан для случая управления

5 динамической памятью, имеющей четыре банка памяти и осуществляющей чтение двухбайтовых слоев и запись одно- и двухбайтовых слов Для управления памятью с большим числом банков памяти и записью

0 большого числа байтов необходимо соответственно увеличить число разрядов регистра состояния для хранения адресных разрядов и сигналов управления байтами и увеличить число входов и выходов дешифра5 торов синхросигналов строки и столбца, а также внести соответствующие изменения в блок управления записью и блок анализа состояния.

Устройство управления динамической

0 памятью (фиг. 1) содержит генератор им- пульсов регенерации 1, генератор тактовых импульсов 2, блок приоритетного обслуживания 3, триггер готовности 4, инвертор 5, элемент ЗИ 6, триггер цикла 7, регистр так5 тов 8, двоичный счетчик 9, триггер разрядов адреса 10, элемент ЗИ-НЕ 11. первый элемент 2И-НЕ 12, блок управления записью 13, мультиплексор адреса 14, дешифратор синхросигналов столбца 15, регистр состоя0 НИР 16, блок анализа состояния 17, дешифратор синхросигналов строки 18, второй элемент 2И-НЕ 19, первый 20, второй 21, третий 22 и четвертый 23 элементы 2И. Адрес обращения к памяти ADR посту5 пает на вход 24 устройства. Сигналы записи WRH и записи байта BYTEH поступают на входы 25 и 26 устройства. Сигнал злпроса обращения MS подается на вход 27 устройства, а сигнал готовности памяти SS выдается на выходе 28 устройства В динамическую память из устрой тнг, поступэют следующие сигналы: записи в младший WEOL и старший WE1L байт с выходов 29 и 30 соответственно, мультиплексированного адреса AM с выхода 31, синхросигнал строки с одного из выходов 32, синхросигнал столбца с одного из выходов 33, строб записи в регистр считывания SDR с выхода 34.

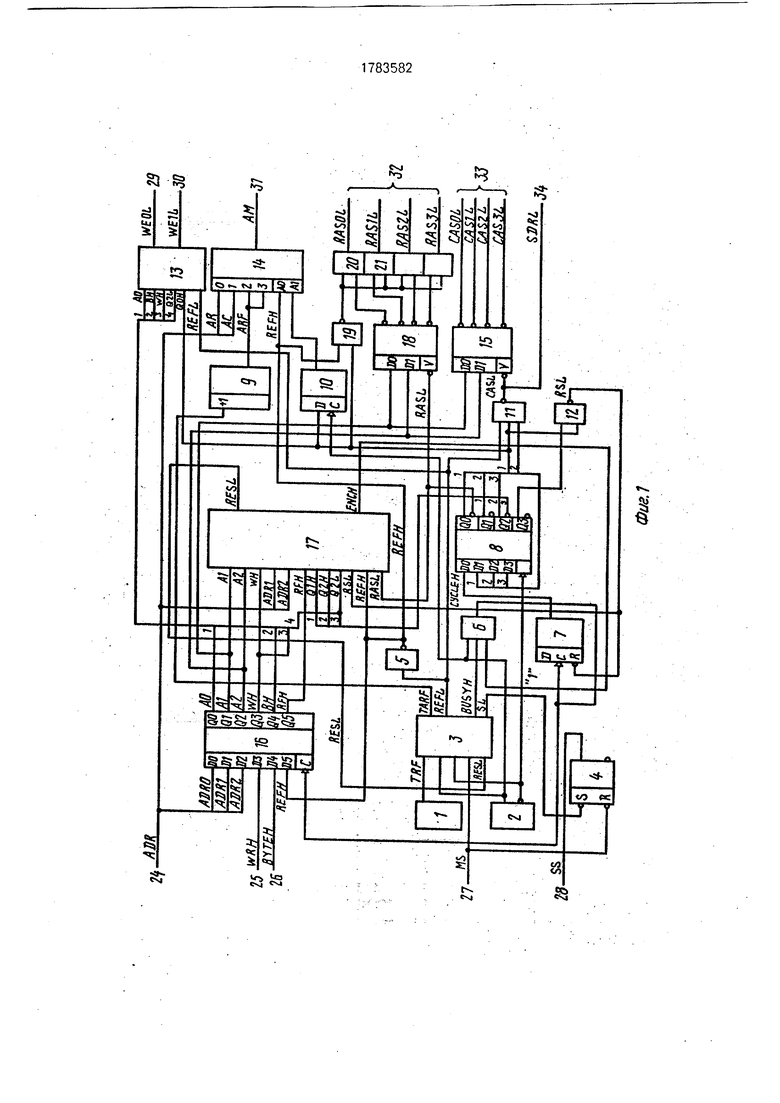

Блок приоритетного обслуживания 3 (фиг. 2) содержит D-триггеры 35-38, элементы 2И-НЕ 39-45, инвертор 46 и элемент 2И 47.

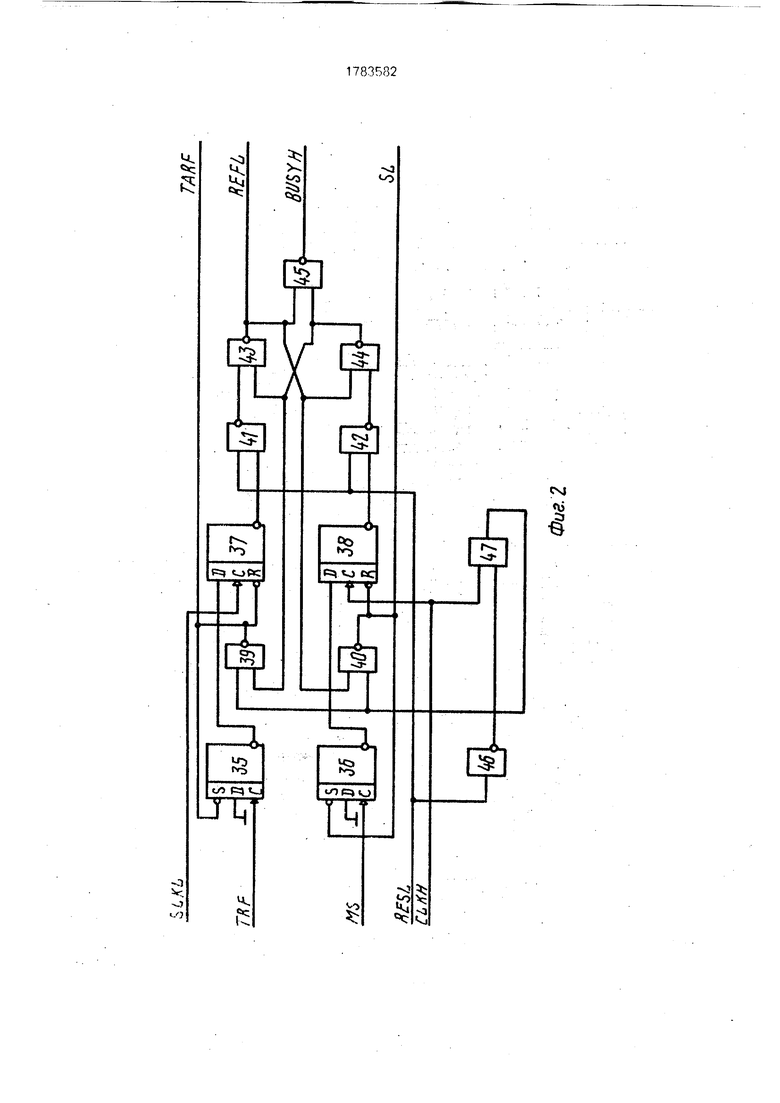

Блок анализа состояния 17 (фиг. 3) содержит элемент сравнения 48, элемент ЗИЛИ 49, элемент 2И-НЕ 50, элементы 21/1 51 и 52, инверторы 53 и 54, элемент 2И- 2ИЛИ-НЕ55.

Блок управления записью 13 (фиг. 4) содержит инвертор 56, элементы 2И-НЕ 57 и 58, элемент ЗИ 59, элементы 2И-НЕ 60 и 61.

Устройство для управления динамической памятью может находиться в трех режимах: ожидания, обработки запроса и паузы.

В режиме ожидания все управляющие элементы устройства находятся в исходном (пассивном) состоянии: триггер цикла 7 сброшен в О, по крайней мере первые два разряда регистра 8 установлены в О, триггер готовности 4 сброшен в О, в блоке приоритетного обслуживания 3 триггеры 35 и 36 установлены в 1, а триггеры 37 и 38 сброшены в О. В динамическую память из устройства управляющие сигналы не подаются.

В режиме обработки запроса осуществляется управление выполнением операциями чтения, записи или регенерации.

Обращение в память (чтение или запись) инициируется переходом сигнала запроса обращения MS на высокий уровень.

Запрос на обращение устанавливает триггер 36 в О. Очередной положительный фронт тактового импульса CLKH записывает 1 в триггер 38. В результате триггер на элементах 2И-НЕ 43 и 44 (фиг 2) устанавливается в состояние обращения в память, при котором сигнал регенерации REFL равен 1 и сигнал занятости BYSYH также равен 1. В результате очередной тактовый сигнал CLKH через элемент ЗИ 6 устанавливает триггер цикла 7 в 1. Мультиплексор адреса 14 пропускает на выход AM разряды строки адреса памяти, которые поступают в память на адресные входы микросхем.

Кроме того, сигнал с выхода элемента ЗИ 6 фиксирует в регистре состояния 16: младшие разряды адреса ADRO-ADR2, сигнал WRH, записи байта BYTEH и тип обращения сигнал REFH, равный в данном

случае О. Через полтакта импульс запишет 1 в первый разряд регистра тактов 8, которая будет с каждым тактом CLKL продвигаться к старшим разрядам. Сигнал с инверсного выхода первого разряда используется для формирования синхросигнала строки RASL, а сигнал с выхода второго разряда определяет начало синхросигнала

0 столбца CAS. При этом выбор одного из четырех банков памяти определяется разрядами А1 и А2 адреса памяти, хранимыми в регистре 16. После записи 1 в первый разряд регистра 8 следующий импульс CLKH

5 установите триггер 10, в результате чего мультиплексор 14 начинает передавать на выход мультиплексированного адреса AM разряды столбца адреса памяти.

При установке в 1 четвертого разряда

0 регистра тактов 8 сигнал сброса RSL с выхода элемента 2И-НЕ 12 сбрасывает триггер цикла 7 в О, а очередной импульс CLKL записывает О в первый разряд регистра тактов 8, что вызывает окончание синхро5 сигналов RASL и CASL.

При выполнении записи байта сигналы WRH и BYTEH равны 1. Зафиксированные в регистре состояния 16, эти сигналы WH и ВН поступают в блок управления записью

0 13 (фиг. 4). Если младший разряд адреса АО равен О, то сигнал записи низкого уровня появляется на выходе записи младшего байта WEOL, а если АО равен 1, - то на выходе записи старшего байта WE1L Если же вы5 полняется запись слова, т.е. ВН равен О, то сигнал 1 с обоих выходов элементов 57 и 58 формирует сигнал разрешения записи для обоих байтов. Начало и окончание сигнала записи WEL определяется сигналами

0 ООН и 02L с прямого первого и инверсного третьего разрядов регистра тактов 8. При выполнении регенерации сигнал REFL равен О и формирование WEL запрещено. При выполнении операции чтения сиг5 нал WH равен О и сигнал сброса RSL в блоке анализа состояния 17 (фиг. 3) через инвертор 54 и элемент 55 поступает на выход блока в виде сигнала RESL и через инвертор 46 (фиг. 2) и элемент И 47 при

0 поступлении импульса CLKH сбрасывает триггер 36 в 1, сбрасывая обслуженный запрос на обращение в память. Одновременно сигнал установки SL устанавливает триггер готовности 4 в 1, информируя сиг5 налом готовности SS источник запроса о готовности считанной информации. Одновременно в блоке анализа состояния 17 анализируется выполняемая текущая и следующая запрашиваемая операция. Если следующий запрос происходит в том же банке памяти, что и текущий, т.е на выходе

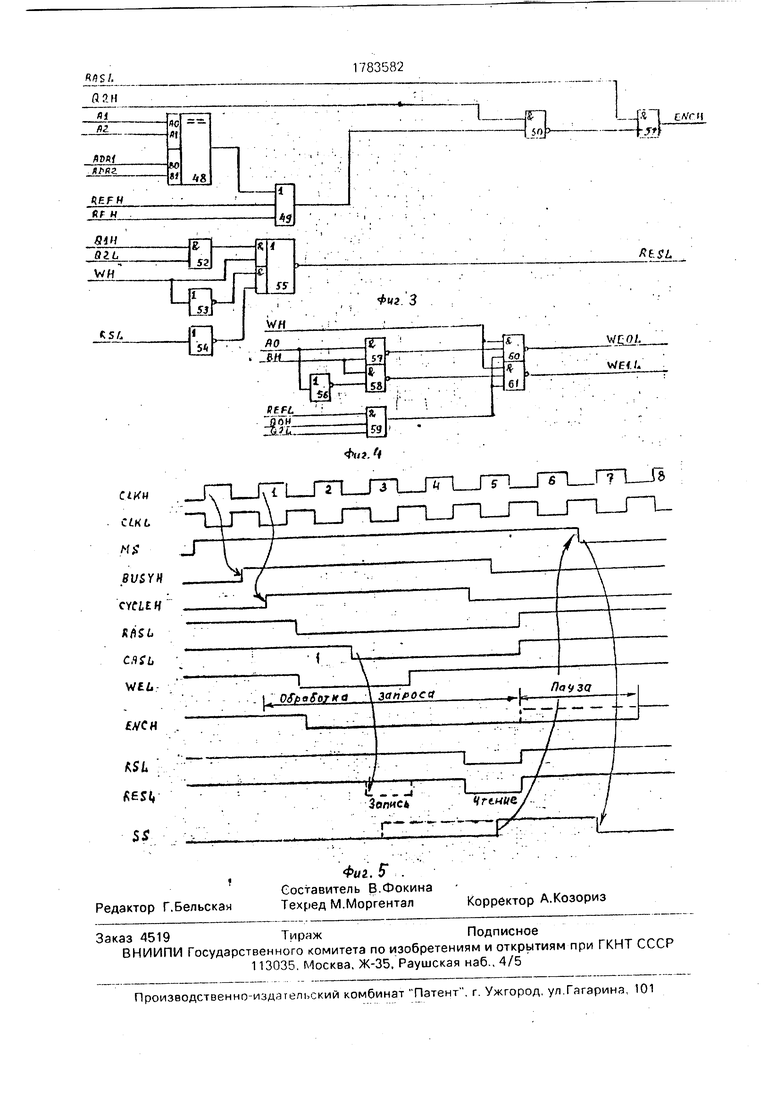

элемента сравнения 48 (фиг. 3) - сигнал 1 совпадения разрядов адреса, либо текущий или следующий запросы являются запросами регенерации и, соответственно, REH или REFH равны 1, то до появления уровня О на прямом выходе Q2H регистра тактов на выходе элемента 50 - сигнал 1, а на выходе элемента 51 - сигнал О. Следовательно, элемент ЗИ 6 будет закрыт сигналом О и обработка следующего запроса не начнется до окончания паузы. В соответствии с фиг. 5 установка триггера 7 будет возможна только положительным фронтом восьмого импульса CLKH. Если же нет обслуживания или запроса регенерации, либо следующее обращение производится к другому банку памяти, в отличие от текущего обращения, то на выходе элемента 50 - сигнал 1 и сигнал ENCH формируется по синхросигналу В данном случае пауза на восстановление заряда не нужна и обработка следующего запроса может начаться, как показано на фиг. 5, уже по фронту шестого импульса CLKH.

Если выполняется запись информации, то сигнал WH равен 1 и сигнал сброса RESL можно установить вскоре после подачи синхросигнала столбца CASL (фиг. 5). Длительность этого сигнала формируется элементом 52 (фиг. 3). В результате сигнал готовности SS появляется по фронту третьего импульса CLKH, существенно сокращая цикл операции записи для источника запроса. Разумеется, как и для операции чтения, обработка следующего запроса в устройстве после операции записи может быть начата только после установки сигнала ENCH в 1.

Операция регенерации инициируется тактовым импульсом регенерации TRF с выхода генератора импульсов регенерации 1, который устанавливает триггер 35 в О, а импульсом CLKL триггер 37 устанавливается в 1. Частота генератора регенерации определяется из расчета обеспечения регенерации каждой строки микросхем памяти в период регенерации, определяемый техническими условиями на микросхему. В результате на выходе блока 3 устанавливается сигнал занятости BYSYH, равный 1, и осуществляется выдача сигнала RASL Однако уровень О сигнала REFL запрещает формирование синхросигнала CASL, a REFH, равный 1, через элемент 2НЕ 19 формирует синхросигналы RASL одновременно для всех банков памяти Сигнал REFH также переключает мультиплексор 14 для передачи на входАМ адреса регенерации с выхода счетчика 9. Одновременно сбросом запроса на регенерацию в триггера 37 и 35 (фиг. 2) сигналом RESL формируется ТРКТОВЫЙ сигнал увеличения адреса регенерации TARF, увеличивающего содержимое счетчика 9 на единицу.

5Таким образом, в данном устройстве

значительная часть обращений в память для чтения информации не потребует введения паузы для восстановления заряда ячеек памяти. Как видно из фигуры 5, период обра- 0 ботки обращений сокращается с 6,5 до 4,5 периодов тактовой частоты, т.е. на 30%. Это заметно повышает быстродействие памяти. При выполнении операции записи дополнительное повышение быстродействия дости5 гается также за счет более ранней установки сигнала готовности устройства. Формула изобретения Устройство для управления динамической памятью, содержащее генератор им0 пульсов регенерации генератор тактовых импульсов, блок приоритетного обслуживания, триггер готовности, инвертор, элемент 31/1, триггер цикла, регистр тактов, двоичный счетчик, триггер разрядов адреса, элемент

5 ЗИ-НЕ, первый элемент 2I/I-HE, блок управления записью, мультиплексор адреса, дешифратор синхросигналов столбца, причем выход генератора импульсов регенерации подключен к входу запроса регенерации

0 блока приоритетного обслуживания, прямой выход генератора тактовых импульсов подключен к входу прямых тактовых импульсов блока приоритетного обслуживания, первому входу элемента ЗИ и

5 синхровходу триггера разрядов адреса, инверсный выход генератора тактовых импульсов подключен к входу инверсных тактовых импульсов блока приоритетного обслуживания и синхровходу регистра так0 тов, выход тактового сигнала адреса реге- нерации блока приоритетного обслуживания подключен к счетному входу двоичного счетчика, выход сигнала регенерации блока приоритетного обслуживания

5 подключен к входу инвертора, первому входу элемента ЗИ-НЕ и входу сигнала регенерации блока управления записью, выход сигнала занятости блока приоритетного обслуживания соединен с вторым входом эле0 мента ЗИ, выход сигнала установки блока приоритетного обслуживания соединен с входом установки триггера готовности, вход запроса обращения к памяти блока приоритетного обслуживания соединен с входом

5 сброса триггера готовности и является входом сигнала запроса обращения к памяти устройства, выход триггера готовности является выходом сигнала готовности устройства, выход элемента ЗИ подключен к синхровходу триггера цикла, информационный вход которого является входом логической единицы устройства, выход триггера цикла соединен с входом первого разряда регистра тактов, прямые выходы разрядов с первого по третий которого подключены со- отёетственно к входам разрядов с второго по четвертый регистра тактов, прямой выход первого разряда которого соединен -с вторым входом элемента ЗИ-НЕ, первым входом первого элемента 2И-НЕ, информационным входом триггера разрядов адреса и первым тактовым входом блока управления записью, прямой выход второго разряда регистра тактов подключен к третьему входу элемента ЗИ-НЕ, выход которого соединен с входом разрешения работы дешифратора синхросигналов столбца и является выходом строба записи устройства, прямой выход четвертого регистра тактов соединен с вторым входом первого элемента 2И-НЕ, выход которого подклю-, чен к входу сброса триггера цикла, выходы дешифратора синхросигналов столбца являются одноименными выходами устройства, второй тактовый вход блока управления записью подключен к инверсному выходу третьего разряда регистра тактов, первый и второй выходы блока управления записью являются соответственно выходами управления записью в младший и старший байты памяти устройства, выход инвертора подключен к первому управляющему входу мультиплексора адреса, второй управляющий вход которого соединен с выходом триггера разрядов адреса, первый информационный вход мультиплексора адреса является входом адресных разрядов столбца устройства, второй информационный вход мультиплексора адреса является входом адресных разрядов строки устройства, третий и четвертый входы мультиплексора адреса объединены и подключены к входу двоичного счетчика, выход мультиплексора адреса является выходом мультиплексированного адреса устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены регистр состояния, блок анализа состояния, дешифратор синхросигналов строки, второй элемент 2И-НЕ, элементы 2И с первого по четвертый, причем первый, второй и третий информационные входы регистра состо- янияобъединены,являются

информационными входами устройства, четвертый и пятый информационные входы

регистра состояния являются соответственно входом сигнала записи и входом сигнала записи байта устройства, шестой информационный вход регистра состояния соединен с выходом инвертора, выходы первого, четвертого и пятого разрядов регистра состояния соединены соответственно с входами младшего разряда адреса, сигнала записи

байта и сигнала записи блока управления записью, выходы второго, третьего, четвертого и шестого разрядов регистра состояния подключены соответственно к первому и второму входам адреса, входу сигнала записи и к первому входу сигнала регенерации- блока анализа состояния, третий и четвертый входы адреса которого объединены и подключены к информационному входу устройства, первый, второй и третий тактовые

входы блока анализа состояния подключены соответственно к прямым выходам пер- вого и второго разрядов и инверсному выходу второго разряда регистра тактов, второй вход сигнала регенерации блока анализа состояния подключен к выходу инвер-. тора, вход синхросигнала строки блока анализа состояния подключен к инверсному выходу первого разряда регистра тактов, вход сброса блока анализа состояния подключей к выходу первого элемента 2И-НЕ, выход разрешения цикла блока анализа состояния соединен с третьим входом элемента ЗИ, а выход сброса блока анализа состояния - с входом сброса блока приоритетного обслуживания, первый вход второго элемента 2И-НЕ подключен к выходу инвертора, второй вход второго элемента 2И-НЕ. соединен с прямым выходом первого разряда регистра тактов, первый и второй информационные входы дешифратора синхросигналов строки соединены с соответствующими входами дешифратора синх- росигналов столбца и подключены соответственно к выходам второго и третьего разрядов регистра состояния, вход разрешения дешифратора синхросигналов строки подключен к инверсному входу первого разряда регистра тактов, выходы дешифратора синхросигнала строки

подключены соответственно к первым входам элементов 2И, выходы которых являются выходами синхросигналов строки устройства, вторые входы элементов 2И объединены и подключены к выходувторого элемента 2И-НЁ.

i ;

S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| Устройство для управления оперативной динамической памятью | 1985 |

|

SU1251174A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Многоканальное устройство для ввода информации от двухпозиционных датчиков | 1988 |

|

SU1550521A1 |

| Устройство формирования сигналов управления динамической памятью | 1989 |

|

SU1741141A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на микросхемах динамической памяти. Цель изобретения - повышение быстродействия. Устройство содержит генератор импульсов регенерации, генератор тактовых импульсов, блок приоритетного обслуживания, триггер готовности, инвертор, элемент ЗИ, триггер цикла, регистр тактов, двоичный счетчик, триггер разрядов адреса, элемент ЗИ-НЕ, два элемента 2И-НЕ, блок управления записью, мультиплексор адреса,-дешифратор синхросигналов столбца,регистр состояния, блок анализа состояния, дешифратор синхросигналов строки, четыре элемента 2И, адресный вход, вход сигнала записи, вход сигнала записи байта, вход сигнала запроса обращения, выход сигнала готовности, выходы сигналов записи в младший и старший байты, выход мультиплексированного адреса, выходы синхросигналов строки и столбца, выход сигнала строба записи в регистр считывания. Быстродействие динамической памяти повышается за счет исключения паузы для восстановления заряда ячеек памяти для значительной части обращений в память при считывании информации, а также более ранней установки сигнала готовности при записи информации. 5 ил. (Л С

V;

о о

см

I

5

| Микропроцессорные средства и системы, 1986, №3 | |||

| с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Микропроцессорные средства и системы, 1989, Мг 1,с | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1992-12-23—Публикация

1990-12-29—Подача