СЛ Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Устройство выделения первого и последнего импульсов в пачке | 1989 |

|

SU1672560A2 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Устройство для ввода информации | 1988 |

|

SU1580339A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

Изобретение относится к импульсной технике и може.т быть испольэова- но в устройствах управления, измерения и обработки информации. Селектор импульсов заданной кодовой комбинации содержит сдвиговые регистры 1, CSpw и 8, дешифраторы 2, 4 и 10, счетчик 3 импульсов, триггеры 5 и 11, элементы ИЛИ 6 и 7, элементы И 12 и 13, инвертор 14. Повьшение достоверности селекции за счет исключения возможное ти формирования ложных и myльcoв на выходной шине позволяет расширить пространство селектируемых адресов кодовых слов без увеличения разрядности приемного регистра и уменьшения количества передаваемой информации. Контроль длительности паузы между кодовыми словами позволяет, не изменяя адресную часть слова, использовать длительность пуазы в качестве- дополнительного признака слова, увеличить объем информации, передаваемой по одной и той же магистрали, в два раза. 2 ил. $ (Л

С9д ;0

Изобретение относится к импульсно технике и может быть использовано в, устройствах зшравления, измерения и обработки информации,

Цель изобретения - повышение дос- товерност селекции за счет исключения возможности формирования ложных импульсов на выходной шине.

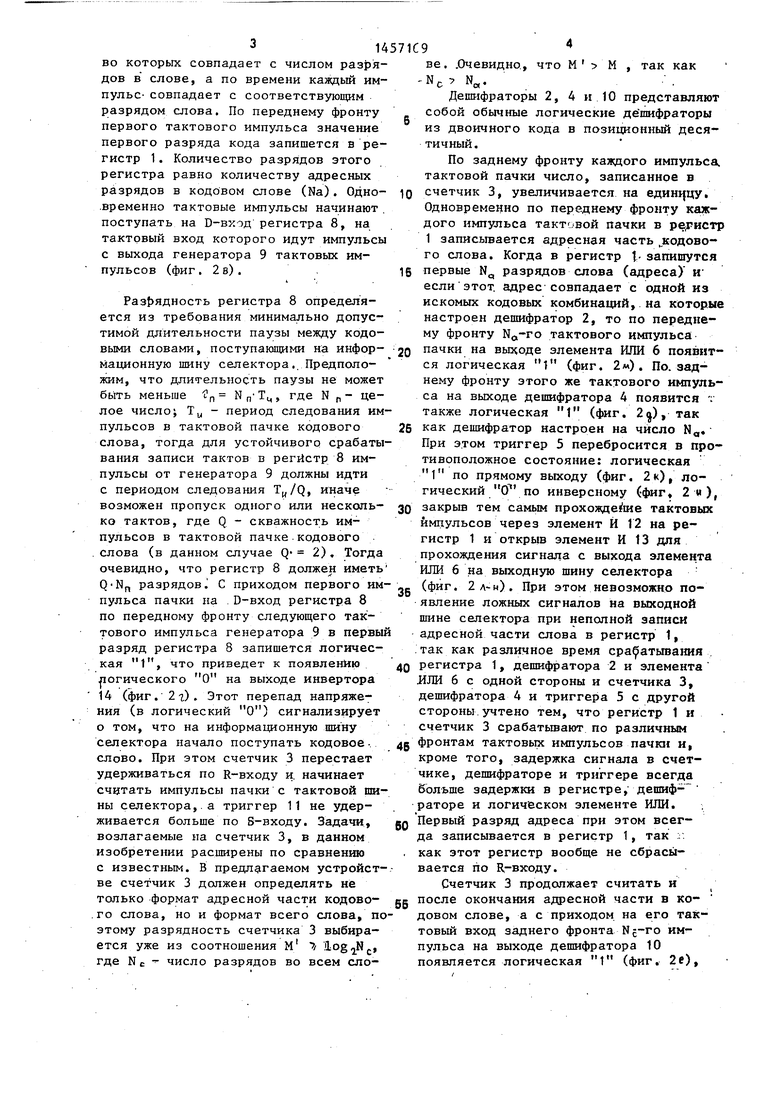

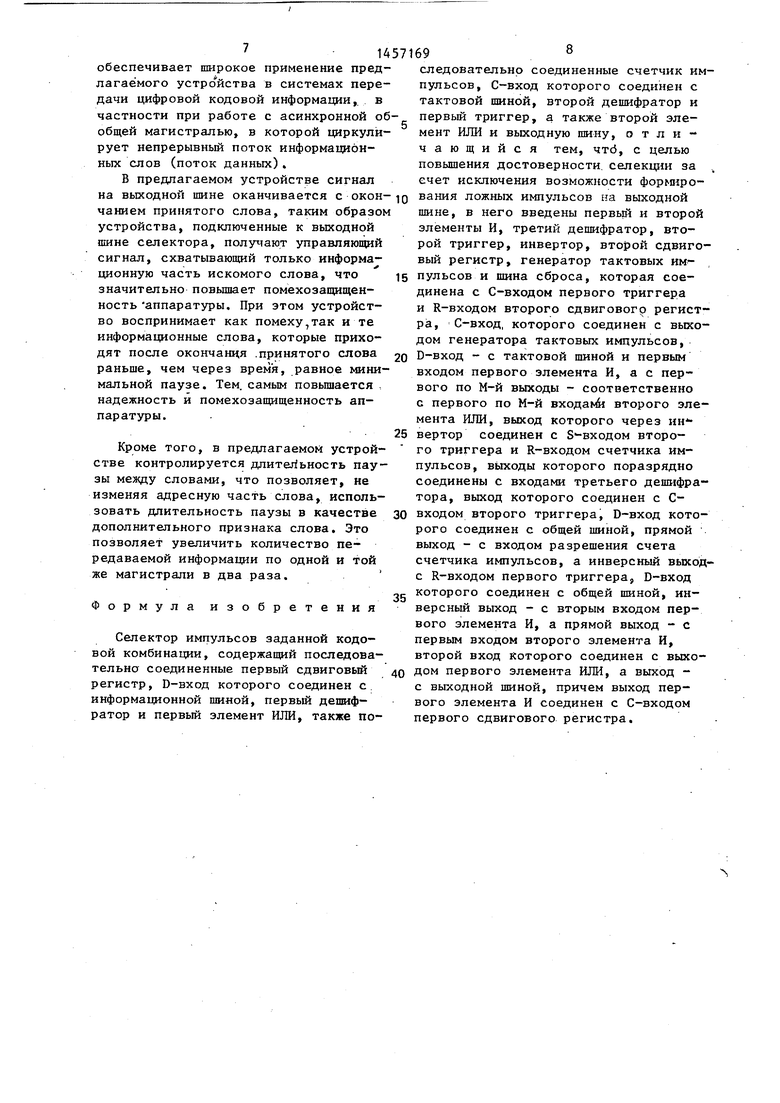

На фиг. 1 показана структурная электрическая схема устройства на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство (фиг. 1) содержит последовательно соединенные первый сдвиговый регистр 1, D-вход которого соединен с информационной шиной, первый дешифратор 2, последовательно соединенные счетчик 3 импульсов и второй дешифратор 4, выход которого соединен с S-входом первого тригге- ра 5. С.первого по N-й выходы дешифратора 2 соединены соответственно с первого по N-й входами первого элемента ИЛИ 6. С первого по М-и входы ,второго элемента ИЛИ 7 соединены соответственно с первого по М-й выходами второго сдвигового регистра 8, С- вход которого соединен с выходом генератора 9 импульсов. Выходы счетч ка 3 поразрядно соединены с входами третьего дешифратора 10, выход которого соединён с С-входом второго тригера 11. Тактовая шина соединена с D-входом регистра 8, С-входом счет- чика 3 и первым входом первого элемента И 12. Прямой выход триг- гера 5 соединен с первым входом второго элемента И 13. Выход элемента ИЛИ 7 через инвер- тор 14 соединен с R-входом счетчика 3 и S-входом триггера 11, D-вход р:оторого соединен с ши- ной, прямой выход - с входом разре- шения счетчика 3, а инверсный выход с R-входом треггера 5, D-вход которого соединен с общей шиной. С-вкод - с шиной сброса и R-входом регистра 8 а инверсный выход - с вторым входом элемента И 12, выход которого соединен с С-входом регистра 1. Выход элемента ИЛИ 6 соединен с вторым входом элемента И 13, выход которого соединен с выходной шиной.

Селектор импульсов заданной кодовой комбинации работает следуюишм образом.

Устройство предназначено для надежного выделения определенных слов

Q

5 0 5 о Q - -

0

5

из потока информационных кодовых слов (потока данных), поступающих на информационную шину селектора иэ общей магистрали. Кодовые слова представляют собой последовательные двоичные коды определенной разрядности. Наличие импульса в разряде кодирует логическую 1, отсутствие - логический О. Несколько первых разрядов слова адресные, остальные информационные . Селектор содержит адресные разряды для. определения искомого информационного слова 4 Если это слово пришло, то на выходной шине селектора появляется прямоугольный и шyльc, позволяющий устройствам, подключенным к выходной шине селектора, вьде- лять информационную часть отселекти- рованного кодового слова (например, коммутатором или записывать в запоминающее устройство), т.е. фактически на выходной шине селектора будет присутствовать строб, охватывающий информационную часть нужного слова.

В исходном состоянии после подачи питающего напряжения приходит импульс начального сброса, который устанавливает в нуль регистр 8 и триггер 5. При этом на выходе элемента ИЛИ 7 установится логический О, а на выходе инвертора 14 - логическая 1 (фиг. 2 ). На прямом выходе триггера 5 по заднему фронту импульса сброса установится логический О (фиг. 2 к), запрещающий прохождение через элемент И 13 -сигнала на выходную шину селектора (фиг. 2н). На инверсном выходе триггера 5 установится логическая 1 (фиг. 2 и), которая разрешает прохождение импульсов с тактовой шины селектора через элемент И 12 на тактовый вход регистра 1, но пока не началось очередное информационное слово, то на тактовой и на информационной шинах селектора присутствует логический О (фиг. 2а, 5, л). На выходах дешифраторов 4 и 10, а также Элемента ИЛИ 6 установится логический О (фиг. , е , к.) , на инверсном выходе триггера 11 - логический О (фиг. 2яО, а на прямом - логическая 1 (фиг. 2з), разрешающая счет в счетчике 3.

С приходом первого разряда како- го-либо информационного кодового слова на информационную шину селектора на его тактовую шину начинает поступать пачка импульсов, количество которых совпадает с числом разрядов в слове, а по времени каждый импульс- совпадает с соответствующим разрядом слова. По переднему фронту первого тактового импульса значение первого разряда кода запишется в регистр 1. Количество разрядов этого регистра равно количеству адресных разрядов в кодовом слове (Na). Одно- .временно тактовые импульсы начинают поступать на D-вход регистра 8, на тактовый вход которого идут импульсы с выхода генератора 9 тактовых импульсов (фиг . 2 в) .

Раз{)ядность регистра 8 определяется из требования минимально допустимой длительности паузы между кодовыми словами, поступающими на инфор- йационную шину селектора, Предположим, что длительность паузы не может быть меньше 1 N„ 1, где N ,, - целое число; Т, - период следования импульсов в тактовой пачке кодового слова, тогда для устойчивого срабатывания записи тактов в регистр 8 импульсы от генератора 9 должны идти с периодом следования , иначе возможен пропуск одного или несколько тактов, где Q - скважность импульсов в тактовой пачке.кодового слова (в данном случае Q 2), Тогда очевидно, что регистр 8 должен иметь

Q-Nf, разрядов. С приходом первого импульса пачки на . D-вход регистра 8 по передному фронту следующего тактового импульса генератора 9 в первы разряд регистра 8 запишется логическая 1, что приведет к появлению логического О на выходе инвертора 14 (фиг. 2 г) . Этот перепад напряжения (в логический О) сигнализирует о том, что на информационную шину селектора начало поступать кодовое-, слово. При этом счетчик 3 перестает удерживаться по R-входу и. начинает считать импульсы пачки с тактовой шины селектора,.а триггер 11 не удерживается больше по В-входу. Задачи, возлагаемые на счетчик 3, в данном изобретении расширены по сравнению с известным. В предлагаемом устройстве счетчик 3 должен определять не только формат адресной части кодово- .го слова, но и формат всего слова, поэтому разрядность счетчика 3 выбирается уже из соотношения М i ., где NC - число разрядов во всем сло

ве. .Очевидно, что М М , так как

-NC м„.

Дешифраторы 2, 4 и 10 представляют собой обычные логические дешифраторы из двоичного кода в позиционный десятичный.

По заднему фронту каждого импульса. тактовой пачки число, записанное в

1Q счетчик 3, увеличивается на един1{цу, Одновременно по переднему фронту каждого импульса тактовой пачки в ре;Ристр 1 записьгеается адресная часть кодового слова. Когда в регистр - запишутся

16 первые N разрядов слова (адреса) и если этот, адрес совпадает с одной из искомых кодовых комбинаций, на которые настроен дешифратор 2, то по переднему фронту ,-ro тактового импульса

0 пачки на выходе элемента ИЛИ 6 появится логическая 1 (фиг. 2м). По. заднему фронту этого же тактового импульса на выходе дешифратора 4 появится ; также логическая 1 (фиг. 2), так

6 как дешифратор настроен на число Ыд. При этом триггер 5 перебросится в противоположное состояние: логическая 1 по прямому выходу (фиг, 2 к), логический по инверсному (фиг, 2 и),

0 закрыв тем самым прохожде ше тактовых ймцульсов через элемент И 12 на регистр 1 и открыв элемент И 13 для прохождения сигнала с выхода элемента ИЛИ 6 на выходную шину селектора (фиг. 2л-н). При этом невозможно появление ложных сигналов на выходной шине селектора при неполной записи адресной части слова в регистр 1, так как различное время срабатывания

0 регистра 1, дешифратора 2 и элемента ИЛИ 6 с одной стороны и счетчика 3, дешифратора 4 и триггера 5 с другой стороны учтено тем, что регистр 1 и счетчик 3 срабатьшают по различным

онтаы тактовых импульсов пачки и, кроме того, задержка сигнала в счет6

0

5

чике, дешифраторе и триггере всегда больше задержки в регистре, дешиф- раторе и логическом элементе ИЛИ. Первый разряд адреса при этом всегда записывается в регистр 1, так г как этот регистр вообще не сбрасывается по R-входу.

Счетчик 3 продолжает считать и после окончания адресной части в кодовом слове, а с приходом на его тактовый вход заднего фронта Nj-rо импульса на выходе дешифратора 10 появляется логическая 1 (фиг. 2е),

так как этот дешифратор настроенного слова, и на все это время на число NC. По перепаду напряженияселектор закрыт для приема информа- (.в логическую 1) состояние тригге-ции. Когда же время минимальной пау- ра 11 изменится на противоположное зы -г, между кодовыми словами пройдет, логическая 1 по инверсному выходуто регистр 8 обнулится и на выходе (фиг. 2х), и логический О по прямо-инвертора 14 установится логическая му (фиг. 2з), так как D-вход этого 1 (фиг,21), которая обнулит счетг триггера соединен с общей шиной. Причик .3 (фиг. 2е) и установит триггер этом запрещается счет .в счетчике 3, ю1 1 в исходное состояние: логический а триггер 5 устанавливается в состоя- О по инверсному выходу (фиг. 2) ние логического О по прямому выхо-и логическая 1 по прямому (фиг.2л), ду и в логическую 1 по инверсномуразрешив тем самым счет в счетчике (фиг. 2и, к), так как еще по ()-3 и подготовив селектор к приему ному тактовому импульсу пачки с S-вхо-is вого кодового слова, да этого триггера была снята логичес-Предположим, что следующее кодо- кая 1 (фиг. 2.). Тем самым элемент вое слово имеет в адресной части ко- И 12 снова открывается для пропуска-довую комбинацию, не подлежащую деко- ния на регистр 1 тактовых импульсовдированию в селекторе. Тогда г при- пачки, но пачка уже окончилась, а20 ходом первого же импульса тактовой элемент И 13 закрывается, импульс напачки на выходе инвертора 14 появля- выходной шине селектора заканчивает-етс:я логический О (фиг. 27), а на ся. Выходной импульс охватывает толь-выходе элемента ИЛИ 6 логическая 1 ко информационную часть кодового ело-сменяется логическим О, так как в на, адрес которого совпадает с одной25 регистре 1 записана кодовая комбина- из кодовых комбинаций, на которые на-ция, не соответствующая числу, на строен селектор. которое настроен дешифратор 2 (фиг. С окончанием слова выходной сиг-2м) В остальном селектор работает нал также окончится, что исключает .как ив первом случае, только сигнал попадание импульсных помех в устрой-ЗО на выходе элемента ИЛИ.6 так и оста- ства, подключенные к выходной шинеется на уровне.логического О, поэ- селектора и активизируемые его выход-тому выходного импульса нет. ным.сигналом например, коммутаторы Предположим теперь, что после или ЗУ).окончания кодового слова раньше, чем -После окончания последнего импуль-. через- время Сп (т.е. во время паузы, са тактовой пачки с передним фрон-которую должно селектировать устрой- том следующего импульса генератораство) ., на селектор начинает поступать 9 в регистр 8 запишется в первом раз-новое кодовое слово или импульсная ряде нуль, но на выходе инверторапомеха (фиг. 2«,б), в данном случав 14 будет по-прежнему логический О,40 .принято ЗТ, а здесь импульс так как в остальных разрядах регист-приходит через время 1,5Т . Это сло- ра В будут записаны логические или помеха не могут быть приняты И так будет до тех пор,.пока хотяселектором, так как счет в счетчике бы в одном разряде.регистра 8 будет3 запрещен а значит не может быть логическая 1. При. этом счетчик 345 открыт элемент И 13. Счетчик 3 будет закрыт для счета логическим О с пря-закрыт для счета до тех пор, пока мого выхода триггера 11, при.ем инфор-пауза между кодовыми словами не ста- мационных слов невозможен. Чтобы всенет равной 1, так как только тог- разряды регистра 8 обнулились надо,да может переброситься триггер 11, чтобы при отсутствии сигналов на D-gQ удерживающий счетчик 3. входе этого регистра (логический О),Таким образом, за счет введения на его тактовый вход пришло количест-новых элементов и связей повысилась во,импульсов, равное количеству разря-надежность работы и помехозащищен- дов этого регистра, т.е. Q-N, а такность предлагаемого устройства, а за как период следования импульсов ге-gg счет этого расширилось пространст- ; нератора 9 равен Tn/Q, то на выходево селектируемых им адресов кодовых .инвертора 14 логический будетслов без увеличения разрядности при- еще держаться время -г „ Нг, Т„ пос-емного регистра и уменьшения ксшиче- ле окончания очередного информацион-ства передаваемой информации. Все это

обеспечивает широкое применение предлагаемого устройства в системах передачи цифровой кодовой информации, в частности при работе с асинхронной о общей магистралью, в которой циркулирует непрерывный поток информационных слов (поток данных).

В предлагаемом устройстве сигнал на выходной шине оканчивается с окон чанием принятого слова, таким образо устройства, подключенные к выходной шине селектора, получают управляющий сигнал, схватывающий только информационную часть искомого слова, что значительно повьппает помехозащищенность аппаратуры. При этом устройство воспринимает как помеху,так и те информационные слова, которые приходят после окончания .принятого слова раньше, чем через время, равное минимальной паузе. Тем. самым повышается надежность и помехозащищенность аппаратуры.

Кроме того, в предлагаемом устройстве контролируется длительность паузы между словами, что позволяет, не изменяя адресную часть слова, использовать длительность паузы в качестве дополнительного признака слова. Это позволяет увеличить количество передаваемой информации по одной и той же магистрали в два раза.

Формула изобретения

Селектор импульсов заданной кодовой комбинации, содержащий последовательно соединенные первый сдвиговый регистр, D-вход которого соединен с. информационной шиной, первый дешифратор и первый элемент ИЛИ, также по8

Q 15 2о

25

О

5

0

следовательно соединенные счетчик импульсов, С-вход которого соединен с тактовой шиной, второй дешифратор и первьй триггер, а также второй элемент ИЛИ и выходную шину, отличающийся тем, чти, с целью повышения достоверности, селекции за счет исключения возможности вания ложных импульсов на выходной шине, в него введены первьв1 и второй элементы И, третий дешифратор, второй триггер, инвертор, второй сдвиговый регистр, генератор тактовых импульсов и шина сброса, которая соединена с С-входом первого триггера и R-входом второго сдвиговогр регистра, С-вход, которого соединен с выходом генератора тактовых импульсов, D-вход - с тактовой шиной и первым входом первого элемента И, а с первого по М-й выходы - соответственно с первого по М-й входами второго элемента ИЛИ, выход которого через ин вертор соединен с З -входом второго триггера и R-входом счетчика импульсов, выходы которого поразрядно соединены с входами третьего дешифратора, выход которого соединен с С- входом второго триггера, D-вход которого соединен с общей шиной, прямой выход - с входом разрешения счета счетчика импульсов, а инверсный вькод- с R-входом первого триггера, D-вход которого соединен с общей шиной, инверсный выход - с вторым входом первого элемента И, а прямой выход - с первым входом второго элемента И, второй вход Которого соединен с выходом первого элемента ИЛИ, а выход - с выходной шиной, причем выход первого элемента И соединен с С-входом первого сдвигового регистра.

М

Н

Tjua

Фиг. 2

| Селектор импульсов заданной кодовой комбинации | 1982 |

|

SU1092715A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Селектор импульсов заданной кодовой комбинации | 1982 |

|

SU1131032A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-02-07—Публикация

1987-02-11—Подача