(5) ДВОИЧНЫЙ УМНОЖИТЕЛЬ ЧИСЛА ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель импульсов | 1984 |

|

SU1292176A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Цифровой генератор функций | 1986 |

|

SU1388842A1 |

| Устройство для измерения расстояния | 1984 |

|

SU1219922A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

1

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах, предназначенных для выполнения операции подсчета числа импульсов с одновременным умножением результата на произвольное наперед заданное положительное натуральное число.

Известен двоичный умножитель числа импульсов, содержащий в каждом разряде триггер, элементы И, элементы ИЛИ 1.

Недостаток этого устройства заключается в ограниченных Функциональных возможностях. Коэффициент умножения может принимать только два фиксированных значения ±5.

Известен двоичный умножитель числа импульсов, содержащий входную шину и М разрядов, первый разряд содержит триггер, каждый последующий разряд содержит триггер и элемент И в каждом разряде, кроме первого,

управляющий вход триггера соединён с первым входом элемента И последующего разряда, второй вход элемента И которого соединен с прямым выходом триггера предыдущего разряда выход элемента И соединен с входом управления триггера, первый и второй входы элемента И второго соединены соответственно с шиной потенциала логической единицы и с прямым выходом триггере первого разряда, выходная шина соединена со счетными входами триггеров разрядов J.

Недостаток известного устройства заключается в ограничениях функцио- . нальных возможностей. Коэффициент умножения может принимать только одно значение +1. .

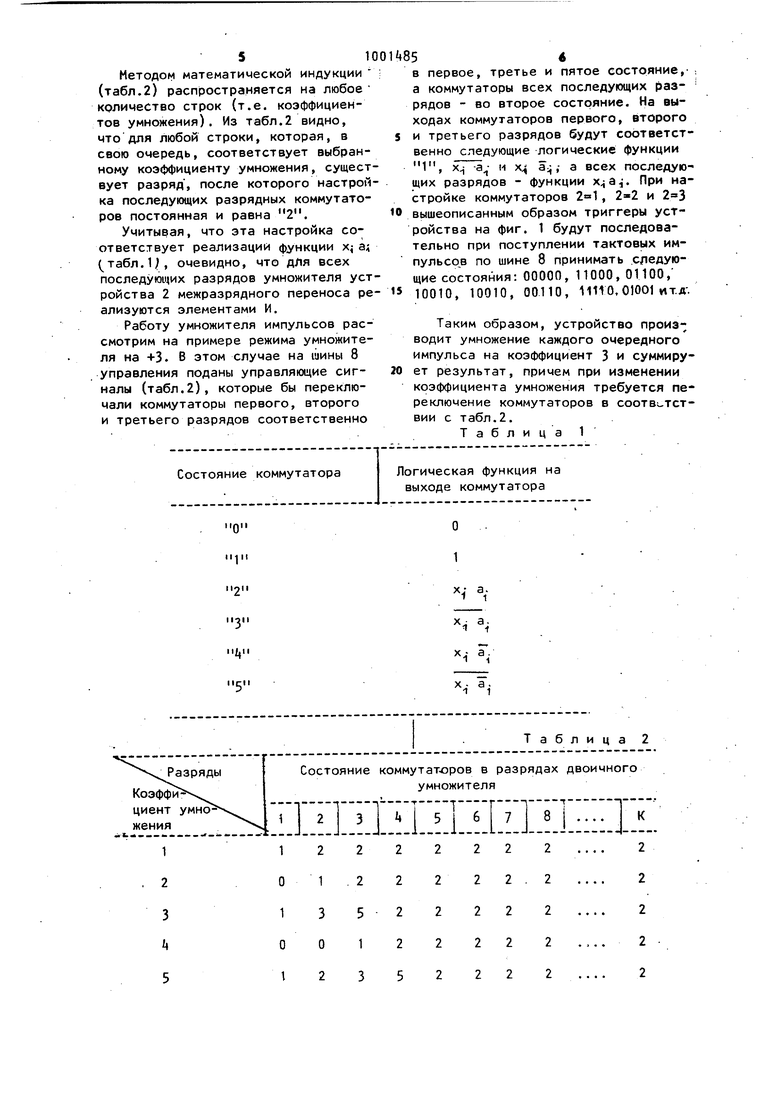

Цель изобретения - расширение функциональных возможностей устройства в части обеспечения умножения числа импульсов на любое натурное положительное число. Поставленная цель достигается тем, что в двоичный умножитель числа импульсов, содержащий входную шину и М разрядов, первый разряд со держит триггер, каждый последукнций разряд содержит триггер и первый эл мент М, в каждом разряде, кроме пер вого, управляющий вход триггера сое динен с первым входом первого элемента И последующего разряда, второ вход первого элемента И которого со динен с прямым выходом триггера пре дыдущего разряда, в каждом разряде, начиная с К-го,где К меньше М, выход первого элемента И соединен с управляющим входом триггера, вход ная шина соединена со счетными вход ми триггеров, введены шины управления, шины потенциалов логических нуля и единицы,в первый разряд вве- у ден коммутатор, а вхаждый разряд с второго по К-1 введены коммутатор, второй элемент И и три элемента НЕ, в каждом разряде с первого по К-1-й шины потенциалов логических нуля и единицы соединены соответственно с первым и вторым инфор1мационными входами коммутатора, вхо ды управления которого соединены с соответствующими шинами управления, выход коммутатора соединен с управляющим входом триггера, в каждом ра ряде с второго по К-1-Й выход перво го элемента И соединен с третьим информационным входом коммутатора и соединен через первый элемент НЕс четвертым информационным входом ком мутатора, пятый.и шестой информационные входы которого соединены соответственно с выходом второго элемента И и с выходом второго элемента НЕ , вход которого соединен с выходом второго элемента И,первый вход которо соединен с первым входом первого элеме та И,второй вход которого соединен с входом третьего элемента НЕ, выход которого соединен с вторым входом вто рого элемента И, На чертеже приведен двоичный умн житель числа импульсов с коэффициентом умножения +3. На чертеже обозначено триггеры 1в1-1 5; коммутаторы элеме ты И , элементы НЕ входная шина 5; шины 6 и 7 потенциалов соответственно логических нуля и единицы; шины 8 управления. Входная шина 5 соединена со счетными входами триггеров входы управления которых соединены соответственно с выходами коммутаторов и с выходами элементов И 3 5 и , выходы коммутаторов 2иЗ и выход элемента И соединены соответственно с первыми входами элементов И , , , вторые входы которых соединены соот- ; ветственно с прямыми выходами три1- герое шины 8 управления соединены с соответствующими входами управления коммутаторов , первый и второй информационные входы которых соединены соответственно с шинами 6 и 7 потенциалов логических нуля, и единицы, третьи информационные входы коммутаторов. и соединены соответственно с выходами элементов. И и и соединены соответственно с входами элементов НЕ .и , выходы которых соединены соответственно с четвертыми информационными входами коммутаторов и ,пятые информационные входы которых соединены соответственно с выходами элементов И и и соединены, соответственно с входами i элементов НЕ и 5, выходы которых соединены соответст-венно с шестыми информационными входами коммутаторов и выходы коммутаторов и соединены соответственно с первыми входами элементов И и . вторые входы которых соединены с выходами элементов НЕ и , входы которых соединены соответственно с прямыми выходами триггеров U-1 и . , На выходах коммутаторов, в зависимости от настройки по шинам 10, сформированы шесть функций, две из которых - потенциалы-логических нуля и единицы, а четыре остальных - функции от аргументов х.- и а.. , где х -д - Де л сигнал разрешения на переключение i-ro триггера, а- - сигнал на прямом выходе i-rb триггера. Приведенная табл. 1 дает соответствие между номером состояния коммутатора и логической функцией на выходе коммутатора. Настройка коммутаторов в зависимости от заранее задаваемых коэффициентов производится в соответствии с табл.2.

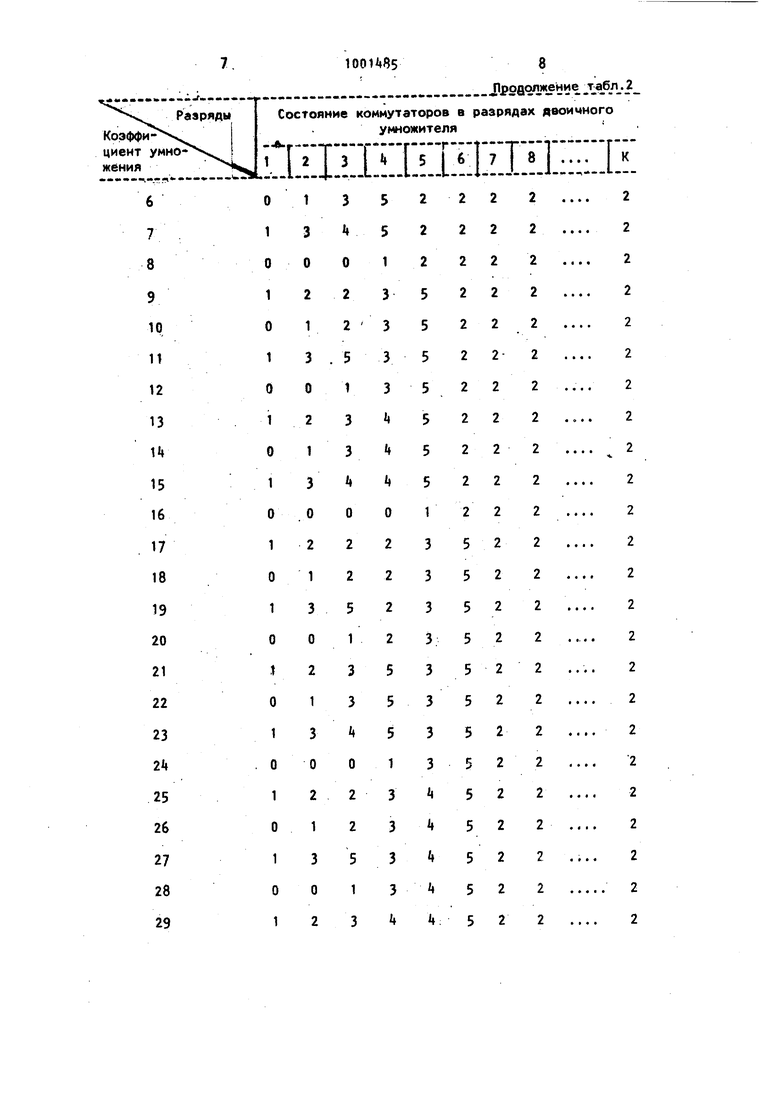

Методом математической индукции (табл.2) расп|эостраняется на любое количество строк (т.е. коэффициентов умножения). Из табл.2 видно, что для любой строки, которая, в свою очередь, соответствует выбранному коэффициенту умножения, существует разряд, после которого настройка последующих разрядных коммутаторов постоянная и равна 2.

Учитывая, что эта настройка соответствует реализации функции х а; (табл.и, очевидно, что для всех последующих разрядов умножителя устройства 2 межразрядного переноса реализуются элементами И,

Работу умножителя импульсов рассмотрим на примере режима умножителя на -ьЗ. В этом случае на шины 8 управления поданы управляющие си|- налы (табл.2), которые бы переключали коммутаторы первого, второго и третьего разрядов соответственно

Состояние коммутатора

О I111I

Пои

11-211

ll/jll

llrll

в первое, третье и пятое состояние, а коммутаторы всех последующих разрядов - во второе состояние. На выходах коммутаторов первого, второго и третьего разрядов будут соответственно следующие логические функции

Ч и х

XH ,- а всех последующих разрядов - функции ,. При настройке коммутаторов , и

вышеописанным образом триггеры устройства на фиг. 1 будут последовательно при поступлении тактовых импульсо в по шине 8 принимать следующие состояния: 00000, 11000, 01100,

10010, 10010, 00110, 11110,01001 ИТД-.

Таким образом, устройство производит умножение каждого очередного импульса на коэффициент 3 и суммирует результат, причем при изменении коэффициента умножения требуется переключение коммутаторов в соотв -тствии с табл.2.

Таблица 1

Логическая функция на выходе коммутатора

а.

N

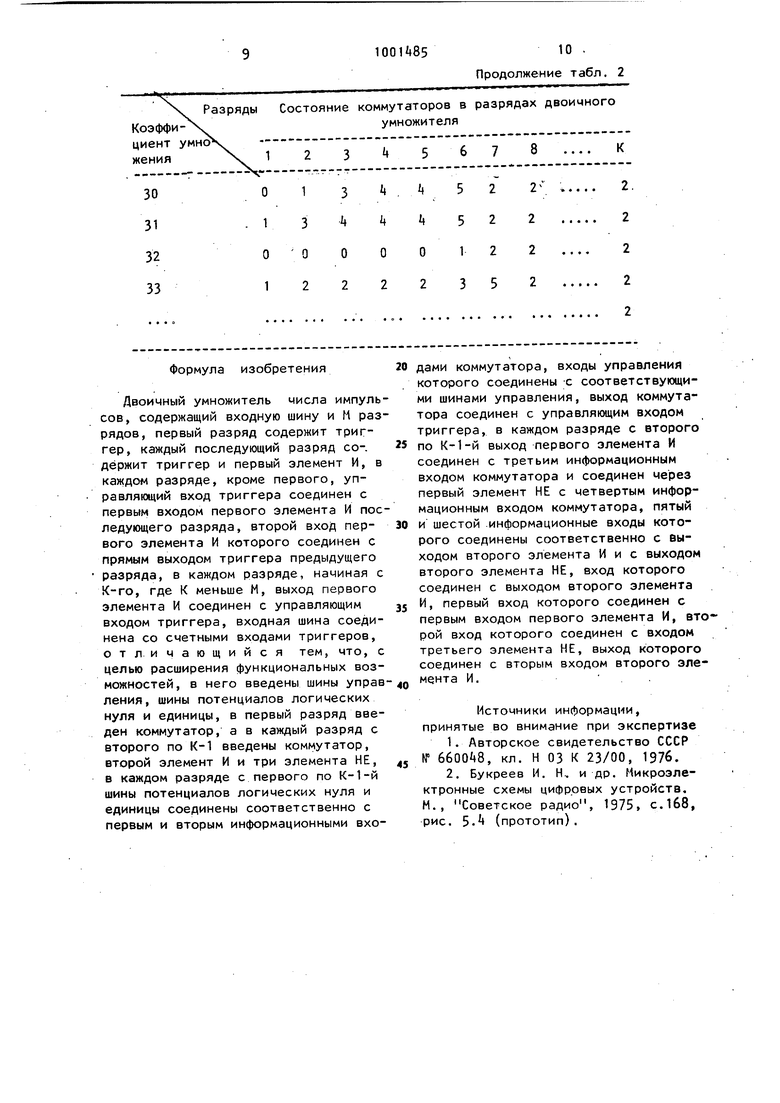

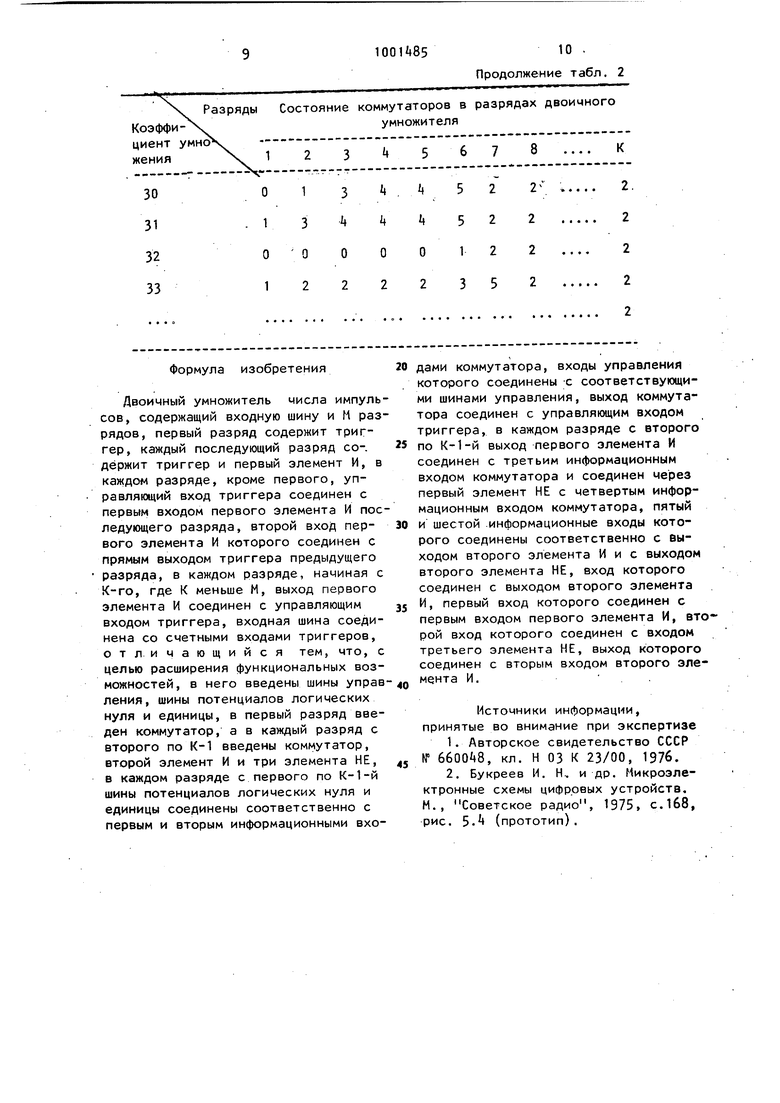

N Таблица 2

100НВ58

продолжение .2 Разряды Состояние коммутаторов в Коэффи-.умножителя циент умноЧ жения N. 123

Формула изобретения

Двоичный умножитель числа импульсов , содержащий входную шину и М разрядов, первый разряд содержит триггер, каждый последующий разряд содержит триггер и первый элемент И, в каждом разряде, кроме первого, управляющий вход триггера соединен с первым входом первого элемента И последующего разряда, второй вход первого элемента И которого соединен с прямым выходом триггера предыдущего разряда, в каждом разряде, начиная с К-го, где К меньше М, выход первого элемента И соединен с управляющим входом триггера, входная шина соединена со счетными входами триггеров, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены шины управления, шины потенциалов логических нуля и единицы, в первый разряд введен коммутатор, а в каждый разряд с второго по К-1 введены коммутатор, второй элемент И и три элемента НЕ, в каждом разряде с первого по К-1-й шины потенциалов логических нуля и единицы соединены соответственно с первым и вторым информационными вхо100U8510 ,

Продолжение табл. 2

дами коммутатора, входы управления которого соединены с соответствующими шинами управления, выход коммутатора соединен с управляющим входом триггера, в каждом разряде с второго

по К-1-й выход первого элемента И соединен с третьим информационным входом коммутатора и соединен через первый элемент НЕ с четвертым информационным входом коммутатора, пятый

и шестой информационные входы которого соединены соответственно с выходом второго элемента И и с выходом второго элемента НЕ, вход которого соединен с выходом второго элемента

И, первый вход которого соединен с первым входом первого элемента И, второй вход которого соединен с входом третьего элемента НЕ, выход которого соединен с вторым входом второго элемента И, ,

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 6600Д8, кл. Н 03 К 23/00, 1976.

2,Букреев И, Н, и др. Микроэлектронные схемы цифровых устройств, М., Советское радио, 1975, с.168, рис. Б. (прототип). разрядах двоичного

Авторы

Даты

1983-02-28—Публикация

1981-10-12—Подача