11

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах, предназначенных для выполнения операции подсчета числа импуль- сов с одновременным умножением результата на произвольное, наперед заданное число.

Цель изобретения - расширение области применения за счет обеспечения возможности умножения на любое число натурального ряда чисел.

На фиг.1 изображена .функциональная схема умножителя импульсов; на фиг.2 - функциональная электрическая схема устройства межразрядного переноса; на фиг.З - временная диаграмма работы умножителя импульсов

Устройство содержит младшие разряды 1, старшие разряды 2, триггеры 3, элементы И4, элементы ИЛИ 5, блок 6 межразрядного переноса, пер- вьш 7 и второй 8 информационные входы устройства, шину 9 управления шину 0 вычитания, шину 11 сложе- ния, выходы 12-16 устройства, вход 17. Блок 6 межразрядного переноса выполнен на первом и втором элементах И 18 и 19, трех элементах НЕ 20-22, коммутаторе 23. Устройство содержит шину 24 логической, и шину 25 логического О.

Устройство работает следзпощим образом.

Состояние коммутатора 23 (настрой ка) определяется кодами на его шинах 9 управления.

Настройка коммутатора 23 блока 6 межразрядного переноса в зависимос- |Ти от заранее задаваемых значений коэффициентов умножения производится для положительных коэффицг1ентов умножения в соответствии с табл.1, а для отрицательных - в соответствии с табл.2.

Методом математической индукции табл.1 и 2 распространяются на любое количество строк (т.е. коэффициентов умножения). Из табл.1 и 2 видно, что для любой строки, которая в свою очередь соответствует выбранному коэффициенту умножения, существует разряд, после которого настройка последующих ,разрядов коммутаторов 23 постоянная к равная 2 для подожитель ных коэффициентов умножения и 5 - . для отрицательных.

Учитьшая, что эта настройка соответствует реализации функции х; а;

O

5

0

5

21

,5

5

0 5

0 5.

0

762

для положительных коэффициентов умножения (см.табл.3) и X ; а; - для отрицательных, очевидно, что для всех старших разрядов умножителя импуль- | сов блок 6 межразрядного переноса реализуется элементами И.

Операция установки кодов управления заключается в подаче управляющих сигналов на шины 9 управления, задающих настройку блоков 6 межразрядного переноса.

Операция подачи входных импульсов заключается в подаче на вход 17 пачки пересчитьюаемых импульсов,а на шину 1 (или шину 10) - команды, определяющей знак пересчета (сложение или вычитание).

Операция считывания результата заключается в готовности выходов 12- 16 и передаче результатов счета.

Времена U,| - и, определяют длительность циклов счета при умножении на коэффициенты К,- К (значения коэффициентов любые из ряда натуральных чисел).

Времена t, t, tj определяют затухание переходного процесса В элементах устройства и выбирают в зависимости от элементной базы, на которой построен умножитель импульсов .

Время t определяется количеством и частотой выходных импульсов, поступающих на вход 17.

Время 1„ выбирается произвольно и определяется интервалом между соседними циклами счета.

Работу умножителей импульсов рассмотрим на примере режима умножения на -5. В этом случае на шину 9 управления должны подаваться следую- .щие управляющие сигналы:

Первый разряд-1

Второй разряд-2

Третий разряд-3

Четвертый разряд -4

Пятьй разряд и все

последующие разряды -5

В соответствии с табл.3 фунции . межразрядных переносов имеют вид:

Для первого разряда 1

Для второго разряда

Для третьего разряда

Для четвертого разряда

Для пятого и всех последующих

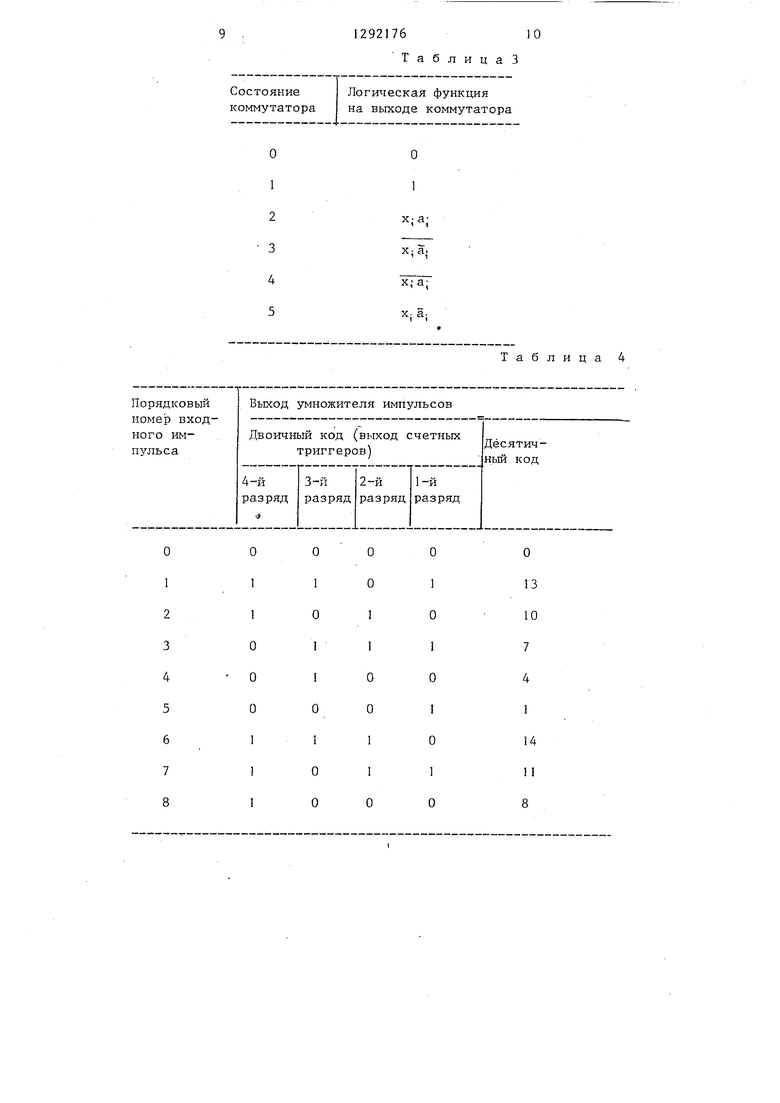

Для рассматриваемого случая состояния умножителя импульсов описывает табл.4.

Х;

31

Из табл.4 следует, что умножитель импульсов проводит умножепие каждого очередного импульса, поступающего на вход 7, на коэффициент - 5 и суммирует результат.

Формула изобретения

Умножитель импульсов, содержащий в каждом младшем разряде блок меж- разрядного переноса, вьтолненный на элементах НЕ, элементах И и коммутаторе, выходы первого и второго элементов И соединены непосредственно с соответствующими первыми и через первый и второй элементы НЕ с соответствующими вторыми входами коммутатора, выход третьего элемента НЕ подключен к первому входу второго элемента И, ив каждом разряде триггер, счетный вход которого является входом умножения, прямой выход триггера в каждом младшем разряде подключен к первому входу первого элемента И и входу третьего элемента НЕ блока межр азрядрюго переноса следующего младшего разряда, в каждом старшем разряде содержит элемент И, прямой выход триггера предьщущего старшего разряда соеди иен с первым входом.элемента И последующего разряда, управляющий вход коммутатора блока межразрядного переноса является управляющим входом умножителя, выход коммутато- ра блока межразрядного переноса . каждого младшего разряда соединен с управляющим входом триггера того же младшего разряда и вторьми входами первого и второго элементов И

-

f5

1-292

ь о5

я

0 ао35 40

20

25

30

1764

блока межразрядного переноса следующего младщего разряда, выход коммутатора блока межразрядного переноса последнего младшего разряда подключен к второму входу первого элемента И первого старшего разряда, первый и второй информационные входы коммутатора блока межразрядного переноса являются соответственно входами логической единицы и логического нуля умножителя, отличающийся тем, что, с целью расширения области применения за счет обеспечения возможности згмножения на любое число из натурального ряда чисел, в него введены в каждьй старший разряд второй элемент И и элемент 1ШИ, выход которого соедр1нен с управляющим входом триггера этого старшего разряда и вторым и первым входами соответственно первого II второго элементов И следующего старшего разряда, выходы которых подключены соответственно к первомз и второму входам элемента ШШ своего старшего разряда, инверсный выход триггера старшего разряда соединен с вторым входом второго элемента И послед тощего старшего разряда, третьи входы первого и второго элементов И старших разрядов являются соответственно входами сложения и вычитания умножителя, первые входы первого и второго элементов И первого младшего разряда объединены и являются первым гшформацион- ным входом у 5ножителя, второй вход первого элемента И и вход третьего элемента НЕ первого младшего разряда объединены и являются вторым ин-, формационным входом умножителя.

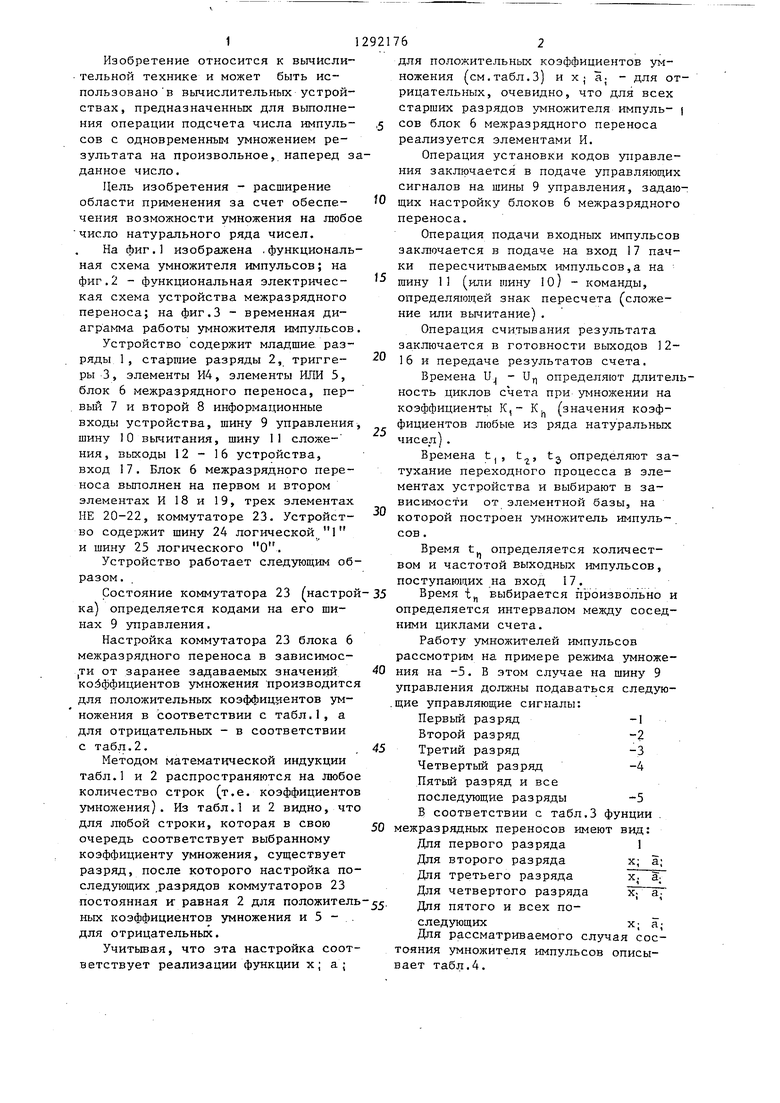

Таблица J

Продолжение табл. J

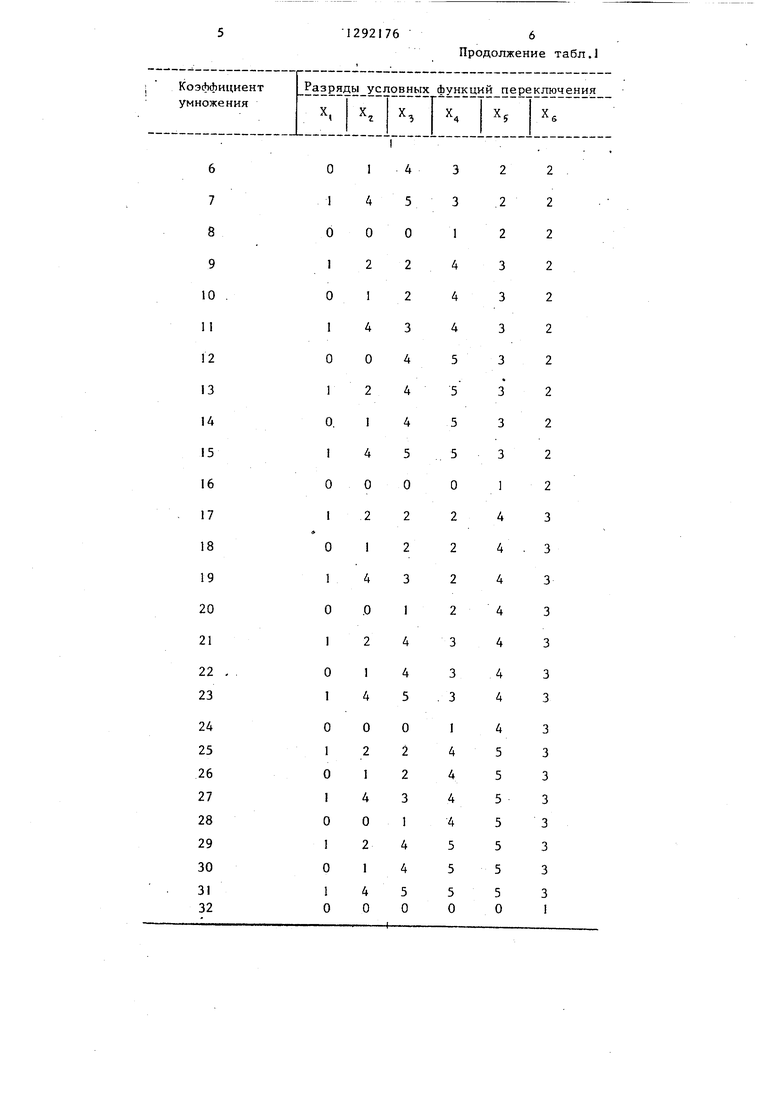

Т а б л и ц а 2

129217610

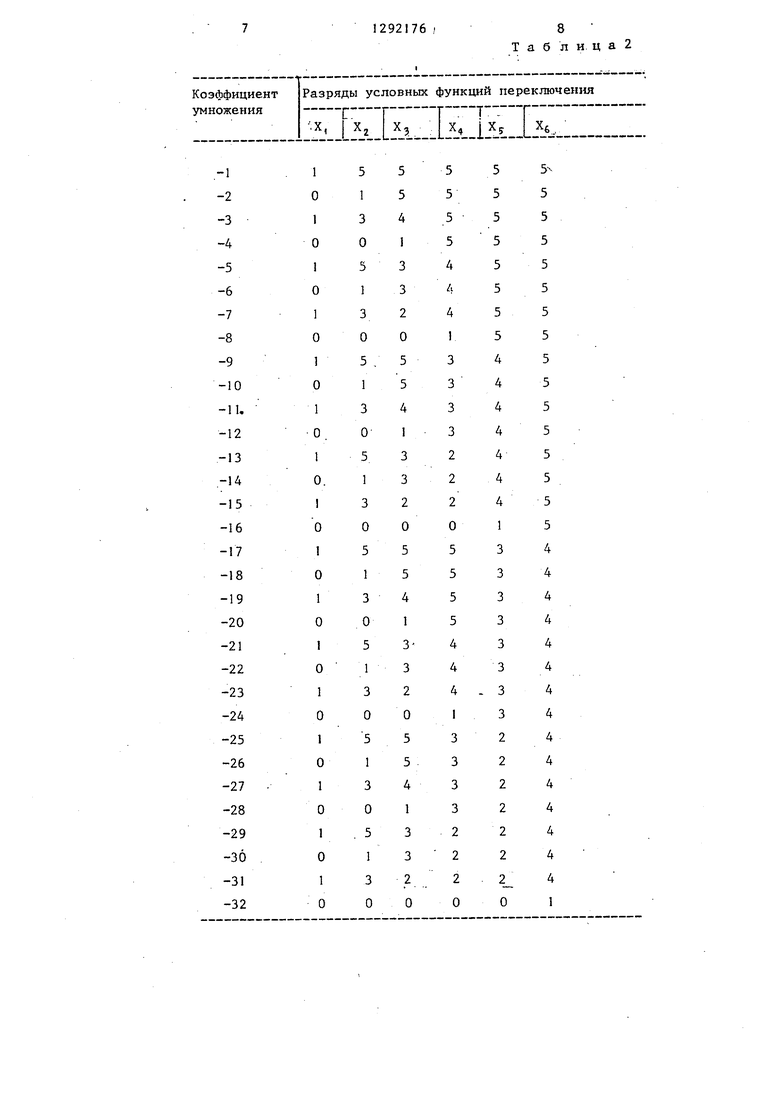

ТаблицаЗ

Таблица 4

25лвг 0 24 AJzTo

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный умножитель числа импульсов | 1981 |

|

SU1001485A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Умножитель числа импульсов | 1984 |

|

SU1211877A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство для деления | 1990 |

|

SU1728860A1 |

Изобретение относится к области, вычислительной техники и может быть использовано в вычислительных устройствах. Целью изобретения является расширение области пр1п-1енения за счет возможности умножения на любое число из натурального ряда чисел. Умножитель импульсов состоит из младших разрядов, старших разрядов, триггеров, элементов И, элементов ИЛИ, блоков межразрядного переноса, первого и второго информационных входов. Устройство содержит шины управления, сложения, вычитания, вход, выходы разрядов, шины логического нуля и логической единицы. Блок межразрядного переноса выполнен на двух элементах И, трех элементах НЕ и коммутаторе. 3 ил. 4 табл.

| Реверсивный счетчик-умножитель | 1975 |

|

SU563726A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Двоичный умножитель числа импульсов | 1981 |

|

SU1001485A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-23—Публикация

1984-07-20—Подача