Изобретение относится к вычислительной технике, а точнее к системам обработки данных, импользуюиих магистральный принцип объединения устройств.

Известны системы обработки данных с магистральной структурой, в которых устройства соединены параллельно с другом через общую шину, причем эта парешлельность подключения выдержана для всех сигналов, кроме сигналов разрешения прерывания и прямого доступа fl3 - СЗ.

Архитектурная стройность известных систем, единство способов подключения устройств и работы с ними является в то же время и причиной одного из недостатков. Единая магистраль ограничивает скорость передачи данных и их формат, т.е. ограничивает быстродействие. Пропускная способность магистрали управляющих вычислительных комплексов СМЗ и См4 при работе с оперативным запомингиощим устройством (ОЗУ) составляет величину порядка 1,Т Мбайт/с, что является существенным ограничением для построения высокопроизводительных моделей этой структуры, затрудняет применение.быстродействующей

полупроводниковой оперативной памяти, быстрых спецпроцессоров и т.о.

При подключении быстрых обрабатывающих, особенно поточных устройств, например спецпроцессоров реального времени, быстродействие их ограничивается пропускной способностью магистрали . При работе достаточно быстрого спецпроцессора, например,

10 с граничной частотой в режиме реального времени 500 кГц (т.е. прием двух комплексных отсчетов и передача KByyi комплексных отсчетов в секунду) необходимо передавать по одному 15 слову (например, действительная часть первого отсчета, мнимая часть первого отсчёта, действительная часть второго отсчета и т.д.) и реальиое быстродействие спецпроцессора опре20деляется параметрами системл магистраль - память, т.е. падает до величины приблизительно 275 кГц.

Целью изобрете.ия является увеличение быстродействия системы об25работки данных с магистральной структурой при обработке массивов.

Цель достигается тем, что.в систему обработки данных, содержащую процессор, два запомингиощих устройства,

30 блок прямого доступа и регистр передачи, вход-выход которого соединен с информационным входом-выходом системы, вход регистра передачи подключен к выходу данных блока прямого доступа/ управляющий вход-выход процессора соединен с управляющими входами-выходами запоминающих устройств и блока, прямого доступа, а вход-выход адреса и вход-выход данных процессора подключены соответственно к входам-выходам адреса и входам-выходам данных первого эапоминаю.щего устройства и блока прямого доступа, введены коммутатор адреса, ко мутатор данных, блок управления и блок элементов И, информационный вхо которого соединён с выходом регистра передачи, управляющий вход блока элементов И подключен к выходу разрешения приема данных блока прямого доступа, а выход блока элементов И соединен с входом-выходом данных второго запоминающего устройства,вход блока управления подключен к выходу управления коммутацией блока прямого доступа, а выход блока управления соединен с управляющими входами коммутаторов адреса и данных, первые входы-выходы которых подключены соответственно к входам-выходам адреса и данных процессора, а вторые входывыходы - к входам-выходам соответственно адреса и данных второго запоминающего устройства.

Кроме того, процессор содержит дв блока элементов И, сумматор, блок регистров, регистр адреса, регистр состояния, шифратор адреса, регистр адреса микрокоманды, память микрокоманд, регистр микрокоманды,блок сравнения приоритетов и регистр управления, вход-выход которого соединен с управляющим входом-выходом процессора, первыми входами шифратора адреса и блока сравнения приоритетов и первым выходом регистра микрокоманда, вход которого подключен к выходу памяти микрокоманд, а выход - к втором входу блока сравнения приоритетов, первым входам первого и второго блоков элементов И и управляющим входам регистра адреса, регистра состояния, сумматора и блока регистров, выход блока регистров соединен с третьим входом блока сравнения приоритетов, первым информационным входом сумматора, выходом регистра состояния и вторым входом шифратора адреса,выход блока сравнения приоритетов подключен к третьему входу шифратора адрес и входу регистра управления, вход регистра адреса микрокоманды соединен с выходом шифратора адреса, а выход с входом памяти микрокоманд, выход сумматора подключен к входам блока регистров/регистра адреса,регистра состояния ri второму входу первого блока элементов И,вход-выход данных процессора соединен с выходом первого блока элементов И и вторым информационным входом сумматора, второй вхо второго блока элементов И подключен к выходу регистра адреса, а выход к входу-выходу адреса процессора.

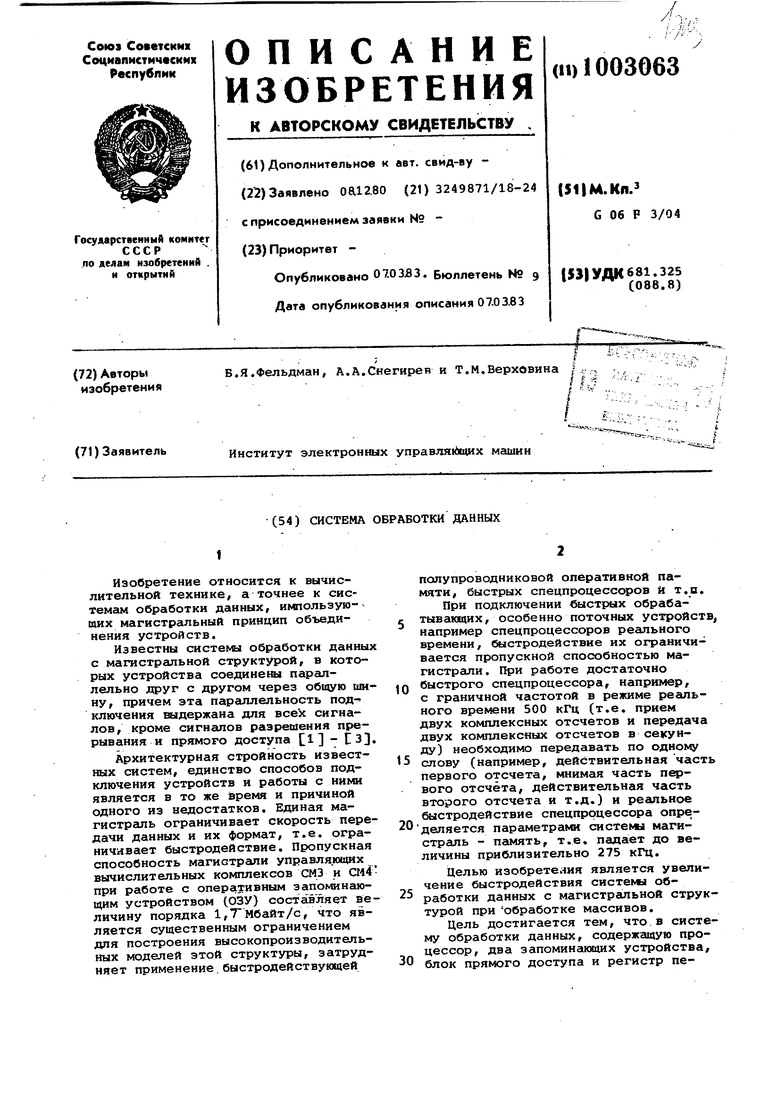

Причем -блок управления содержит триггер режима, элемент И, два элемента И-НЕ и элемент НЕ, при этом вход элемента НЕ, первый и второй входы элемента И и синхровход триггера режима соединены с входом блока, выход элемента И подключен к установочному входу триггера режима, прямой выход которого соединен с выходом блока, а инверсный выход подключен к первым входам первого и второго элементов , вторые входы которых соединены соответственно с входом блока и выходом элемента НЕ, а выходы элементо И-НЕ подключены к выходу блока.

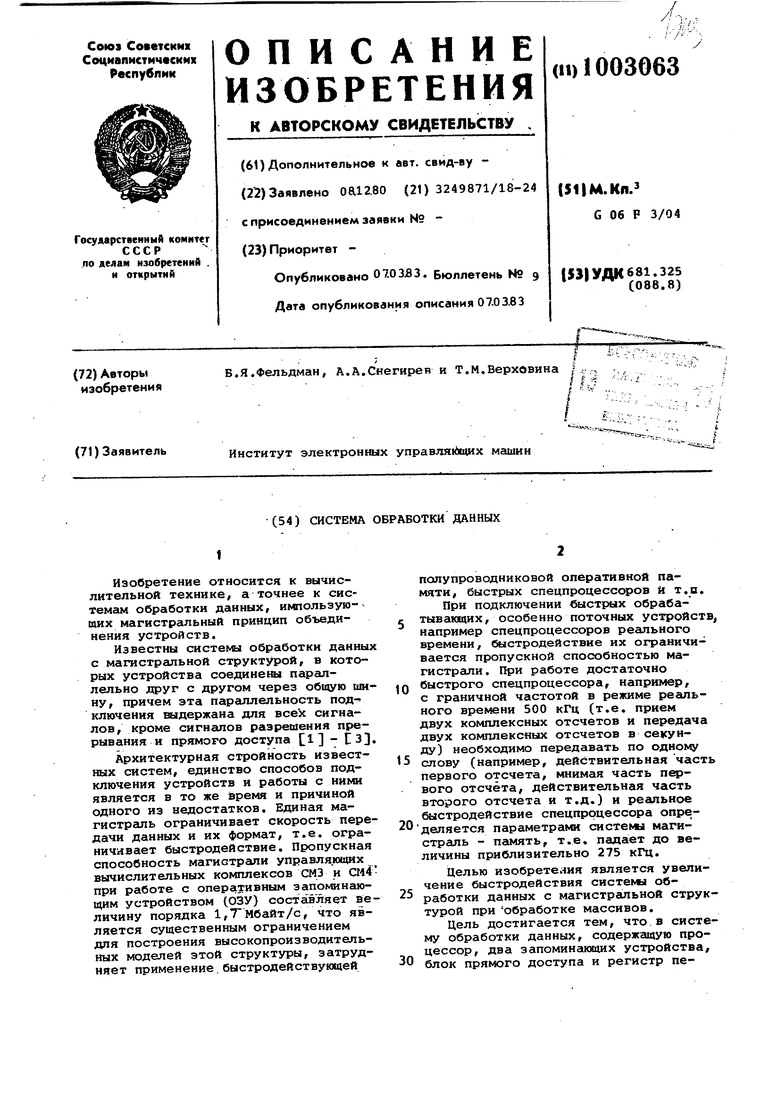

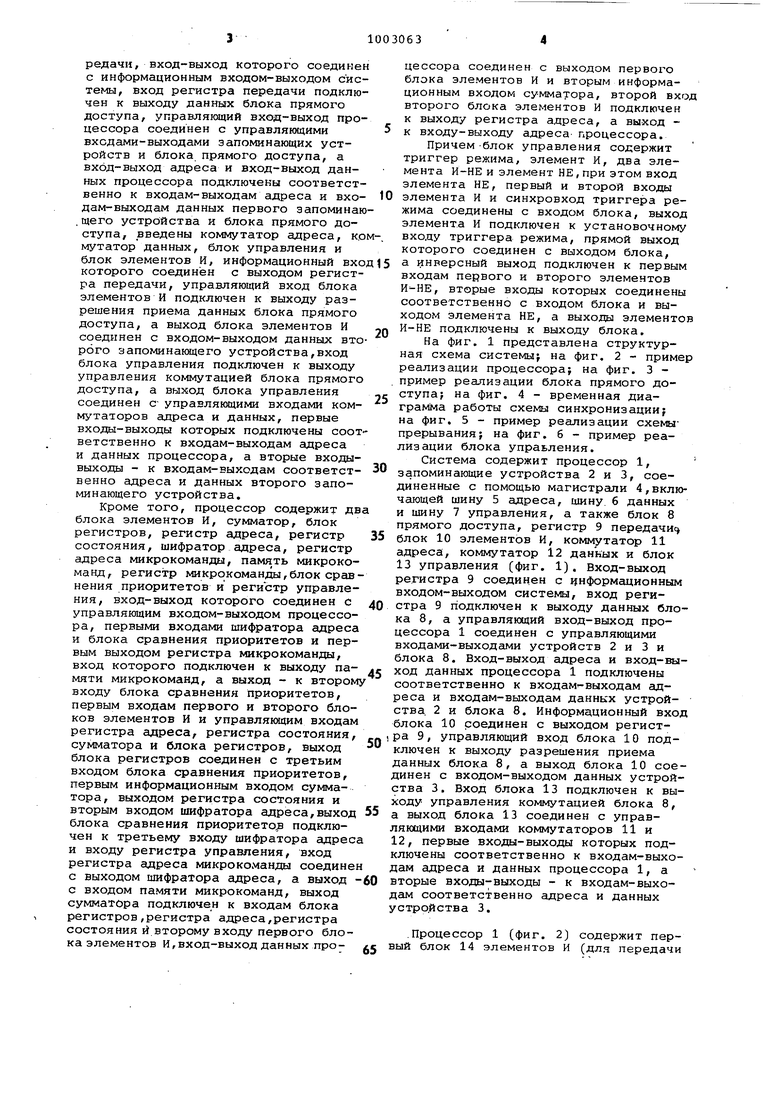

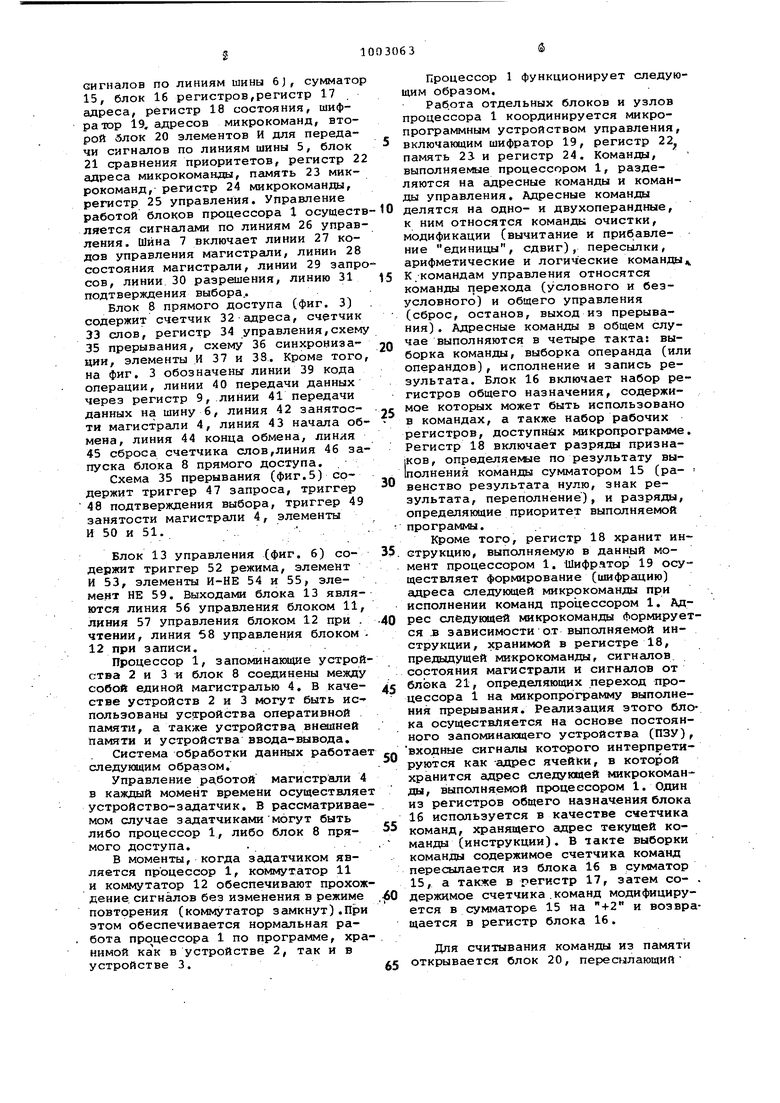

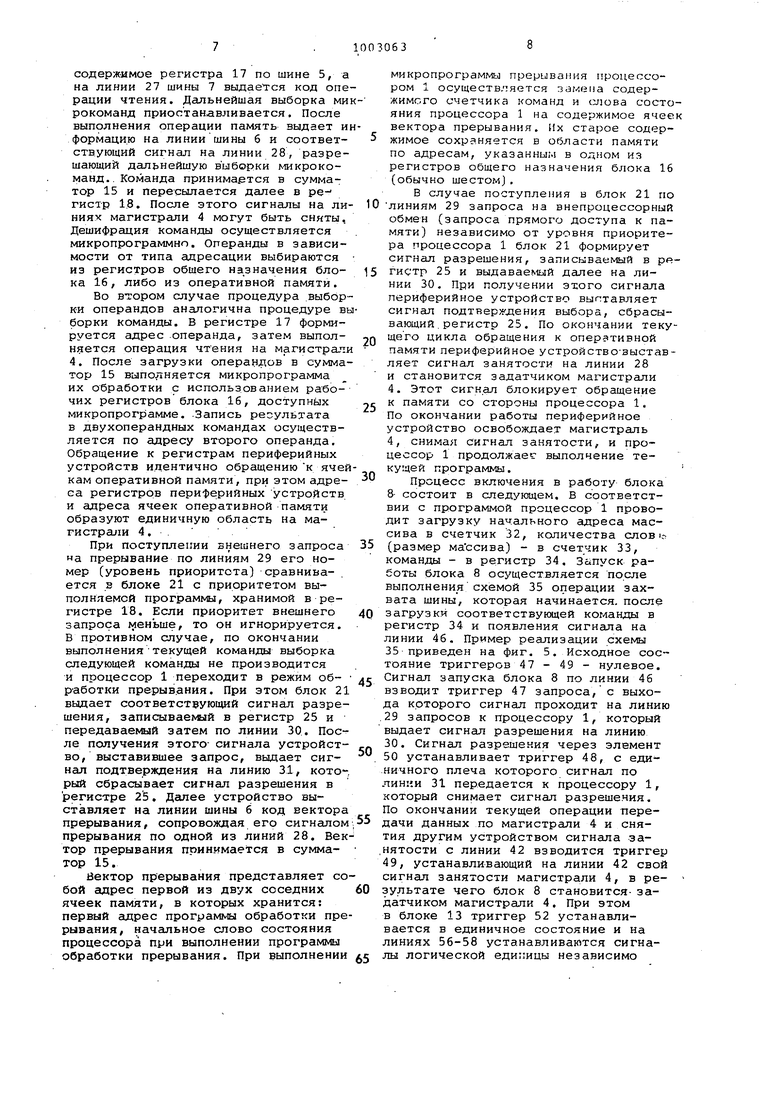

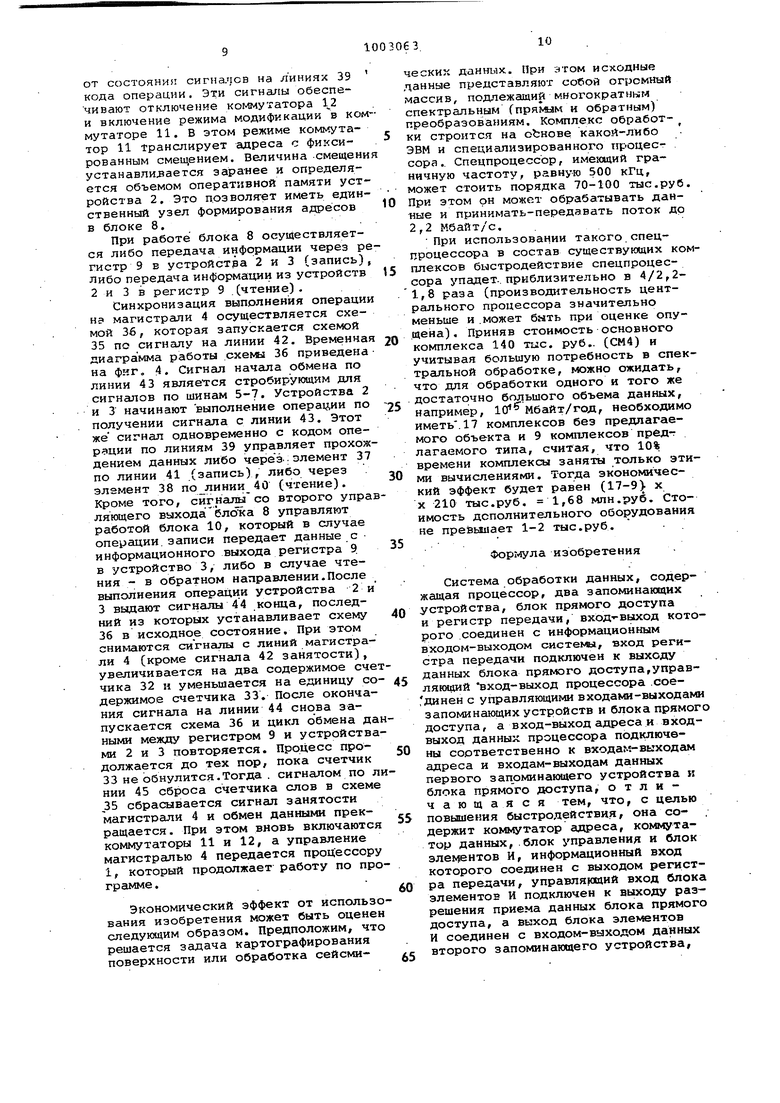

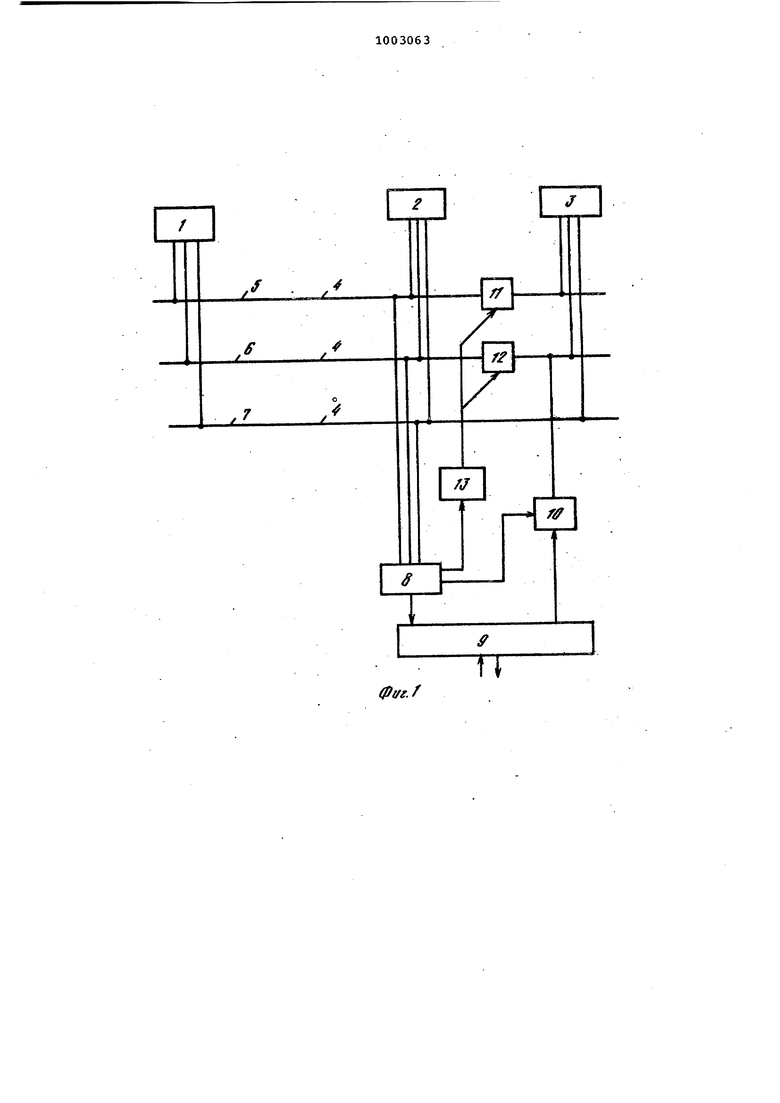

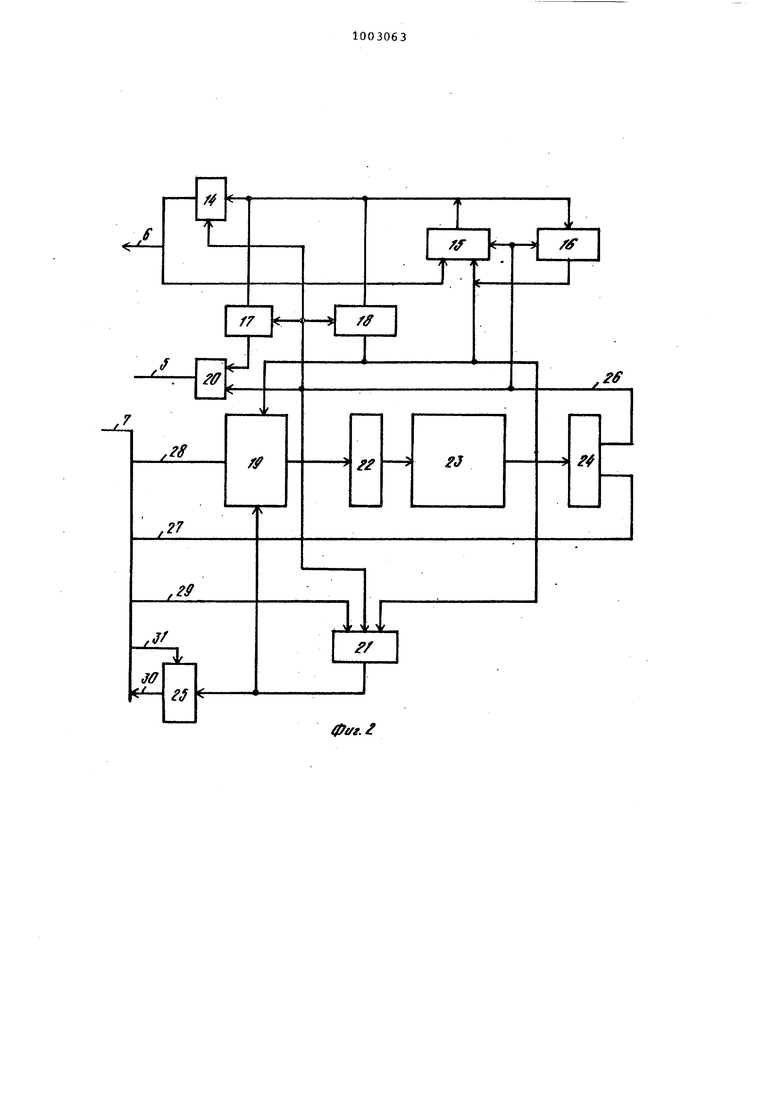

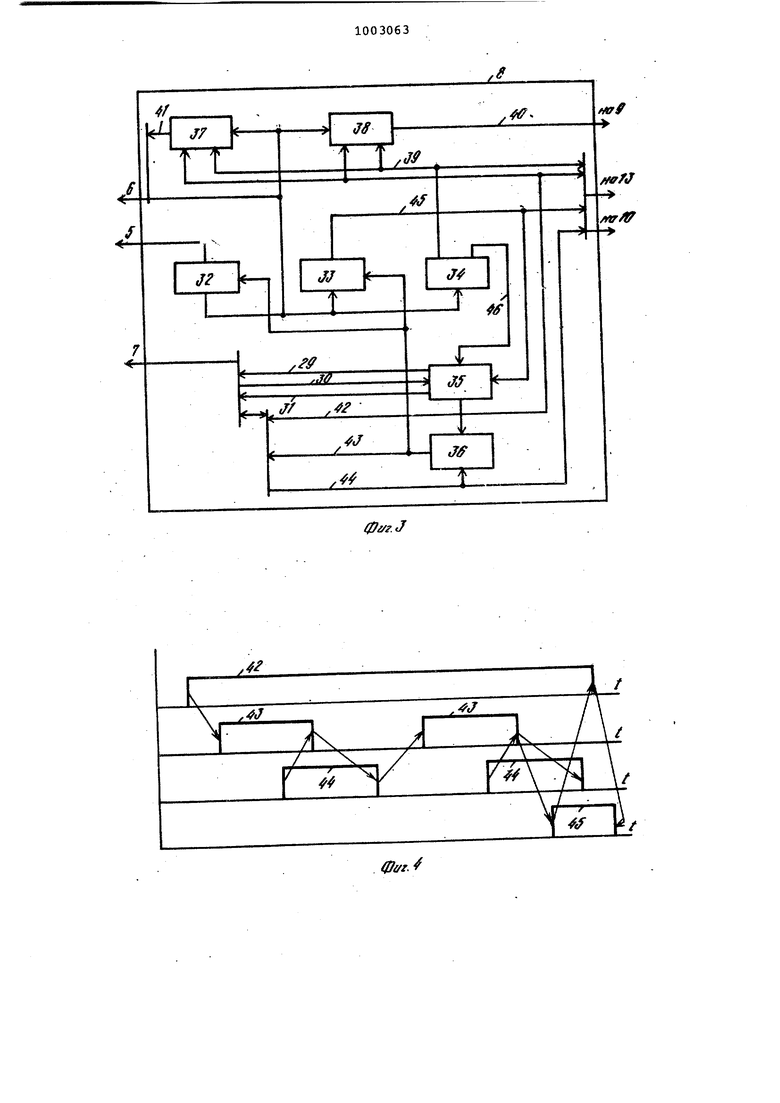

На фиг. 1 представлена структурная схема cиcтeмы на фиг. 2 - приме реализации процессора; на фиг. 3 пример реализации блока прямого доступа; на фиг. 4 - временная диаграмма работы схемы синхронизации на фиг. 5 - пример реализации схемы прерывания; на фиг. б - пример реализации блока управления.

Система содержит процессор 1, запоминающие устройства 2 и 3, соединенные с помощью магистрали 4,включающей шину 5 адреса, шину. 6 данных и шину 7 управления, а также блок 8 прямого доступа, регистр 9 передачи; блок 10 элементов И, коммутатор 11 адреса, коммутатор 12 данных и блок 13 управления (фиг. 1). Вход-выход регистра 9 соединен с информационным входом-выходом системы, вход регистра 9 подключен к выходу данных блока 8, а управляющий вход-выход процессора 1 соединен с управляющими входами-выходами устройств 2 и 3 и блока 8. Вход-выход адреса и вход-выход данных процессора 1 подключены соответственно к входам-выходам адреса и входам-выходам данньсх устройства. 2 и блока 8. Информационный вход блока 10 соединен с выходом регистра 9, управляющий вход блока 10 подключен к выходу разрешения приема данных блока 8, а выход блока 10 соединен с входом-выходом данных устройства 3. Вход блока 13 подключен к выходу управления коммутацией блока 8, а выход блока 13 соединен с управляющими входами коммутаторов 11 и 12, первые входы-выходы которых подключены соответственно к входам-выходам адреса и данных процессора 1, а вторые входы-выходы - к входам-выходам соответственно адреса и данных устройства 3.

.Процессор 1 (фиг. 2) содержит первый блок 14 элементов И (для передачи

сигналов по линиям шины 6J, сумматор 15, блок 16 регистров,регистр 17 . адреса, регистр 18 состояния, шифратор 19, адресов микрокоманд, второй блок 20 элементов И для передачи сигналов по линиям шины 5, блок 21 сравнения приоритетов, регистр 22 адреса микрокоманды, память 23 микрокоманд, регистр 24 микрокоманды, регистр 25 управления. Управление работой блоков процессора I осуществ-Ю ляется сигналами по линиям 26 управления. Шина 7 включает линии 27 кодов управления магистрали, линии 28 состояния магистрали, линии 29 запросов, линии 30 разрешения, линию 31 V5 подтверждения выбора.

Блок 8 прямого доступа (фиг. 3) содержит счетчик 32 адреса, счетчик 33 слов, регистр 34 управления,схему 35 прерывания, схему 36 синхрониза- 20 НИИ, элементы И 37 и 38. Кроме того, на фиг. 3 обозначены линии 39 кода операции, линии 40 передачи данных через регистр 9,.линии 41 передачи данных на шину 6, линия 42 занятое- s ти магистрали 4, линия 43 начала об- мена, линия 44 конца обмена, линия 45 сброса счетчика слов,линия 46 запуска блока 8 прямого доступа.

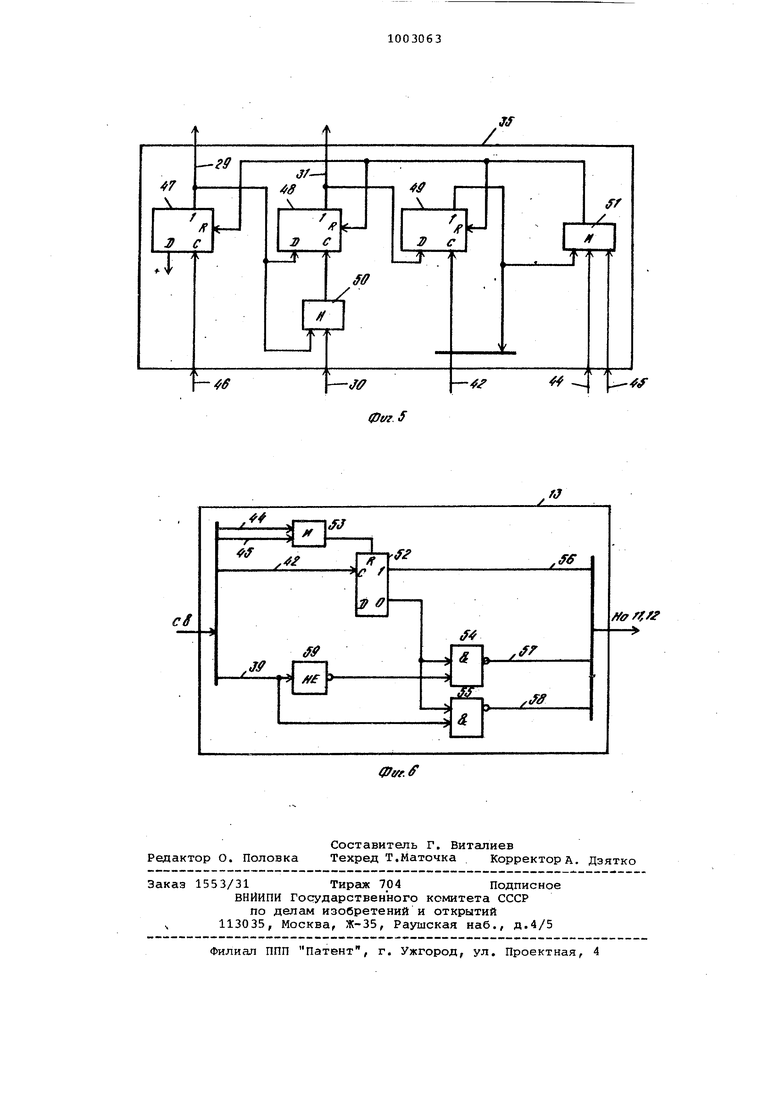

Схема 35 прерывания (фиг.5) со- . держит триггер 47 запроса, триггер 48 подтверждения выбора, триггер 49 занятости магистрали 4, элементы И 50 и 51. , . . Блок 13 управления (фиг. 6) со- 35. держит триггер 52 режима, элемент И 53, элементы И-НЕ 54 и 55, элемент НЕ 59. Выходами блока 13 являются линия 56 управления блоком 11, линия 57 управления блоком 12 при . -40 чтении, линия 58 управления блоком 12 при записи. , .

Процессор 1, запоминающие устройства 2 и 3 -и блок 8 соединены между собой единой магистралью 4. В каче- 45 стне устройств 2 и 3 могут быть использованы устройства оперативной . памяти, а также устройства внаиней памяти и устройства ввода-шлвода.

Система обработки данных работает сп следующим образом..

Управление работой магистрали 4 в каждый момент времени осуществляет стройство-задатчик. В рассматриваеом случае задатчикамимогут быть ибо процессор 1, либо блок 8 пряого доступа. .,

В моменты, когда задатчиком явяется процессор 1, коммутатор 11 коммутатор 12 обеспечивают прохожение, сигналов без изменения в режиме ,-jSO овторения (коммутатор замкнут).При том обеспечивается нормальная раота про цессора 1 по программе, храимой как в устройстве 2, так и в стройстве 3.

Процессор 1 функционирует следующим образом.

Раб.ота отдельных блоков и узлов процессора 1 координируется микропрограммным устройством управления, включающим шифратор 19, регистр 22, память 23 и регистр 24. Команды, выполняемые процессором 1, разделяются на адресные команды и команды управления. Адресные команды делятся на одно- и двухоперандные, к ним относятся команда; очистки, модификации (вычитание и прибавление единицы, сдвиг), пересылки, арифметические и логические команды К командам управления относятся команды перехода (условного и безусловного) и общего управления (сброс, останов, выход из прерывания) . Адресные команды в общем случае выполняются в четыре такта: выборка команды, выборка операнда (или операндов), исполнение и запись результата. Блок 16 включает набор регистров общего назначения, содержимое которых может быть использовано в командах, а также набор рабочих регистров, доступных микропрограмме Регистр 18 включает разряды признаJKOB, определяемые по результату выполнения команды сумматором 15 (равенство результата нулю, знак результата, переполнение), и разряды, определяющие приоритет выполняемой программы.

Кроме тогр, регистр 18 хранит инструкцию, выполняемую в данный момент процессором 1. Шифратор 19 осуществляет формирование (шифрацию) адреса следующей микрокоманды при исполнении команд процессором 1. Адрес следующей микрокоманды Формируется .в зависимости от выполняемой инструкции, хранимой в регистре 18, предыдущей микрокоманды, сигналов состояния магистрали и сигналов от блока 21, определяющих переход процессора 1 на микропрограмму выполнения прерывания. Реализация этого блока осуществляется на основе постоянного запоминающего устройства (ПЗУ), входные сигналы которого интерпретируются как -адрес ячейки, в которой хранится адрес сяедуюией микрокоманды, выполняемой процессором 1. Один из регистров общего назначения блока 16 используется в качестве счетчика команд, хранящего адрес текущей команды (инструкции). В такте выборки команды содержимое счетчика команд пересылается из блока 16 в сумматор 15, а также в регистр 17, затем содержимое счетчика .команд модифицируется в сумматоре 15 на +2 и возвращается в регистр блока 16.

Для считывания команды из памяти открывается блок 20, пересылающий содержимое регистра 17 по шине 5, а на линии 27 шины 7 выдается код опе рации чтения. Дальнейшая выборка ми рокоманд приостанавливается. После выполнения операции память выдает и формацию на линии шины б и соответствующий сигнал на линии 28, разрешающий дальнейшую выборки макрокоманд. . Команда принимается в сумматор 15 и пересылается далее в ре- гистр 1.8. После этого сигналы на ли ниях магистрали 4 могут быть сняты, Дешифрация команды осуществляется микропрограммно. Операнды в зависимости от типа адресации выбираются из регистров общего на.значения блока 16, либо из оперативной памяти. Во втором случае процедура выбор ки операндов аналогична процедуре в борки команды. В регистре 17 формируется адрес -операнда, затем выполняется операция чтения на магистрал 4. После загрузки операндов в сумма тор 15 выполняется микропрограмма их обработки с использованием рабочих регистров блока 16, доступных микропрограмме. .Запись результата в двухоперандных командах осуществляется по адресу второго операнда. Обращение к регистрам периферийных устройств идентично обращению к яче кам оперативной памяти, при этом адреса регистров периферийных устройств и адреса ячеек оперативной памяти образуют единичную область на магистрали 4. . При поступлении внешнего запроса а прерывание по линиям 29 его номер (уровень приоритета) сравнивается S блоке 21 с приоритетом выполняемой программы, хранимой в регистре 18. Если приоритет внешнего запроса меньше, то он игнорируется. В противном случае, по окончании выполнениятекущей команды выборка следующей команды не производится и процессор 1 переходит в режим обр-аботки прерывания. При этом блок 2 выдает соответствующий сигнал разре шения, записывае ый в регистр 25 и передаваемый затем по линии 30. Пос ле получения этого- сигнала устройст во, выставившее запрос, выдает сигнал подтверждения на линию 31, кото рый сбрасывает сигнал разрешения в регистре 25. Далее устройство выставляет на линии шины 6 код вектора прерывания, сопровождая его сигналом прерывания по одной из линий 28. Ве тор прерывания принимается в сумматор 15. Вектор прерывания представляет со бой адрес первой из двух соседних ячеек памяти, в которых хранится: первый адрес программы обработки пре рывания, начальное слово состояния процессора при выполнении программы обработки прерывания. При выполнении микропрограммы прерывания процессором 1 осуществ.;яется замена содержимого счетчика команд и сиюва состояния процессора 1 на содержимое ячеек вектора прерывания. Их старое содержимое сохраняется в области памяти по адресам, указанны;. в одном из регистров общего назначения блока 16 (обычно шестом, В случае поступления в блок 21 по линиям 29 запроса на внепроцессорный обмен (запроса прямого доступа к памяти) независимо от уровня приоритера процессора 1 блок 21 формирует сигнал разрешения, записываемый в регистр 25 и выдаваемый далее на линии 30, При получении эхого сигнала периферийное устройство выставляет сигнал подтверждения выбора, сбрасывающий, регистр 25. По окончании текущего цикла обращения к оперативной памяти периферийное устройство-выставляет сигнал занятости на линии 28 и становится задатчиком магистрали 4. Этот сигнал блокирует обращение к памяти со стороны процессора 1. По окончании работы периферийное устройство освобождает магистраль 4, снимая сигнал занятости, и процессор 1 продолжаес выполнение текущей программы. Процесс включения в работу блока 8- состоит в следующем. В соответствии с программой процессор 1 проводит загрузку начального адреса массива в счетчик 32, количества слов k(размер массива) - в счетчик 33, команды - в регистр 34. Запуск работы блока 8 осуществляется после выполнения схемой 35 операции захвата шины, которая начинается, после загрузки соответствующей команды в регистр 34 и появления сигнала на линии 46. Пример реализации схемы 35 приведен на фиг. 5. Исходное состояние триггеров 47 - 49 - нулевое. Сигнал запуска блока 8 по линии 46 взводит триггер 47 запроса, с выхода которого сигнал проходит на линию 29 запросов к процессору 1, который выдает сигнал разрешения на линию 30. Сигнал разрешения через элемент 50 устанавливает триггер 48, с единичного плеча которого сигнал по линии 31 передается к процессору 1, который снимает сигнал разреше.ния. По окончании текущей операции передачи данных по магистрали 4 и снятия другим устройством сигнала занятости с линии 42 взводится триггер 49, устанавливающий на линии 42 свой сигнал занятости магистрали 4, в ре- зультате чего блок 8 становится- задатчиком магистрали 4. При этом в блоке 13 триггер 52 устанавливается в единичное состояние и на линиях 56-58 устанавливаются сигналы логической единицы независимо от состояния сигналов на линиях 39 кода операции. Эти сигналы обеспечивают отключение коммутатора 2 и включение режима модификации в ком мутаторе 11. В этом режиме коммутатор 11 Транслирует адреса с фиксированным смещением. Величина -смещени устанавлилается заранее и определяется объемом оперативной памяти устройства 2. Это дозволя-ет иметь единственный узел формирования адресов в блоке 8. . При работе блока 8 осуществляется либо передача информации через ре гистр 9 в устройства 2 и 3 (запись) либо передача информации из устройств 2и 3 в регистр 9 (чт:ет1е} . Синхронизация выполнения операции нэ магистрали 4 осуществляется схемой 36, которая запускается схемой 35по сигналу на линии 42. Временная диаграмма работы .схемы 36 приведена на фкг, 4. Сигнал начала обмена по линии 43 является стробирукяцим для сигналов по шинам 5-7. Устройства 2 и 3 начинают выполнение операции по получении сигнала с линии 43. Этот же сигнал одновременно с кодом операции по линиям 39 управляет прохождением данных либо череэ.: элемент 37 по линии 41 (запись), либо через . элемент 38 по линии 40 (чтение). Кроме того, сигнсшы со второго управ ляющего выходаблотка 8 управляют работой блока 10, который в случае операции.записи передает данные с информационного выхода регистра 9. в устройство 3, либо в случае чтения - в обратном направлении.После выполнения операции устройства 2 и 3выдают сигналы 44 конца, последний из которых устанавливает схему 36в исходное состояние. При этом снимаются сигналы с линий магистрали 4 (кроме сигнала 42 занятости), увеличивается на два содержимое счет чика 32 и уменьшается на единицу содержимое счетчика 33. После окончания сигнала на линии 44 снова запускается схема 36 и цикл обмена дан ными между регистром 9 и устройствами 2 и 3 повторяется. Процесс продолжается до тех пор, пока счетчик 33 не обнулится.Тогда . сигналом по ли нии 45 сброса счетчика слов в схеме ,35 сбрасывается сигнал занятости магистрали 4 и обмен данными прекращается . При этом вновь включаются коммутаторы 11 и 12, а управление магистралью 4 передается процессору 1, который продолжает работу по программе . Экономический эффект от использо вания изобретения может быть оценен следующим образом. Предположим, что решается задача картографирования поверхности или обработка сейсмических данных;. При этом исходные данные представляют собой огромный массив, подлежащий многократным спектральным (прягвлм и обратным) преобразованиям. Комплекс обработки строится на оЪнове какой-либо ЭВМ и специализированного процессора .. Спецпроцессор, имеющий граничную частоту, равную 500 кГц, может стоить порядка 70-100 тыс.руб. При этом он может обрабатывать данные и принимать-передавать поток до 2,2 Мбайт/с. При использовании такого.спецпроцессора в состав существующих комплексов быстродействие спецпроцессора упадет., приблизительно в 4/2,21,8 раза (производительность центрального процессора значительно меньше и .может бать при оценке опущена). Приняв стоимость основного комплекса 140 тис. руб.. (СМ4) и учитывая большую потребность в спектрёшьной обработке, можно ожидать, что для обработки одного и того же достаточно большого объема данных, например, 10 Мбайт/год, необходимо иметь. 17 комплексов без предлагаемого объекта и 9 комплексов предт лагаемого типа, считая, что 10% времени комплексы заняты только этими вычислениями. Тогда экономический эффект будет равен (17-9 х X 210 тыс.руб. 1,68 млн.руб. Стоимость дополнительного оборудования не превыиает 1-2 тыс.руб. Форг- ула изобретения Система обработки данных, содержащая процессор, два запоминающих устройства, блок прямого доступа и регистр передачи, вход--выход которого .соединен с информационным входом-выходом систеки, вход регистра передачи подключен к выходу данных блока прямого доступа,управляющий вход-выход процессора .соединен с управляющими входами-выходами запоминающих устройств и блока прямого доступа, а вход-выход адреса и входвыход данных процессора подключены соответственно к входам-выходам адреса и входам-выходам данных первого запоминающего устройства к блока прямого доступа, отличающаяся тем, что, с целью повышения быстродействия, она содержит коммутатор адреса, коммутатор данных,.блок управления и блок элементов И, информационный вход которого соединен с выходом регистра передачи, управлявший вход блока элементов И подключен к выходу разрешения приема данных блока прямого доступа, а выход блока элементов И соединен с входом-выходом данных второго запоминающего устройства, вход блока управления подключен к выходу управления коммутацией блрка прямого доступа, а выход блока управления соединен с управляющими входаг-ад коммутаторов адреса и дан-. ных, первые входы-выходы которых подключеньт соответственно к входамвыходам адреса и данных, первые вхо ды-выходы которых подключены соотве ственно к входам-выходам адреса и Сданных процессора, а вторые входывыкоды - к входам-выходам соответст венно адреса и данных второго запоминающего ус-гройства, 2, Система поп.1,отличающаяся тем, что процес™ сор содержит два блока элементов И, сумматор, блок регистров, регистр адреса, регистр состояния, шифратор адреса, регистр адреса микрокоманды, память микрокоманд, регист микрокоманды, блок сравнения приоритетов и регистр управления,.входвыход которого соединен с управляющим входом-выходом процессора, первыми входами шифратора адреса и блока сравнения приоритетов и первым выходом регистра микрокоманды, вход которого подключен к выходу памяти микрокоманд, а выход - к второму входу блока сравнения приор тетов, первым входам первого и второго блоков элементов И и управляющ входам регистра адреса, регистра со тояния, сумматора и блока регистров выход блока регистров соединен с третьим входом блока сравнения прио ритетов, первым информационным входом сумматора, выходом регистра сос тояния и вторым входом шифратора ад реса, выход блока сравнения приоритетов подключен к третьему входу ши ;: ратора адреса и входу регистра управления, вход регистра адреса микрокоманды соединен с выходом шифратора адреса, а вщход - с входом памяти микрокоманд, выход сумматора подключен к входа блока регистров, регистра адреса, регистра состояния и второму входу первого блока элементоЕ И, вход-выход данных процессора соединен -с выходом первого блока элементов И и вторым информационным входом сумматора, второй вход второго блокг элементов И подключен к выходу регистра адреса, а выход -к входу-выход адреса процессора. 3. Система по п.1, о т л и ч а ю щ а я с я тем, что блок управления содержит триггер режима, элемент И, два элемента И-НЕ и элемент НЕ, при этом вход элемента НЕ, первый и второй входы элемента И и синхровход триггера режима соединены с входом блока, выход элемента И подключен к установочному входу триггера режима, прямой выход которого соединен с выходом блока, а инверсный выход подключен к первым входам первого и второго элементов И-НЕ, вторые вхохг которых соединены соответственно с входом блока и выходом элемента НЕ, а выходы элементов И-НЕ подключены к выходу блока. Источники информации, принятые во внимание при экспвртиз& 1.Патент ОНА № 3710324, кл. 340-172.5, опублик. 1973. 2.Техническое описание Управляющий вычислительный комплекс СМ4 261.620.006 ТО. 3.Техническое описание Управляющий вычислительный комплекс СМЗ, 261.620,005 ТО (прототип).

фуг.

фиг. I

Фf/г.J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

Авторы

Даты

1983-03-07—Публикация

1980-12-08—Подача